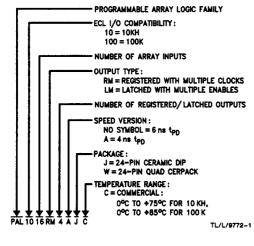

# PAL10/10016RM4A, PAL10/10016LM4A ECL Programmable Array Logic

#### **General Description**

The PAL10/10016RM4A and PAL10/10016LM4A are members of the National Semiconductor ECL PAL® family. The ECL PAL Series-A is characterized by 4 ns maximum propagation delays (combinatorial input-to-output). The pinout, JEDEC fuse-map format and programming algorithm of these devices are compatible with those of all prior ECL PAL products from National. Series-A ECL PAL devices are manufactured using National Semiconductor's advanced oxide-isolated process with proven titanium-tungsten fuse technology to provide high-speed user-programmable replacements for conventional ECL SSI/MSI logic with significant chip-count reduction.

Programmable logic devices provide convenient solutions for a wide variety of application-specific functions, including random logic, custom decoders, state machines, etc. By programming fuse links to configure AND/OR gate connections, the system designer can implement custom logic as convenient sum-of-products Boolean functions. System prototyping and design iterations can be performed quickly using these off-the-shelf products.

The PAL10/10016RM/LM4A logic array has a total of 16 complementary input pairs, 32 product terms and four output functions; each output function is the OR-sum of 8 product terms. The 16RM4A provides an edge-triggered D-type register on each of its four outputs. Registers allow the PAL device to implement sequential logic circuits. The 16LM4A provides D-type transparent latches on its four outputs. Polarity fuses allow each output to be active-high or active-low.

Programming equipment and software make PAL design development quick and easy. Programming is accomplished using TTL voltage levels and is therefore supported by several conventional TTL PLD programming units. After programming and verifying the logic array, an additional security fuse may be programmed to prevent direct copying of proprietary logic designs.

#### **Features**

■ High speed:

t<sub>SU</sub> = 3 ns min

t<sub>CLK</sub> = 2 ns max

f<sub>MAX</sub> = 200 MHz max (registered)

t<sub>PD</sub> = 4 ns max (combinatorial)

- Programmable replacement for ECL SSI/MSI logic

- Both 10 KH and 100K I/O compatible versions

- Four registered or latched output functions with !/O pin feedback; twelve dedicated inputs

- Individually programmable polarity on all logic outputs

- Reliable Titanium Tungsten fuses

- Security fuse to prevent direct copying

- Programmed on conventional TTL PLD programmers

- Fully Supported by PLAN™ Software

- Packaging:

24-pin thin DIP (0.300") 24-pin Quad Cerpak

#### Ordering Information

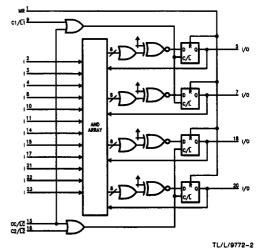

#### Block Diagram PAL10/10016RM/LM4A

$V_{EE} = 12$ ,  $V_{CC} = 24$ ,  $V_{CCO}$  (5,7) = 6,  $V_{CCO}$  (18,20) = 19 Pinout applies to 24-pin DIP.

2-217

#### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Temperature Under Bias

V<sub>EE</sub> Relative to V<sub>CC</sub>

-55°C to +125°C

Storage Temperature Range

-65°C to +150°C -7V to +0.5V Input Voltage

$V_{EE}$  to +0.5V

Output Current

Lead Temperature (Soldering, 10 seconds)

--50 mA 300°C

1000V

ESD Tolerance

$C_{ZAP} = 100 \text{ pF}$  $R_{ZAP} = 1500\Omega$

Test Method: Human Body Model Test Specification: NSC SOP-5-028

**Recommended Operating Conditions**

| Symbol          | Parameter                       |       | Min   | Тур  | Max   | Units    |

|-----------------|---------------------------------|-------|-------|------|-------|----------|

| V <sub>EE</sub> | Supply Voltage                  | 10 KH | -5.46 | -5.2 | -4.94 | v        |

|                 |                                 | 100K  | -4.73 | -4.5 | -4.27 |          |

| Т               | Operating Temperature<br>(Note) | 10 KH | 0     |      | + 75  | •c       |

|                 |                                 | 100K  | 0     |      | +85   | <u> </u> |

| RL              | Standard 10 KH/100K Load        |       |       | 50   |       | Ω        |

| CL              | Standard 10 KH/100K Load        |       |       | 5    |       | pF       |

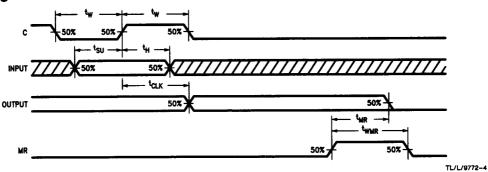

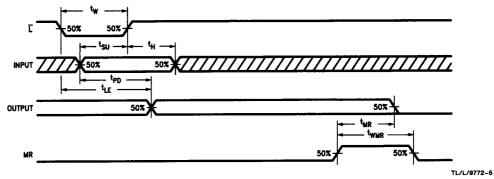

| tsu             | Setup Time of Input or Feedback |       | 3.0   |      |       | ns       |

| tн              | Input Hold Time                 |       | 0     |      |       | ns       |

| tw              | Clock or Enable Pulse Width     |       | 2.0   |      |       | ns       |

| twmn            | Master Reset Pulse Width        |       | 2.0   |      |       | ns       |

#### Electrical Characteristics Over Recommended Operating Conditions

| Symbol                                    | Parameter                                  |                                                                   | Conditions           |                         |                         | Min                     | Max                     | Units |

|-------------------------------------------|--------------------------------------------|-------------------------------------------------------------------|----------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------|

| VIH                                       | High Level Input Voltage                   | Guaranteed Inpu<br>High For All Input                             |                      | 10 KH                   | 0°C<br>+ 25°C<br>+ 75°C | -1170<br>-1130<br>-1070 | -840<br>-810<br>-735    | mV    |

|                                           |                                            |                                                                   |                      | 100K                    | 0°C to +85°C            | -1165                   | -880                    |       |

| VIL                                       | Low Level Input Voltage Low For All Inputs |                                                                   | 10 KH                | 0°C<br>+ 25°C<br>+ 75°C | 1950<br>1950<br>1950    | -1480<br>-1480<br>-1450 | m∨                      |       |

|                                           |                                            |                                                                   |                      | 100K                    | 0°C to +85°C            | -1810                   | -1475                   |       |

| V <sub>OH</sub> High Level Output Voltage |                                            | $V_{IN} = V_{IH}$ Max. or $V_{IL}$ Min.                           |                      | 10 KH                   | 0°C<br>+ 25°C<br>+ 75°C | -1020<br>-980<br>-920   | -840<br>-810<br>-735    | m∨    |

|                                           |                                            |                                                                   | ı                    | 100K                    | 0°C to +85°C            | -1025                   | -880                    |       |

| V <sub>OL</sub> Low Level Output Voltage  |                                            | V <sub>IN</sub> = V <sub>IH</sub> Max. or V <sub>IL</sub> Min.    |                      | 10 KH                   | 0°C<br>+ 25°C<br>+ 75°C | 1950<br>1950<br>1950    | -1630<br>-1630<br>-1600 | m∨    |

|                                           |                                            |                                                                   |                      | 100K                    | 0°C to +85°C            | -1810                   | -1620                   |       |

| <sup>1</sup> ІН                           | High Level Input Current                   | urrent V <sub>IN</sub> = V <sub>IH</sub> Max. Inputs, I/Os and MR |                      |                         |                         |                         | 220                     | μΑ    |

|                                           |                                            |                                                                   | Clocks/Latch Enables |                         |                         |                         | 350                     |       |

| I <sub>IL</sub>                           | Low Level Input Current                    | V <sub>IN</sub> = V <sub>IL</sub> Min. Except I/O Pins            |                      |                         |                         | 0.5                     |                         | μА    |

| IEE                                       | Supply Current                             | V <sub>EE</sub> = Min., All Inputs and Outputs Open               |                      |                         |                         | -240                    |                         | mA    |

Note: Operating temperatures for circuits in Dual-In-Line packages are specified as ambient temperatures (T<sub>A</sub>) with circuits mounted in socket or printed circuit board and transverse airflow exceeding 500 linear feet per minute. Operating temperatures for circuits packaged in Quad Cerpak are specified as case temperatures (T<sub>C</sub>). All specifications apply after thermal equilibrium has been established.

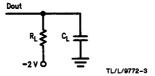

## **Switching Characteristics** Over Recommended Operating Conditions Output Load: R<sub>L</sub> = $50\Omega$ to -2.0V, C<sub>L</sub> = 5 pF to GND

| Symbol                       | Parameter -                  | Mea                                    | Min  | Max | Units |     |

|------------------------------|------------------------------|----------------------------------------|------|-----|-------|-----|

| Symbol                       |                              | From                                   | То   |     |       |     |

| t <sub>CLK</sub> (Note 1)    | Clock to Output or Feedback  | C <sub>n</sub> ↑                       | 1/0  |     | 2.0   | ns  |

| t <sub>LE</sub> (Note 2)     | Enable to Output or Feedback | <u>L</u> n ↓                           | 1/0  |     | 2.0   | ns  |

| t <sub>PD</sub> (Note 2)     | Input or Feedback to Output  | 1                                      | 1/0  |     | 4.0   | ns  |

| t <sub>MR</sub> (Note 1, 2)  | Master Reset to Output       | MR ↑                                   | 1/0↓ |     | 3.5   | ns  |

| f <sub>MAX</sub> (Note 1, 3) | Maximum Frequency            |                                        |      |     | 200   | MHz |

| t <sub>r</sub>               | Output Rise Time             | Measured Between<br>20% and 80% points |      | 0.5 | 2.0   | ns  |

| t <sub>f</sub>               | Output Fall Time             |                                        |      | 0.5 | 2.0   | ns  |

Note 1: Applies to 16RM4. Note 2: Applies to 16LM4. Note 3:  $f_{MAX} = (t_{SU} + t_{CLK})^{-1}$

#### **Test Load**

#### Timing Waveform PAL10/10016RM4A

### Timing Waveform PAL10/10016LM4A

2-219

#### **Connection Diagrams** 24-Pin Dual-In-Line Packages PAL10/10016RM4A PAL10/10016LM4A 24 24 2 23 23 22 22 21 21 1/0-1/0 20 20 - v<sub>∞</sub> Acco. 19 19 V<sub>∞</sub> ٠٧ 1/0 18 1/0 18 17 17 C1 16 LI 16 .17 10 15 15 12 13 V<sub>EE</sub> 13 TL/L/9772-6 TL/L/9772-7 24-Pin Quad Cerpak PAL10/10016RM4A PAL10/10016LM4A 22 21 24 23 22 21 20 C2 18 13 18 17 17 1/0-1/0 16 V<sub>CCO</sub> 15 V<sub>CCO</sub> 15 Vcco Vcco 1/0 1/0 1/0 14 13 10 11 12 10 11 8 8 TL/L/9772-8 TL/L/9772-9 **Pin Descriptions** Pin Description Pin Description Twelve dedicated inputs to logic array. 12 Latch enable input ORed with LC to control latches on output pins\* 18 and 20. Latches are transparent I/O Four outputs from registered or latched logic functions. Also provides feedback and may be used for (data written into latch) while both L2 and LC are low. additional inputs to logic array. Common Clock input (see C1, C2). CC Clock input ORed with CC to control registers on out-LC Common Latch enable input (see 11, 2). put pins\* 5 and 7. Data is written into registers on Master Reset input. Asynchronously resets all regisrising edge of clock. ters or latches to the low state while MR is high Clock input ORed with CC to control registers on out-(overrides clock and latch enable inputs). put pins\* 18 and 20. Data is written into registers on VEE Supply voltage. rising edge of clock. V<sub>CC</sub> Ground for internal circuitry. Latch enable input ORed with LC to control latches on V<sub>CCO</sub> Ground for output drivers (2 outputs per V<sub>CCO</sub>). output pins\* 5 and 7. Latches are transparent (data written into latch) while both 12 and 10 are low. \*Corresponds to DIP pinout

#### **Functional Description**

The PAL10/10016RM/LM4A consists of a single programmable AND-gate array with fixed OR-gate connections. The AND array consists of 16 complementary pairs of input lines crossing 32 product-term lines with a programmable fuse at each intersection (1024 fuses). The product terms are organized into four groups of eight each. The eight product terms in each group are connected into an OR-gate to produce the sum-of-products logic function.

An unprogrammed fuse establishes a connection between an input line (true or complement phase of an array input signal) and a product term. Programming the fuse removes the connection. A product term is satisfied (logically true) while all the input lines connected to it (via intact fuses) are in the proper logic state. Therefore, if both the true and complement of at least one array input are left connected to a product line, that product term would always be held in the low logic state (which is the state of all product terms in an unprogrammed device).

The four outputs of the PAL10/10016RM4A pass through D-type registers triggered on the high-going edge of the appropriate clock input. The outputs of the PAL10/10016LM4A pass through D-type transparent latches which are enabled (pass data) while the appropriate enable inputs are low. The four registers or latches are separated into two pairs. A separate clock/latch-enable input is provided for each pair. An additional common clock/enable input is ORed with each (see logic diagrams which follow).

The AND-OR logic functions can be optionally inverted before the registers or latches. Polarity inversion is controlled by an individual "polarity fuse" associated with each output function (the original unprogrammed state produces active-high logic functions). Device output pins always indicate active-high register/latch outputs.

The I/O pins used for outputting the registered/latched logic functions also feed back into the logic array as additional inputs. This is useful, for example, to implement sequential circuits with registered parts. Any of these I/O pins may, instead, be used as an additional dedicated input pin. By leaving the associated logic function unprogrammed, the output driver would remain in the low logic state allowing an externally-applied signal to control the array input.

Logic functions requiring more than eight product terms can be implemented conveniently by OR-tying two (or more) device outputs. Partial sums are formed on each of the OR-tied output functions. Each function, however, must be programmed for active-high output polarity, and the associated registers/latches should be controlled by the same clock/enable signal. Each of the array inputs fed back from the OR-tied I/O pins would indicate the correct final logic function.

All input and I/O pins have on-chip 50  $k\Omega$  pull-down resistors.

#### **Functional Testing**

As with all field-programmable devices, the user of ECL PAL devices provides the final manufacturing step. While National's PAL devices undergo extensive testing when they are manufactured, their logic function can be fully tested only after they have been programmed to the user's pattern.

To ensure that the programmed PAL devices will operate properly in your system, National Semiconductor (along with most other manufacturers of PAL devices) strongly recommends that PAL devices be functionally tested before they are installed in your system. Even though the number of post-programming functional failures is small, testing the logic function of the PAL devices before they reach system assembly will save board debugging and rework costs. For more information about the functional testing of PAL devices, please refer to National Semiconductor's Application Note #351 and the *Programmable Logic Design Guide*.

#### **Design Development Support**

A variety of software tools and programming hardware is available to support the development of designs using PAL products. Typical software packages accept Boolean logic equations to define desired functions. Most are available to run on personal computers and generate JEDEC-compatible "fuse maps". The industry-standard JEDEC format ensures that the resulting fuse-map files can be down-loaded into a large variety of programming equipment. Many software packages and programming units support a large variety of programmable logic products as well. The PLANTM software package from National Semiconductor supports all programmable logic products available from National and is fully JEDEC-compatible. PLAN software also provides automatic device selection based on the designer's Boolean logic equations.

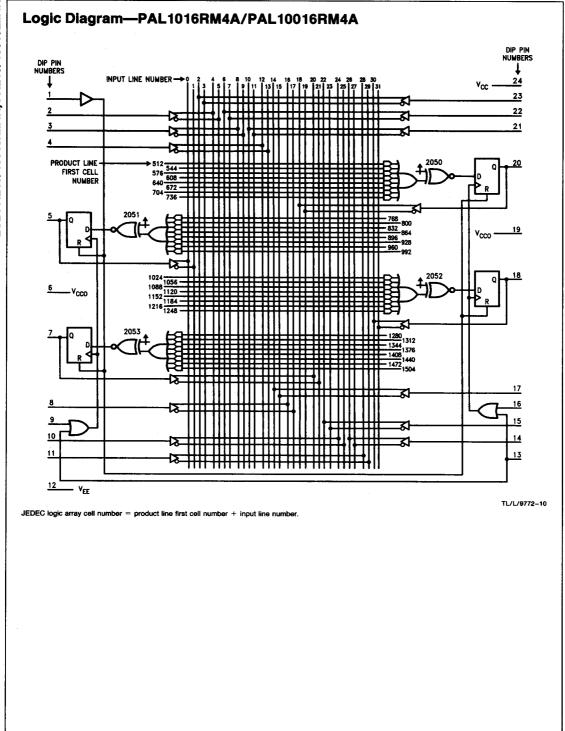

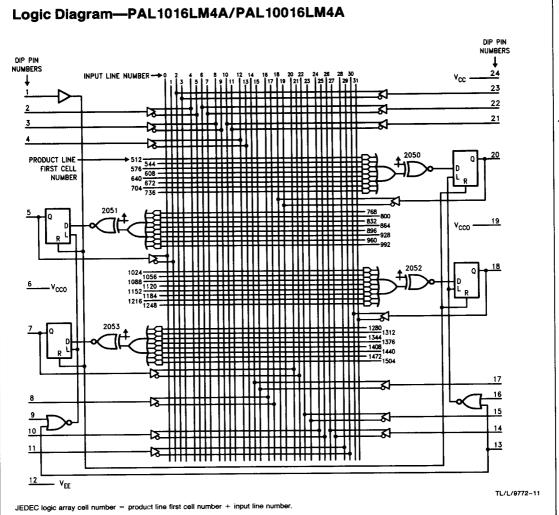

Detailed logic diagrams showing all JEDEC fuse-map addresses for the PAL10/10016RM/LM4A are provided for direct map editing and diagnostic purposes. For a list of current software and programming support tools available for these devices, please contact your local National Semi-conductor sales representative or distributor. If detailed specifications of the ECL PAL programming algorithm are needed, please contact the National Semi-conductor Programmable Device Support Department.