# P93U422 HIGH SPEED 256 × 4 **CMOS STATIC RAM**

T-46-23-08

### **FEATURES**

- Universal 256 × 4 Static RAM

- One part, the 93U422, replaces the following bipolar and CMOS parts:

- 93422A

- 93422

- -- 93L422A

- 93L422

- PACE Technology™ for High Performance/Low

- Fast Access Time

- 35 ns (Commercial)

- 35 ns (Military)

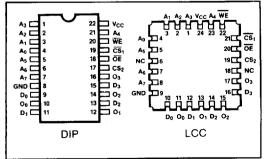

- Standard 400 mil DIP and Chip carrier packages

- CMOS for Low Power

- 440 mW (Commercial)

- 495 mW (Military)

- 5V Power Supply ±10% for both commercial and military temperature ranges

- Separate I/O

- Fully static operation with equal access and cycle

- Resistant to single event upset and latchup due to advanced process and design improvements

- Capable of withstanding greater than 2000V static discharge

#### DESCRIPTION

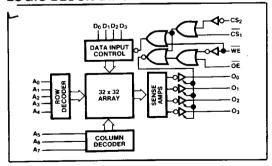

The P93U422 is a universal device designed to replace the entire 93 and 93L 256×4 bit static RAM families. The memory requires no clocks or refreshing and has equal access and cycle times. Inputs and outputs are fully TTL compatible. Operation is from a single 5 Volt supply. Easy memory expansion is provided by an active LOW chip select one (CS<sub>1</sub>) and an active HIGH chip select two (CS<sub>2</sub>) as well as 3-state outputs.

The P93U422 is part of the PACE RAM™ family of static RAMs. These high performance static RAMs are manufactured using PACE Technology™.

PACE Technology is Performance Advanced CMOS Engineered to use 0.8 micron effective channel lengths to give 500 picoseconds loaded\* internal gate delays. PACE Technology™ includes two level metal and epitaxial substrates. In addition to very high performance and very high density, the technology features latch-up protection, single event upset protection, and is supported by a class 2 environment volume production facility. The P93U422 is one of a family of PACE RAM™ products offering super fast access times.

\*For a fan-in/fan-out of 4, at 85°C junction temperature and 5.0V. For a fan-in/fan-out of 1, the internal gate delay is 200 picoseconds at room temperature and 5.0V.

# LOGIC BLOCK DIAGRAM

### PIN CONFIGURATIONS

SEMICONDUCTOR CORPORATION

Means Quality, Service and Speed

## **MAXIMUM RATINGS**(1,2)

PERFORMANCE

(Above which the useful life may be impaired.)

T-46-23-08

| Storage Temperature                                     | -65°C to +150°C                    |

|---------------------------------------------------------|------------------------------------|

| Ambient Temperature with Power Applied                  | -55°C to +125°C                    |

| Supply Voltage to Ground<br>Potential (Pin 22 to Pin 8) | -0.5V to +7.0V                     |

| DC Voltage Applied to Outputs for High Output State     | -0.5V to<br>V <sub>CC</sub> + 0.5V |

| DC Input Voltage                                        | -0.5V to<br>V <sub>CC</sub> + 0.5V |

| Output Current,<br>Into Outputs (Low)                    | 20mA                |

|----------------------------------------------------------|---------------------|

| DC Input Current                                         | -30 mA to<br>+5.0mA |

| Static Discharge Voltage (per MIL-STD-883 Method 3015.2) | >2000V              |

| Latchup Current                                          | >200mA              |

### **OPERATING RANGE**

| Range      | V <sub>CC</sub> | Ambient<br>Temperature | Range <sup>(6)</sup> | V <sub>CC</sub> | Ambient<br>Temperature |

|------------|-----------------|------------------------|----------------------|-----------------|------------------------|

| Commercial | 5V ±10%         | 0°C to 75°C            | Military             | 5V ±10%         | -55°C to +125°C        |

## DC ELECTRICAL CHARACTERISTICS(6)

Over Operating Range (Commercial and Military)

| Parameters      | Description                     | Test Cond                                                    | itions                                      | P93U422 |      | I     |

|-----------------|---------------------------------|--------------------------------------------------------------|---------------------------------------------|---------|------|-------|

| rarameters      | Description                     | lest Cond                                                    | IIIONS                                      | Min.    | Max. | Units |

| V <sub>OH</sub> | Output HIGH Voltage             | V <sub>CC</sub> = Min., V <sub>IN</sub> = V <sub>IH</sub> or | V <sub>IL</sub> , I <sub>OH</sub> = -5.2 mA | 2.4     |      | ٧     |

| V <sub>OL</sub> | Output LOW Voltage              | V <sub>CC</sub> = Min., V <sub>IN</sub> = V <sub>IH</sub> or | V <sub>IL</sub> , I <sub>OL</sub> = 8.0 mA  |         | 0.45 | ٧     |

| VIH             | Input HIGH Level                |                                                              |                                             | 2.1     |      | v     |

| V <sub>IL</sub> | Input LOW Level                 |                                                              |                                             |         | 0.8  | v     |

| I <sub>IL</sub> | Input LOW Current               | V <sub>IN</sub> = 0.40 V                                     |                                             |         | -300 | μΑ    |

| I <sub>IH</sub> | Input HIGH Current              | V <sub>CC</sub> = Max., V <sub>IN</sub> = 4.5 V              |                                             |         | 40   | μΑ    |

| I <sub>SC</sub> | Output Short Circuit Current(3) | V <sub>CC</sub> = Max., V <sub>OUT</sub> = 0.0               | V                                           |         | -70  | mA    |

|                 |                                 |                                                              | T <sub>A</sub> = 125°C                      |         | 70   |       |

| 1               | Power Supply Current            | All Inputs = GND                                             | T <sub>A</sub> = 75°C                       |         | 70   |       |

| Icc             | Power Supply Current            | V <sub>CC</sub> = Max.                                       | T <sub>A</sub> = 0°C                        |         | 80   | mA    |

|                 |                                 |                                                              | T <sub>A</sub> = -55°C                      |         | 90   |       |

| $V_{CL}$        | Input Clamp Voltage             | I <sub>IN</sub> = -10mA                                      |                                             |         | -1.5 | ٧     |

| 1               | Output Lookago Current          | V <sub>OUT</sub> = 2.4V, V <sub>CC</sub> = Max               |                                             |         | 50   |       |

| ICEX            | Output Leakage Current          | V <sub>OUT</sub> = 0.5V, V <sub>CC</sub> = Max.              |                                             | -50     |      | μΑ    |

### **CAPACITANCE**

| Parameters      | Description                             | P93U422 | Units | Parameters       | Description                              | P93U422 | Units |

|-----------------|-----------------------------------------|---------|-------|------------------|------------------------------------------|---------|-------|

|                 |                                         | Typ.    |       |                  | 2 000.19.1011                            | Тур.    | 0     |

| C <sub>IN</sub> | Input Pin<br>Capacitance <sup>(4)</sup> | 5       | рF    | C <sub>OUT</sub> | Output Pin<br>Capacitance <sup>(4)</sup> | 7       | pF    |

Unused inputs must always be connected to an appropriate logic voltage level, preferably either V<sub>CC</sub> or ground.

3) For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.

4) Tested on a sample basis.

<sup>1)</sup> These devices contain circuits to protect the inputs and outputs against damage due to high static voltages or electrostatic fields, however, it is advised that precautions be taken to avoid application of any voltage higher than maximum-rated voltages to these high-impedance circuits.

T-46-23-08

### **SWITCHING CHARACTERISTICS**

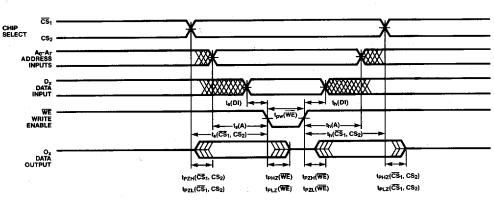

An active LOW write enable (WE) controls the writing/reading operation of the memory. When the chip select one (CS<sub>1</sub>) and the write enable (WE) are LOW and chip select two (CS2) is HIGH, the information on data inputs (D<sub>0</sub> through D<sub>3</sub>) is written into the addressed memory word and preconditions the output circuitry so that true data is present at the outputs when the write cycle is complete. This preconditioning operation insures minimum write recovery times by eliminating the "write recovery

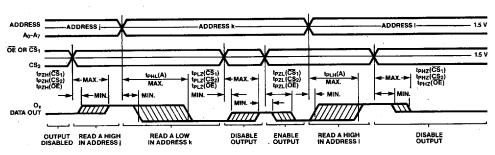

glitch". Reading is performed with chip select one (CS<sub>1</sub>) LOW, chip select two (CS<sub>2</sub>) HIGH, write enable (WE) HIGH and output enable (OE) LOW. The information stored in the addressed word is read out on the non-inverting outputs (O<sub>0</sub> through O<sub>3</sub>). The outputs of the memory go to an inactive high impedance state whenever chip select one (CS<sub>1</sub>) is HIGH, chip select two (CS2) is LOW, output enable (OE) is HIGH, or during the writing operation when write enable (WE) is LOW.

### MODE SELECT TABLE

|                 |                 | Input |    |    | Output           |                |

|-----------------|-----------------|-------|----|----|------------------|----------------|

| CS <sub>2</sub> | CS <sub>1</sub> | WE    | OE | Dn | On               | Mode           |

| L               | Х               | Χ.    | Х  | Х  | *HIGH Z          | Not Select     |

| Х               | Н               | Х     | Х  | Х  | *HIGH Z          | Not Select     |

| Н               | L               | X     | Н  | Х  | *HIGH Z          | Output Disable |

| н               | ٦               | Н     | L  | х  | Selected<br>Data | Read Data      |

|                 |                 | Input |    | Output |         |           |

|-----------------|-----------------|-------|----|--------|---------|-----------|

| CS <sub>2</sub> | CS <sub>1</sub> | WE    | OE | Dn     | On      | Mode      |

| Ή               | L               | L     | Х  | با     | *HIGH Z | Write "0" |

| Н               | L               | L     | X  | Н      | *HIGH Z | Write "1" |

#### Notes:

H = HIGH L = LOW X = Don't Care

\*HIGH Z implies outputs are disabled or off. This condition is defined as high impedance state for the P93U422.

### SWITCHING CHARACTERISTICS (5.6)

Over Operating Range (Commercial and Military)

| Parameters                                                                                                                                   | Description                                                                            | P93U422 |      |       |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------|------|-------|

|                                                                                                                                              | Description                                                                            | Min.    | Max. | Units |

| t <sub>PLH(A)</sub> <sup>(7)</sup><br>t <sub>PHL(A)</sub> <sup>(7)</sup>                                                                     | Delay from Address to Output (Address Access Time) (See Fig. 2)                        |         | 35   | ns    |

| t <sub>PZH</sub> (CS <sub>1</sub> , CS <sub>2</sub> ) <sup>(8)</sup><br>t <sub>PZL</sub> (CS <sub>1</sub> , CS <sub>2</sub> ) <sup>(8)</sup> | Delay from Chip Select to Active Output and Correct Data (See Fig. 2)                  |         | 25   | ns    |

| t <sub>PZH</sub> (WE) <sup>(8)</sup><br>t <sub>PZL</sub> (WE) <sup>(8)</sup>                                                                 | Delay from Write Enable to Active Output and Correct Data (Write Recovery)(See Fig. 1) |         | 25   | ns    |

| t <sub>PZH</sub> (OE) <sup>(8)</sup><br>t <sub>PZL</sub> (OE) <sup>(8)</sup>                                                                 | Delay from Output Enable to Active Output and Correct Data (See Fig. 2)                |         | 25   | ns    |

| t <sub>s</sub> (A)                                                                                                                           | Setup Time Address (Prior to Initiation of Write)(See Fig. 1)                          | 5       |      | ns    |

| t <sub>h</sub> (A)                                                                                                                           | Hold Time Address (After Termination of Write)(See Fig. 1)                             | 5       |      | ns    |

| t <sub>s</sub> (DI)                                                                                                                          | Setup Time Data Input (Prior to Initiation of Write)(See Fig. 1)                       | 5       |      | ns    |

| t <sub>h</sub> (DI)                                                                                                                          | Hold Time Data Input (After Termination of Write)(See Fig. 1)                          | 5       |      | ns    |

| t <sub>s</sub> (CS <sub>1</sub> , CS <sub>2</sub> )                                                                                          | Setup Time Chip Select (Prior to Initiation of Write)(See Fig. 1)                      | 5       |      | ns    |

| th (CS <sub>1</sub> , CS <sub>2</sub> )                                                                                                      | Hold Time Chip Select (After Termination of Write)(See Fig. 1)                         | 5       |      | ns    |

| t <sub>pw</sub> (WE)                                                                                                                         | Minimum Write Enable Pulse Width (to Insure Write)(See Fig. 1)                         | 20      |      | ns    |

| t <sub>PHZ</sub> (CS <sub>1</sub> , CS <sub>2</sub> ) <sup>(8)</sup><br>t <sub>PLZ</sub> (CS <sub>1</sub> , CS <sub>2</sub> ) <sup>(8)</sup> | Delay from Chip Select to Inactive Output (HIGH Z)(See Fig. 2)                         |         | 30   | ns    |

| t <sub>PHZ</sub> (WE) <sup>(8)</sup><br>t <sub>PLZ</sub> (WE) <sup>(8)</sup>                                                                 | Delay from Write Enable to Inactive Output (HIGH Z)(See Fig. 1)                        |         | 30   | ns    |

| t <sub>PHZ</sub> (OE) <sup>(8)</sup><br>t <sub>PLZ</sub> (OE) <sup>(8)</sup>                                                                 | Delay from Output Enable to Inactive Output (HIGH Z)(See Fig. 2)                       |         | 30   | ns    |

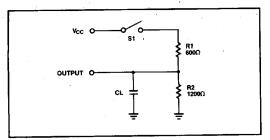

- 5) Test conditions assume signal transition times of 10 ns or less

- 6) Extended temperature operation guaranteed with 400 linear feet per minute of air flow.

- 7)  $t_{PLH}(A)$  and  $t_{PHL}(A)$  are tested with  $S_1$  closed and  $C_L = 15$  pF with both input and output timing referenced to 1.5V.

- 8) t<sub>PZH</sub>(WE), t<sub>PZH</sub>(CS<sub>1</sub>, CS<sub>2</sub>) and t<sub>PZH</sub>(OE) are measured with S<sub>1</sub> open, C<sub>L</sub> = 15 pF and with both the input and output timing referenced to 1.5V.  $t_{PZL}(\overline{WE})$ ,  $t_{PZL}(\overline{CS}_1, CS_2)$  and  $t_{PZL}(\overline{OE})$  are measured with  $S_1$  closed,  $C_L = 15$  pF and with both the input and output timing referenced to 1.5V.

- $_{\rm tpHZ}(\overline{

m WE}),\, _{\rm tpHZ}(\overline{

m CS}_1,\, {

m CS}_2)$  and  $_{\rm tpHZ}(\overline{

m OE})$  are measured with  ${

m S}_1$  open,  ${

m C}_L$  < 5 pF and are measured between the 1.5 V level on the input to the VOH - 500mV level on the output.

- $t_{PLZ}(\overrightarrow{NE}), t_{PLZ}(\overrightarrow{CS}_1, CS_2)$  and  $t_{PLZ}(\overrightarrow{OE})$  are measured with  $S_1$  closed,  $C_L < 5$  pF and are measured between the 1.5V level on the input to the Vol. +500mV level on the output.

### **SWITCHING TEST**

Test Circuits (7,8)

T-46-23-08

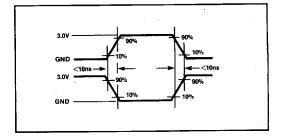

### **KEY TO DIAGRAM**

| Waveform | inputs                    | Outputs                      |

|----------|---------------------------|------------------------------|

|          | Must be steady            | Will be steady               |

| 777777   | May change from<br>H to L | Will be changing from H to L |

| 7////    | May change from<br>L to H | Will be changing from L to H |

| Waveform         | Inputs                           | Outputs                                         |

|------------------|----------------------------------|-------------------------------------------------|

| *****            | Don't care; any change permitted | Changing;<br>state unknown                      |

| <del>}}-</del> € | Does not apply                   | Center line is<br>high impedance<br>"off" state |

## **SWITCHING WAVEFORMS**

Write Mode (with OE = Low)

Figure 1.

#### Read Mode

Figure 2.

P93U422

## PERFORMANCE SEMICONDUCTOR CORPORATION

T-46-23-08 SELECTION GUIDE

(For higher performance and lower power refer to the P4C422 data sheet)

| Maximum Access | Commercial | 35 | Maximum Operating | Commercial | 80 |

|----------------|------------|----|-------------------|------------|----|

| Time (ns)      | Military   | 35 | Current (mA)      | Military   | 90 |

| \              | <u> </u>   |    |                   |            |    |

### **ORDERING INFORMATION**

| Ordering<br>Code               | Package<br>Type | Operating<br>Range |  |

|--------------------------------|-----------------|--------------------|--|

| P4C422-35PC or<br>P93U422-35PC | Plastic DIP     | Commercial         |  |

| P4C422-35DC or<br>P93U422-35DC | Ceramic DIP     | Commercial         |  |

| P4C422-35LC or<br>P93U422-35LC | LCC             | Commercial         |  |

| Ordering<br>Code                 | Package<br>Type | Operating<br>Range |

|----------------------------------|-----------------|--------------------|

| P4C422-35DMB or<br>P93U422-35DMB | Ceramic DIP     | Military           |

| P4C422-35LMB or<br>P93U422-35LMB | LCC             | Military           |