# Hitachi Single-Chip Microcomputer H8/538,

# H8/539

# Hardware Manual

2nd Edition

# Preface

The H8/538 and H8/539 are original Hitachi high-performance single-chip microcontrollers with a high-speed 16-bit H8/500 CPU core and extensive on-chip peripheral functions. They are suitable for controlling a wide range of medium-scale office and industrial equipment and consumer products.

The general-register architecture and highly orthogonal, optimized instruction set of the H8/500 CPU enable even programs coded in the high-level C language to be compiled into efficient object code.

Many of the peripheral functions needed in microcontroller application systems are provided onchip, including large RAM and ROM, a powerful set of timers, a serial interface, a high-precision A/D converter, and I/O ports. Compact, high-performance systems can be implemented easily.

The H8/538 and H8/539 are available with mask-programmable ROM for full-scale volume production, and in ZTAT<sup>TM</sup> (zero turn-around time) versions with on-chip PROM for products with frequent design changes, or for the early stages of volume production.

This document describes the H8/538 and H8/539 hardware. For further details about the H8/500 CPU instruction set, refer to the *H8/500 Series Programming Manual*.

Note: ZTAT<sup>TM</sup> is a registered trademark of Hitachi, Ltd.

# Contents

| Secti | on 1                    | Overview                       | 1  |  |

|-------|-------------------------|--------------------------------|----|--|

| 1.1   | Feature                 | s                              | 1  |  |

| 1.2   | Block I                 | Diagram                        | 5  |  |

| 1.3   | Pin Des                 | criptions                      | 7  |  |

|       | 1.3.1                   | Pin Arrangement                | 7  |  |

|       | 1.3.2                   | Pin Functions                  | 9  |  |

| Secti | on 2                    | Operating Modes                | 21 |  |

| 2.1   | Overvie                 | 2W                             | 21 |  |

|       | 2.1.1                   | Selection of Operating Mode    | 21 |  |

|       | 2.1.2                   | Register Configuration         | 22 |  |

| 2.2   | Mode C                  | Control Register               | 23 |  |

| 2.3   | Operati                 | ng Mode Descriptions           | 24 |  |

|       | 2.3.1                   | Mode 1 (Expanded Minimum Mode) | 24 |  |

|       | 2.3.2                   | Mode 2 (Expanded Minimum Mode) | 24 |  |

|       | 2.3.3                   | Mode 3 (Expanded Maximum Mode) | 24 |  |

|       | 2.3.4                   | Mode 4 (Expanded Maximum Mode) | 24 |  |

|       | 2.3.5                   | Modes 5 and 6                  | 24 |  |

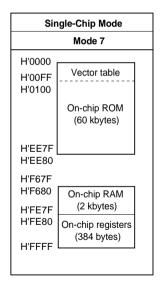

|       | 2.3.6                   | Mode 7 (Single-Chip Mode)      | 24 |  |

| 2.4   | Pin Fun                 | ctions in Each Operating Mode  | 25 |  |

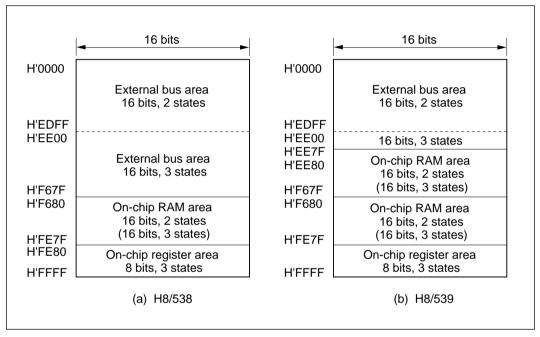

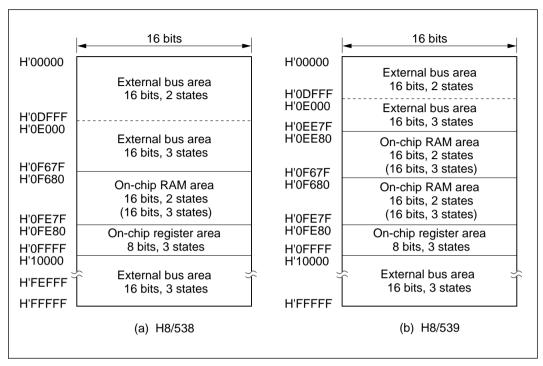

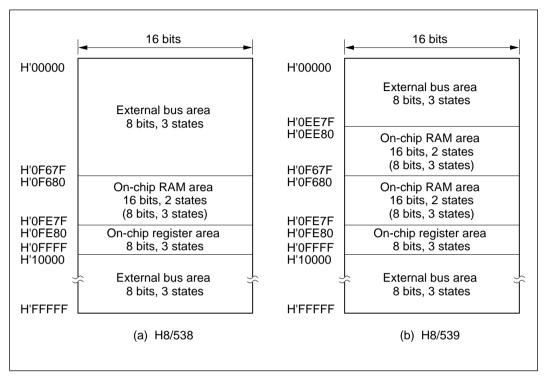

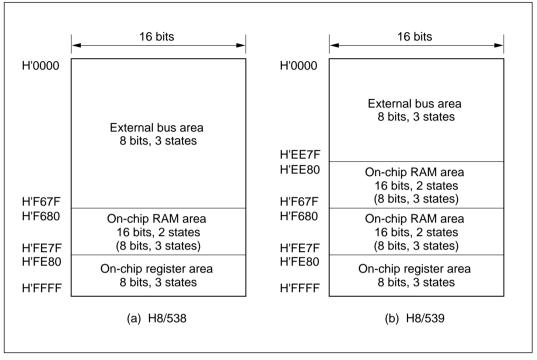

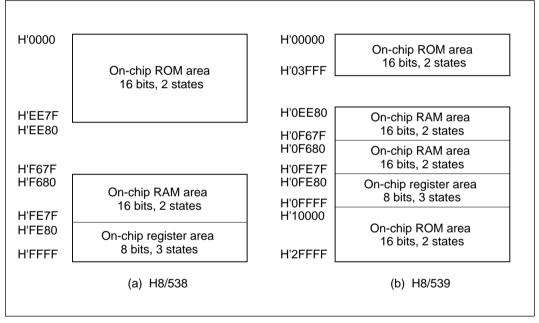

| 2.5   | Memory Map in Each Mode |                                |    |  |

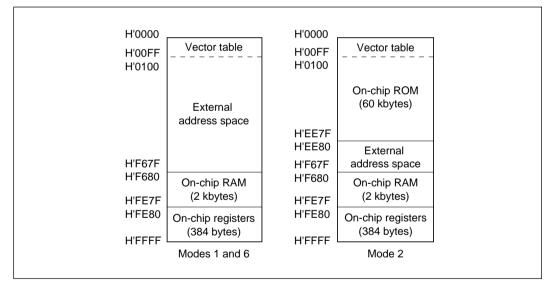

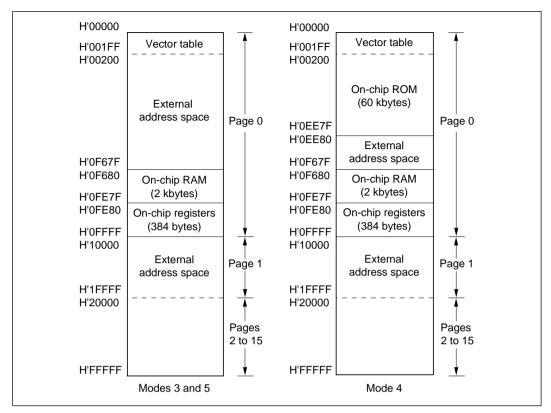

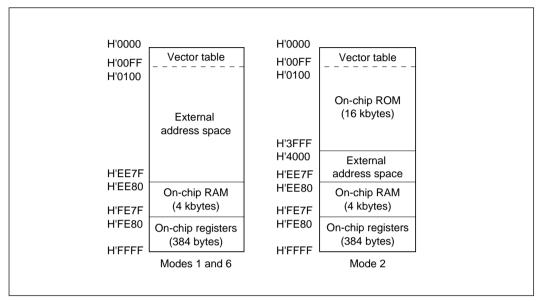

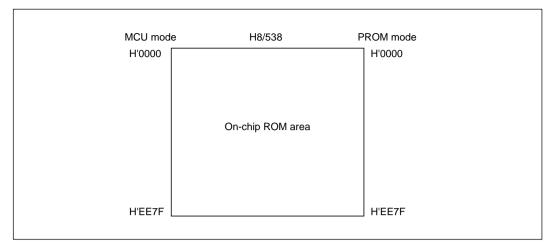

|       | 2.5.1                   | H8/538 Memory Maps             | 26 |  |

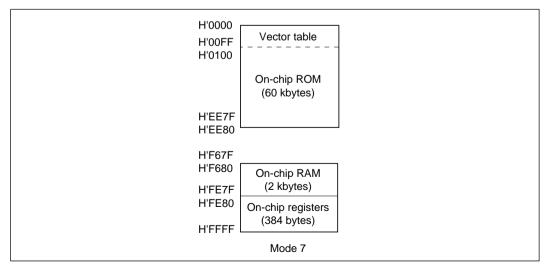

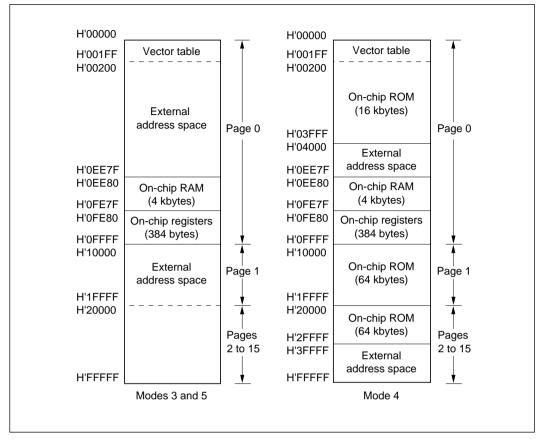

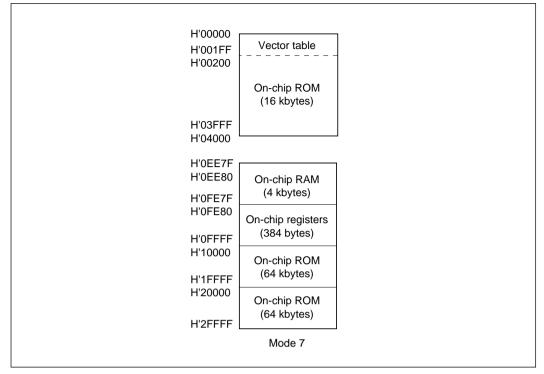

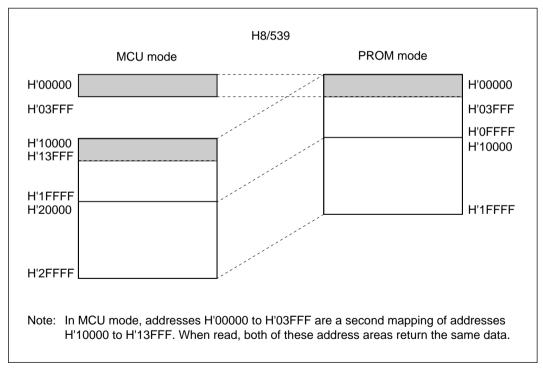

|       | 2.5.2                   | H8/539 Memory Maps             | 28 |  |

| Secti | on 3                    | CPU                            | 31 |  |

| 3.1   | Overvie                 | 2W                             | 31 |  |

|       | 3.1.1                   | Features                       | 31 |  |

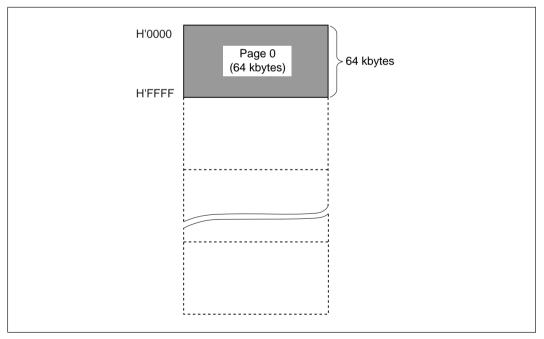

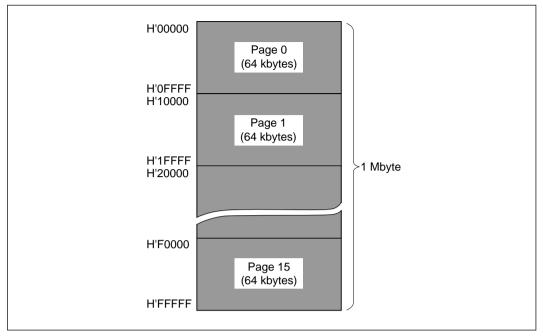

|       | 3.1.2                   | Address Space                  | 32 |  |

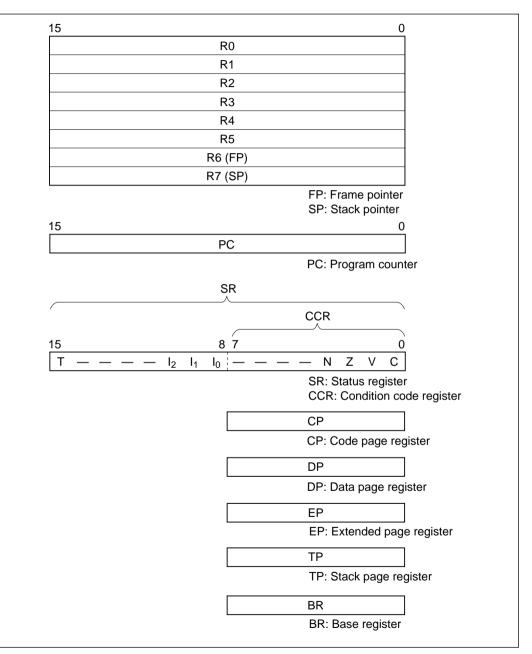

|       | 3.1.3                   | Programming Model              | 34 |  |

| 3.2   | General                 | Registers                      | 35 |  |

|       | 3.2.1                   | Overview                       | 35 |  |

|       | 3.2.2                   | Register Configuration         | 35 |  |

|       | 3.2.3                   | Stack Pointer                  | 35 |  |

|       | 3.2.4                   | Frame Pointer                  | 35 |  |

| 3.3   | Control                 | Registers                      | 36 |  |

|       | 3.3.1                   | Overview                       | 36 |  |

|       | 3.3.2                   | Register Configuration         | 36 |  |

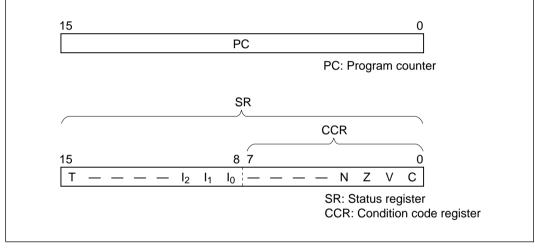

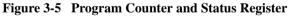

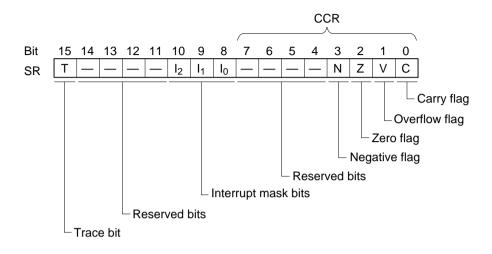

|       | 3.3.3                   | Program Counter                | 36 |  |

|       | 3.3.4                   | Status Register                |    |  |

|       |                         | -                              |    |  |

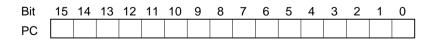

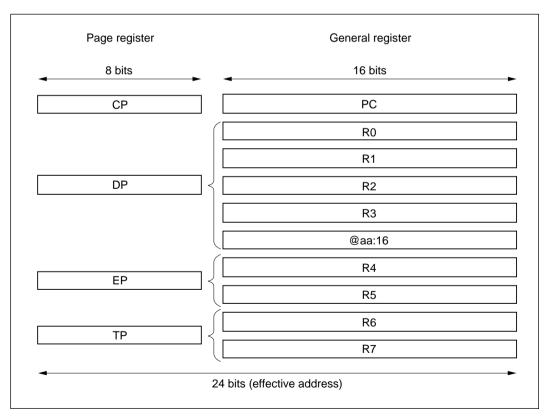

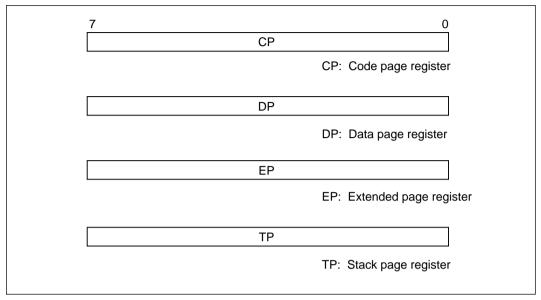

| 3.4   | Page R  | egisters                                     | 40 |

|-------|---------|----------------------------------------------|----|

|       | 3.4.1   | Overview                                     | 40 |

|       | 3.4.2   | Register Configuration                       | 41 |

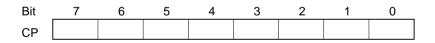

|       | 3.4.3   | Code Page Register                           | 41 |

|       | 3.4.4   | Data Page Register                           | 42 |

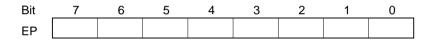

|       | 3.4.5   | Extended Page Register                       |    |

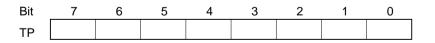

|       | 3.4.6   | Stack Page Register                          | 42 |

| 3.5   | Base R  | egister                                      | 43 |

|       | 3.5.1   | Overview                                     | 43 |

|       | 3.5.2   | Register Configuration                       | 43 |

| 3.6   | Data Fo | ormats                                       | 44 |

|       | 3.6.1   | Data Formats in General Registers            | 44 |

|       | 3.6.2   | Data Formats in Memory                       | 45 |

|       | 3.6.3   | Stack Data Formats                           | 45 |

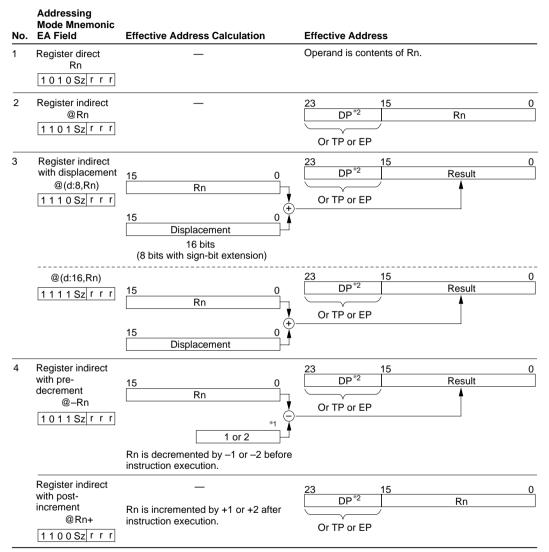

| 3.7   | Addres  | sing Modes and Effective Address Calculation | 46 |

|       | 3.7.1   | Addressing Modes                             | 46 |

|       | 3.7.2   | Effective Address Calculation                |    |

| 3.8   | Operati | ing Modes                                    | 52 |

|       | 3.8.1   | Minimum Mode                                 | 52 |

|       | 3.8.2   | Maximum Mode                                 | 52 |

| 3.9   | Basic ( | Dperational Timing                           | 52 |

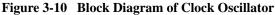

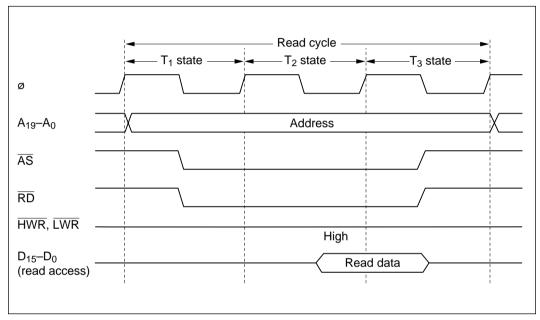

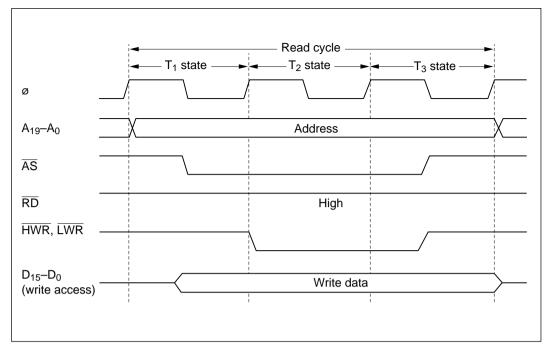

|       | 3.9.1   | Overview                                     | 53 |

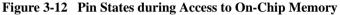

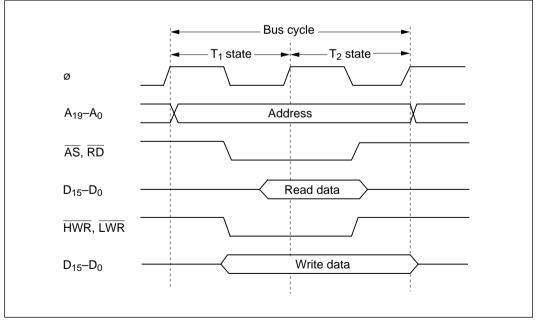

|       | 3.9.2   | Access to On-Chip Memory                     | 53 |

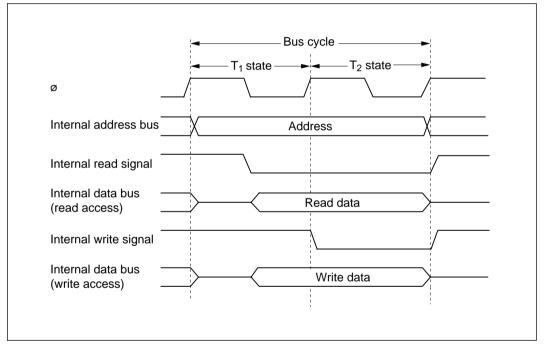

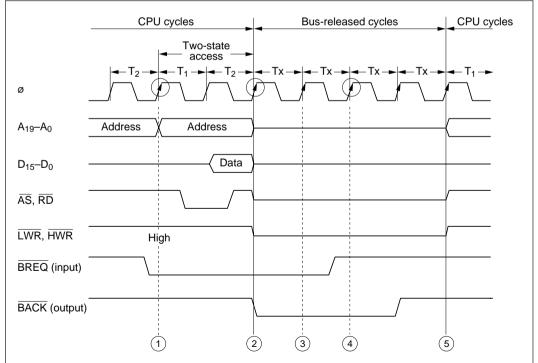

|       | 3.9.3   | Access to Two-State-Access Address Space     |    |

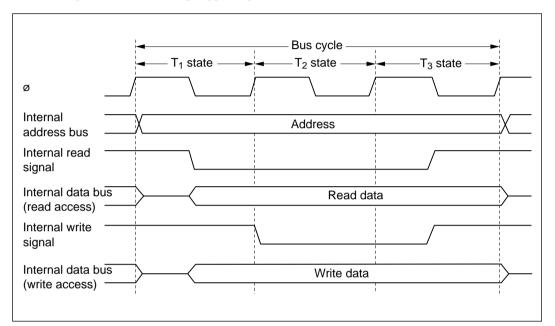

|       | 3.9.4   | Access to On-Chip Supporting Modules         | 55 |

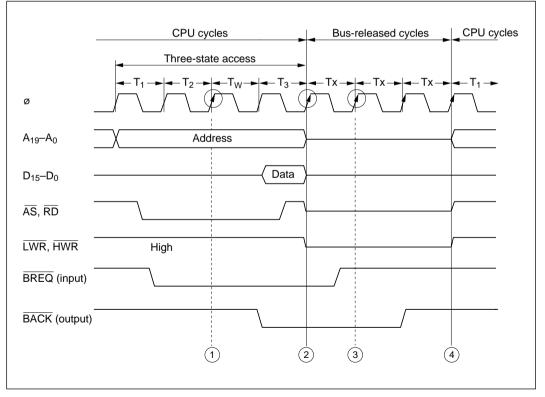

|       | 3.9.5   | Access to Three-State-Access Address Space   |    |

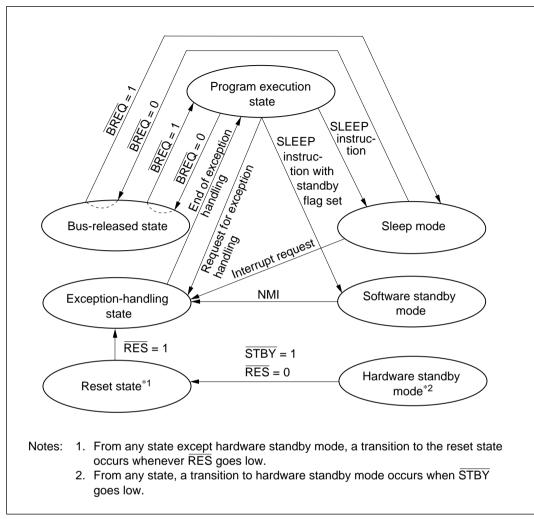

| 3.10  | CPU St  | tates                                        | 58 |

|       | 3.10.1  | Overview                                     | 58 |

|       | 3.10.2  | Program Execution State                      | 59 |

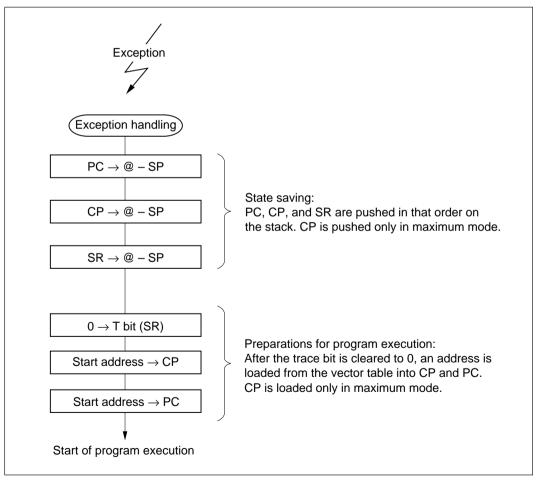

|       | 3.10.3  | Exception-Handling State                     |    |

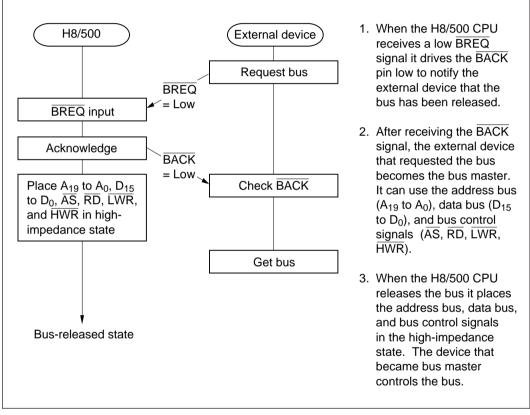

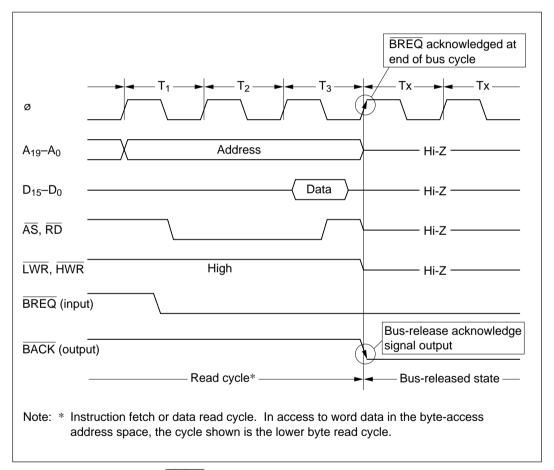

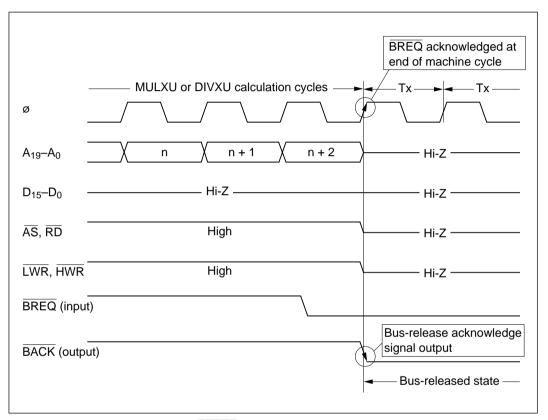

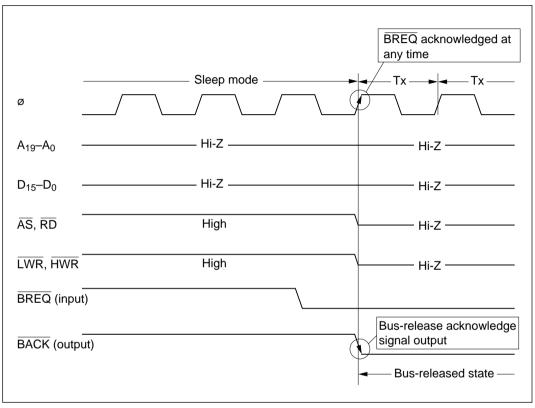

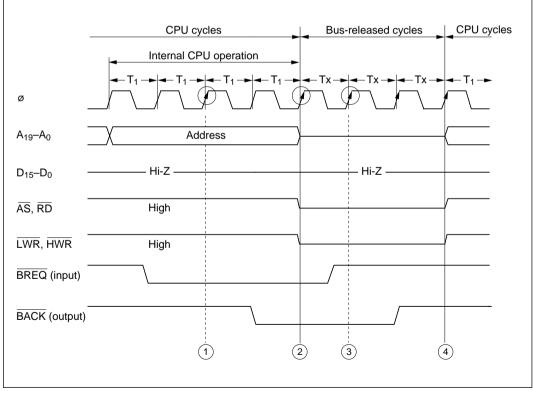

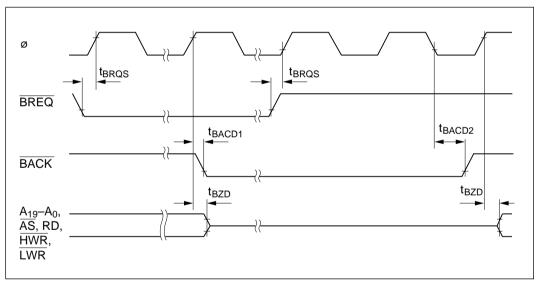

|       | 3.10.4  | Bus-Released State                           | 60 |

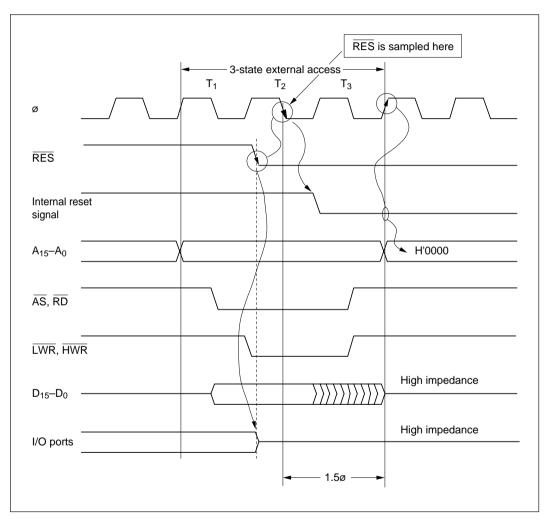

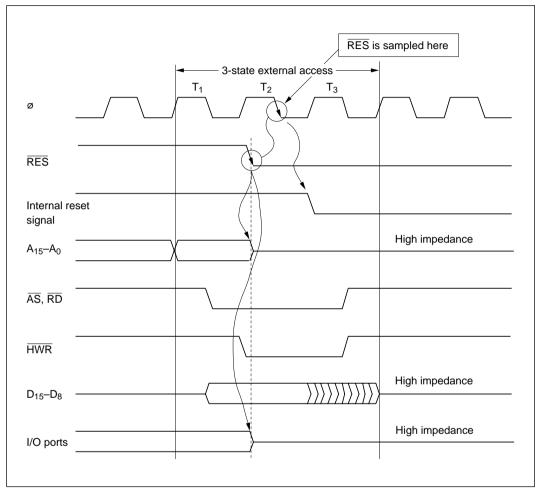

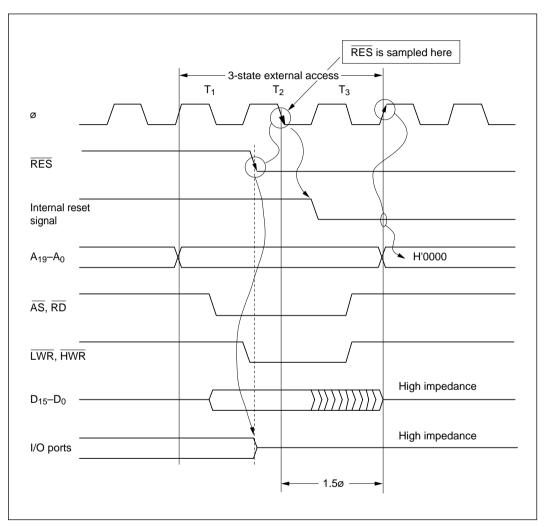

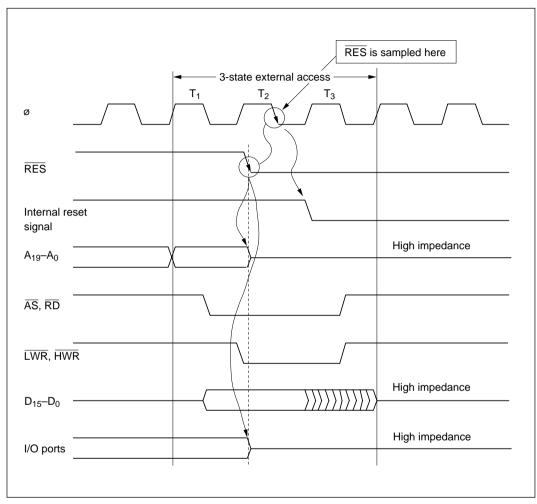

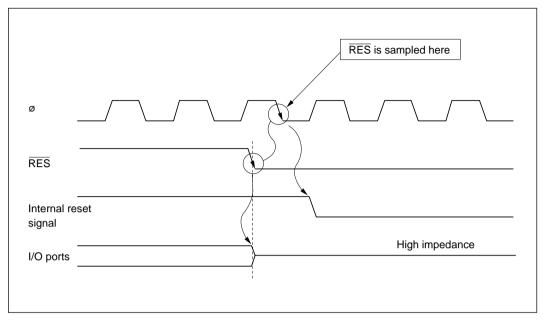

|       | 3.10.5  | Reset State                                  | 68 |

|       | 3.10.6  | Power-Down State                             | 68 |

| Secti | on 4    | Exception Handling                           | 69 |

| 4.1   |         | ew                                           | 69 |

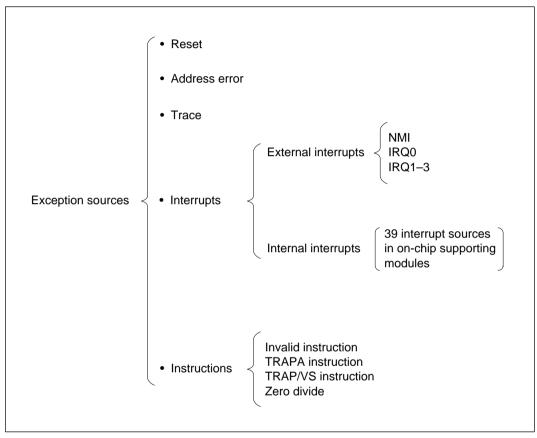

| 4.1   | 4.1.1   | Exception Handling Types and Priority        | 69 |

|       | 4.1.2   | Exception Handling Operation                 | 70 |

|       | 4.1.2   | Exception Franching Operation                | 70 |

| 4.2   | Reset   | Exception sources and vector rable           | 73 |

| т.2   | 4.2.1   | Overview                                     | 73 |

|       | T.4.1   | 0 101 11017                                  | 15 |

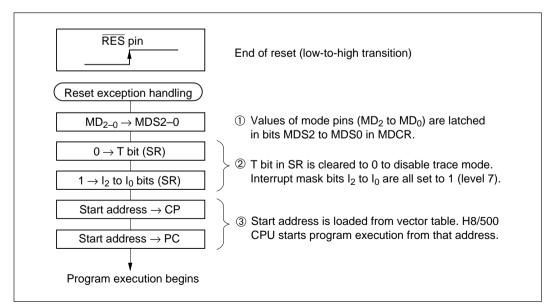

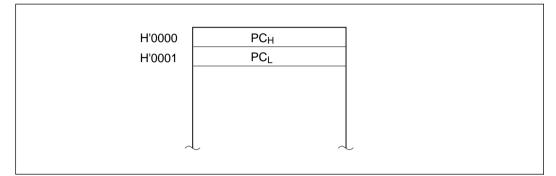

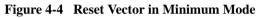

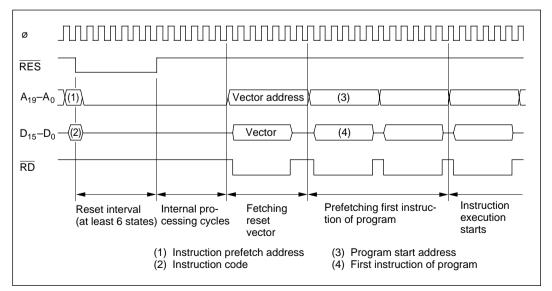

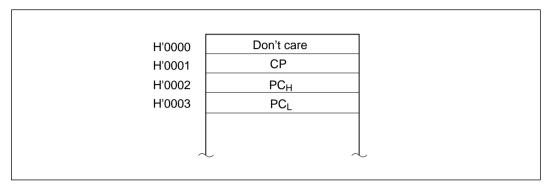

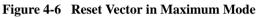

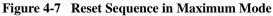

|       | 4.2.2    | Reset Sequence                                                     | 73 |

|-------|----------|--------------------------------------------------------------------|----|

|       | 4.2.3    | Interrupts after Reset                                             | 76 |

| 4.3   | Addres   | s Error                                                            | 76 |

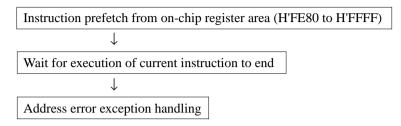

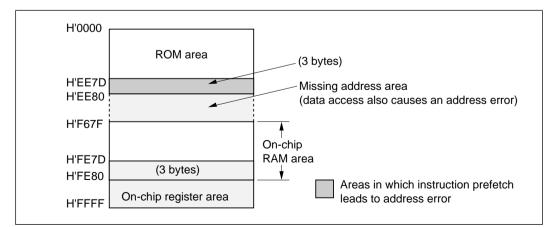

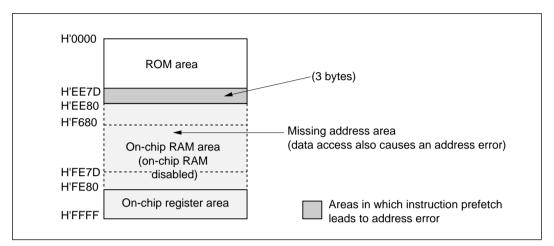

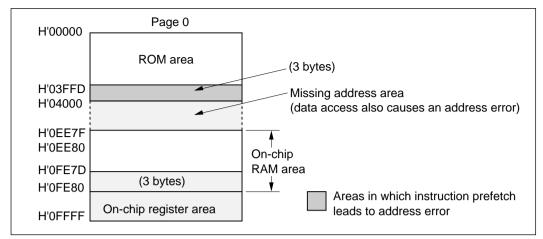

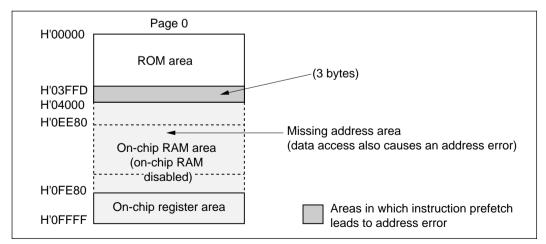

|       | 4.3.1    | Address Error in Instruction Prefetch                              | 77 |

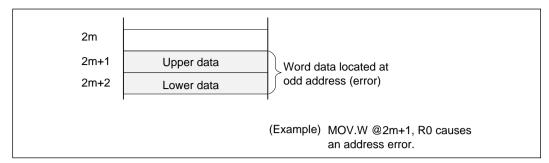

|       | 4.3.2    | Address Error in Word Data Access                                  | 77 |

|       | 4.3.3    | Address Error in Single-Chip Mode                                  | 78 |

| 4.4   | Trace    |                                                                    | 81 |

| 4.5   | Interru  | pts                                                                | 81 |

| 4.6   | Invalid  | Instructions                                                       | 82 |

| 4.7   | Trap In  | structions and Zero Divide                                         | 83 |

| 4.8   | Cases i  | n which Exception Handling is Deferred                             | 84 |

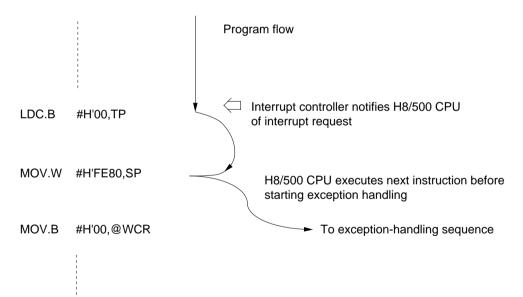

|       | 4.8.1    | Instructions that Disable Exception Handling                       | 84 |

|       | 4.8.2    | Disabling of Exceptions Immediately after a Reset                  | 85 |

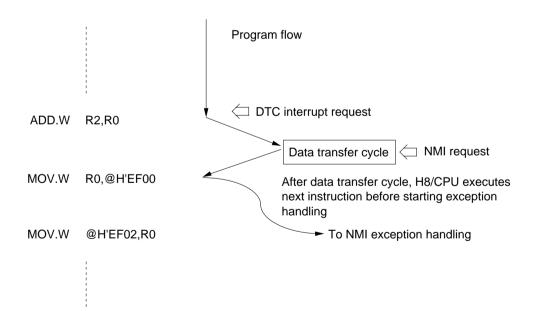

|       | 4.8.3    | Disabling of Interrupts after a Data Transfer Cycle                | 85 |

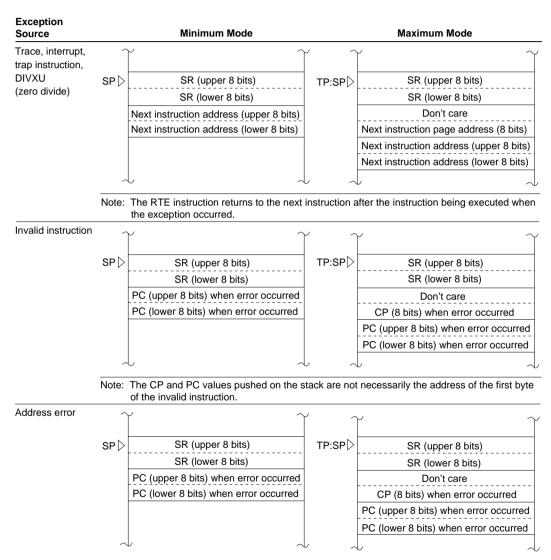

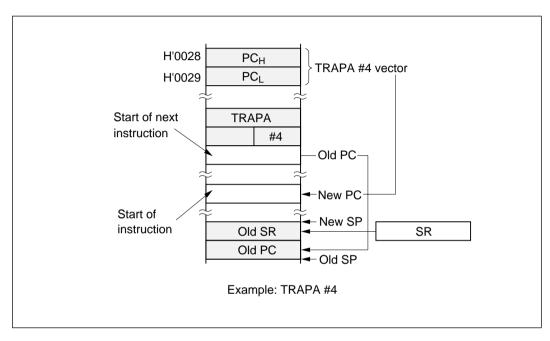

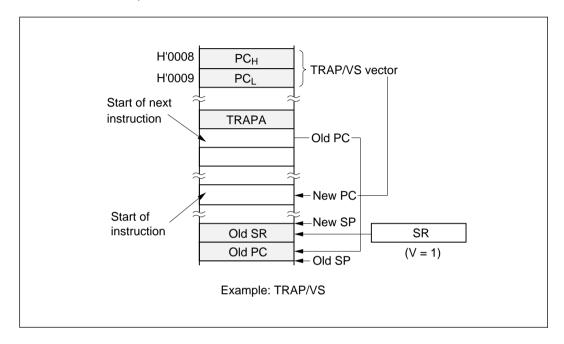

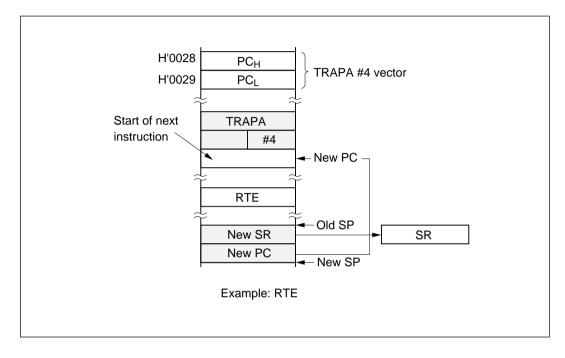

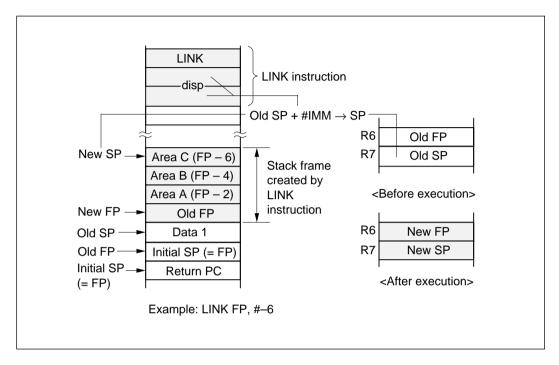

| 4.9   | Stack S  | Status after Completion of Exception Handling                      | 86 |

|       | 4.9.1    | PC Value Pushed on Stack for Trace, Interrupts, Trap Instructions, |    |

|       |          | and Zero Divide Exceptions                                         | 87 |

|       | 4.9.2    | PC Value Pushed on Stack for Address Error and Invalid Instruction | 87 |

| 4.10  | Notes of | on Use of the Stack                                                | 87 |

|       |          |                                                                    |    |

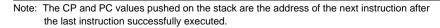

| Secti | on 5     | H8 Multiplier (H8/539 Only)                                        | 89 |

| 5.1   | Overvi   | ew                                                                 | 89 |

|       | 5.1.1    | Features                                                           | 89 |

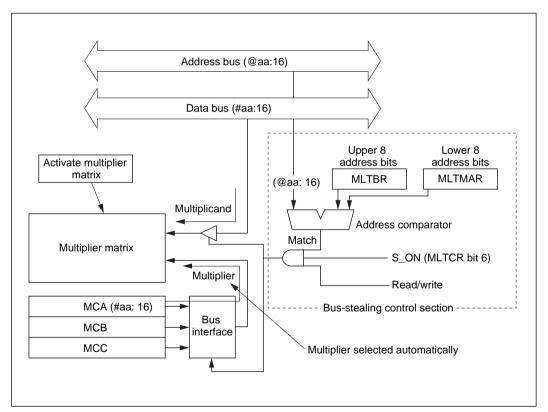

|       | 5.1.2    | Block Diagram                                                      | 90 |

|       | 5.1.3    | Register Configuration                                             | 91 |

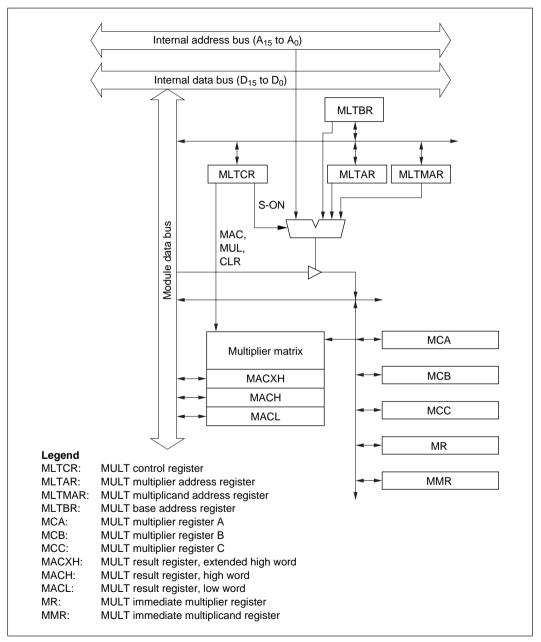

| 5.2   | Registe  | er Descriptions                                                    | 92 |

|       | 5.2.1    | MULT Control Register                                              | 92 |

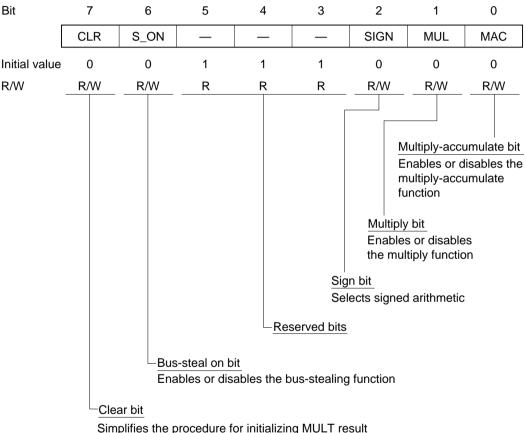

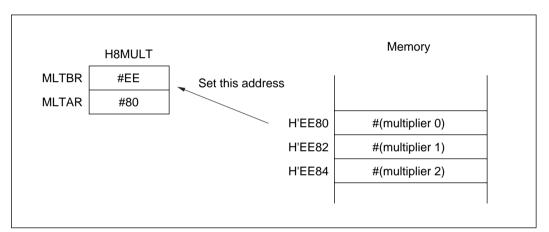

|       | 5.2.2    | MULT Base Address Register                                         | 94 |

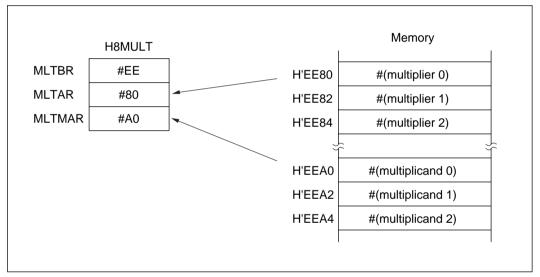

|       | 5.2.3    | MULT Multiplier Address Register                                   | 94 |

|       | 5.2.4    | MULT Multiplicand Address Register                                 | 94 |

|       | 5.2.5    | MULT Multiplier Register A                                         | 95 |

|       | 5.2.6    | MULT Multiplier Register B                                         | 95 |

|       | 5.2.7    | MULT Multiplier Register C                                         | 95 |

|       | 5.2.8    | MULT Immediate Multiplier Register                                 | 96 |

|       | 5.2.9    | MULT Immediate Multiplicand Register                               | 96 |

|       | 5.2.10   | MULT Result Register, Extended High Word                           | 97 |

|       | 5.2.11   | MULT Result Register, High Word                                    | 97 |

|       | 5.2.12   | MULT Result Register, Low Word                                     | 97 |

| 5.3   | Operati  | ion                                                                | 98 |

|       | 5.3.1    | Initialization of MULT Result Registers                            | 98 |

|       | 5.3.2    | Writing to MULT Multiplier Registers                               | 99 |

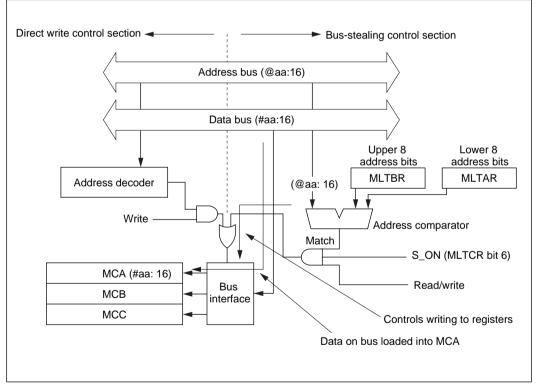

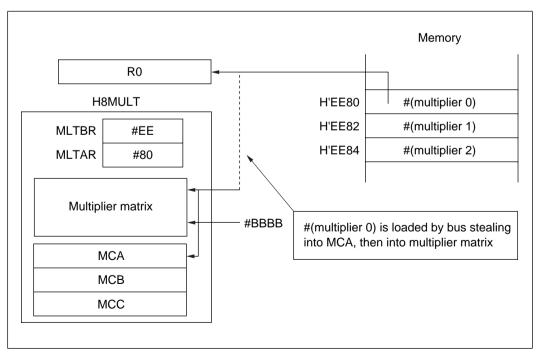

|       | 5.3.3    | Bus-Stealing Function                      | 99  |

|-------|----------|--------------------------------------------|-----|

|       | 5.3.4    | Multiply and Multiply-Accumulate Functions | 102 |

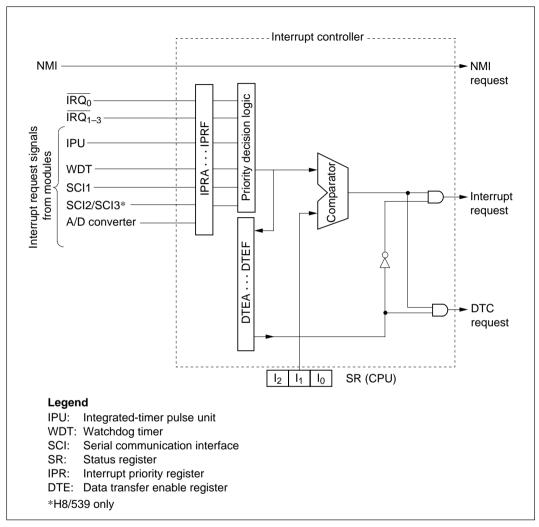

| Secti | on 6     | Interrupt Controller                       | 111 |

| 6.1   |          | ew                                         |     |

| 0.1   | 6.1.1    | Features                                   |     |

|       | 6.1.2    | Block Diagram                              |     |

|       | 6.1.3    | Register Configuration                     |     |

| 6.2   |          | pt Sources                                 |     |

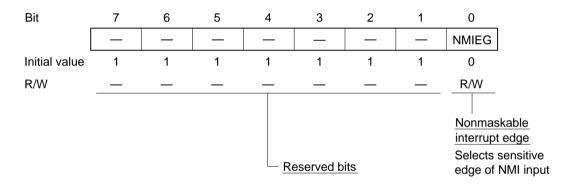

| 0.2   | 6.2.1    | NMI                                        |     |

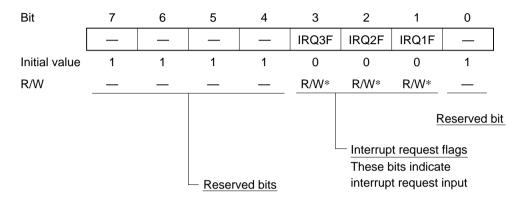

|       | 6.2.2    | IRQ0                                       |     |

|       | 6.2.3    | IRQ1 to IRQ3                               |     |

|       | 6.2.4    | Internal Interrupts                        |     |

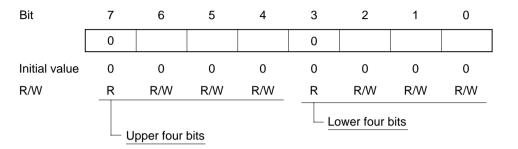

| 6.3   |          | r Descriptions                             |     |

| 0.5   | 6.3.1    | Interrupt Priority Registers A to F        |     |

|       | 6.3.2    | Timing of Priority Changes                 |     |

| 6.4   |          | pt Operations                              |     |

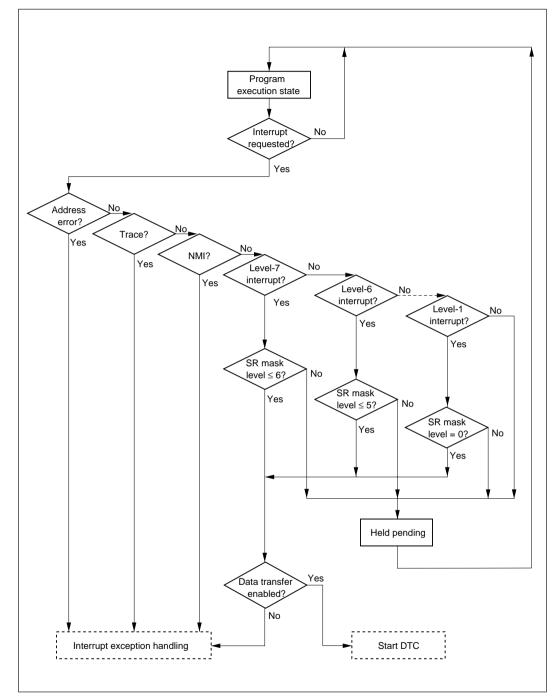

| 0.4   | 6.4.1    | Operations up to Interrupt Acceptance      |     |

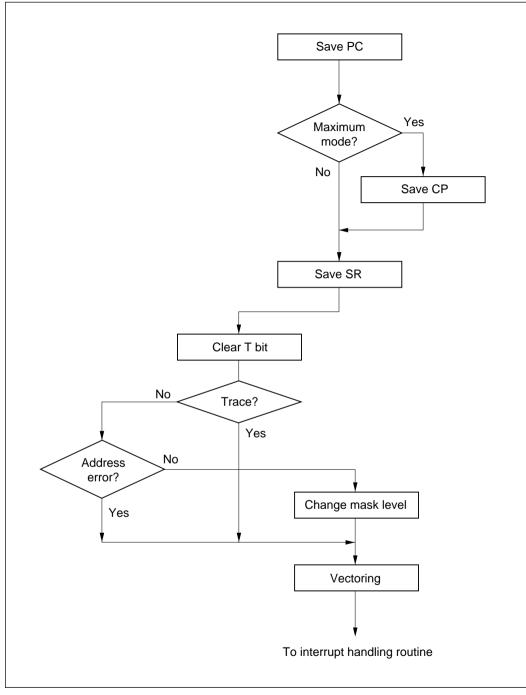

|       | 6.4.2    | Interrupt Exception Handling               |     |

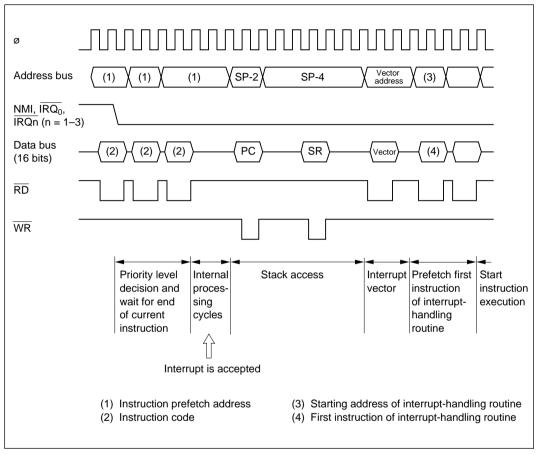

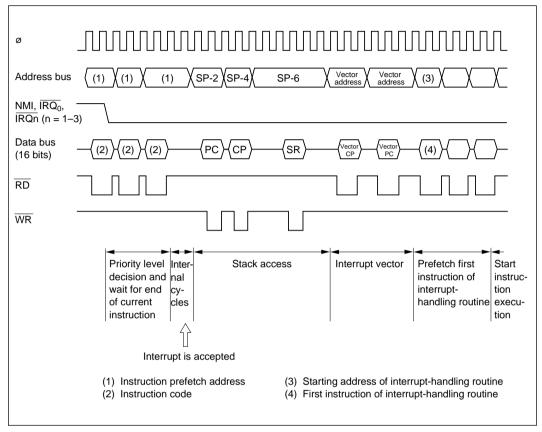

|       | 6.4.3    | Interrupt Exception Handling Sequence      |     |

|       | 6.4.4    | Stack after Interrupt Exception Handling   |     |

| 6.5   |          | pts during DTC Operation                   |     |

| 6.6   | -        | pt Response Time                           |     |

| 0.0   | Interruj |                                            | 152 |

| Secti | on 7     | Data Transfer Controller                   | 135 |

| 7.1   | Overvie  | ew                                         | 135 |

|       | 7.1.1    | Features                                   | 135 |

|       | 7.1.2    | Block Diagram                              | 136 |

|       | 7.1.3    | Register Configuration                     | 137 |

| 7.2   | Registe  | r Descriptions                             | 138 |

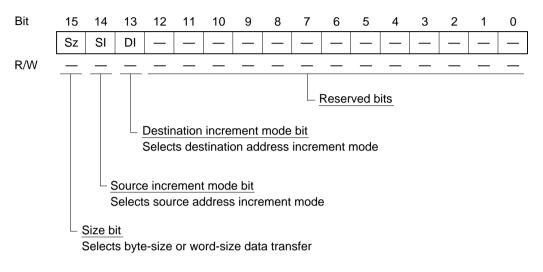

|       | 7.2.1    | Data Transfer Mode Register                |     |

|       | 7.2.2    | Data Transfer Source Address Register      |     |

|       | 7.2.3    | Data Transfer Destination Address Register |     |

|       | 7.2.4    | Data Transfer Count Register               | 140 |

|       | 7.2.5    | Data Transfer Enable Registers A to F      | 140 |

|       | 7.2.6    | Note on Timing of DTE Modifications        |     |

| 7.3   | Operati  | ion                                        |     |

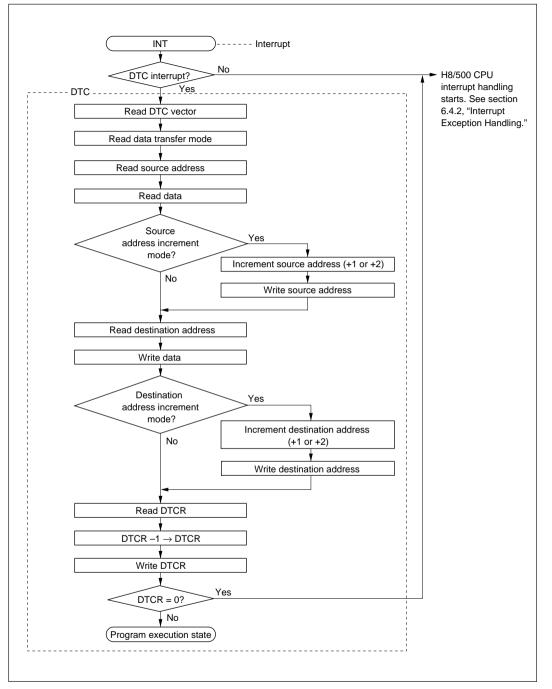

|       | 7.3.1    | DTC Operations                             |     |

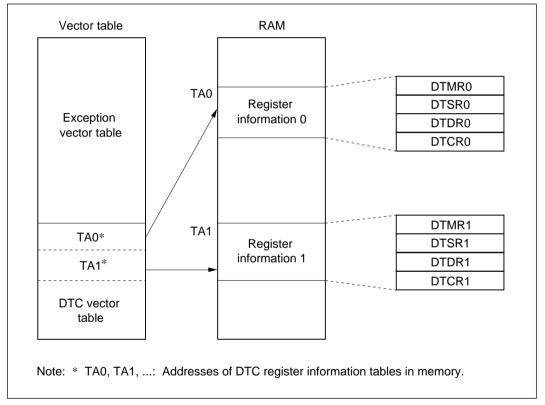

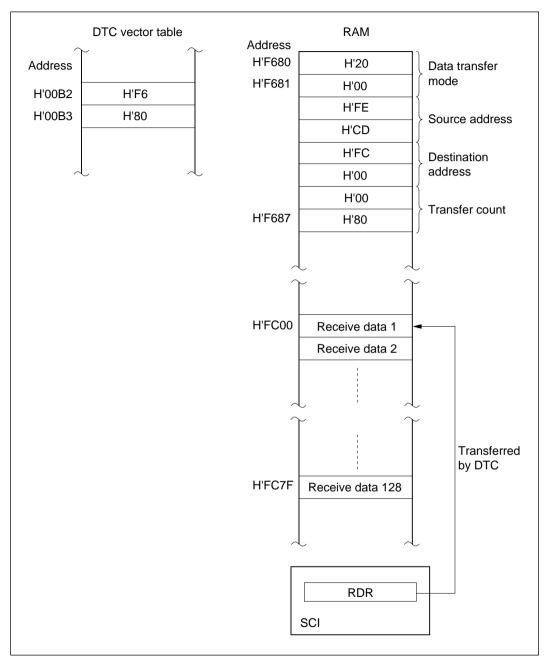

|       | 7.3.2    | DTC Vector Table                           |     |

|       | 7.3.3    | Location of Register Information in Memory | 149 |

|       | 7.3.4    | Number of States per Data Transfer         |     |

| 7.4       | Procedu  | re for Using DTC               | 152 |

|-----------|----------|--------------------------------|-----|

| 7.5       | Exampl   | e                              | 153 |

|           |          |                                |     |

| Section 8 |          | Wait-State Controller          | 157 |

| 8.1       | Overvie  | 2W                             | 157 |

|           | 8.1.1    | Features                       | 157 |

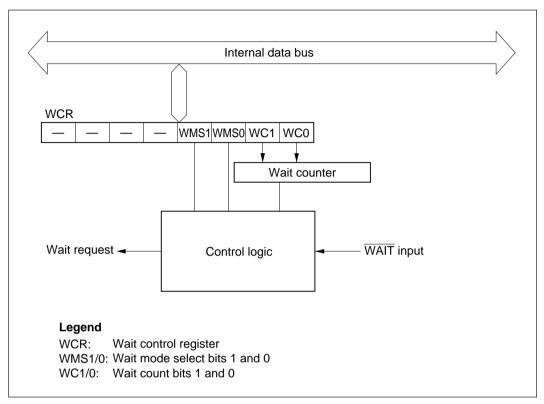

|           | 8.1.2    | Block Diagram                  | 158 |

|           | 8.1.3    | Register Configuration         | 158 |

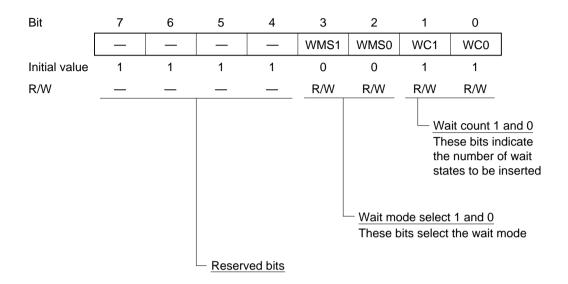

| 8.2       | Wait Co  | ontrol Register                | 159 |

| 8.3       | Operati  | on                             | 160 |

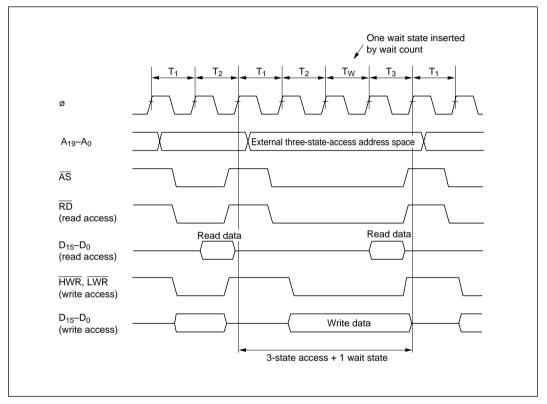

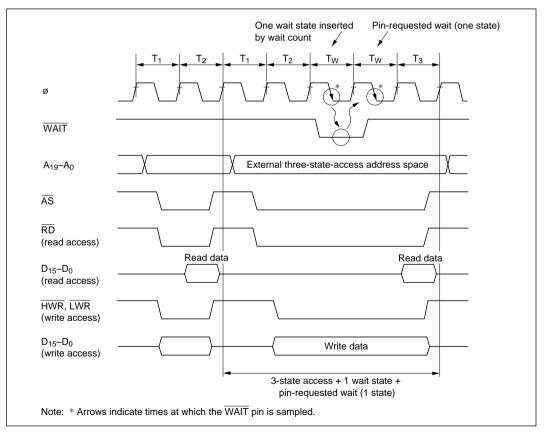

|           | 8.3.1    | Programmable Wait Mode         | 161 |

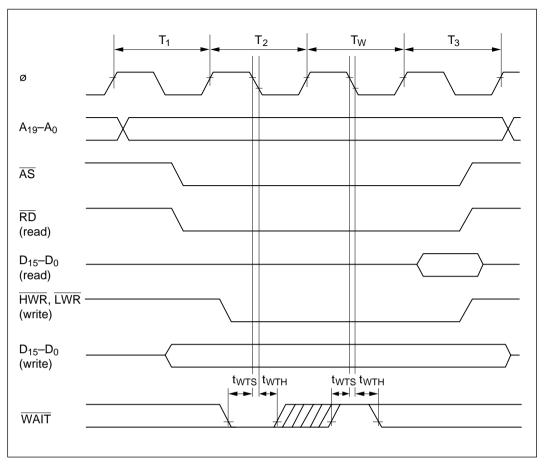

|           | 8.3.2    | Pin Wait Mode                  |     |

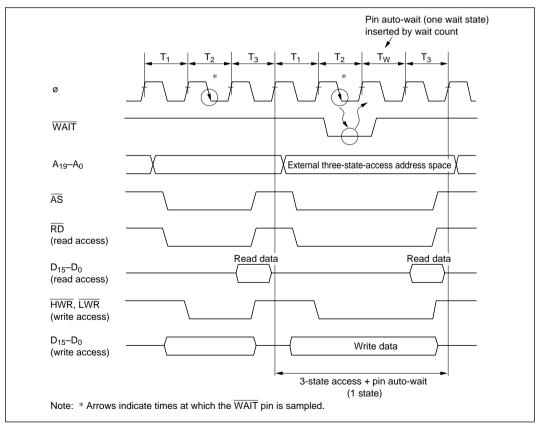

|           | 8.3.3    | Pin Auto-Wait Mode             |     |

|           |          |                                |     |

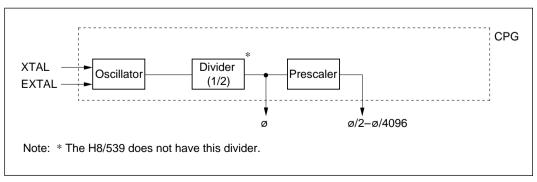

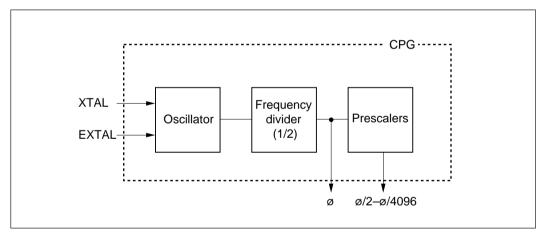

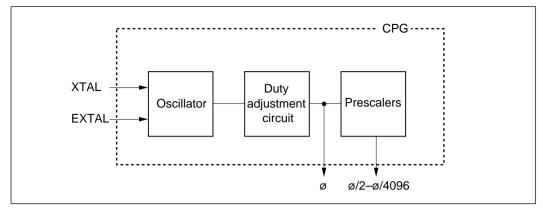

| Section   | on 9     | Clock Pulse Generator          | 165 |

| 9.1       | Overvie  | 2W                             |     |

|           | 9.1.1    | Block Diagram                  | 165 |

| 9.2       | Oscillat | or Circuit                     |     |

|           | 9.2.1    | Connecting a Crystal Resonator |     |

|           | 9.2.2    | External Clock Input           |     |

| 9.3       |          | Clock Divider                  |     |

| 9.4       | 2        | djustment Circuit              |     |

|           | ,        | -j                             |     |

| Section   | on 10    | I/O Ports                      | 171 |

| 10.1      | Overvie  | 2W                             |     |

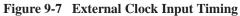

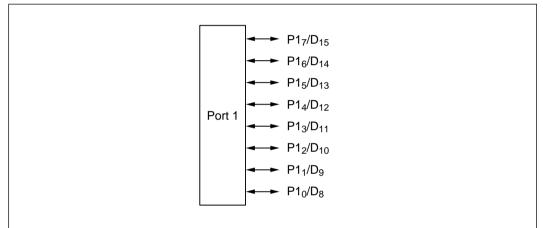

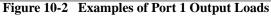

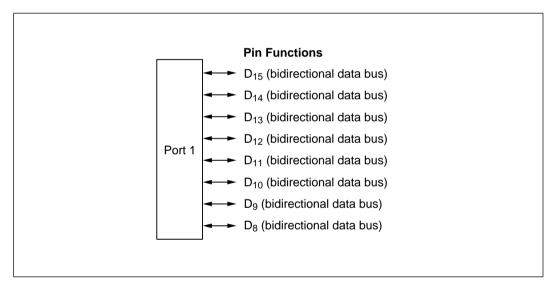

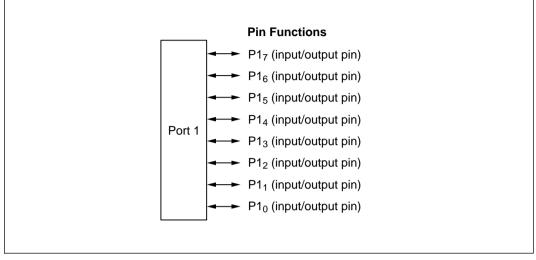

| 10.2      | Port 1   |                                | 176 |

|           | 10.2.1   | Overview                       |     |

|           | 10.2.2   | Register Descriptions          | 177 |

|           | 10.2.3   | Pin Functions in Each Mode     |     |

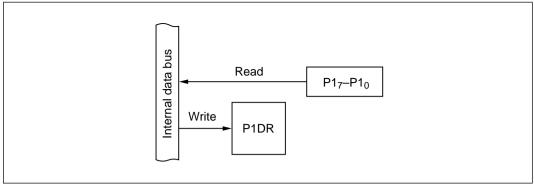

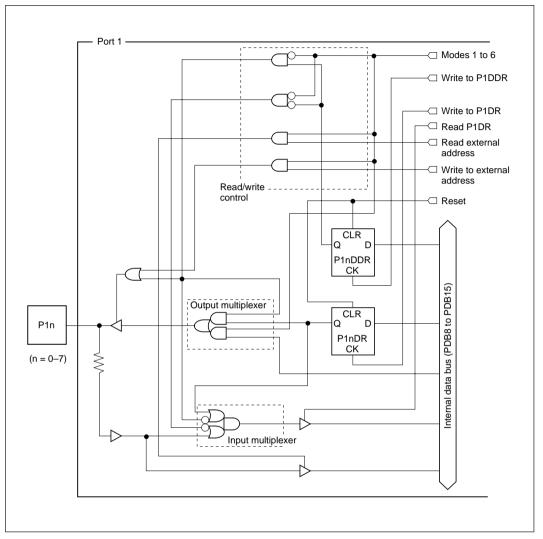

|           | 10.2.4   | Port 1 Read/Write Operations   |     |

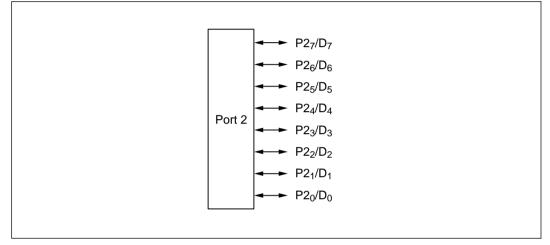

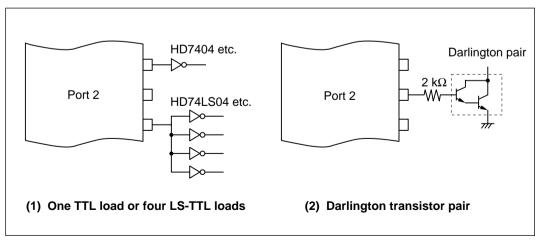

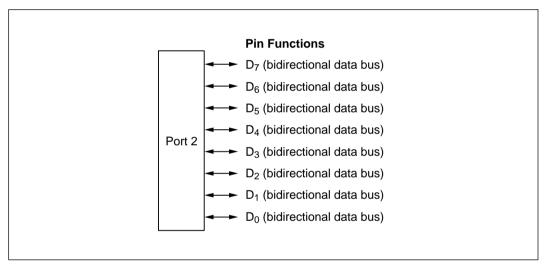

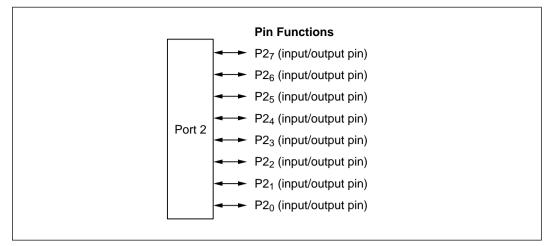

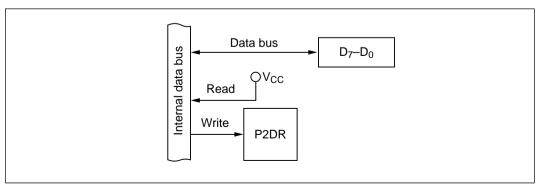

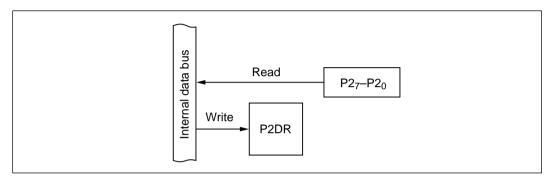

| 10.3      | Port 2   |                                |     |

|           | 10.3.1   | Overview                       |     |

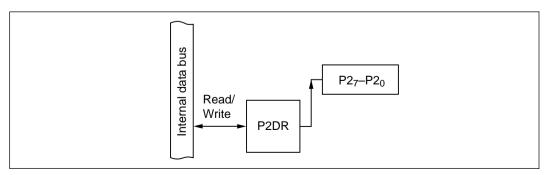

|           | 10.3.2   | Register Descriptions          |     |

|           | 10.3.3   | Pin Functions in Each Mode     |     |

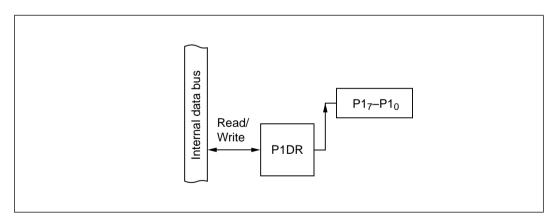

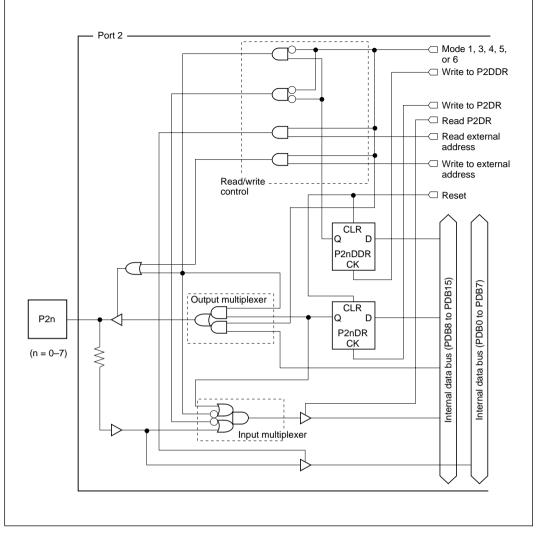

|           | 10.3.4   | Port 2 Read/Write Operations   |     |

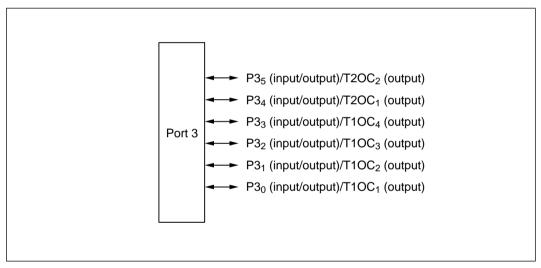

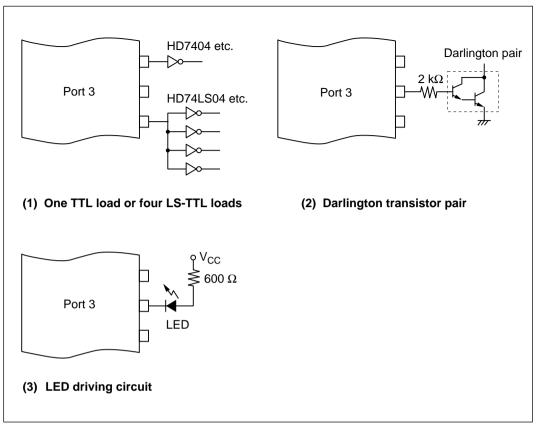

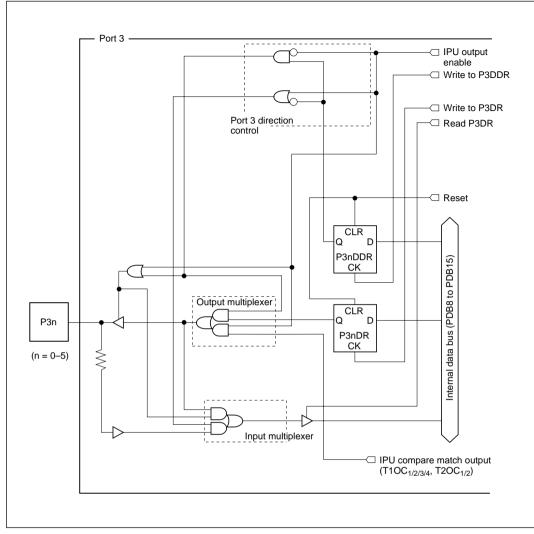

| 10.4      | Port 3   |                                |     |

| 10.1      | 10.4.1   | Overview                       |     |

|           | 10.4.2   | Register Descriptions          |     |

|           | 10.4.2   | Pin Functions in Each Mode     |     |

|           | 10.4.4   | Port 3 Read/Write Operations   |     |

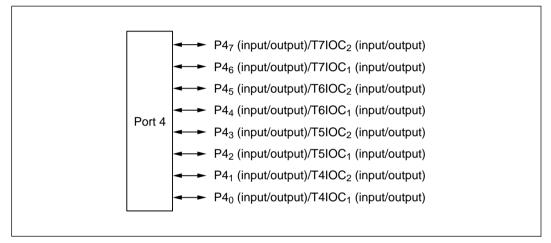

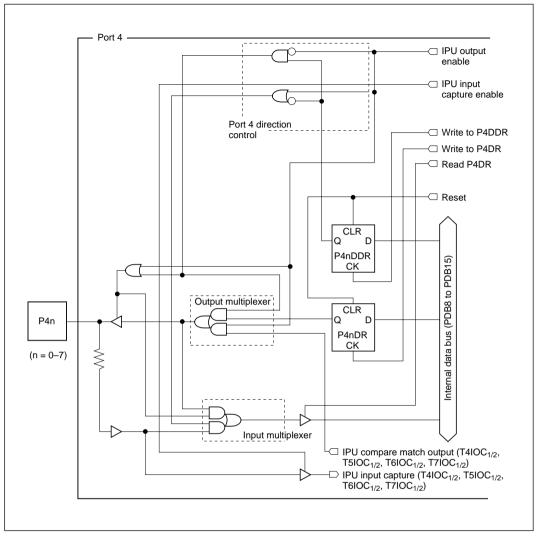

| 10.5      | Port 4   | Tore 5 Read while Operations   |     |

| 10.5      | I UIL T  |                                | 1/2 |

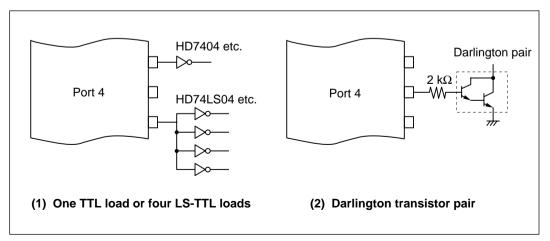

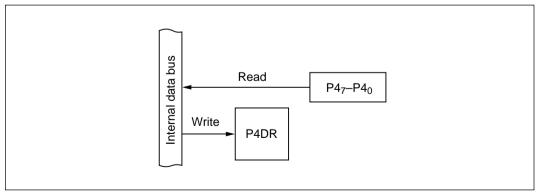

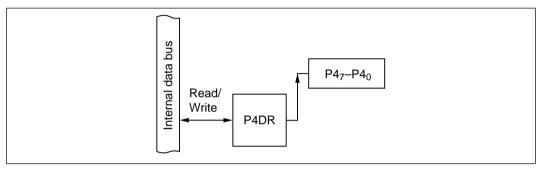

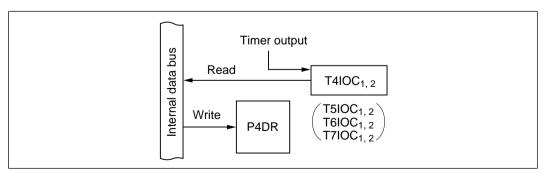

|       | 10.5.1  | Overview                     | 192 |

|-------|---------|------------------------------|-----|

|       | 10.5.2  | Register Descriptions        | 193 |

|       | 10.5.3  | Pin Functions in Each Mode   | 194 |

|       | 10.5.4  | Port 4 Read/Write Operations | 194 |

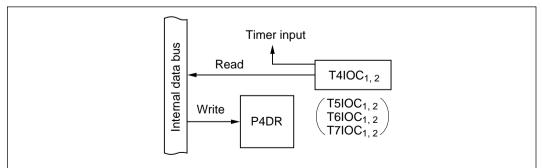

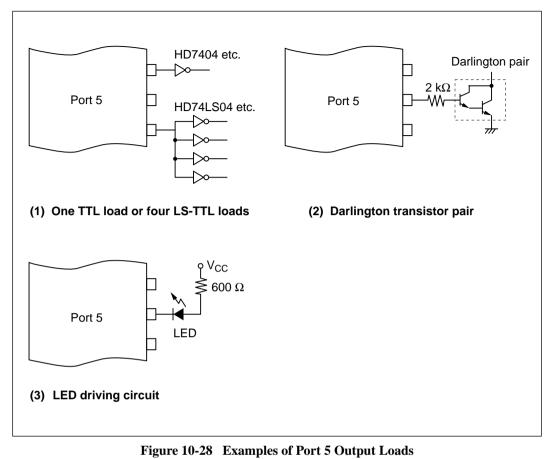

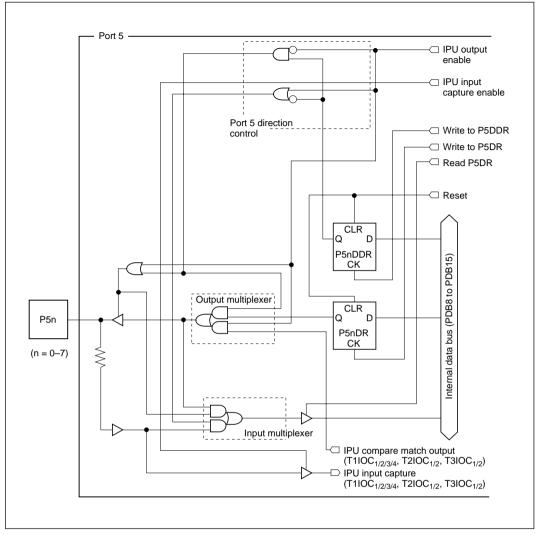

| 10.6  | Port 5  |                              | 197 |

|       | 10.6.1  | Overview                     | 197 |

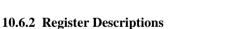

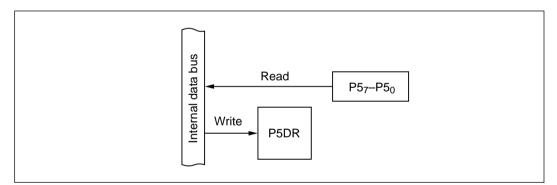

|       | 10.6.2  | Register Descriptions        | 198 |

|       | 10.6.3  | Pin Functions in Each Mode   | 199 |

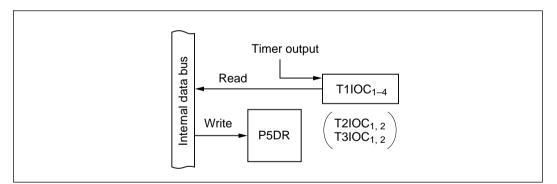

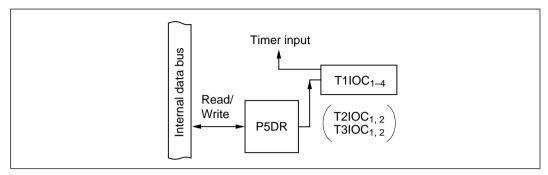

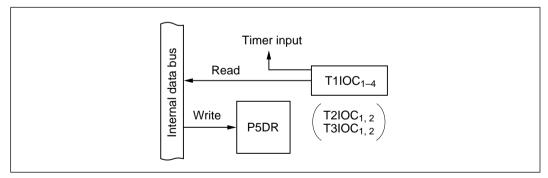

|       | 10.6.4  | Port 5 Read/Write Operations | 200 |

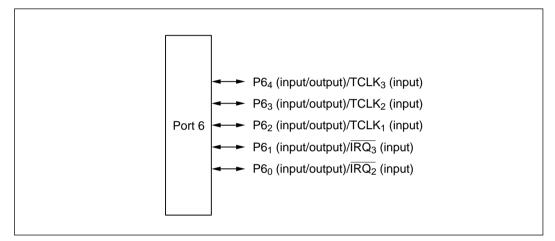

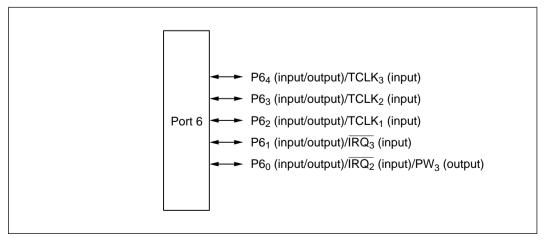

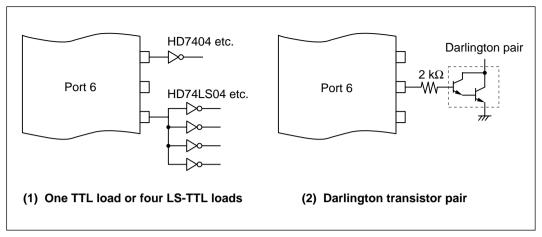

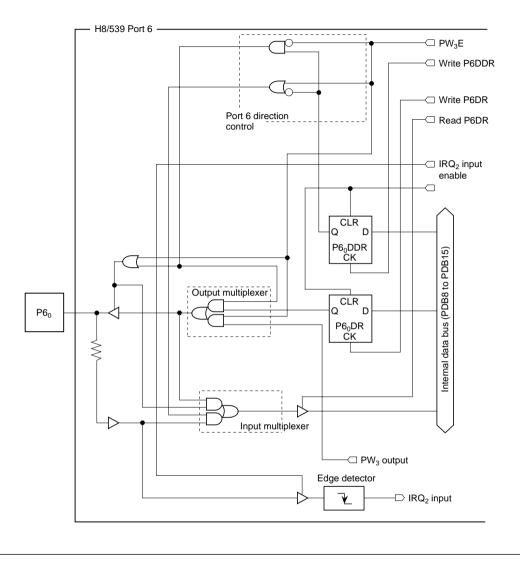

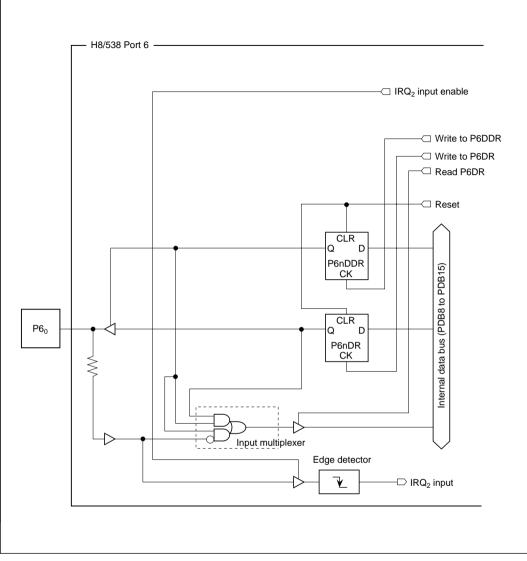

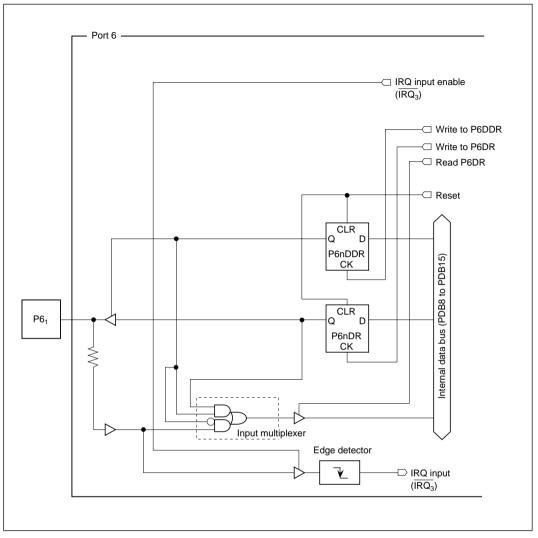

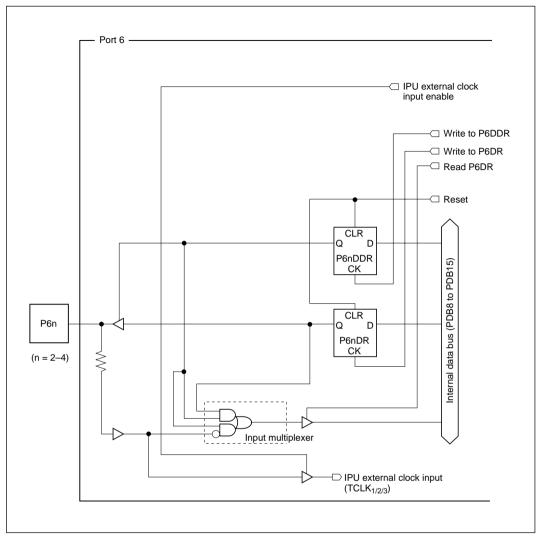

| 10.7  | Port 6  |                              | 203 |

|       | 10.7.1  | Overview                     | 203 |

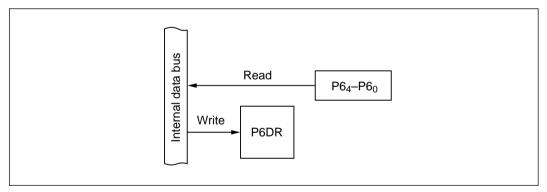

|       | 10.7.2  | Register Descriptions        | 204 |

|       | 10.7.3  | Pin Functions in Each Mode   | 206 |

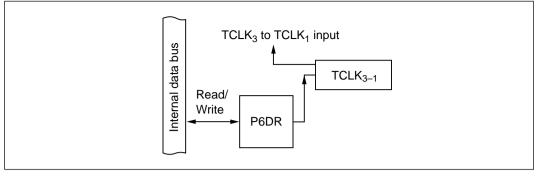

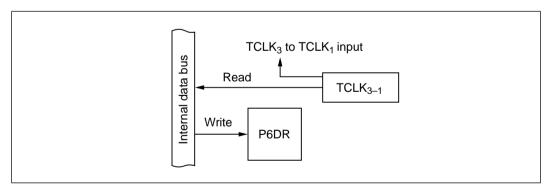

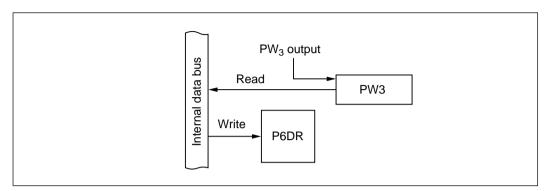

|       | 10.7.4  | Port 6 Read/Write Operations | 206 |

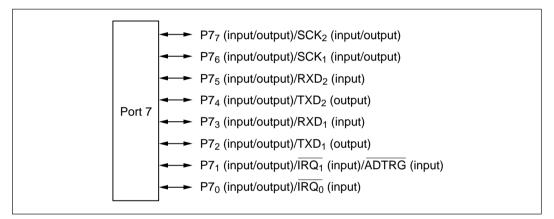

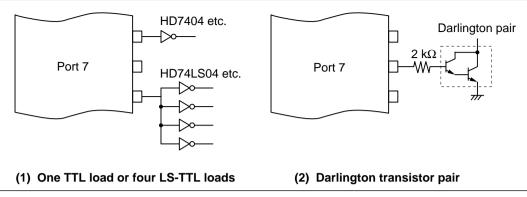

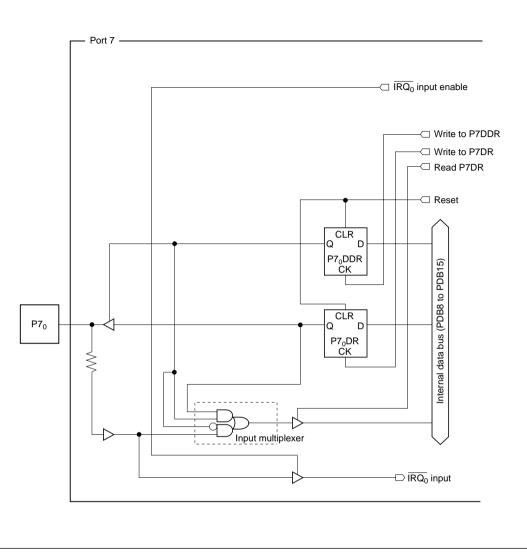

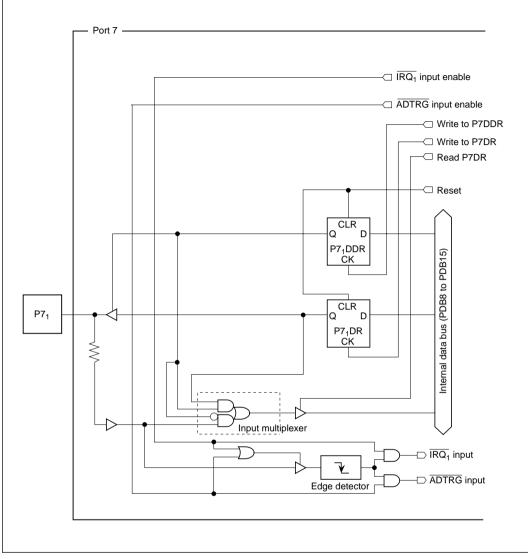

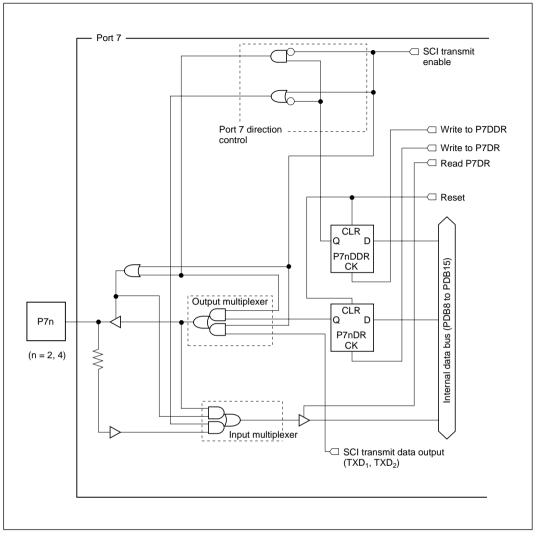

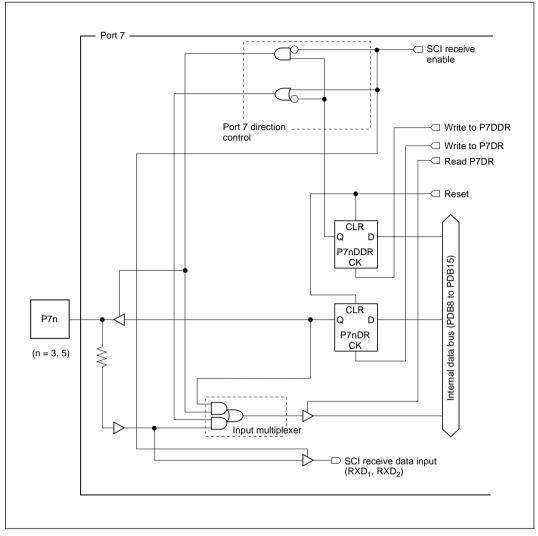

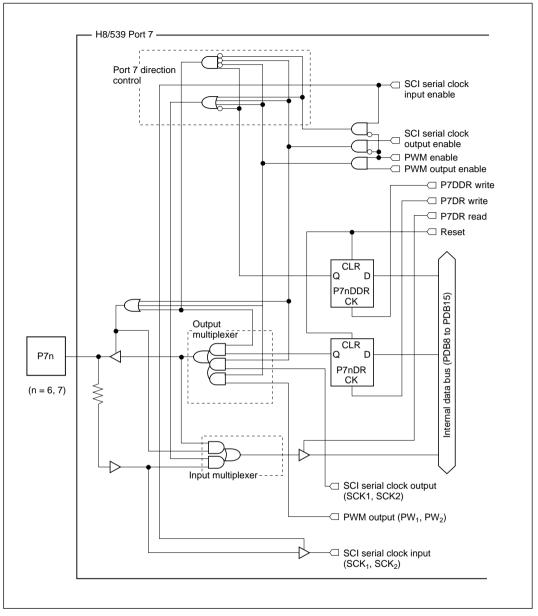

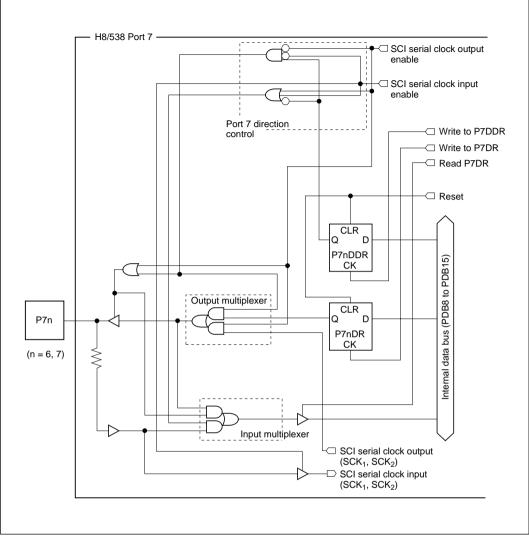

| 10.8  | Port 7  |                              | 211 |

|       | 10.8.1  | Overview                     | 211 |

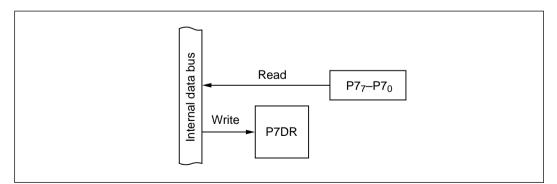

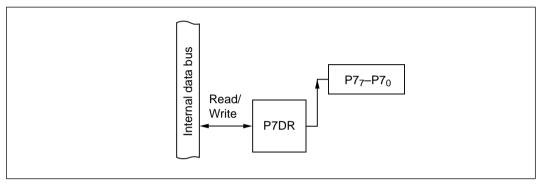

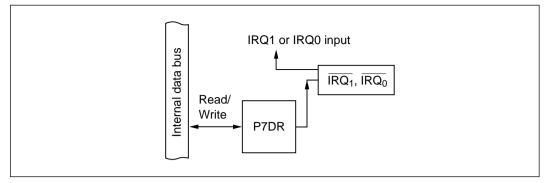

|       | 10.8.2  | Register Descriptions        | 212 |

|       | 10.8.3  | Pin Functions in Each Mode   | 214 |

|       | 10.8.4  | Port 7 Read/Write Operations | 214 |

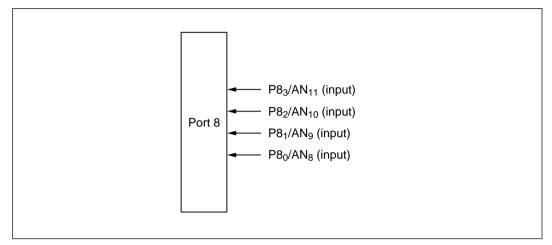

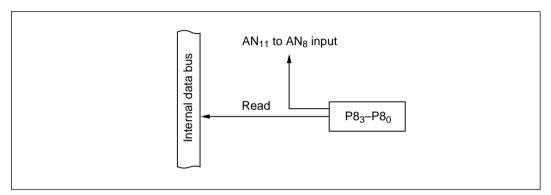

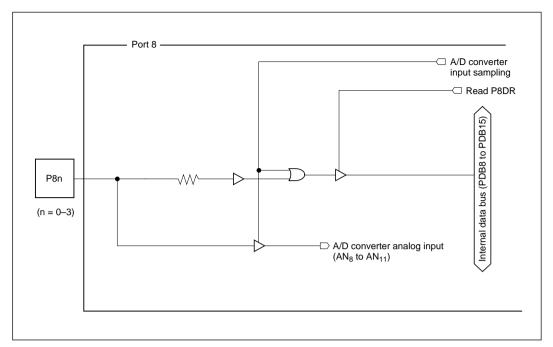

| 10.9  | Port 8  | -                            | 220 |

|       | 10.9.1  | Overview                     | 220 |

|       | 10.9.2  | Register Descriptions        | 220 |

|       | 10.9.3  | Port 8 Read Operation        | 221 |

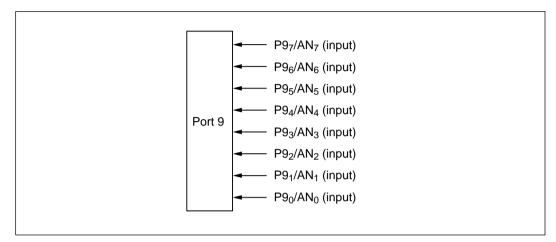

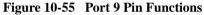

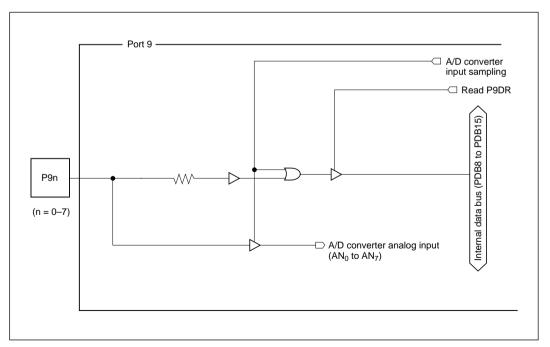

| 10.10 | Port 9  |                              | 222 |

|       | 10.10.1 | Overview                     | 222 |

|       | 10.10.2 | Register Descriptions        | 222 |

|       | 10.10.3 | Port 9 Read Operation        | 223 |

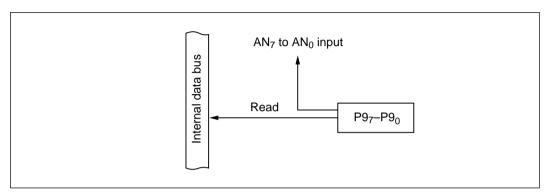

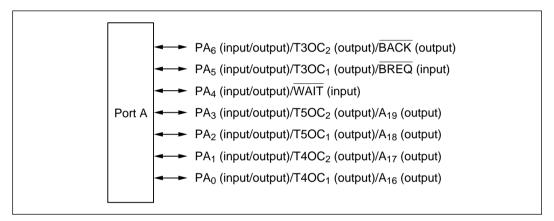

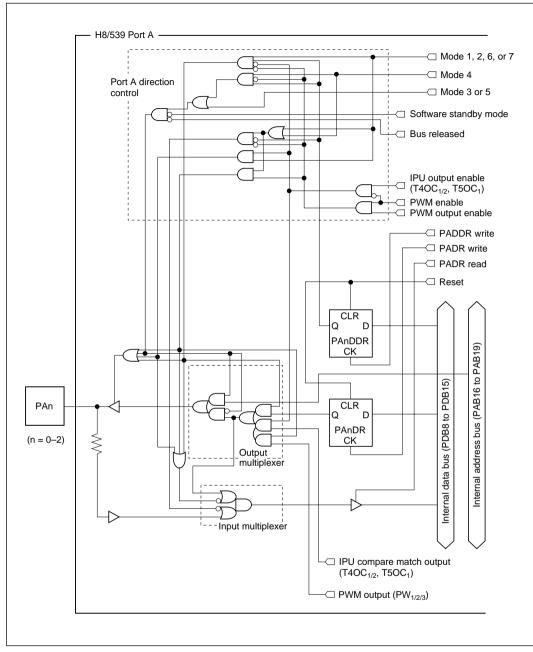

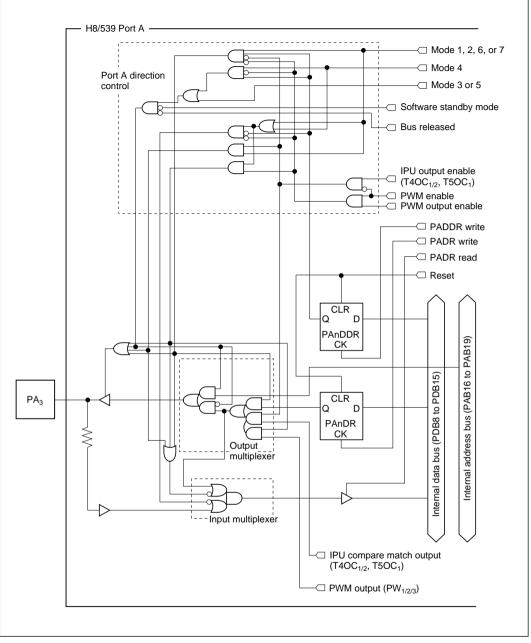

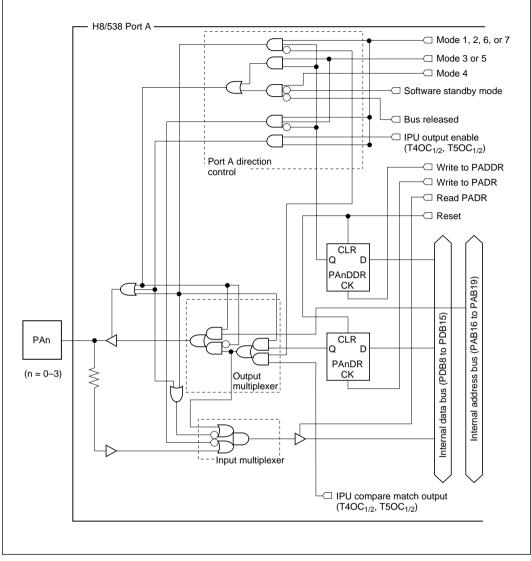

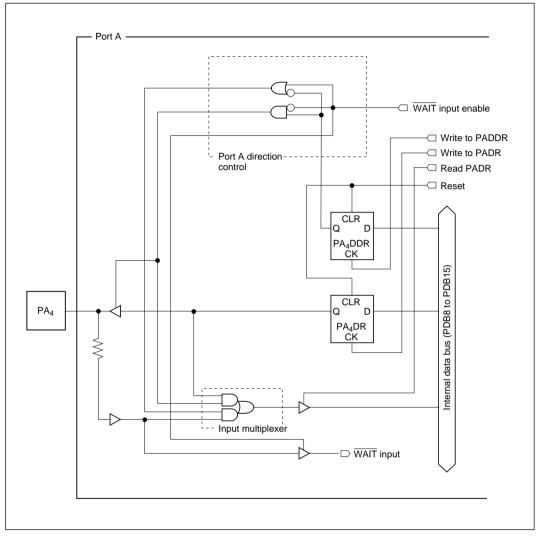

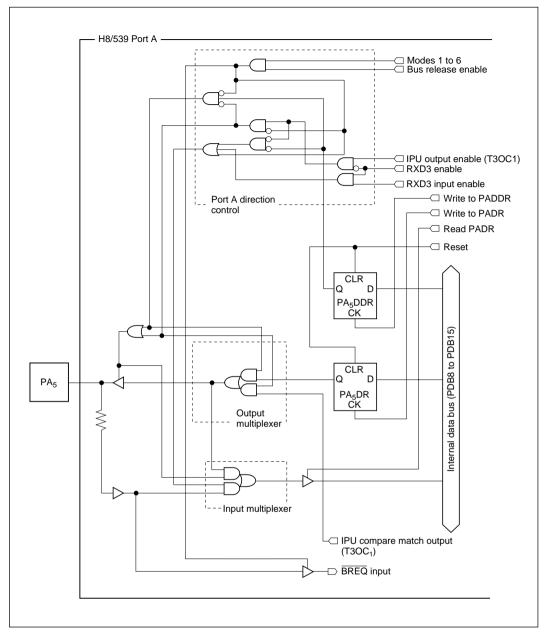

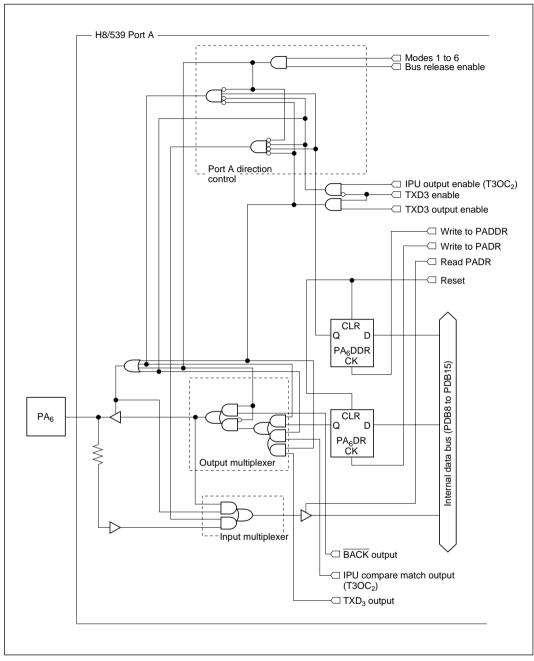

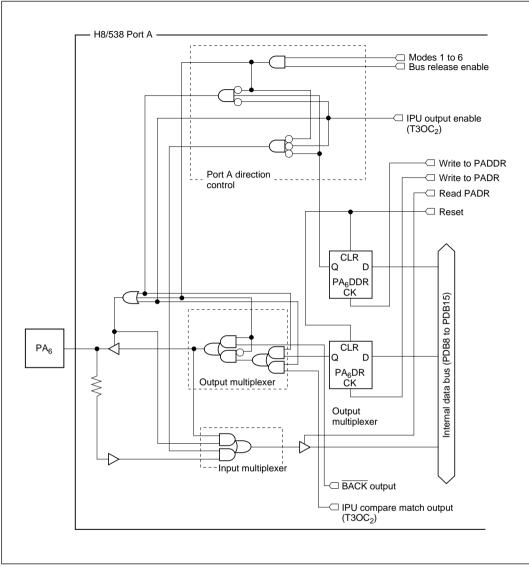

| 10.11 | Port A  |                              | 224 |

|       | 10.11.1 | Overview                     | 224 |

|       | 10.11.2 | Register Descriptions        | 225 |

|       | 10.11.3 | Pin Functions in Each Mode   | 227 |

|       | 10.11.4 | Port A Read/Write Operations | 231 |

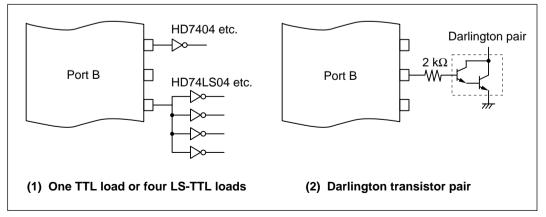

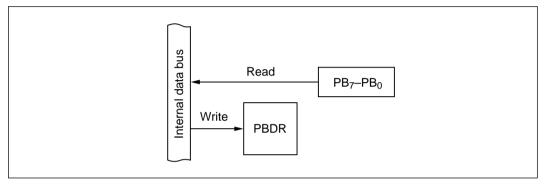

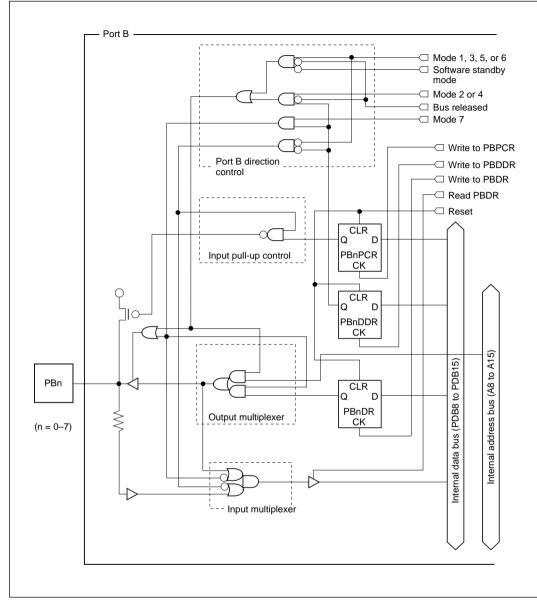

| 10.12 | Port B  |                              | 238 |

|       | 10.12.1 | Overview                     | 238 |

|       | 10.12.2 | Register Descriptions        | 239 |

|       | 10.12.3 | Pin Functions in Each Mode   | 240 |

|       | 10.12.4 | Built-In Pull-Up Transistors | 242 |

|       | 10.12.5 | Port B Read/Write Operations | 243 |

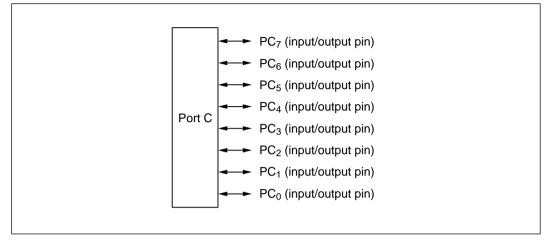

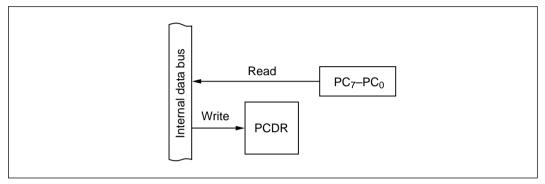

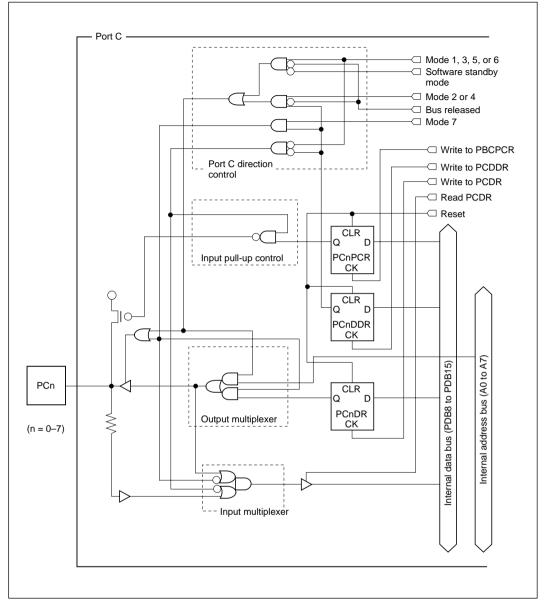

| 10.13 | Port C  |                              | 246 |

|       | 10.13.1 | Overview                     | 246 |

|       | 10.13.2 | Register Descriptions        | 247 |

|         | 10.13.3 | Pin Functions in Each Mode             | 248 |

|---------|---------|----------------------------------------|-----|

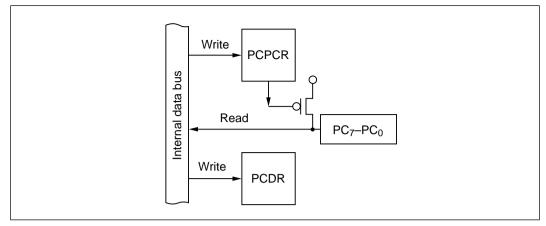

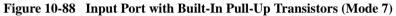

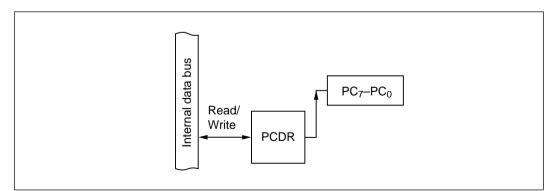

|         | 10.13.4 | Built-In MOS Pull-Up Transistors       | 250 |

|         | 10.13.5 | Port C Read/Write Operations           | 251 |

| 10.14   | ø Pin   | -                                      | 254 |

|         | 10.14.1 | Overview                               | 254 |

|         | 10.14.2 | Register Description                   | 254 |

|         |         |                                        |     |

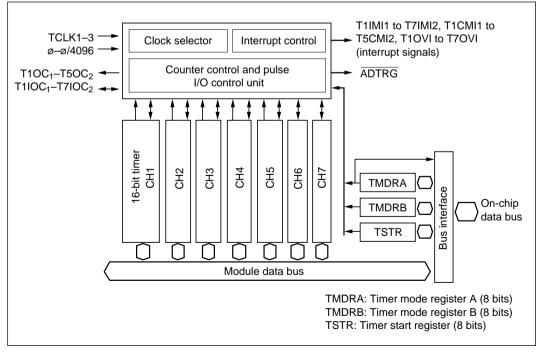

| Section | on 11   | 16-Bit Integrated-Timer Pulse Unit     | 255 |

| 11.1    | Overvie | -<br>2W                                | 255 |

|         | 11.1.1  | Features                               | 255 |

|         | 11.1.2  | Block Diagram                          | 256 |

|         | 11.1.3  | Input/Output Pins                      | 257 |

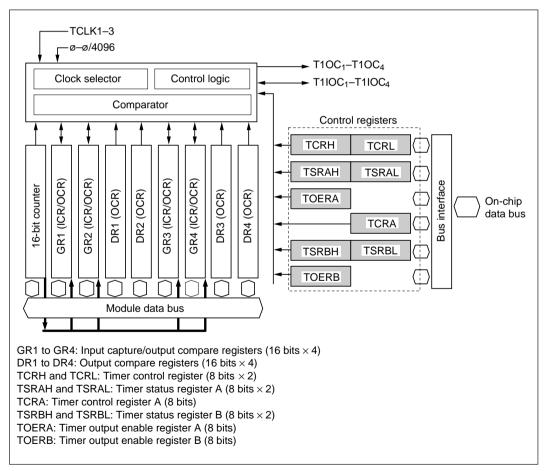

| 11.2    | Timer ( | Counters and Compare/Capture Registers | 258 |

| 11.3    | Channe  | l 1 Registers                          | 259 |

|         | 11.3.1  | Register Configuration                 | 260 |

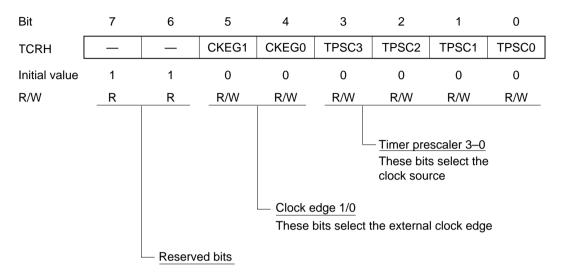

|         | 11.3.2  | Timer Control Register (High)          | 262 |

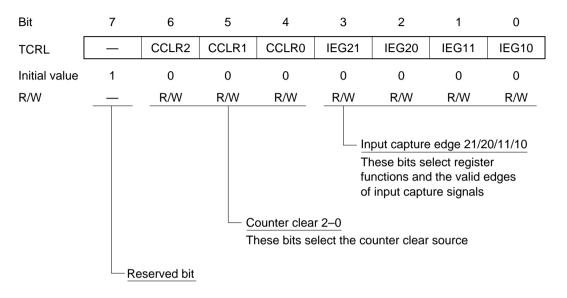

|         | 11.3.3  | Timer Control Register (Low)           | 264 |

|         | 11.3.4  | Timer Status Register (High)           | 268 |

|         | 11.3.5  | Timer Status Register (Low)            | 272 |

|         | 11.3.6  | Timer Output Enable Register           | 276 |

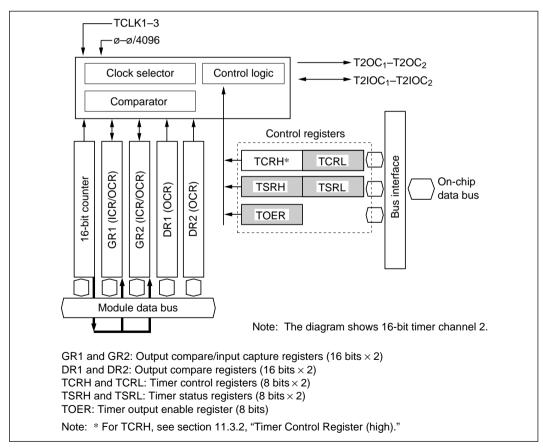

| 11.4    | Channe  | 1 2 to 5 Registers                     | 281 |

|         | 11.4.1  | Register Configuration                 | 282 |

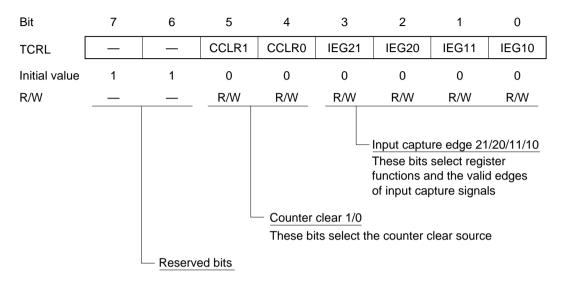

|         | 11.4.2  | Timer Control Register (Low)           | 286 |

|         | 11.4.3  | Timer Status Register (High)           | 288 |

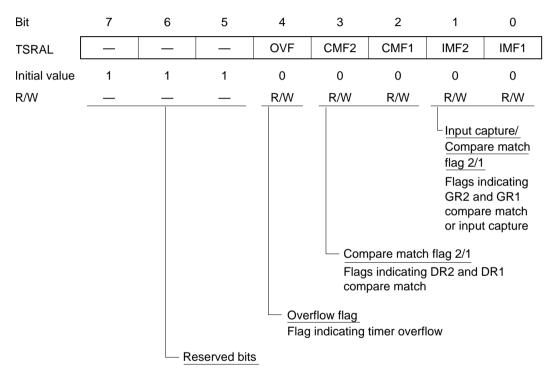

|         | 11.4.4  | Timer Status Register (Low)            | 290 |

|         | 11.4.5  | Timer Output Enable Register           | 292 |

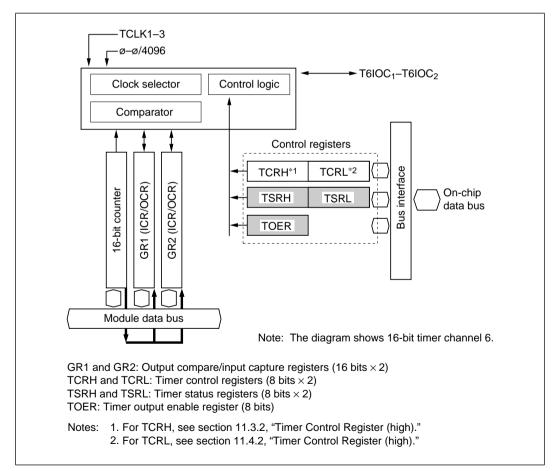

| 11.5    | Channe  | el 6 and 7 Registers                   | 295 |

|         | 11.5.1  | Register Configuration                 | 296 |

|         | 11.5.2  | Timer Status Register (High)           | 298 |

|         | 11.5.3  | Timer Status Register (Low)            | 300 |

|         | 11.5.4  | Timer Output Enable Register           | 302 |

| 11.6    | IPU Re  | gister Descriptions                    | 304 |

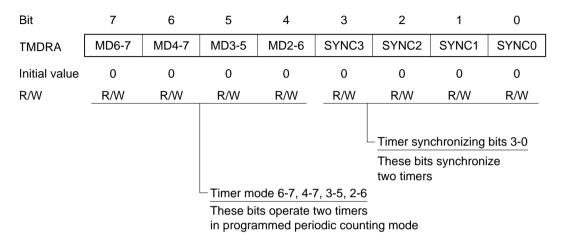

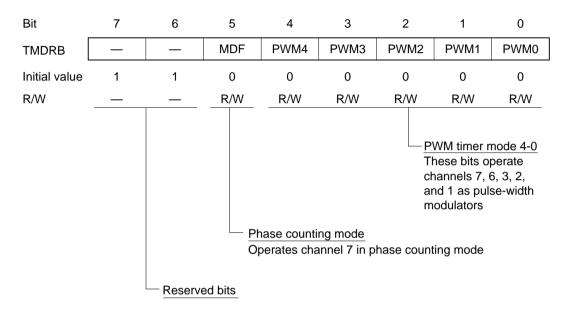

|         | 11.6.1  | Timer Mode Register A                  | 304 |

|         | 11.6.2  | Timer Mode Register B                  | 307 |

|         | 11.6.3  | Timer Start Register                   | 310 |

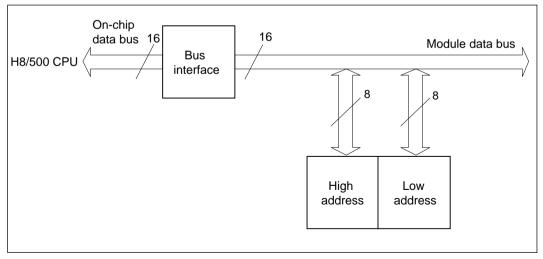

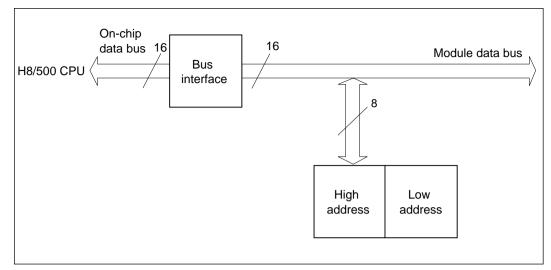

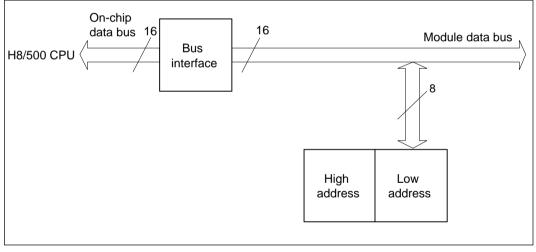

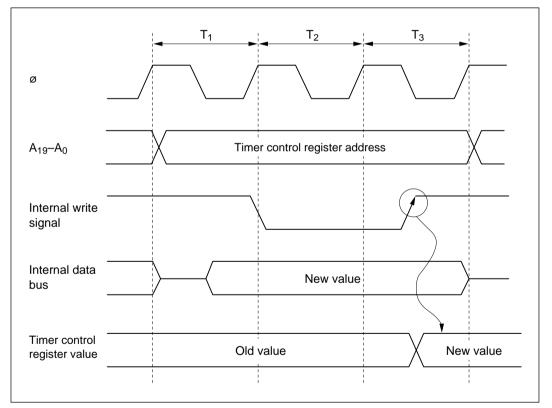

| 11.7    | H8/500  | CPU Interface                          | 312 |

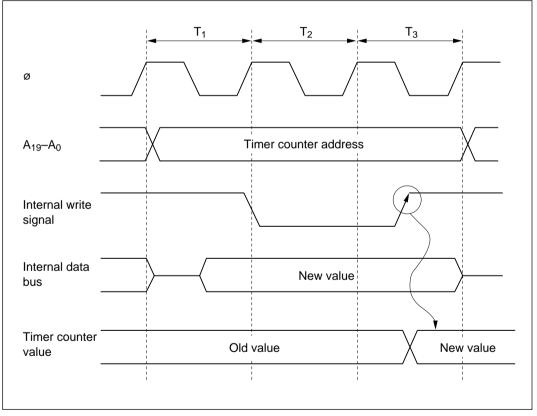

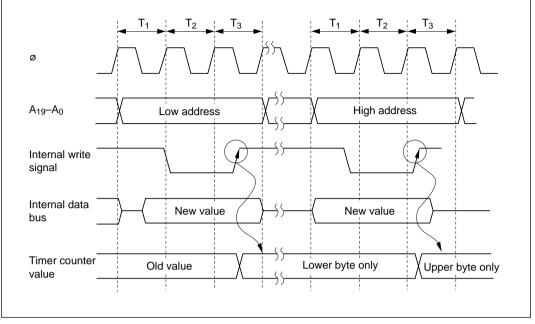

|         | 11.7.1  | 16-Bit Accessible Registers            | 312 |

|         | 11.7.2  | Eight-Bit Accessible Registers         | 315 |

| 11.8    | Exampl  | les of Timer Operation                 | 318 |

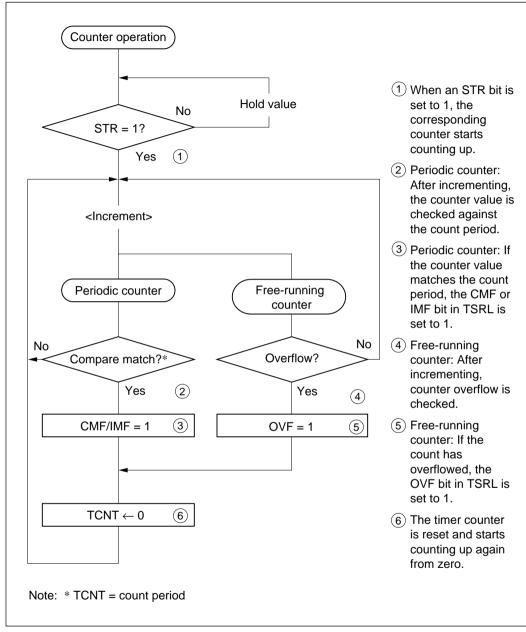

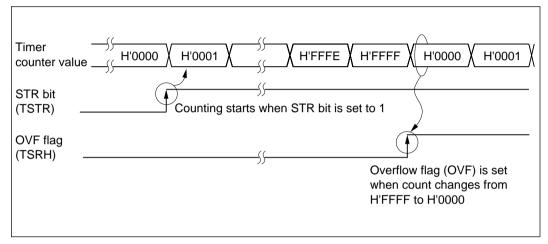

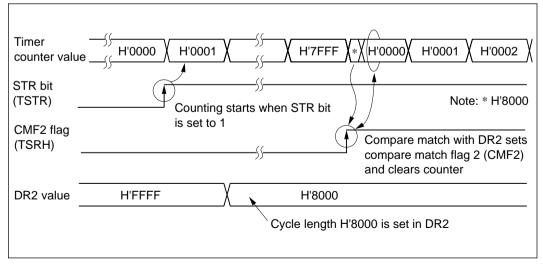

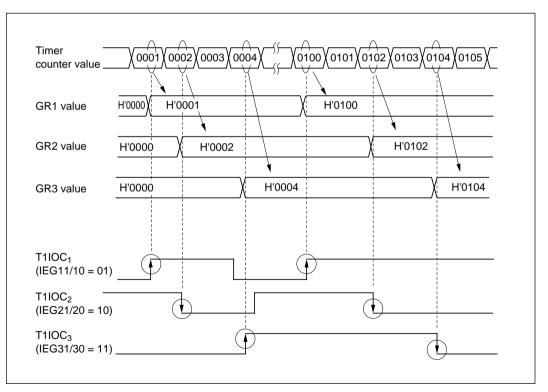

|         | 11.8.1  | Examples of Counting                   | 318 |

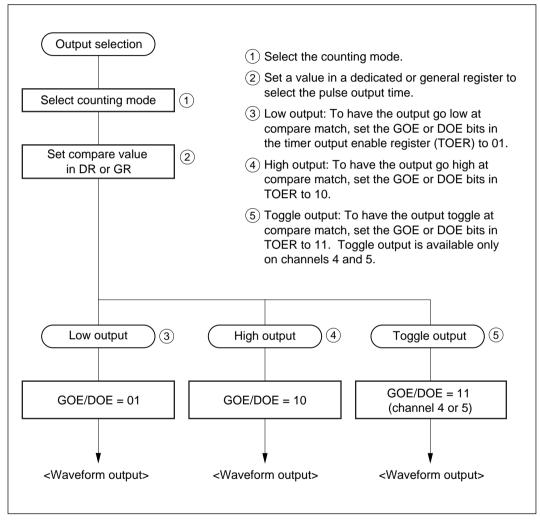

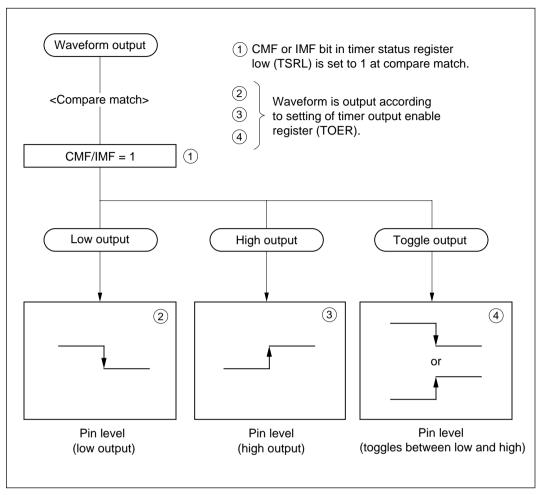

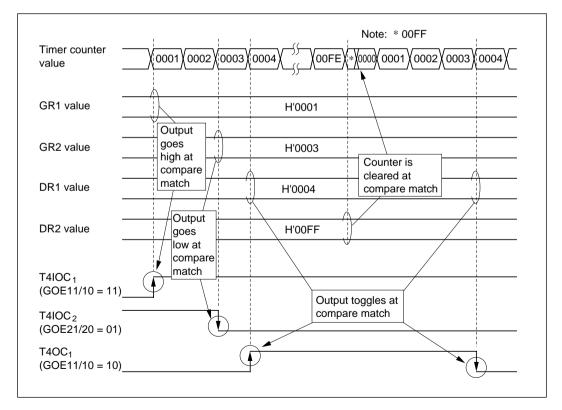

|         | 11.8.2  | Selection of Output Level              | 321 |

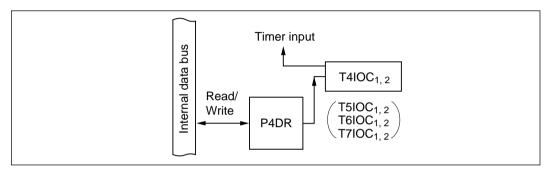

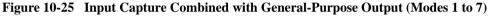

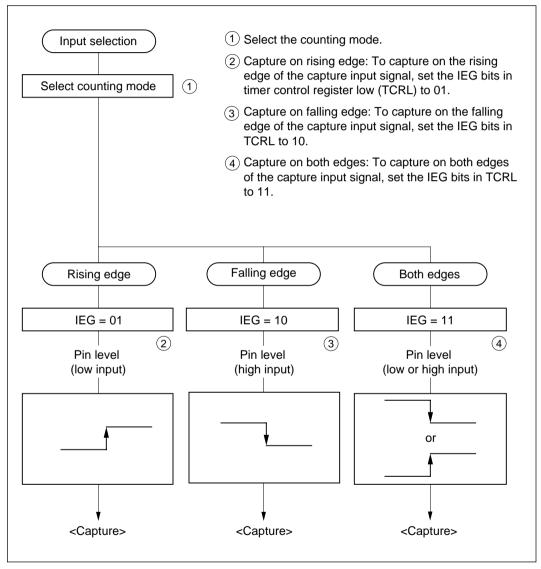

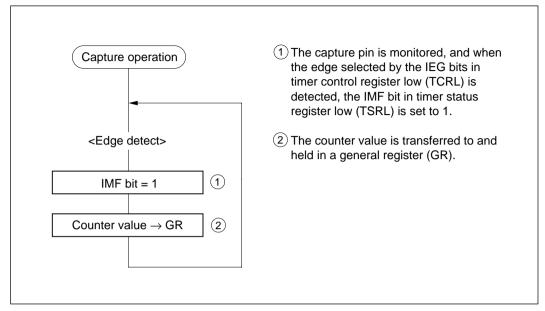

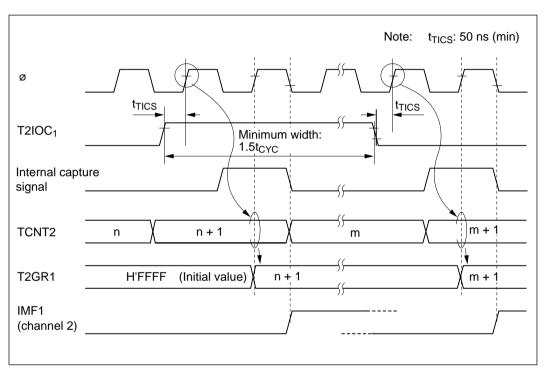

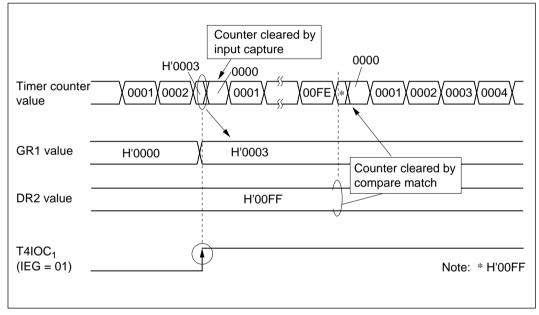

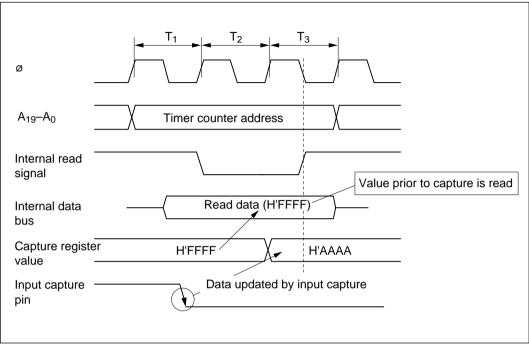

|         | 11.8.3   | Input Capture Function                               | 324 |

|---------|----------|------------------------------------------------------|-----|

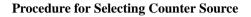

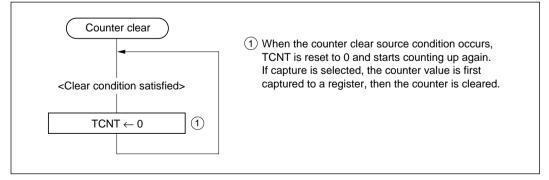

|         | 11.8.4   | Counter Clearing Function                            | 328 |

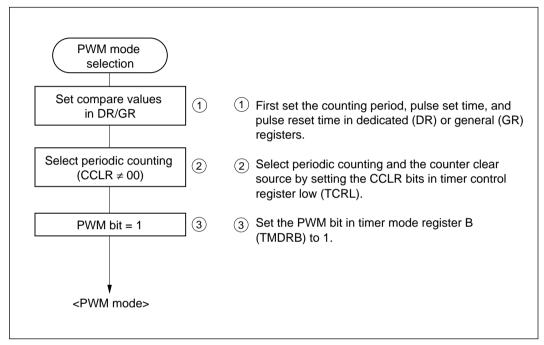

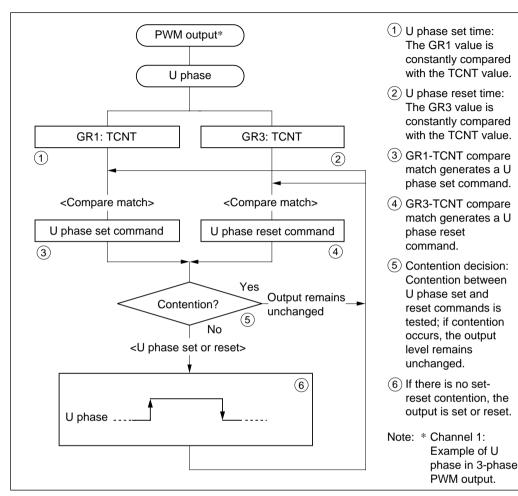

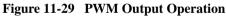

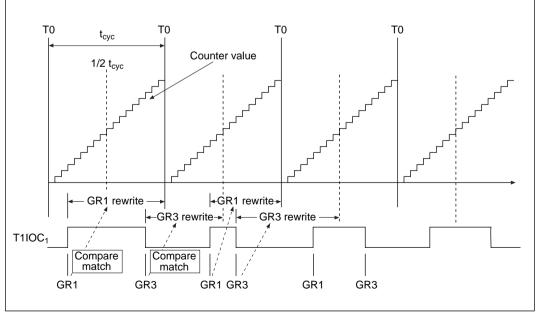

|         | 11.8.5   | PWM Output Mode                                      | 330 |

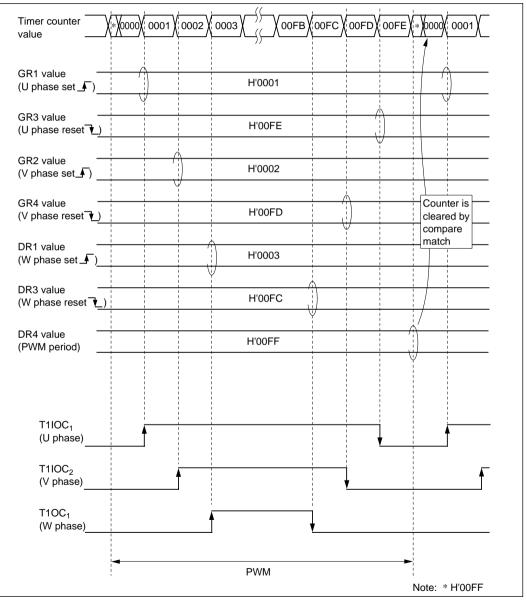

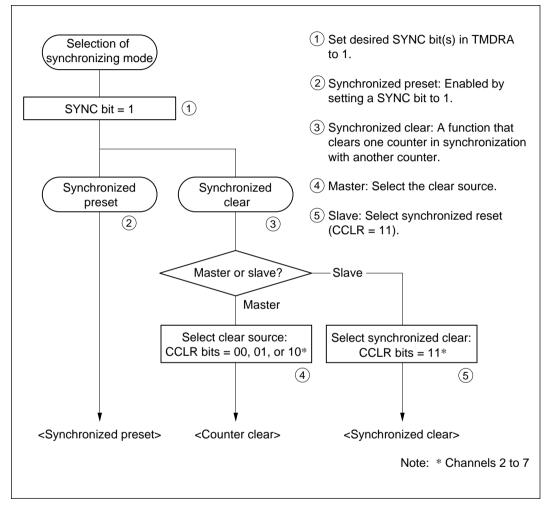

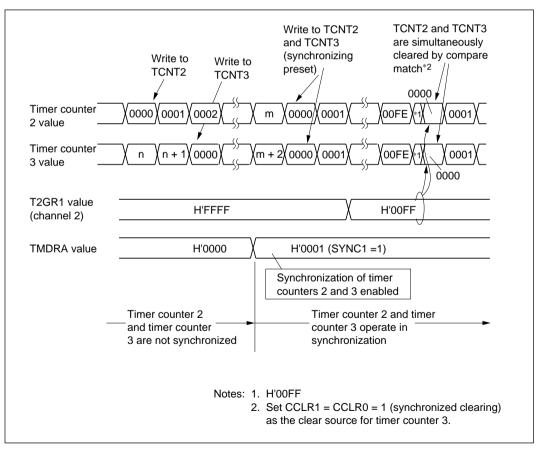

|         | 11.8.6   | Synchronizing Mode                                   | 334 |

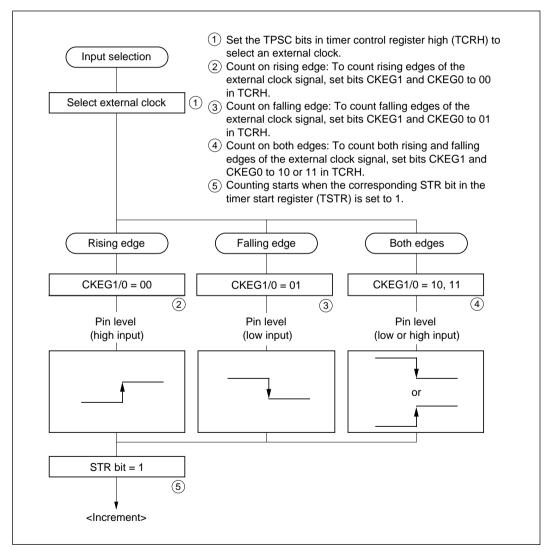

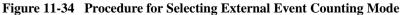

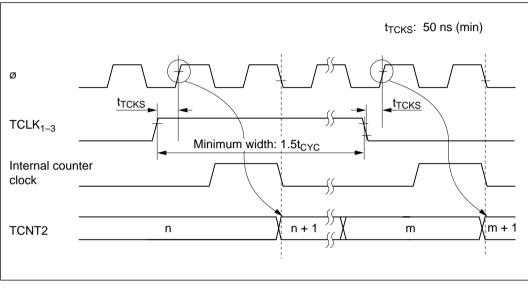

|         | 11.8.7   | External Event Counting                              | 337 |

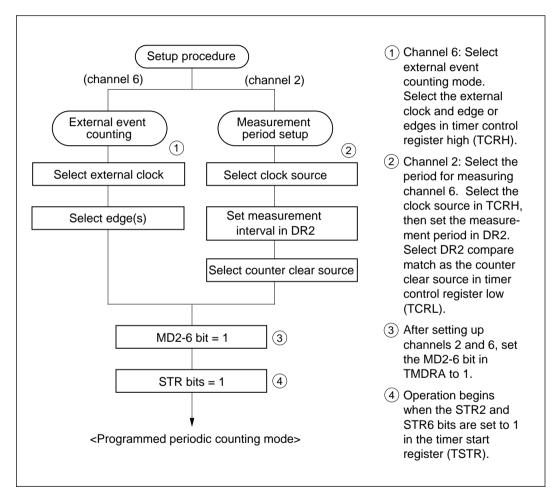

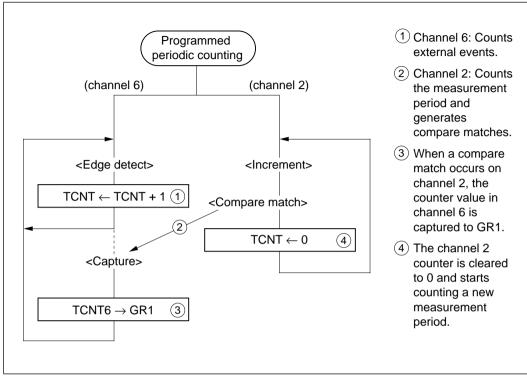

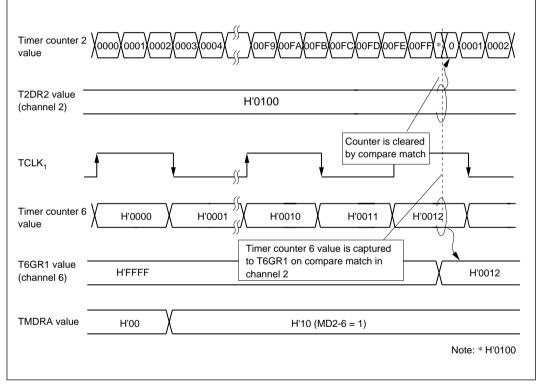

|         | 11.8.8   | Programmed Periodic Counting Mode                    | 340 |

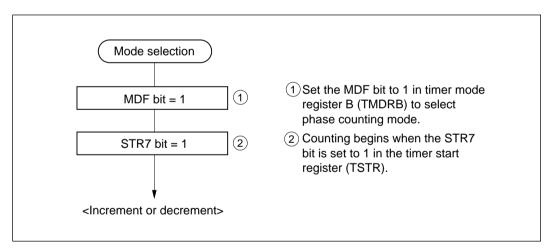

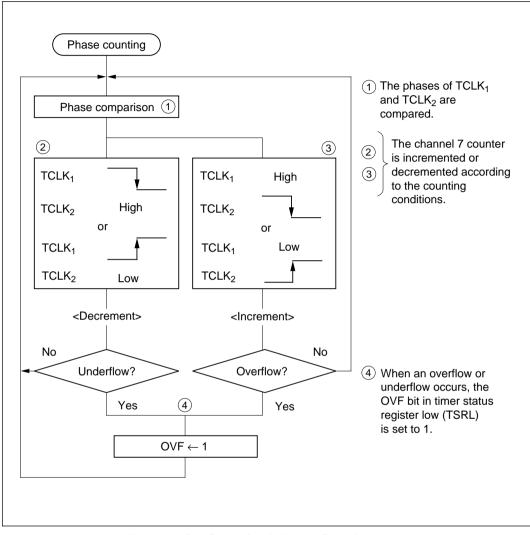

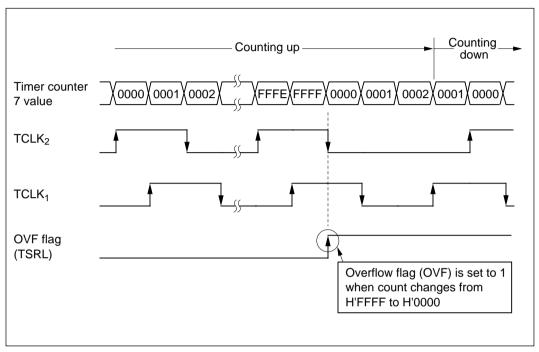

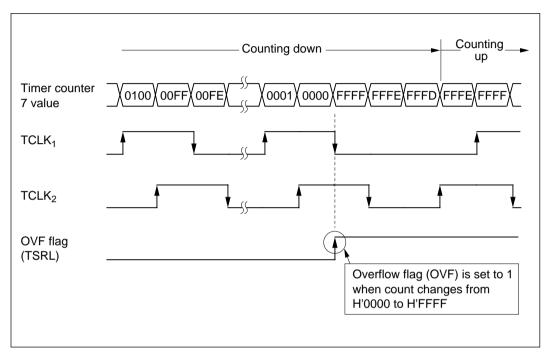

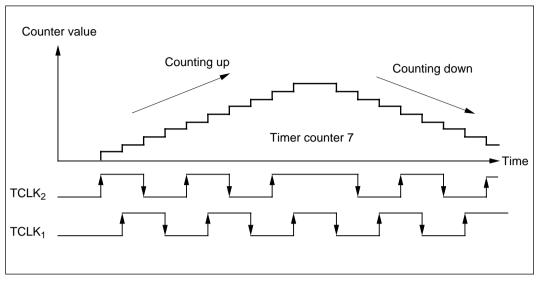

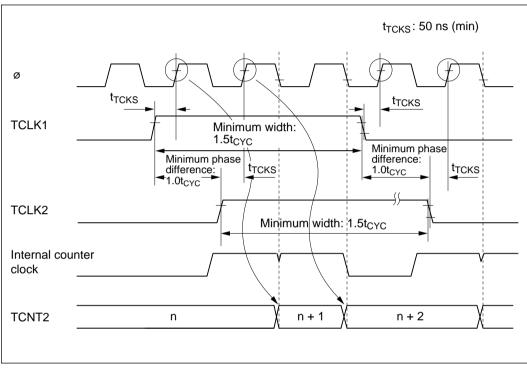

|         | 11.8.9   | Phase Counting Mode                                  | 343 |

| 11.9    | Interrup | ots                                                  | 349 |

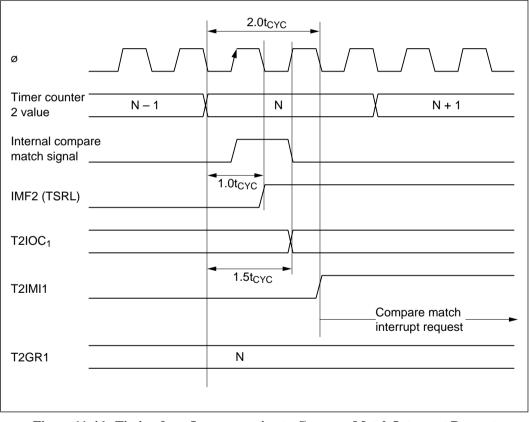

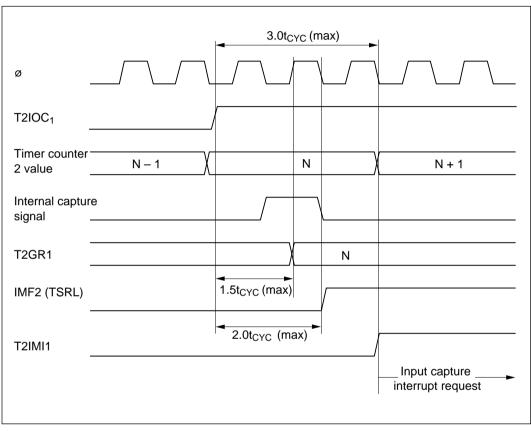

|         | 11.9.1   | Interrupt Timing                                     | 349 |

|         | 11.9.2   | Interrupt Sources and DTC Interrupts                 | 351 |

| 11.10   | Notes a  | nd Precautions                                       | 353 |

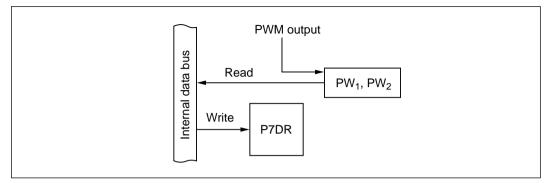

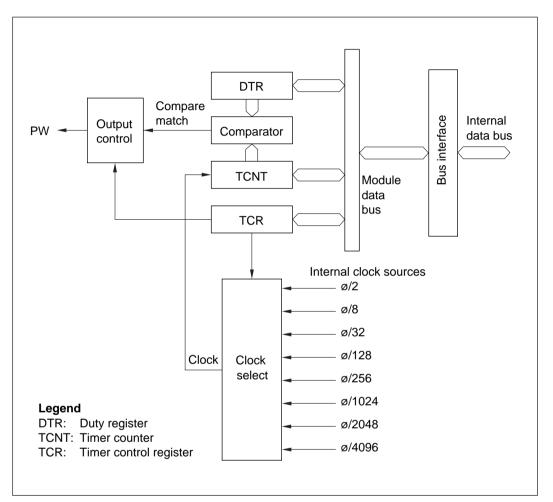

| Section | on 12    | PWM Timers (H8/539 only)                             | 365 |

| 12.1    | Overvie  | 2W                                                   | 365 |

|         | 12.1.1   | Features                                             | 365 |

|         | 12.1.2   | Block Diagram                                        | 366 |

|         | 12.1.3   | Pin Configuration                                    | 367 |

|         | 12.1.4   | Register Configuration                               | 367 |

| 12.2    | Registe  | r Descriptions                                       | 368 |

|         | 12.2.1   | Timer Counter                                        | 368 |

|         | 12.2.2   | Duty Register                                        | 368 |

|         | 12.2.3   | Timer Control Register                               |     |

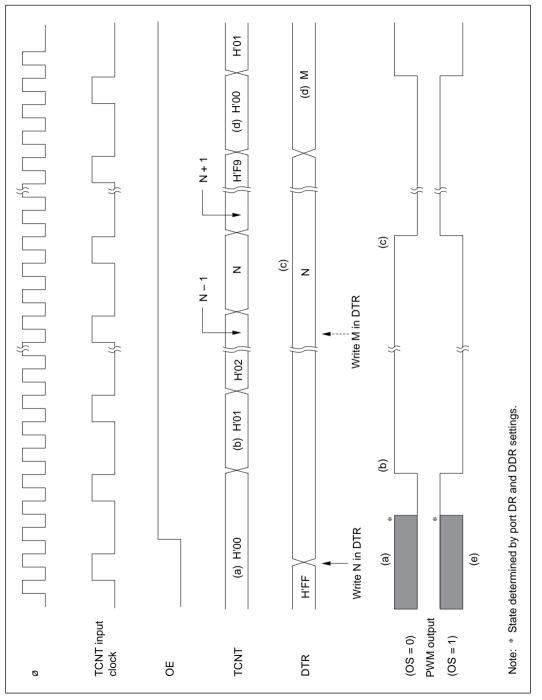

| 12.3    | PWM 7    | Fimer Operation                                      | 371 |

| 12.4    | Usage 1  | Notes                                                | 373 |

| Section | on 13    | Watchdog Timer                                       | 375 |

| 13.1    | Overvie  | 2W                                                   | 375 |

|         | 13.1.1   | Features                                             | 375 |

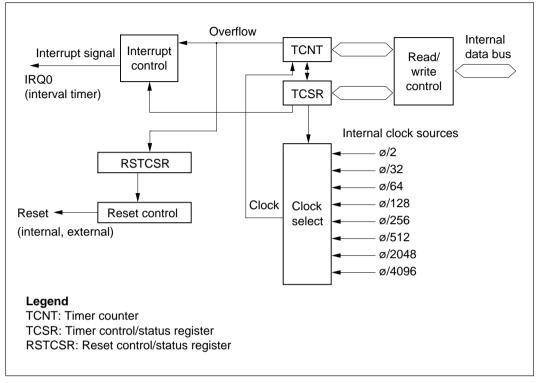

|         | 13.1.2   | Block Diagram                                        | 376 |

|         | 13.1.3   | Register Configuration                               | 376 |

| 13.2    | Registe  | r Descriptions                                       | 377 |

|         | 13.2.1   | Timer Counter                                        | 377 |

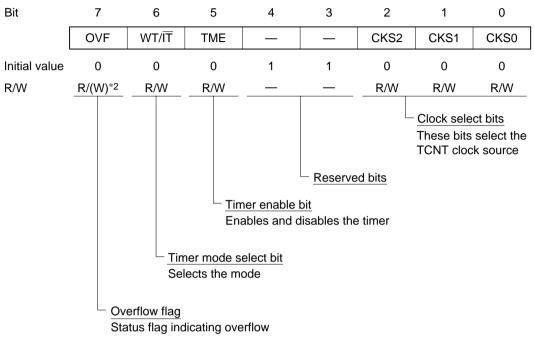

|         | 13.2.2   | Timer Control/Status Register                        | 378 |

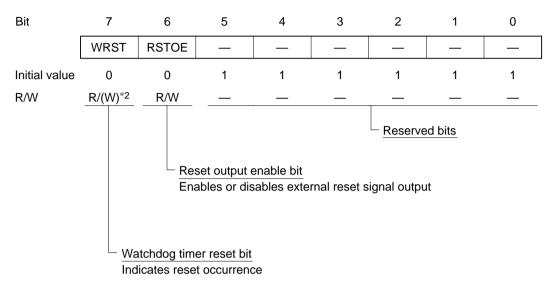

|         | 13.2.3   | Reset Control/Status Register                        | 380 |

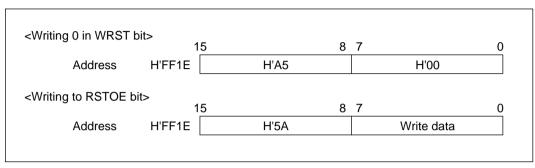

|         | 13.2.4   | Notes on Register Access                             | 381 |

| 13.3    | Operati  | on                                                   | 383 |

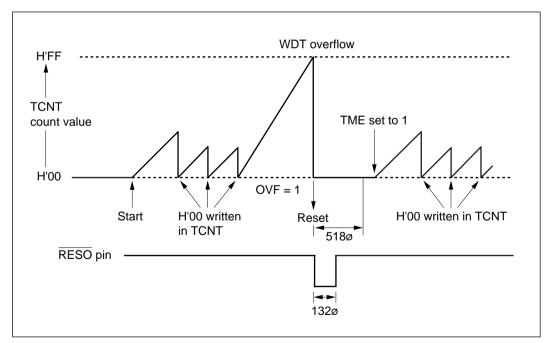

|         | 13.3.1   | Watchdog Timer Operation                             | 383 |

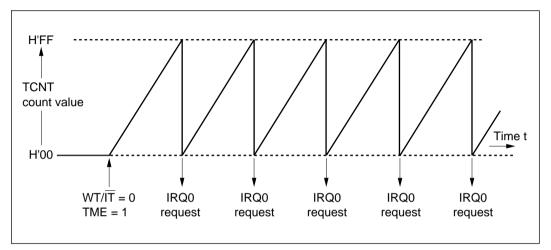

|         | 13.3.2   | Interval Timer Operation                             | 384 |

|         | 13.3.3   | Operation in Software Standby Mode                   |     |

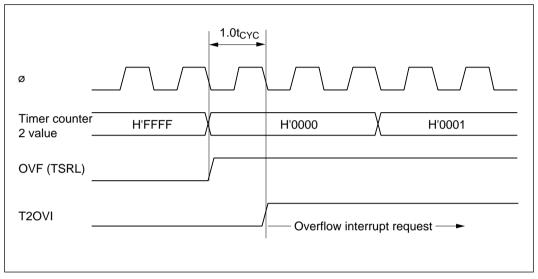

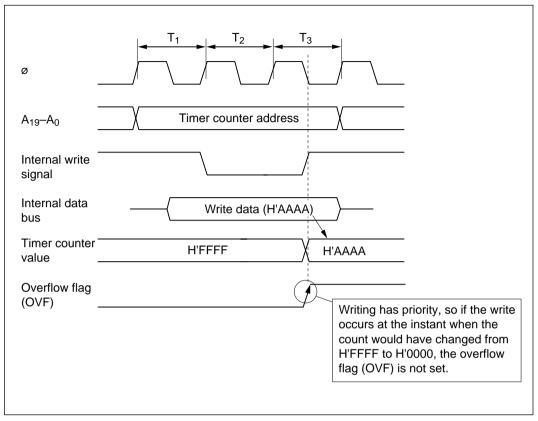

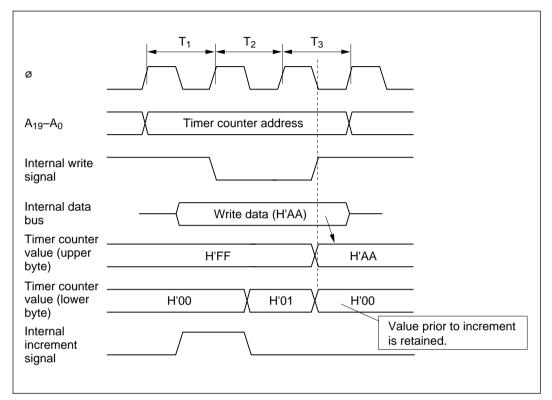

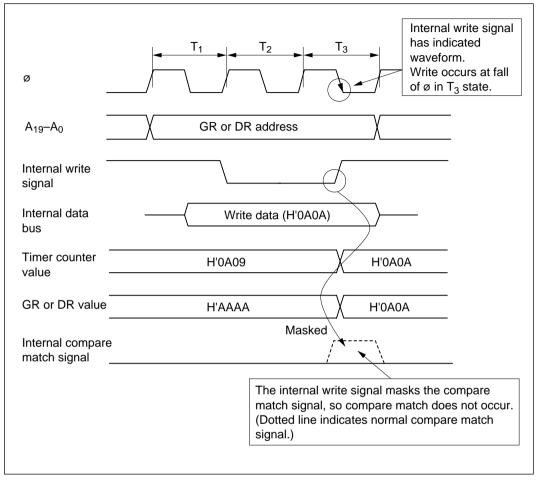

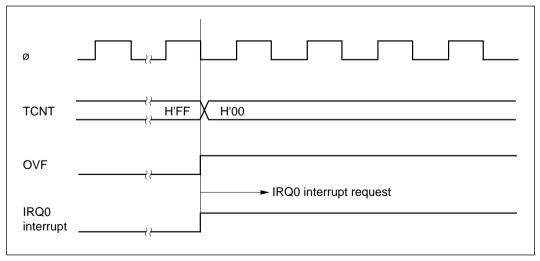

|         | 13.3.4   | Timing of Setting of Overflow Flag (OVF)             | 385 |

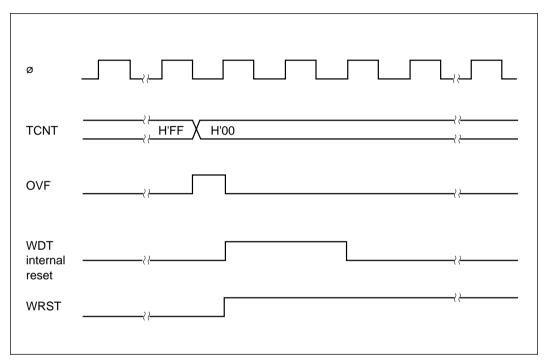

|         | 13.3.5   | Timing of Setting of Watchdog Timer Reset Bit (WRST) | 386 |

| 13.4    | Usage 1 | Notes                                         | 387 |

|---------|---------|-----------------------------------------------|-----|

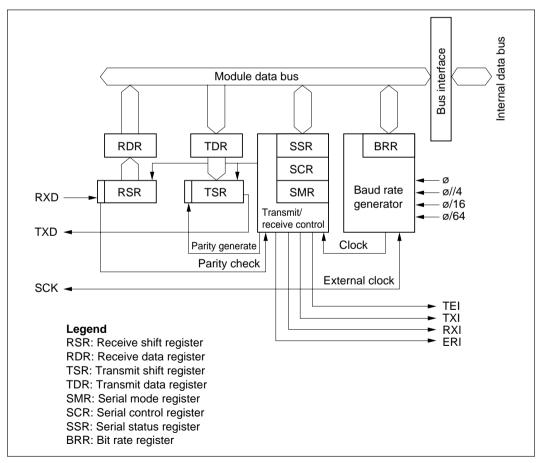

| Section | on 14   | Serial Communication Interface                | 389 |

| 14.1    | Overvie | ew                                            | 389 |

|         | 14.1.1  | Features                                      | 389 |

|         | 14.1.2  | Block Diagram                                 | 390 |

|         | 14.1.3  | Input/Output Pins                             | 391 |

|         | 14.1.4  | Register Configuration                        | 391 |

| 14.2    | Registe | r Descriptions                                | 393 |

|         | 14.2.1  | Receive Shift Register                        | 393 |

|         | 14.2.2  | Receive Data Register                         | 393 |

|         | 14.2.3  | Transmit Shift Register                       | 394 |

|         | 14.2.4  | Transmit Data Register                        | 394 |

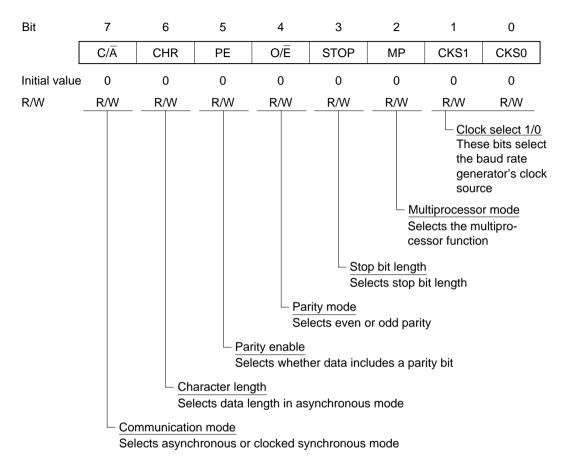

|         | 14.2.5  | Serial Mode Register                          | 395 |

|         | 14.2.6  | Serial Control Register                       |     |

|         | 14.2.7  | Serial Status Register                        | 403 |

|         | 14.2.8  | Bit Rate Register                             | 408 |

| 14.3    | Operati | on                                            | 415 |

|         | 14.3.1  | Overview                                      | 415 |

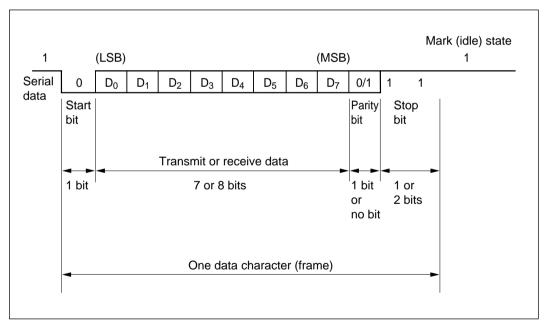

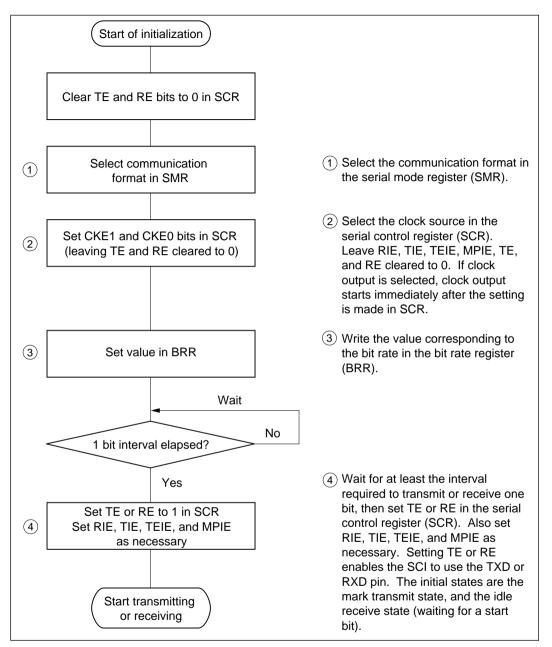

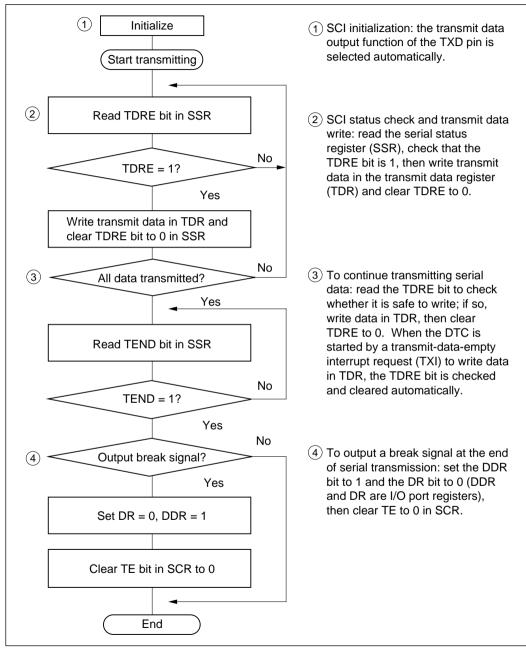

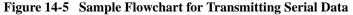

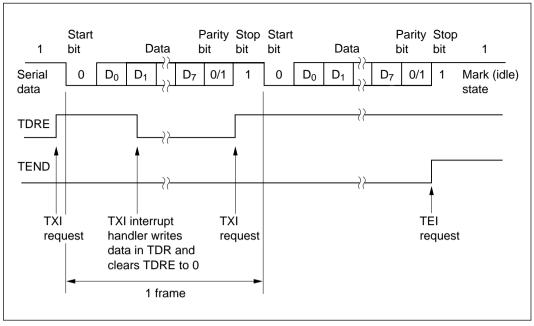

|         | 14.3.2  | Operation in Asynchronous Mode                | 417 |

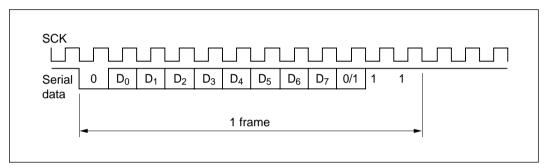

|         | 14.3.3  | Clocked Synchronous Operation                 | 427 |

|         | 14.3.4  | Multiprocessor Communication                  | 437 |

| 14.4    | Interru | pts and DTC                                   | 445 |

| 14.5    | Usage 1 | Notes                                         | 445 |

|         |         |                                               |     |

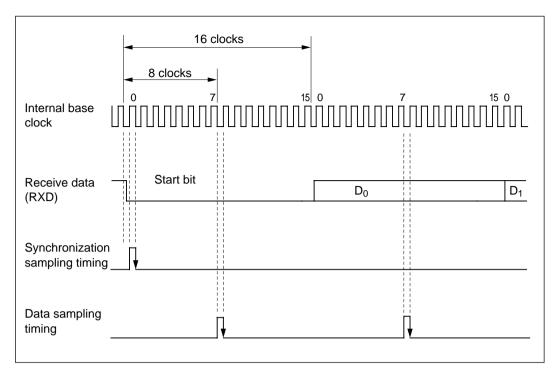

| Section | on 15   | A/D Converter                                 | 449 |

| 15.1    | Overvie | ew                                            | 449 |

|         | 15.1.1  | Features                                      | 449 |

|         | 15.1.2  | Block Diagram                                 | 450 |

|         | 15.1.3  | Input/Output Pins                             | 451 |

|         | 15.1.4  | Register Configuration                        | 452 |

| 15.2    | Registe | r Descriptions                                | 453 |

|         | 15.2.1  | A/D Data Registers 0 to B                     | 453 |

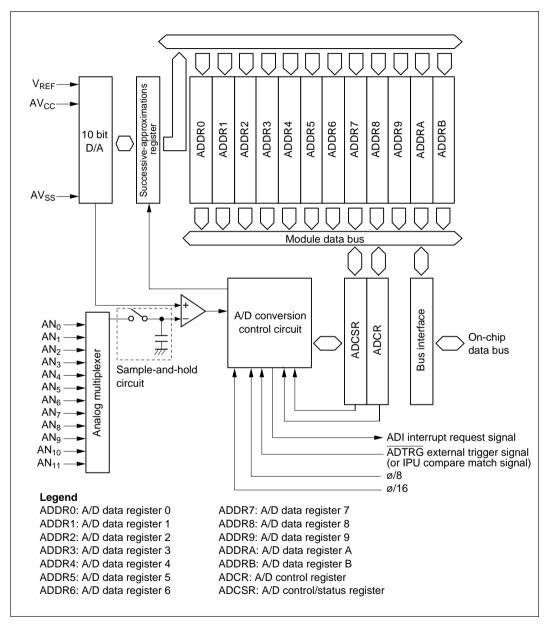

|         | 15.2.2  | A/D Control Status Register                   | 454 |

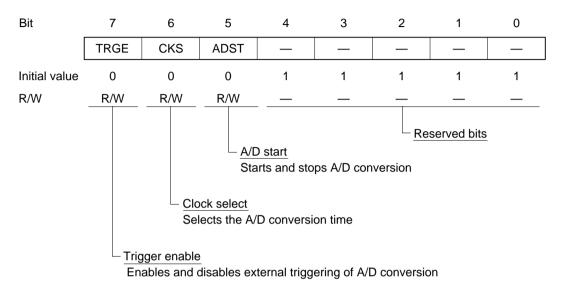

|         | 15.2.3  | A/D Control Register                          | 458 |

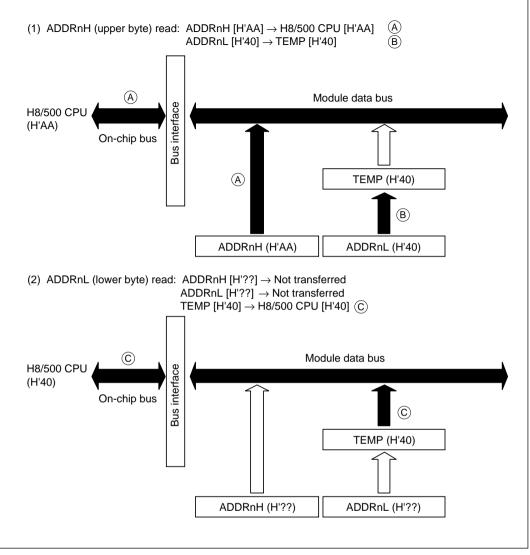

| 15.3    | H8/500  | CPU Interface                                 | 460 |

| 15.4    | Operati | on                                            | 462 |

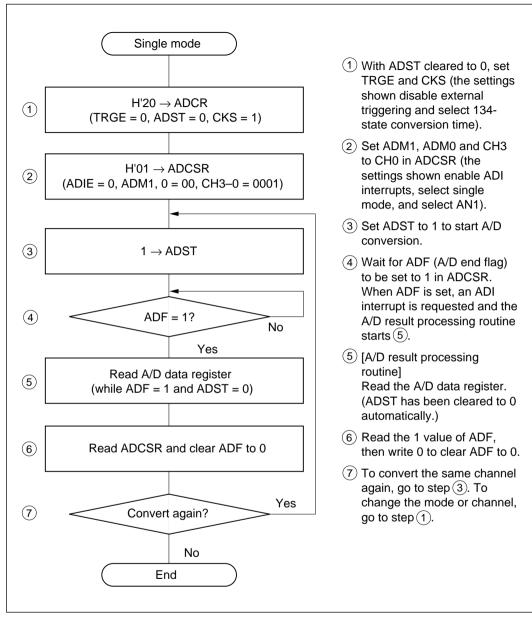

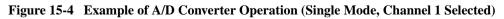

|         | 15.4.1  | Single Mode                                   | 462 |

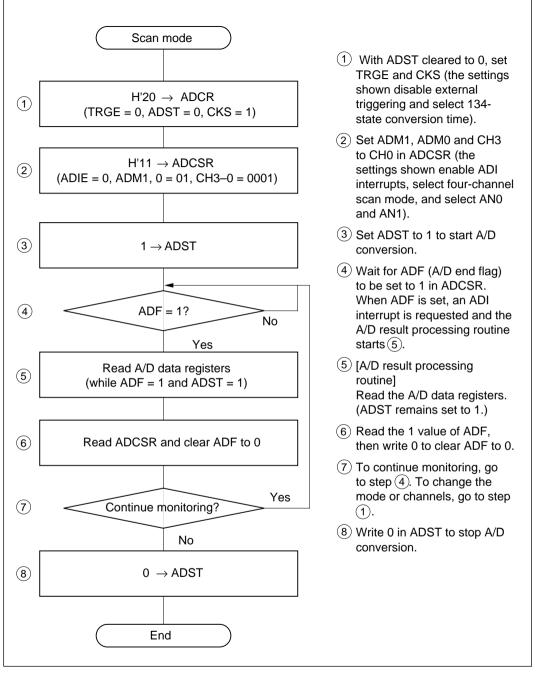

|         | 15.4.2  | Scan Mode                                     | 465 |

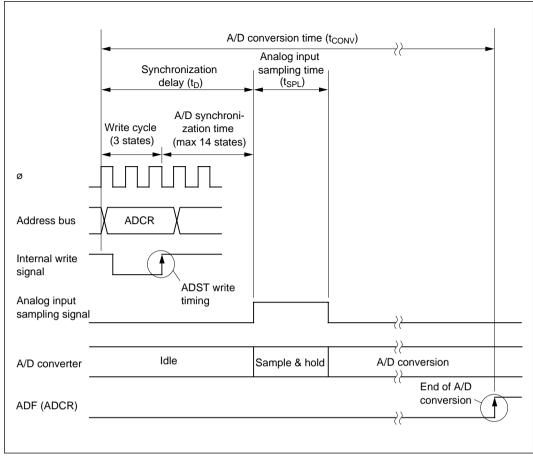

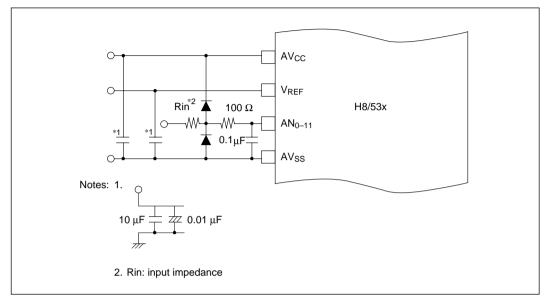

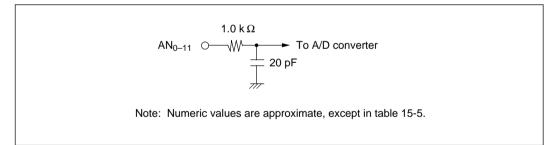

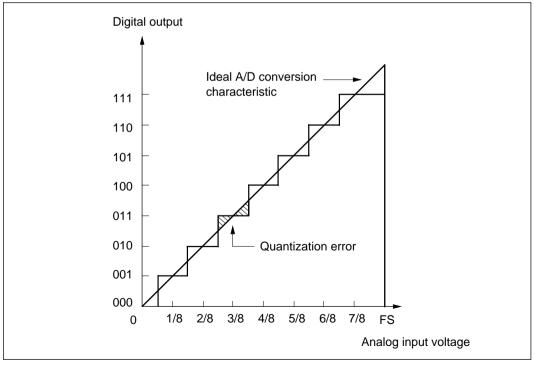

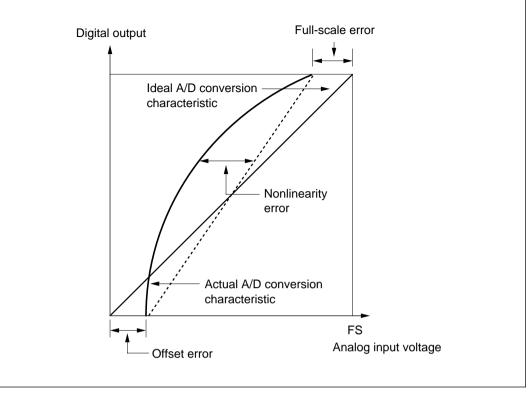

|         | 15.4.3  | Analog Input Sampling and A/D Conversion Time | 468 |

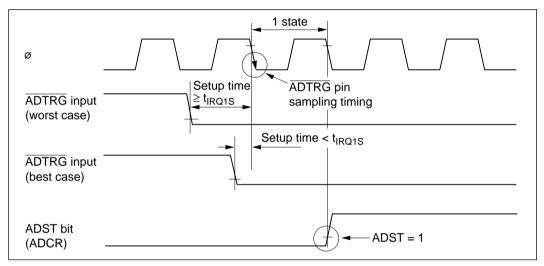

|         | 15.4.4  | External Triggering of A/D Conversion         | 470 |

|         | 15.4.5   | Starting A/D Conversion by IPU              | 470 |

|---------|----------|---------------------------------------------|-----|

| 15.5    | Interrup | ots and DTC                                 | 471 |

| 15.6    | Usage I  | Notes                                       | 471 |

|         |          |                                             |     |

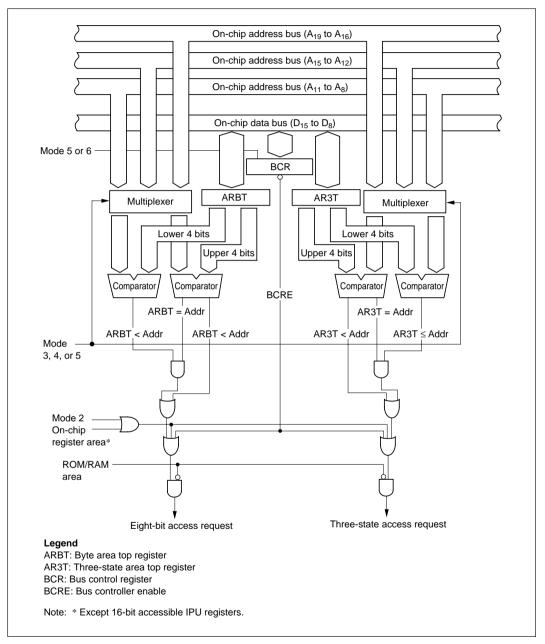

| Section | on 16    | Bus Controller                              | 475 |

| 16.1    | Overvie  | 2W                                          | 475 |

|         | 16.1.1   | Features                                    | 475 |

|         | 16.1.2   | Block Diagram                               |     |

|         | 16.1.3   | Register Configuration                      | 477 |

| 16.2    | Registe  | r Descriptions                              | 477 |

|         | 16.2.1   | Byte Area Top Register                      | 477 |

|         | 16.2.2   | Three-State Area Top Register               | 478 |

|         | 16.2.3   | Bus Control Register                        | 479 |

| 16.3    | Operati  | on                                          | 483 |

|         | 16.3.1   | Operation after Reset in Each Mode          | 483 |

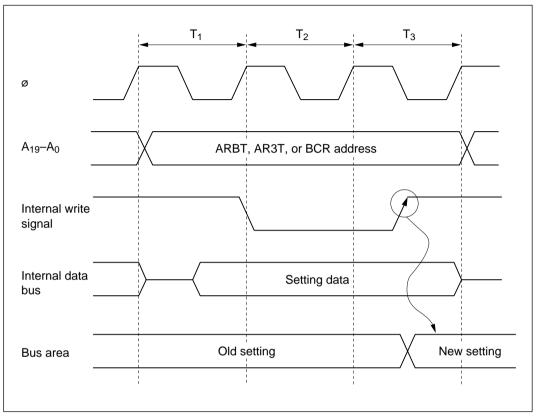

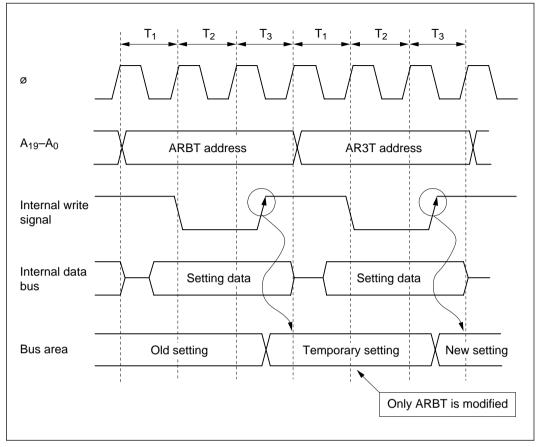

|         | 16.3.2   | Timing of Changes in Bus Areas and Bus Size | 490 |

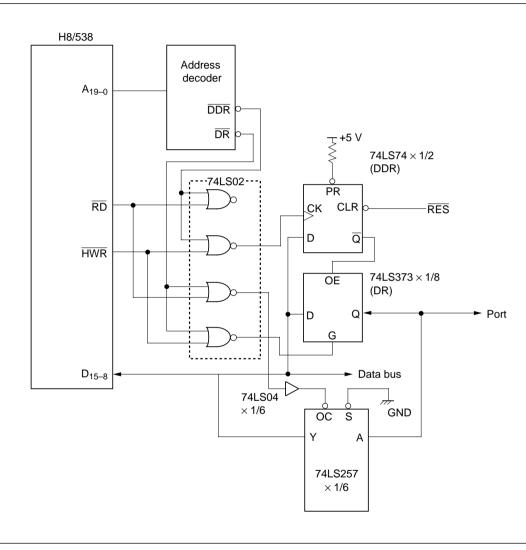

|         | 16.3.3   | I/O Port Expansion Function                 | 492 |

| 16.4    |          | Notes                                       |     |

|         |          |                                             |     |

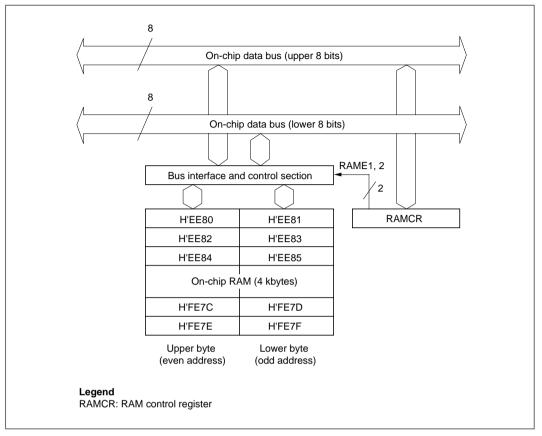

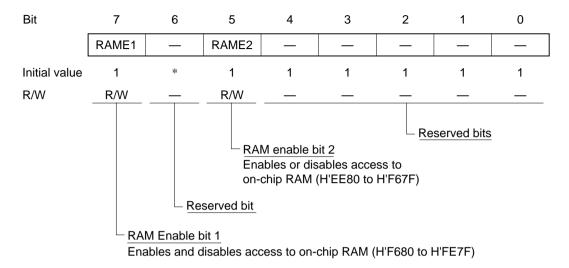

| Sectio  | on 17    | RAM                                         | 501 |

| 17.1    | Overvie  | 2W                                          | 501 |

|         | 17.1.1   | Block Diagram                               | 501 |

|         | 17.1.2   | Register Configuration                      | 502 |

| 17.2    | RAM C    | Control Register                            | 503 |

| 17.3    | Operati  | on                                          | 504 |

|         | 17.3.1   | Expanded Modes (Modes 1 to 6)               | 504 |

|         |          | Single-Chip Mode (Mode 7)                   |     |

|         |          |                                             |     |

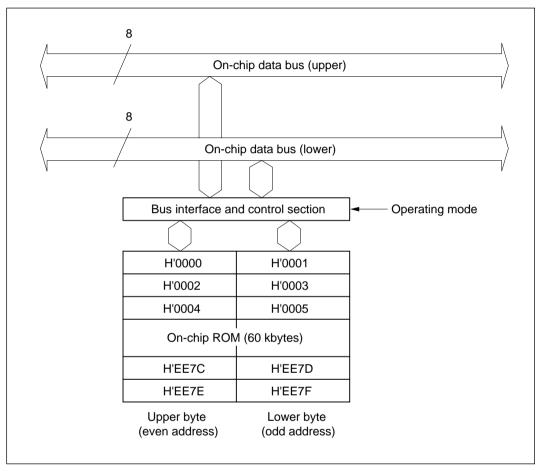

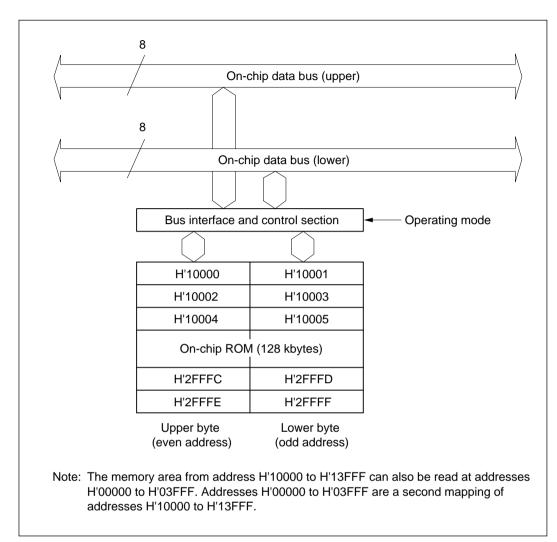

| Sectio  | on 18    | ROM                                         | 505 |

| 18.1    | Overvie  | 2W                                          | 505 |

|         | 18.1.1   | Block Diagram                               | 506 |

| 18.2    | PROM     | Mode                                        | 508 |

|         | 18.2.1   | PROM Mode Setting                           | 508 |

|         | 18.2.2   | Socket Adapter and Memory Map               | 508 |

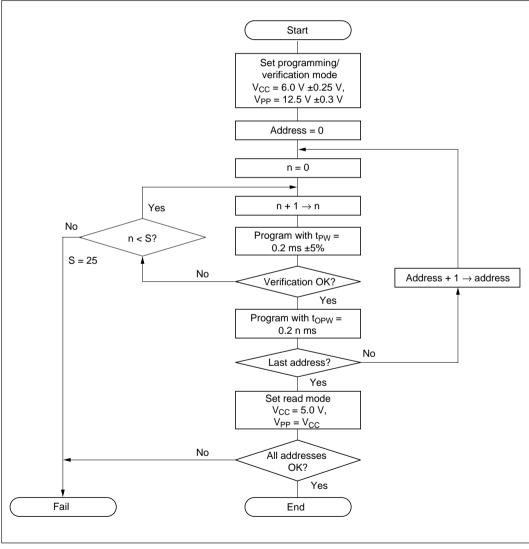

| 18.3    | Program  | nming                                       | 511 |

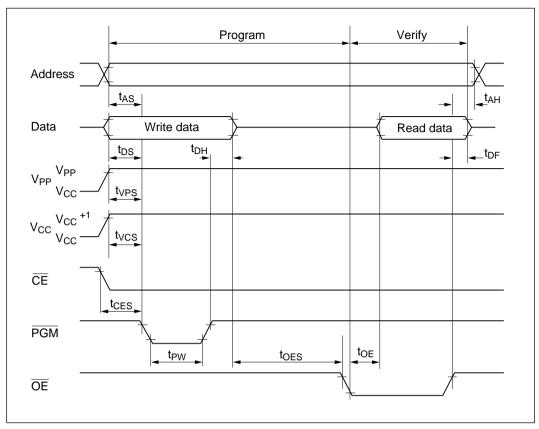

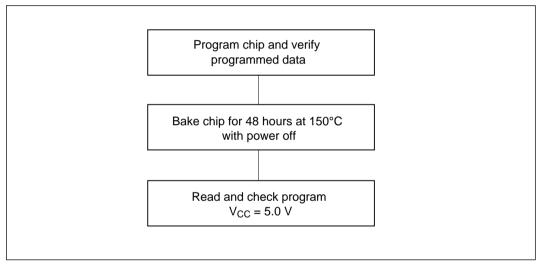

|         | 18.3.1   | Programming and Verification                | 512 |

|         | 18.3.2   | Programming Precautions                     | 514 |

| 18.4    |          | lity of Programmed Data                     |     |

|         |          |                                             |     |

| Sectio  | on 19    | Power-Down State                            | 517 |

| 19.1    | Overvie  | 2W                                          | 517 |

|         |          |                                             |     |

| 19.2         | Sleep N | 10de                                        | 518 |

|--------------|---------|---------------------------------------------|-----|

|              | 19.2.1  | Transition to Sleep Mode                    | 518 |

|              | 19.2.2  | Exit from Sleep Mode                        | 518 |

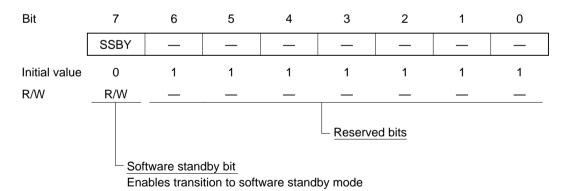

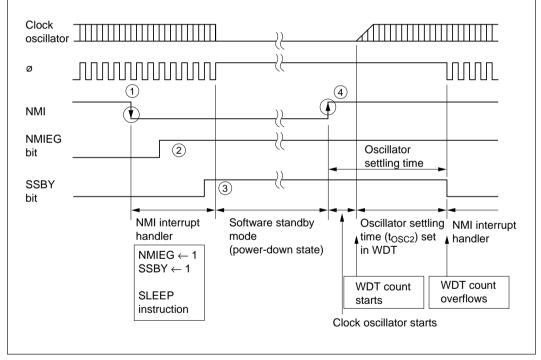

| 19.3         | Softwar | re Standby Mode                             | 519 |

|              | 19.3.1  | Transition to Software Standby Mode         | 519 |

|              | 19.3.2  | Software Standby Control Register           | 519 |

|              | 19.3.3  | Exit from Software Standby Mode             | 520 |

|              | 19.3.4  | Sample Application of Software Standby Mode | 521 |

|              | 19.3.5  | Note                                        | 521 |

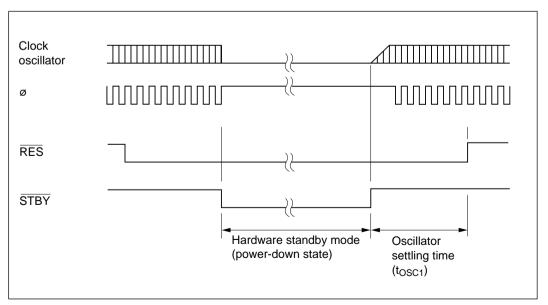

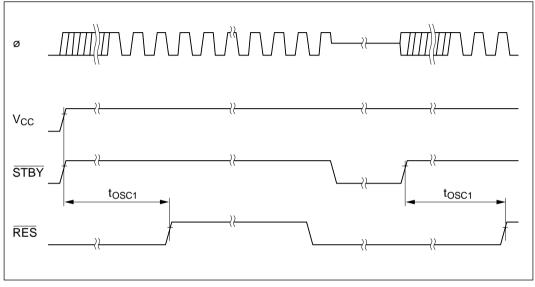

| 19.4         | Hardwa  | re Standby Mode                             | 522 |

|              | 19.4.1  | Transition to Hardware Standby Mode         | 522 |

|              | 19.4.2  | Recovery from Hardware Standby Mode         | 522 |

|              | 19.4.3  | Timing for Hardware Standby Mode            | 522 |

| а <i>(</i> : | 20      |                                             |     |

| Sectio       |         | Electrical Characteristics                  |     |

| 20.1         |         | te Maximum Ratings (H8/538)                 |     |

| 20.2         |         | cal Characteristics (H8/538)                |     |

|              |         | DC Characteristics                          |     |

|              | 20.2.2  | AC Characteristics                          |     |

|              | 20.2.3  | A/D Conversion Characteristics              |     |

| 20.3         |         | te Maximum Ratings (H8/539)                 |     |

| 20.4         |         | al Characteristics (H8/539)                 |     |

|              | 20.4.1  | DC Characteristics                          | 534 |

|              | 20.4.2  | AC Characteristics                          |     |

|              | 20.4.3  | A/D Conversion Characteristics              | 550 |

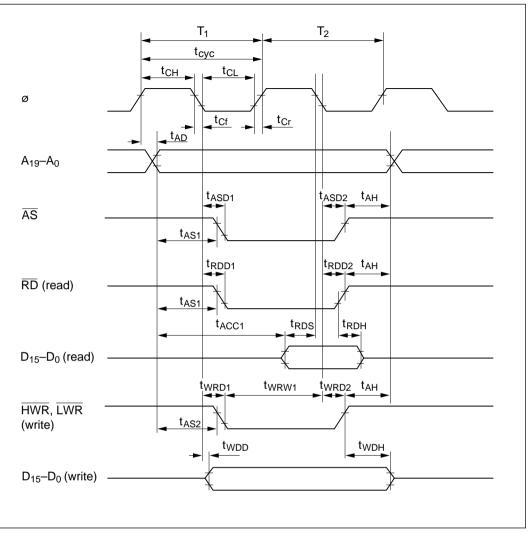

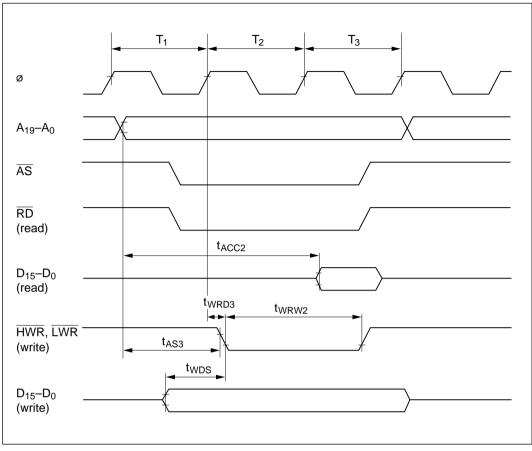

| 20.5         | Operati | onal Timing                                 | 551 |

|              | 20.5.1  | Bus Timing                                  | 551 |

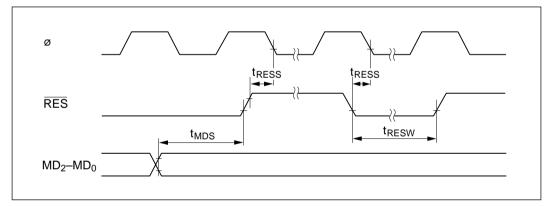

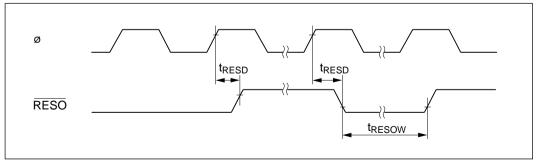

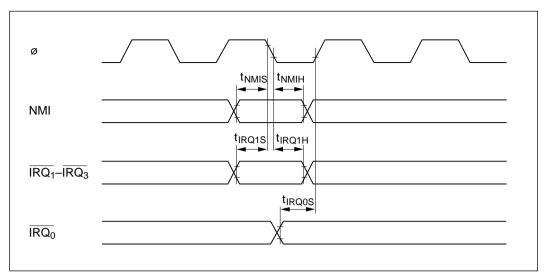

|              | 20.5.2  | Control Signal Timing                       | 555 |

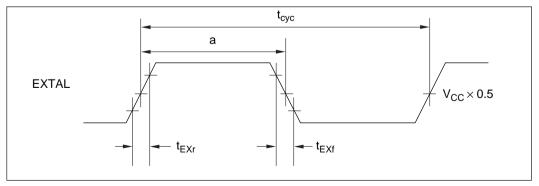

|              | 20.5.3  | Clock Timing                                | 557 |

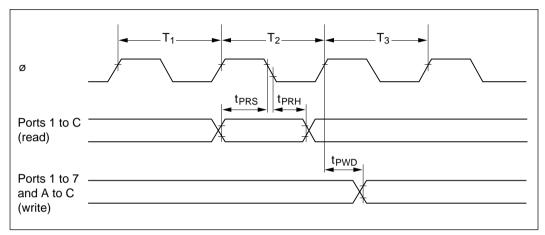

|              | 20.5.4  | I/O Port Timing                             | 558 |

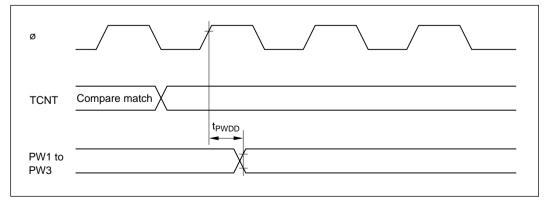

|              | 20.5.5  | PWM Timing                                  | 558 |

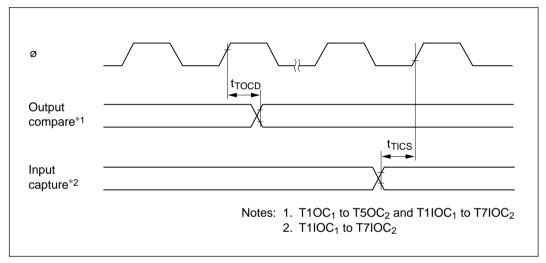

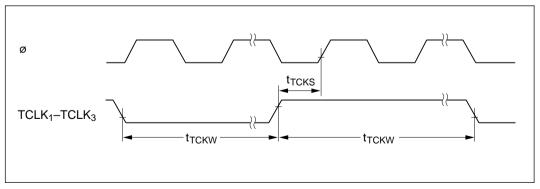

|              | 20.5.6  | IPU Timing                                  | 559 |

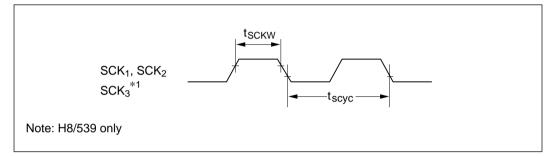

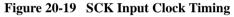

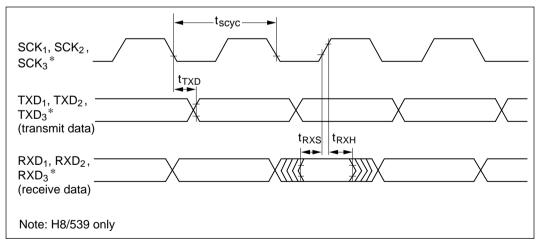

|              | 20.5.7  | SCI Input/Output Timing                     | 560 |

|              | 1. 4    |                                             |     |

|              |         | Instruction Set                             |     |

| A.1          |         | ion List                                    |     |

| A.2          |         | e-Language Instruction Codes                |     |

| A.3          | -       | on Code Map                                 |     |

| A.4          |         | r of States Required for Execution          |     |

| A.5          |         | ion Set                                     |     |

|              | A.5.1   | Features                                    | 595 |

|       | A.5.2     | Instruction Types               | 595 |

|-------|-----------|---------------------------------|-----|

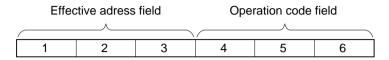

|       | A.5.3     | Basic Instruction Formats       | 596 |

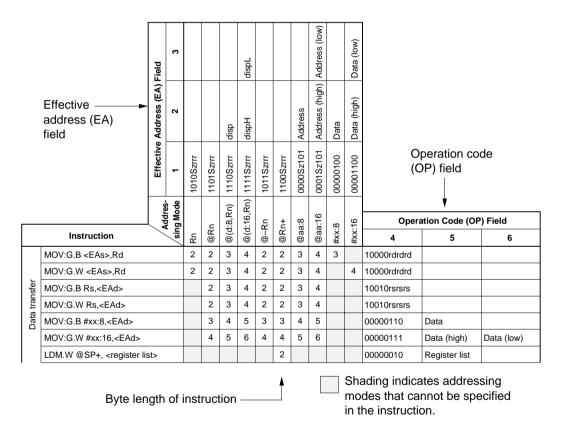

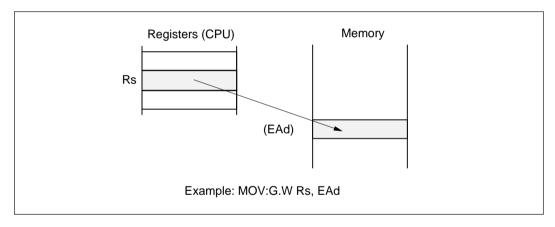

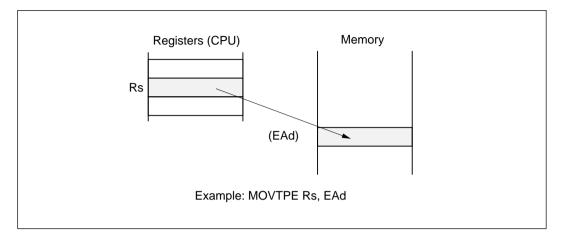

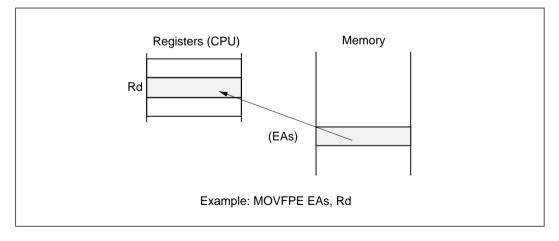

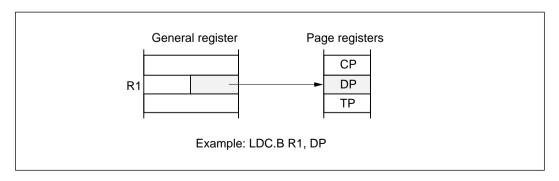

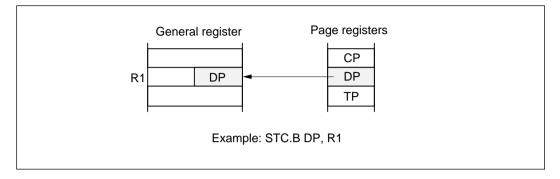

|       | A.5.4     | Data Transfer Instructions      | 597 |

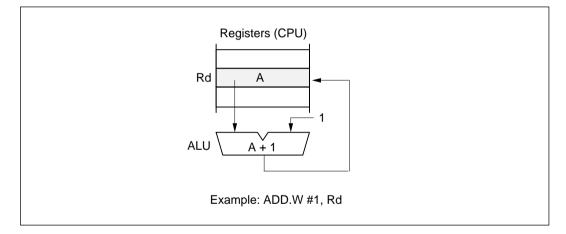

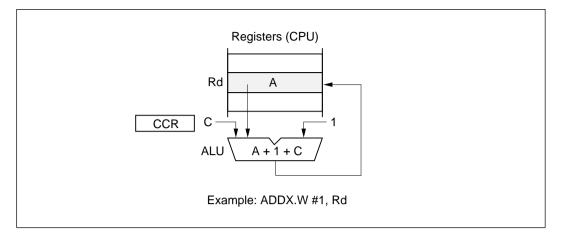

|       | A.5.5     | Arithmetic Instructions         | 601 |

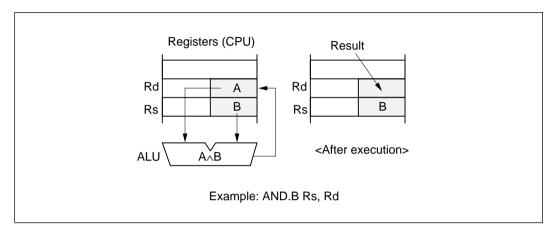

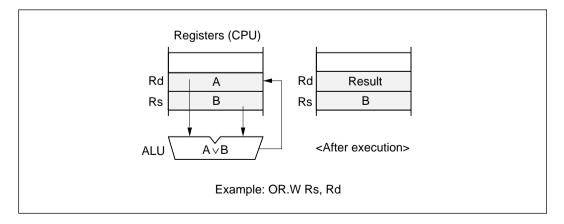

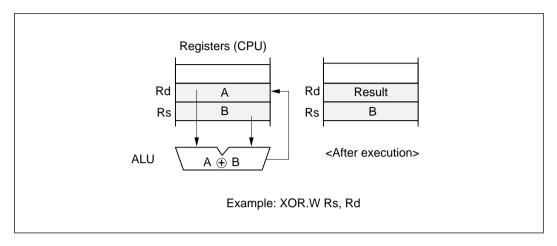

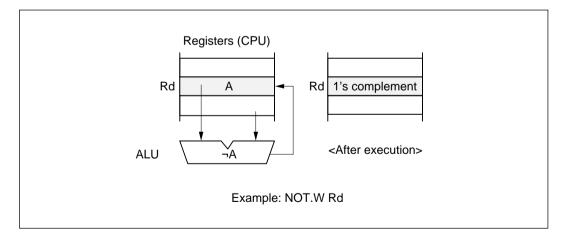

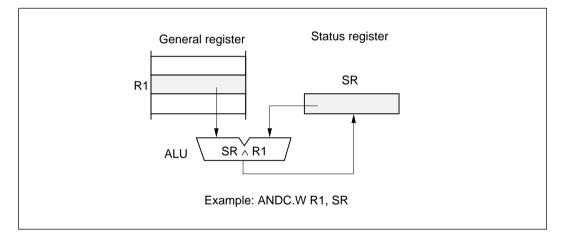

|       | A.5.6     | Logic Instructions              | 608 |

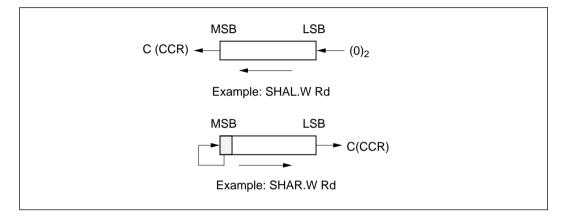

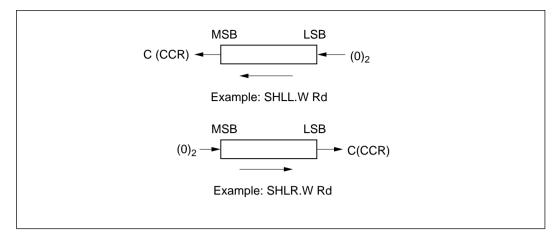

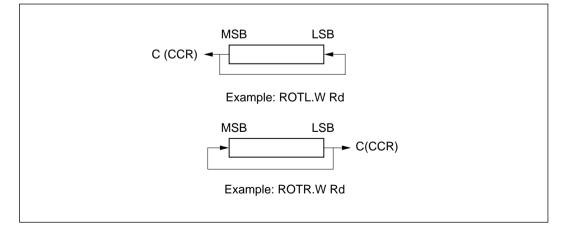

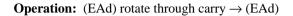

|       | A.5.7     | Shift Instructions              | 610 |

|       | A.5.8     | Bit Manipulation Instructions   | 612 |

|       | A.5.9     | Branch Instructions             | 615 |

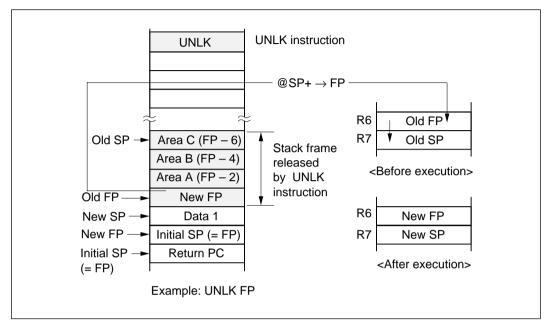

|       | A.5.10    | System Control Instructions     | 623 |

|       | A.5.11    | Short-Format Instructions       | 630 |

| Appe  | ndix B    | Initial Values of CPU Registers | 631 |

| Appe  | ndix C    | On-Chip Registers               | 632 |

| Appe  | ndix D    | Pin Function Selection          | 652 |

| D.1   | Port 3 F  | unction Selection               | 652 |

| D.2   | Port 4 F  | unction Selection               | 653 |

| D.3   | Port 5 F  | unction Selection               | 655 |

| D.4   | Port 6 F  | unction Selection               | 657 |

| D.5   | Port 7 F  | unction Selection               | 658 |

| D.6   | Port A F  | Function Selection              | 660 |

| Appe  | ndix E    | I/O Port Block Diagrams         | 665 |

| Apper | ndix F    | Memory Maps                     | 691 |

| F.1   | H8/538    |                                 | 691 |

| F.2   | H8/539    |                                 | 692 |

| Appe  | ndix G    | Pin States                      | 693 |

| G.1   |           | f I/O Ports                     | 693 |

| G.2   | Pin State | es at Reset                     | 694 |

| Appe  | ndix H    | Package Dimensions              | 699 |

# Section 1 Overview

# **1.1 Features**

The H8/538 and H8/539 are CMOS microcontroller units (MCUs) with an original Hitachi architecture. Each consists of an H8/500 CPU core plus supporting functions required in system configurations.

The H8/500 CPU features a highly orthogonal instruction set that permits addressing modes and data sizes to be specified independently in each instruction. An internal 16-bit architecture and 16-bit, two-state access to both on-chip memory and external memory enhance the CPU's data-processing capability and provide the speed needed for realtime control applications.

The on-chip supporting functions include RAM, ROM, timers, a serial communication interface (SCI), A/D converter, and I/O ports. An on-chip data transfer controller (DTC) provides an efficient way to transfer data in either direction between memory and I/O without using the CPU.

For on-chip ROM, a choice is offered between mask-programmable ROM and electrically programmable ROM (PROM). The PROM version can be programmed by the user with a general-purpose PROM programmer.

Table 1-1 lists the main features of the H8/538 and H8/539.

| Feature    | Description                                                                                                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H8/500 CPU | General-register machine <ul> <li>Eight 16-bit general registers</li> <li>Five 8-bit and two 16-bit control registers</li> </ul>                                                                 |

|            | <ul> <li>High-speed operation</li> <li>Maximum clock rate (H8/538): 10 MHz (oscillator frequency: 20 MHz)</li> <li>Maximum clock rate (H8/539): 16 MHz (oscillator frequency: 16 MHz)</li> </ul> |

|            | <ul><li>Two operating modes</li><li>Minimum mode: maximum 64-kbyte address space</li><li>Maximum mode: maximum 1-Mbyte address space</li></ul>                                                   |

|            | <ul><li>Highly orthogonal instruction set</li><li>Addressing modes and data size can be specified independently for each instruction</li></ul>                                                   |

|            | <ul><li>Register and memory addressing modes</li><li>Register-register operations</li><li>Register-memory (or memory-register) operations</li></ul>                                              |

|            | <ul> <li>Instruction set optimized for C language</li> <li>Special short formats for frequently-used instructions and addressing modes</li> </ul>                                                |

## Table 1-1 Features

## Table 1-1 Features (cont)

| Feature                                 | Description                                                                                                                                                                                                                                    |                                                                              |                              |  |  |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------|--|--|--|

| Memory                                  | H8/538 <ul> <li>2-kbyte high-speed on-chip RAM</li> <li>60-kbyte on-chip electrically programmable ROM or masked ROM</li> </ul>                                                                                                                |                                                                              |                              |  |  |  |

|                                         | H8/539<br>• 4-kbyte high-spee<br>• 128-kbyte on-chip                                                                                                                                                                                           | d on-chip RAM<br>electrically programmable                                   | e ROM or masked ROM          |  |  |  |

| 16-bit integrated-                      | Pulse unit with sever                                                                                                                                                                                                                          | n 16-bit timer channels                                                      |                              |  |  |  |

| timer pulse unit<br>(IPU)               | Channel                                                                                                                                                                                                                                        | Compare Registers                                                            | Compare/Capture<br>Registers |  |  |  |

|                                         | Channel 1                                                                                                                                                                                                                                      | 4                                                                            | 4                            |  |  |  |

|                                         | Channels 2 to 5                                                                                                                                                                                                                                | 2                                                                            | 2                            |  |  |  |

|                                         | Channels 6 & 7                                                                                                                                                                                                                                 | _                                                                            | 2                            |  |  |  |

|                                         | <ul> <li>Clock source can be selected independently for each channel</li> <li>Thirteen internal clock sources</li> <li>Three external clock sources</li> <li>Two counting modes</li> <li>Free-running timer</li> <li>Interval timer</li> </ul> |                                                                              |                              |  |  |  |

|                                         | Three types of pulse output<br>• One-shot output<br>• Toggle output<br>• PWM output                                                                                                                                                            |                                                                              |                              |  |  |  |

|                                         | <ul><li>Automatic measurement functions</li><li>Programmable period counting</li><li>Phase counting</li></ul>                                                                                                                                  |                                                                              |                              |  |  |  |

|                                         | <ul><li>Synchronization function</li><li>Counters on different channels can be synchronized</li></ul>                                                                                                                                          |                                                                              |                              |  |  |  |

| Serial communication<br>interface (SCI) | <ul> <li>Asynchronous or clocked synchronous mode (selectable)</li> <li>Full duplex: can send and receive simultaneously</li> <li>On-chip baud rate generator</li> <li>Multiprocessor communication function (asynchronous mode)</li> </ul>    |                                                                              |                              |  |  |  |

| A/D converter                           |                                                                                                                                                                                                                                                | single mode or scan mode<br>externally, or by IPU comp<br>e conversion range |                              |  |  |  |

#### Feature Description 74 input/output pins I/O ports 12 input-only pins Interrupt controller Five external interrupt pins (NMI, IRQ<sub>0</sub> to IRQ<sub>3</sub>) · Thirty-nine internal interrupt sources (INTC) Eight programmable priority levels Data transfer Can transfer data in both directions between memory and I/O controller (DTC) without using the CPU Can insert wait states (T<sub>W</sub>) in access to external I/O or memory Wait-state controller (WSC) Bus controller (BSC) Address space can be partitioned into 16-bit-bus and 8-bit-bus areas Address space can be partitioned into two-state-access and threestate-access areas I/O ports can be expanded and reconfigured Operating modes Seven operating modes 1. High-speed 16-bit bus modes, starting in 2-state 16-bit mode at reset Expanded minimum mode (mode 1) Expanded maximum modes (modes 3 and 4) 2. Low-speed 16-bit bus modes, starting in 3-state 8-bit mode at reset • Expanded minimum mode (mode 6) Expanded maximum mode (mode 5) 3. Low-speed 8-bit bus mode Expanded minimum mode (mode 2) 4. Single-chip mode H8/539 Maximum mode (mode 7) H8/538 Minimum mode (mode 7) Power-down state Three power-down modes Sleep mode Software standby mode · Hardware standby mode Watchdog timer Timer overflow can generate reset output (WDT) Also usable as an interval timer PWM timer\* Duty cycle: 0% to 100% Resolution: 1/250 Multiplier\* 16 bit × 16 bit signed or unsigned multiplication (H8MULT) Multiply-accumulate: 32 bits (saturating); 42 bits (non-saturating) On-chip clock oscillator Other features

#### Table 1-1 Features (cont)

Note: \* H8/539 only.

## Table 1-1 Features (cont)

| Description |                                                 |                                                                                                                                                                                                     |

|-------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Model       | Package                                         | ROM                                                                                                                                                                                                 |

| HD6475388F  | 112-pin plastic QFP (FP-112)                    | PROM                                                                                                                                                                                                |

| HD6435388F  | 112-pin plastic QFP (FP-112)                    | Masked ROM                                                                                                                                                                                          |

| HD6475398F  | 112-pin plastic QFP (FP-112)                    | PROM                                                                                                                                                                                                |

| HD6435398F  | 112-pin plastic QFP (FP-112)                    | Masked ROM                                                                                                                                                                                          |

|             | Model<br>HD6475388F<br>HD6435388F<br>HD6475398F | Model         Package           HD6475388F         112-pin plastic QFP (FP-112)           HD6435388F         112-pin plastic QFP (FP-112)           HD6475398F         112-pin plastic QFP (FP-112) |

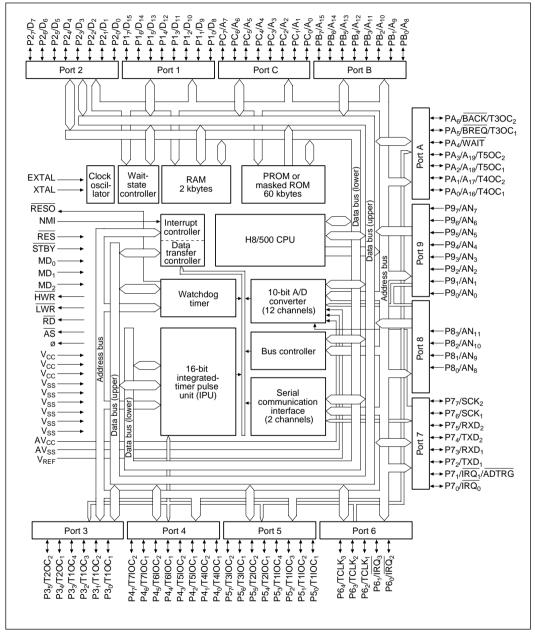

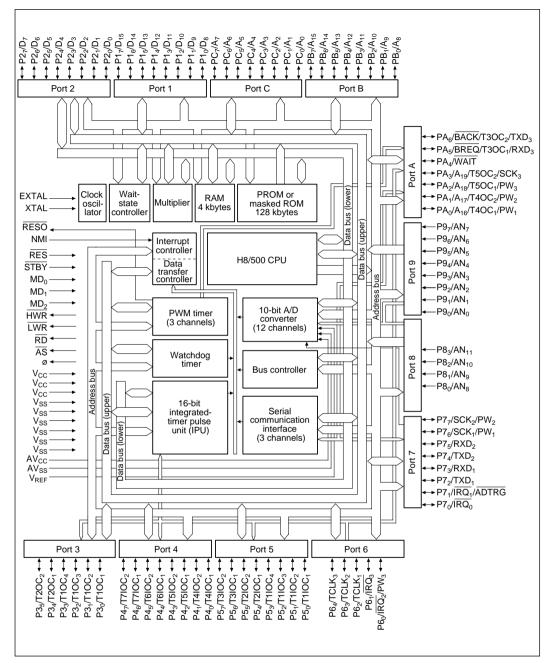

# 1.2 Block Diagram

Figures 1-1 and 1-2 show block diagrams of the H8/538 and H8/539.

Figure 1-1 H8/538 Block Diagram

Figure 1-2 H8/539 Block Diagram

# **1.3 Pin Descriptions**

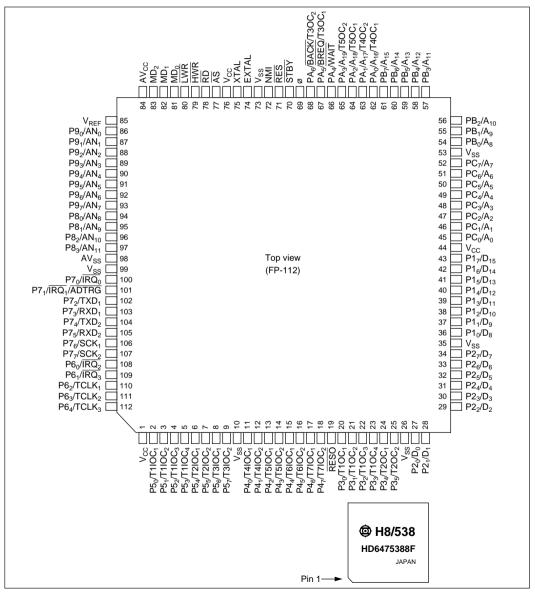

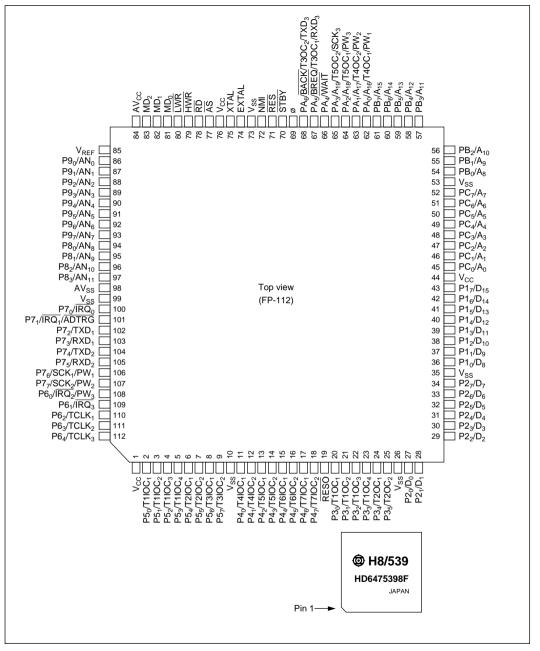

# 1.3.1 Pin Arrangement

Figure 1-3 shows the pin arrangement of the H8/538 (FP-112 package). Figure 1-4 shows the pin arrangement of the H8/539 (FP-112 package).

Figure 1-3 H8/538 Pin Arrangement (FP-112, Top View)

Figure 1-4 H8/539 Pin Arrangement (FP-112, Top View)

#### 1.3.2 Pin Functions

(1) **Pin Assignments in Each Operating Mode:** Table 1-2 lists the assignments of the pins of the FP-112 package in each operating mode. H8/538 and H8/539 pin functions are the same unless otherwise noted.

|     | Expanded Minimum<br>Modes           |                                     | Expanded Maximum<br>Modes           |                                     | Single-Chip<br>Mode                 |                 |

|-----|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-----------------|

| No. | Modes<br>1 and 6                    | Mode 2                              | Modes<br>3 and 5                    | Mode 4                              | Mode 7                              | PROM<br>Mode    |

| 1   | V <sub>CC</sub>                     | V <sub>CC</sub> |

| 2   | P50/T1IOC1                          | P50/T1IOC1                          | P50/T1IOC1                          | P50/T1IOC1                          | P50/T1IOC1                          | NC              |

| 3   | P5 <sub>1</sub> /T1IOC <sub>2</sub> | NC              |

| 4   | P5 <sub>2</sub> /T1IOC <sub>3</sub> | NC              |

| 5   | P5 <sub>3</sub> /T1IOC <sub>4</sub> | NC              |

| 6   | P5 <sub>4</sub> /T2IOC <sub>1</sub> | NC              |

| 7   | P5 <sub>5</sub> /T2IOC <sub>2</sub> | NC              |

| 8   | P5 <sub>6</sub> /T3IOC <sub>1</sub> | NC              |

| 9   | P5 <sub>7</sub> /T3IOC <sub>2</sub> | NC              |

| 10  | V <sub>SS</sub>                     | V <sub>SS</sub> |

| 11  | P4 <sub>0</sub> /T4IOC <sub>1</sub> | P40/T4IOC1                          | P40/T4IOC1                          | P40/T4IOC1                          | P4 <sub>0</sub> /T4IOC <sub>1</sub> | NC              |

| 12  | P4 <sub>1</sub> /T4IOC <sub>2</sub> | NC              |

| 13  | P4 <sub>2</sub> /T5IOC <sub>1</sub> | NC              |

| 14  | P4 <sub>3</sub> /T5IOC <sub>2</sub> | NC              |

| 15  | P4 <sub>4</sub> /T6IOC <sub>1</sub> | NC              |

| 16  | P4 <sub>5</sub> /T6IOC <sub>2</sub> | NC              |

| 17  | P4 <sub>6</sub> /T7IOC <sub>1</sub> | NC              |

| 18  | P47/T7IOC2                          | P4 <sub>7</sub> /T7IOC <sub>2</sub> | P4 <sub>7</sub> /T7IOC <sub>2</sub> | P47/T7IOC2                          | P4 <sub>7</sub> /T7IOC <sub>2</sub> | NC              |

| 19  | RESO                                | RESO                                | RESO                                | RESO                                | RESO                                | V <sub>PP</sub> |

| 20  | P30/T1OC1                           | P3 <sub>0</sub> /T1OC <sub>1</sub>  | P3 <sub>0</sub> /T1OC <sub>1</sub>  | P30/T1OC1                           | P3 <sub>0</sub> /T1OC <sub>1</sub>  | NC              |

| 21  | P31/T1OC2                           | P3 <sub>1</sub> /T1OC <sub>2</sub>  | P3 <sub>1</sub> /T1OC <sub>2</sub>  | P31/T1OC2                           | P3 <sub>1</sub> /T1OC <sub>2</sub>  | NC              |

| 22  | P3 <sub>2</sub> /T1OC <sub>3</sub>  | NC              |

| 23  | P3 <sub>3</sub> /T1OC <sub>4</sub>  | NC              |

#### Table 1-2 Pin Assignments in Each Operating Mode (FP-112)

Notes: 1. For the PROM mode, see section 18, "ROM."

2. Pins marked NC should be left unconnected.

|     | Expanded Minimum<br>Modes          |                                    | Expanded<br>Modes                  | d Maximum                          | Single-Chip<br>Mode                |                 |

|-----|------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|-----------------|

| No. | Modes<br>1 and 6                   | Mode 2                             | Modes<br>3 and 5                   | Mode 4                             | Mode 7                             | PROM<br>Mode    |

| 24  | P3 <sub>4</sub> /T2OC <sub>1</sub> | NC              |

| 25  | P3 <sub>5</sub> /T2OC <sub>2</sub> | NC              |

| 26  | V <sub>SS</sub>                    | V <sub>SS</sub> |

| 27  | D <sub>0</sub>                     | P2 <sub>0</sub>                    | D <sub>0</sub>                     | D <sub>0</sub>                     | P2 <sub>0</sub>                    | NC              |

| 28  | D <sub>1</sub>                     | P2 <sub>1</sub>                    | D <sub>1</sub>                     | D <sub>1</sub>                     | P2 <sub>1</sub>                    | NC              |

| 29  | D <sub>2</sub>                     | P2 <sub>2</sub>                    | D <sub>2</sub>                     | D <sub>2</sub>                     | P2 <sub>2</sub>                    | NC              |

| 30  | D <sub>3</sub>                     | P2 <sub>3</sub>                    | D <sub>3</sub>                     | D <sub>3</sub>                     | P2 <sub>3</sub>                    | NC              |

| 31  | D <sub>4</sub>                     | P2 <sub>4</sub>                    | D <sub>4</sub>                     | D <sub>4</sub>                     | P2 <sub>4</sub>                    | NC              |

| 32  | $D_5$                              | P2 <sub>5</sub>                    | $D_5$                              | D <sub>5</sub>                     | P2 <sub>5</sub>                    | NC              |

| 33  | D <sub>6</sub>                     | P2 <sub>6</sub>                    | D <sub>6</sub>                     | D <sub>6</sub>                     | P2 <sub>6</sub>                    | NC              |

| 34  | D <sub>7</sub>                     | P2 <sub>7</sub>                    | D <sub>7</sub>                     | D <sub>7</sub>                     | P2 <sub>7</sub>                    | NC              |

| 35  | V <sub>SS</sub>                    | V <sub>SS</sub> |

| 36  | D <sub>8</sub>                     | D <sub>8</sub>                     | D <sub>8</sub>                     | D <sub>8</sub>                     | P1 <sub>0</sub>                    | O <sub>0</sub>  |

| 37  | D <sub>9</sub>                     | D <sub>9</sub>                     | D <sub>9</sub>                     | D <sub>9</sub>                     | P1 <sub>1</sub>                    | 0 <sub>1</sub>  |

| 38  | D <sub>10</sub>                    | D <sub>10</sub>                    | D <sub>10</sub>                    | D <sub>10</sub>                    | P1 <sub>2</sub>                    | O <sub>2</sub>  |

| 39  | D <sub>11</sub>                    | D <sub>11</sub>                    | D <sub>11</sub>                    | D <sub>11</sub>                    | P1 <sub>3</sub>                    | O <sub>3</sub>  |

| 40  | D <sub>12</sub>                    | D <sub>12</sub>                    | D <sub>12</sub>                    | D <sub>12</sub>                    | P1 <sub>4</sub>                    | O <sub>4</sub>  |

| 41  | D <sub>13</sub>                    | D <sub>13</sub>                    | D <sub>13</sub>                    | D <sub>13</sub>                    | P1 <sub>5</sub>                    | O <sub>5</sub>  |

| 42  | D <sub>14</sub>                    | D <sub>14</sub>                    | D <sub>14</sub>                    | D <sub>14</sub>                    | P1 <sub>6</sub>                    | O <sub>6</sub>  |

| 43  | D <sub>15</sub>                    | D <sub>15</sub>                    | D <sub>15</sub>                    | D <sub>15</sub>                    | P1 <sub>7</sub>                    | 0 <sub>7</sub>  |

| 44  | V <sub>CC</sub>                    | $V_{CC}$        |

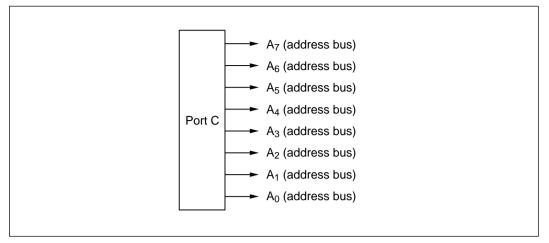

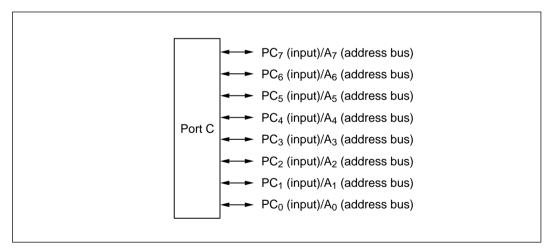

| 45  | A <sub>0</sub>                     | PC <sub>0</sub> /A <sub>0</sub>    | A <sub>0</sub>                     | PC <sub>0</sub> /A <sub>0</sub>    | PC <sub>0</sub>                    | A <sub>0</sub>  |

| 46  | A <sub>1</sub>                     | PC <sub>1</sub> /A <sub>1</sub>    | A <sub>1</sub>                     | PC <sub>1</sub> /A <sub>1</sub>    | PC <sub>1</sub>                    | A <sub>1</sub>  |

| 47  | A <sub>2</sub>                     | PC <sub>2</sub> /A <sub>2</sub>    | A <sub>2</sub>                     | PC <sub>2</sub> /A <sub>2</sub>    | PC <sub>2</sub>                    | A <sub>2</sub>  |

| 48  | A <sub>3</sub>                     | PC <sub>3</sub> /A <sub>3</sub>    | A <sub>3</sub>                     | PC <sub>3</sub> /A <sub>3</sub>    | PC <sub>3</sub>                    | A <sub>3</sub>  |

| 49  | A <sub>4</sub>                     | PC <sub>4</sub> /A <sub>4</sub>    | A <sub>4</sub>                     | PC <sub>4</sub> /A <sub>4</sub>    | PC <sub>4</sub>                    | A <sub>4</sub>  |

| 50  | A <sub>5</sub>                     | PC <sub>5</sub> /A <sub>5</sub>    | A <sub>5</sub>                     | PC <sub>5</sub> /A <sub>5</sub>    | PC <sub>5</sub>                    | $A_5$           |

## Table 1-2 Pin Assignments in Each Operating Mode (FP-112) (cont)

Notes: 1. For the PROM mode, see section 18, "ROM."

2. Pins marked NC should be left unconnected.

| Expanded<br>Modes |                                                                         | l Minimum                                                                     | Expanded<br>Modes                                                                          | d Maximum                                                                                   | Single-Chip<br>Mode                                                     |                 |

|-------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|

| No.               | Modes<br>1 and 6                                                        | Mode 2                                                                        | Modes<br>3 and 5                                                                           | Mode 4                                                                                      | Mode 7                                                                  | PROM<br>Mode    |

| 51                | A <sub>6</sub>                                                          | PC <sub>6</sub> /A <sub>6</sub>                                               | A <sub>6</sub>                                                                             | PC <sub>6</sub> /A <sub>6</sub>                                                             | PC <sub>6</sub>                                                         | A <sub>6</sub>  |

| 52                | A <sub>7</sub>                                                          | PC <sub>7</sub> /A <sub>7</sub>                                               | A <sub>7</sub>                                                                             | PC <sub>7</sub> /A <sub>7</sub>                                                             | PC <sub>7</sub>                                                         | A <sub>7</sub>  |

| 53                | V <sub>SS</sub>                                                         | V <sub>SS</sub>                                                               | V <sub>SS</sub>                                                                            | V <sub>SS</sub>                                                                             | V <sub>SS</sub>                                                         | V <sub>SS</sub> |

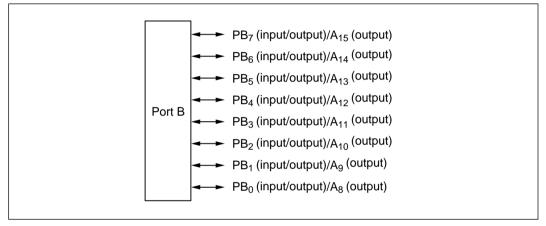

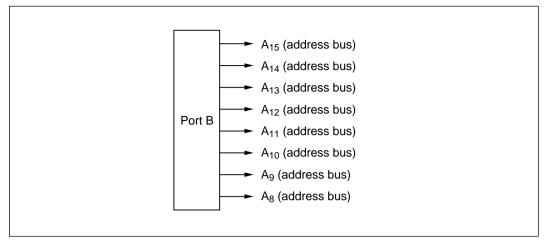

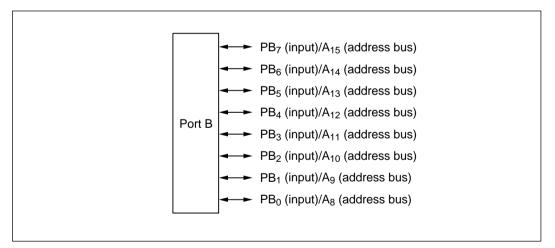

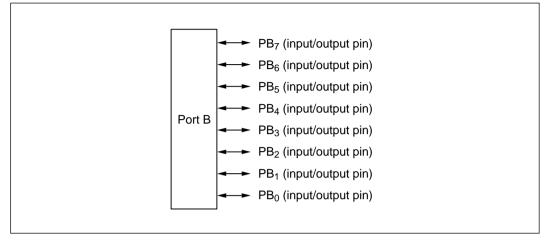

| 54                | A <sub>8</sub>                                                          | PB <sub>0</sub> /A <sub>8</sub>                                               | A <sub>8</sub>                                                                             | PB <sub>0</sub> /A <sub>8</sub>                                                             | PB <sub>0</sub>                                                         | A <sub>8</sub>  |

| 55                | A <sub>9</sub>                                                          | PB <sub>1</sub> /A <sub>9</sub>                                               | A <sub>9</sub>                                                                             | PB <sub>1</sub> /A <sub>9</sub>                                                             | PB <sub>1</sub>                                                         | ŌE              |

| 56                | A <sub>10</sub>                                                         | PB <sub>2</sub> /A <sub>10</sub>                                              | A <sub>10</sub>                                                                            | PB <sub>2</sub> /A <sub>10</sub>                                                            | PB <sub>2</sub>                                                         | A <sub>10</sub> |

| 57                | A <sub>11</sub>                                                         | PB <sub>3</sub> /A <sub>11</sub>                                              | A <sub>11</sub>                                                                            | PB <sub>3</sub> /A <sub>11</sub>                                                            | PB <sub>3</sub>                                                         | A <sub>11</sub> |

| 58                | A <sub>12</sub>                                                         | PB <sub>4</sub> /A <sub>12</sub>                                              | A <sub>12</sub>                                                                            | PB <sub>4</sub> /A <sub>12</sub>                                                            | PB <sub>4</sub>                                                         | A <sub>12</sub> |

| 59                | A <sub>13</sub>                                                         | PB <sub>5</sub> /A <sub>13</sub>                                              | A <sub>13</sub>                                                                            | PB <sub>5</sub> /A <sub>13</sub>                                                            | PB <sub>5</sub>                                                         | A <sub>13</sub> |

| 60                | A <sub>14</sub>                                                         | PB <sub>6</sub> /A <sub>14</sub>                                              | A <sub>14</sub>                                                                            | PB <sub>6</sub> /A <sub>14</sub>                                                            | PB <sub>6</sub>                                                         | A <sub>14</sub> |

| 61                | A <sub>15</sub>                                                         | PB <sub>7</sub> /A <sub>15</sub>                                              | A <sub>15</sub>                                                                            | PB <sub>7</sub> /A <sub>15</sub>                                                            | PB <sub>7</sub>                                                         | CE              |

| 62                | PA <sub>0</sub> /T4OC <sub>1</sub> /<br>PW <sub>1</sub> *3              | PA <sub>0</sub> /T4OC <sub>1</sub> /<br>PW <sub>1</sub> <sup>*3</sup>         | A <sub>16</sub>                                                                            | PA <sub>0</sub> /A <sub>16</sub> /<br>PW <sub>1</sub> * <sup>3</sup>                        | PA <sub>0</sub> /T4OC <sub>1</sub> /<br>PW <sub>1</sub> * <sup>3</sup>  | V <sub>CC</sub> |

| 63                | PA <sub>1</sub> /T4OC <sub>2</sub> /<br>PW <sub>2</sub> *3              | PA <sub>1</sub> /T4OC <sub>2</sub> /<br>PW <sub>2</sub> *3                    | A <sub>17</sub>                                                                            | PA <sub>1</sub> /A <sub>17</sub> /<br>PW <sub>2</sub> * <sup>3</sup>                        | PA <sub>1</sub> /T4OC <sub>2</sub> /<br>PW <sub>2</sub> <sup>*3</sup>   | V <sub>CC</sub> |

| 64                | PA <sub>2</sub> /T5OC <sub>1</sub> /<br>PW <sub>3</sub> *3              | PA <sub>2</sub> /T5OC <sub>1</sub> /<br>PW <sub>3</sub> <sup>*3</sup>         | A <sub>18</sub>                                                                            | PA <sub>2</sub> /A <sub>18</sub> /<br>PW <sub>3</sub> <sup>*3</sup>                         | PA <sub>2</sub> /T5OC <sub>1</sub> /<br>PW <sub>3</sub> <sup>*3</sup>   | NC              |

| 65                | PA <sub>3</sub> /T5OC <sub>2</sub> /<br>SCK <sub>3</sub> * <sup>3</sup> | PA <sub>3</sub> /T5OC <sub>2</sub> /<br>SCK <sub>3</sub> * <sup>3</sup>       | A <sub>19</sub>                                                                            | PA <sub>3</sub> /A <sub>19</sub> /<br>SCK <sub>3</sub> *3                                   | PA <sub>3</sub> /T5OC <sub>2</sub> /<br>SCK <sub>3</sub> * <sup>3</sup> | NC              |

| 66                | PA <sub>4</sub> /WAIT                                                   | PA <sub>4</sub> /WAIT                                                         | PA <sub>4</sub> /WAIT                                                                      | PA <sub>4</sub> /WAIT                                                                       | PA <sub>4</sub>                                                         | A <sub>16</sub> |

| 67                | PA <sub>5</sub> /BREQ/<br>T3OC <sub>1</sub> /RXD <sub>3</sub>           | PA <sub>5</sub> /BREQ/<br>* <sup>3</sup> T3OC <sub>1</sub> /RXD <sub>3</sub>  | PA <sub>5</sub> /BREQ/<br>*3T3OC <sub>1</sub> /RXD <sub>3</sub>                            | PA <sub>5</sub> /BREQ/<br>3 <sup>*3</sup> T3OC <sub>1</sub> /RXD <sub>3</sub> *3            | PA <sub>5</sub> /T3OC <sub>1</sub> /<br>RXD <sub>3</sub> * <sup>3</sup> | NC              |

| 68                | PA <sub>6</sub> /BACK/<br>T3OC <sub>2</sub> /TXD <sub>3</sub> *         | PA <sub>6</sub> /BACK/<br><sup>*3</sup> T3OC <sub>2</sub> /TXD <sub>3</sub> * | PA <sub>6</sub> / <mark>BACK</mark> /<br><sup>*3</sup> T3OC <sub>2</sub> /TXD <sub>3</sub> | PA <sub>6</sub> /BACK/<br>* <sup>3</sup> T3OC <sub>2</sub> /TXD <sub>3</sub> * <sup>3</sup> | PA <sub>6</sub> /T3OC <sub>2</sub> /<br>TXD <sub>3</sub> *3             | NC              |

| 69                | Ø                                                                       | Ø                                                                             | Ø                                                                                          | Ø                                                                                           | Ø                                                                       | NC              |

| 70                | STBY                                                                    | STBY                                                                          | STBY                                                                                       | STBY                                                                                        | STBY                                                                    | $V_{SS}$        |

| 71                | RES                                                                     | RES                                                                           | RES                                                                                        | RES                                                                                         | RES                                                                     | V <sub>SS</sub> |

| 72                | NMI                                                                     | NMI                                                                           | NMI                                                                                        | NMI                                                                                         | NMI                                                                     | A <sub>9</sub>  |

| Table 1-2 | Pin Assignments in Each | <b>Operating Mode (FP-112) (cont)</b> |

|-----------|-------------------------|---------------------------------------|

|-----------|-------------------------|---------------------------------------|

Notes: 1. For the PROM mode, see section 18, "ROM."

2. Pins marked NC should be left unconnected.

3. In the H8/538, port A does not have the  $\mathsf{PW}_1$  to  $\mathsf{PW}_3,\,\mathsf{SCK}_3,\,\mathsf{RXD}_3,\,\mathsf{and}\,\mathsf{TXD}_3$  functions.

|     | Expanded Minimum<br>Modes         |                                   | Expande<br>Modes                  | Expanded Maximum<br>Modes         |                                   |                 |

|-----|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------|

| No. | Modes<br>1 and 6                  | Mode 2                            | Modes<br>3 and 5                  | Mode 4                            | Mode 7                            | PROM<br>Mode    |

| 73  | V <sub>SS</sub>                   | V <sub>SS</sub> |

| 74  | EXTAL                             | EXTAL                             | EXTAL                             | EXTAL                             | EXTAL                             | NC              |

| 75  | XTAL                              | XTAL                              | XTAL                              | XTAL                              | XTAL                              | NC              |

| 76  | V <sub>CC</sub>                   | V <sub>CC</sub> |

| 77  | ĀS                                | AS                                | AS                                | ĀS                                | ĀS                                | NC              |

| 78  | RD                                | RD                                | RD                                | RD                                | RD                                | NC              |

| 79  | HWR                               | HWR                               | HWR                               | HWR                               | HWR                               | NC              |

| 80  | LWR                               | LWR                               | LWR                               | LWR                               | LWR                               | NC              |

| 81  | MD <sub>0</sub>                   | V <sub>SS</sub> |

| 82  | MD <sub>1</sub>                   | $V_{SS}$        |

| 83  | MD <sub>2</sub>                   | MD <sub>2</sub>                   | $MD_2$                            | MD <sub>2</sub>                   | MD <sub>2</sub>                   | $V_{SS}$        |

| 84  | AV <sub>CC</sub>                  | V <sub>CC</sub> |

| 85  | V <sub>REF</sub>                  | V <sub>CC</sub> |

| 86  | P9 <sub>0</sub> /AN <sub>0</sub>  | NC              |

| 87  | P9 <sub>1</sub> /AN <sub>1</sub>  | NC              |

| 88  | P9 <sub>2</sub> /AN <sub>2</sub>  | NC              |

| 89  | P9 <sub>3</sub> /AN <sub>3</sub>  | NC              |

| 90  | P9 <sub>4</sub> /AN <sub>4</sub>  | NC              |

| 91  | P9 <sub>5</sub> /AN <sub>5</sub>  | NC              |

| 92  | P9 <sub>6</sub> /AN <sub>6</sub>  | NC              |

| 93  | P9 <sub>7</sub> /AN <sub>7</sub>  | NC              |

| 94  | P8 <sub>0</sub> /AN <sub>8</sub>  | NC              |

| 95  | P8 <sub>1</sub> /AN <sub>9</sub>  | NC              |

| 96  | P8 <sub>2</sub> /AN <sub>10</sub> | NC              |

| 97  | P8 <sub>3</sub> /AN <sub>11</sub> | NC              |

| 98  | AV <sub>SS</sub>                  | $V_{SS}$        |

| 99  | V <sub>SS</sub>                   | $V_{SS}$        |

Table 1-2

Pin Assignments in Each Operating Mode (FP-112) (cont)

Notes: 1. For the PROM mode, see section 18, "ROM."

2. Pins marked NC should be left unconnected.

|     | Expanded Minimum<br>Modes                                 |                                                                       | Expanded Maximum<br>Modes                                 |                                                                       | Single-Chip<br>Mode                                       |                 |

|-----|-----------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------|-----------------|

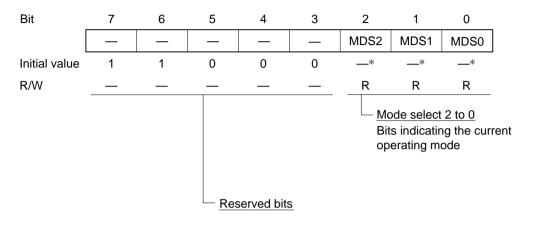

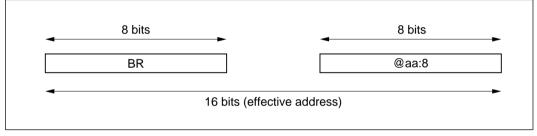

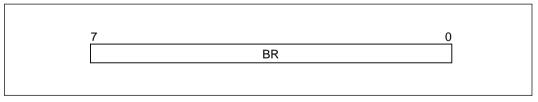

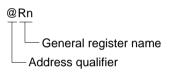

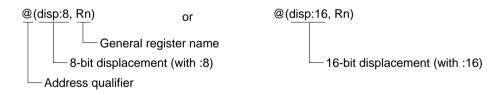

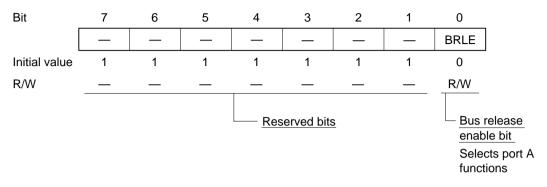

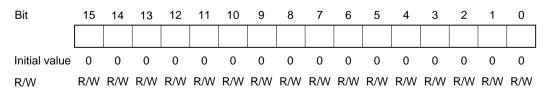

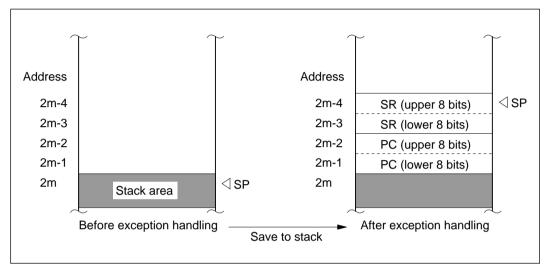

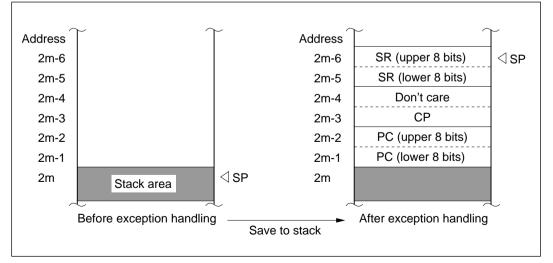

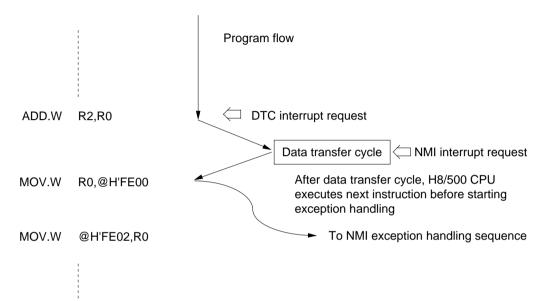

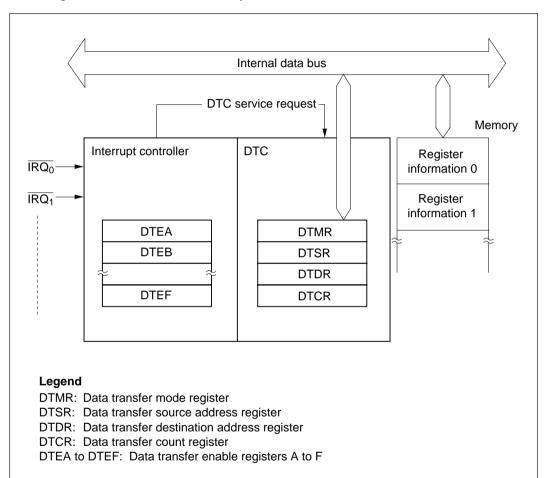

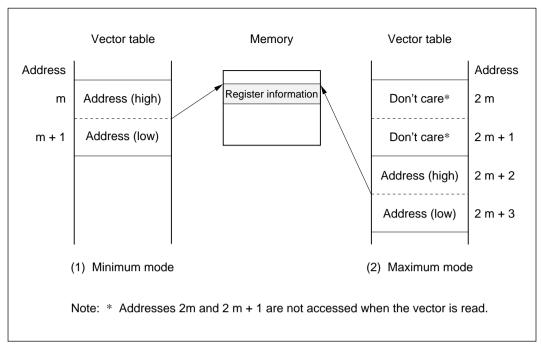

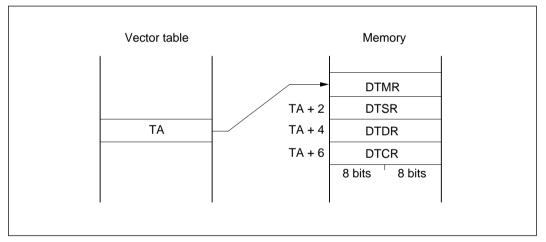

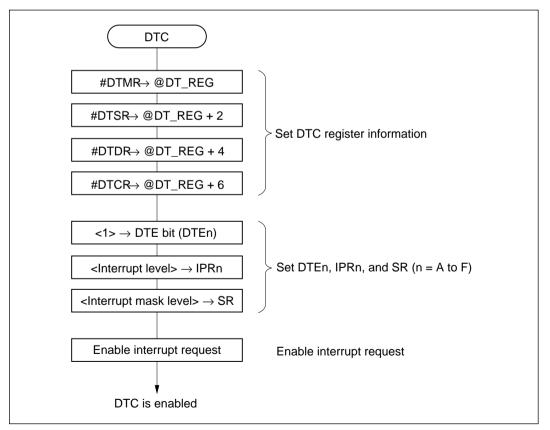

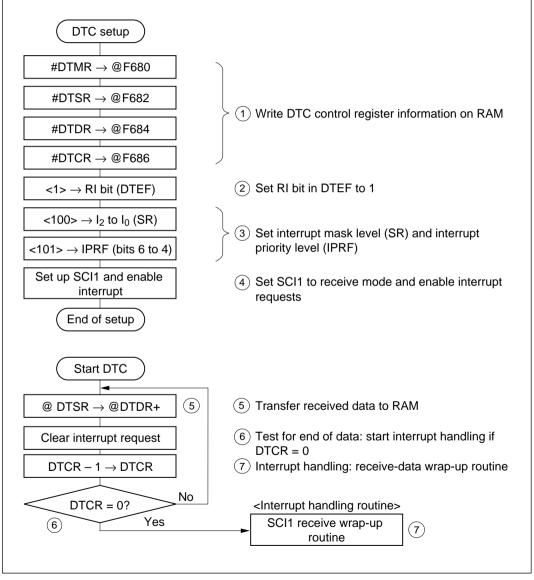

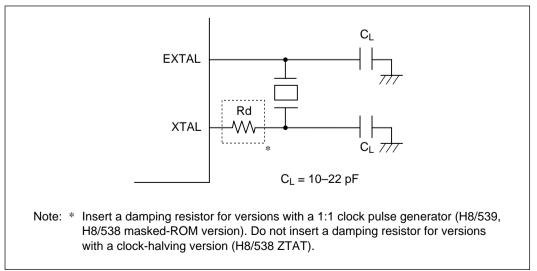

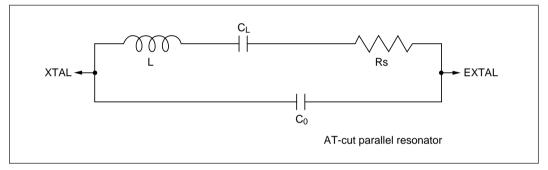

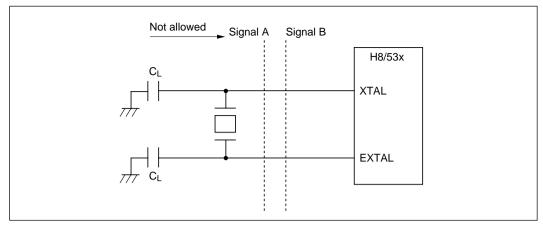

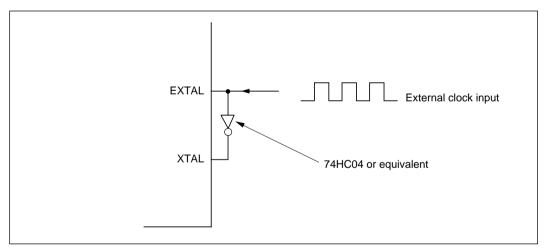

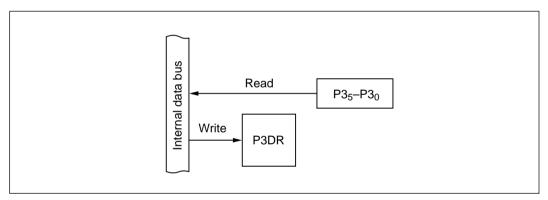

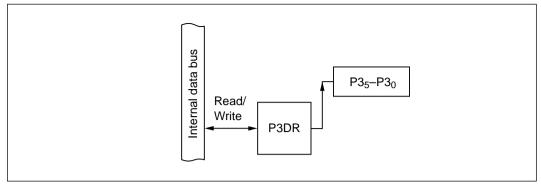

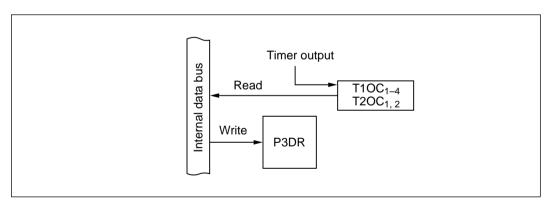

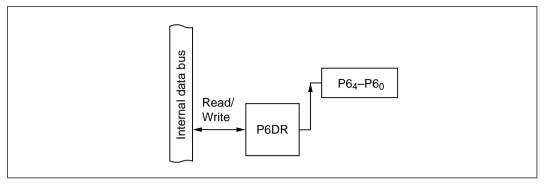

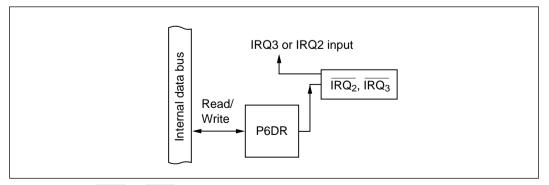

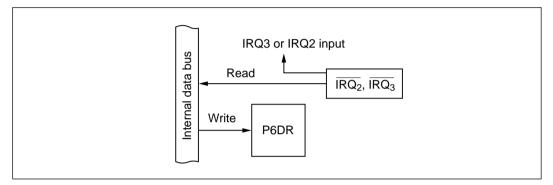

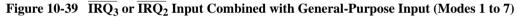

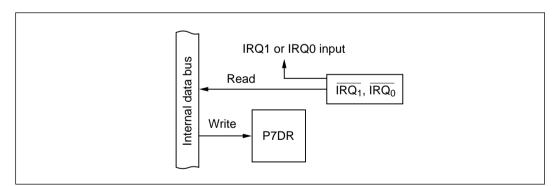

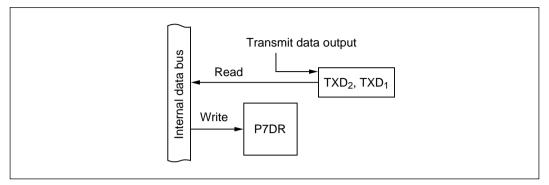

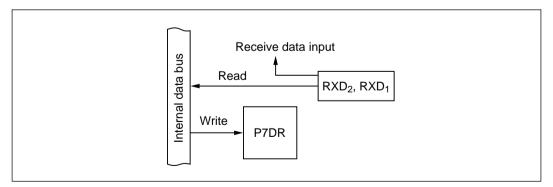

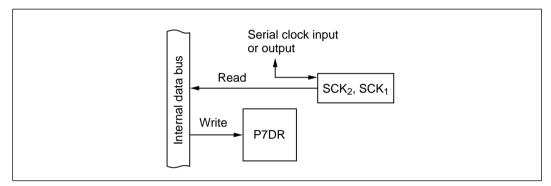

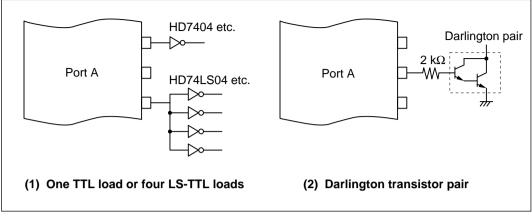

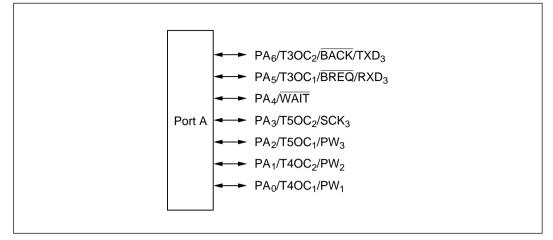

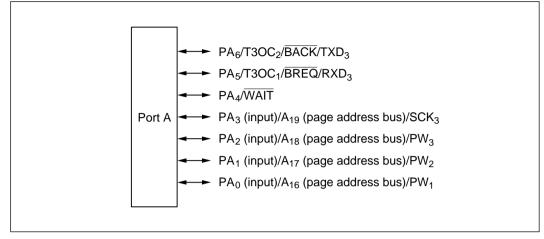

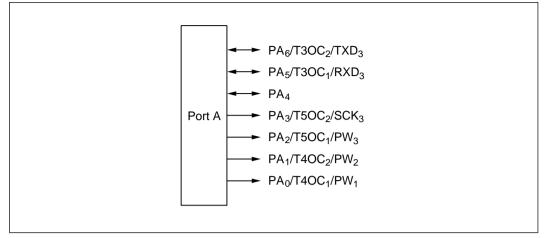

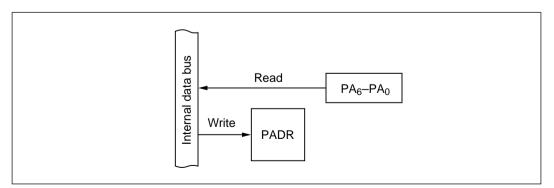

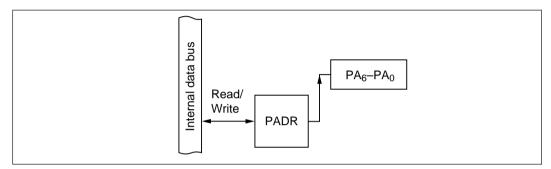

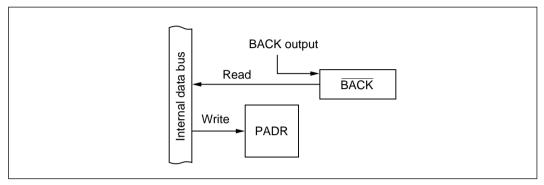

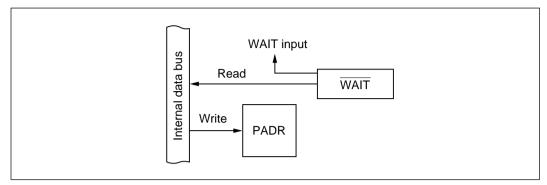

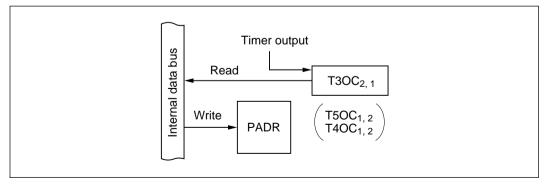

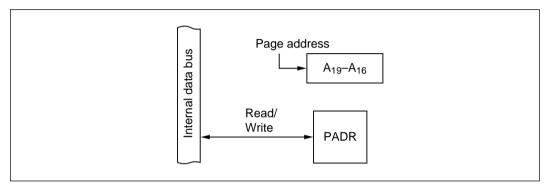

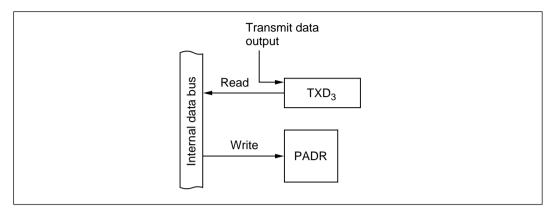

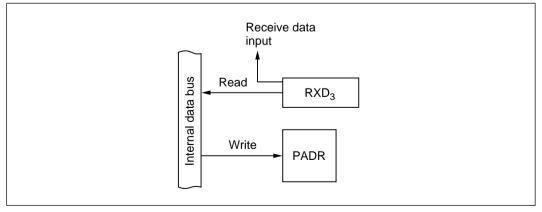

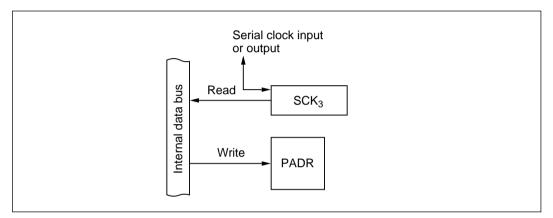

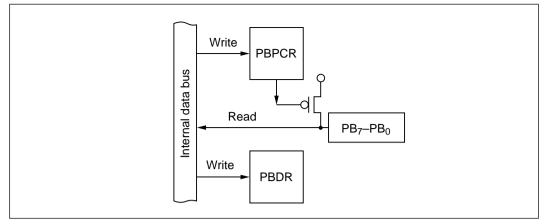

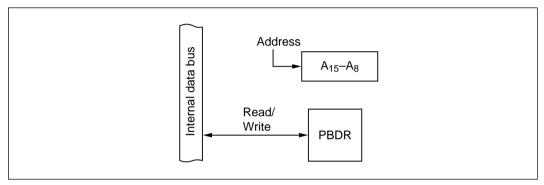

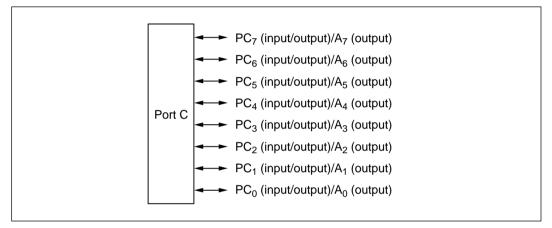

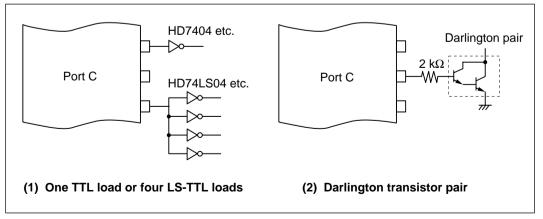

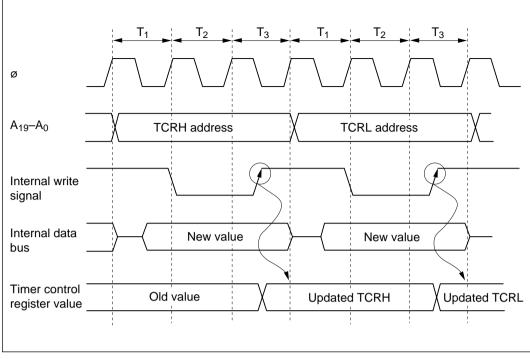

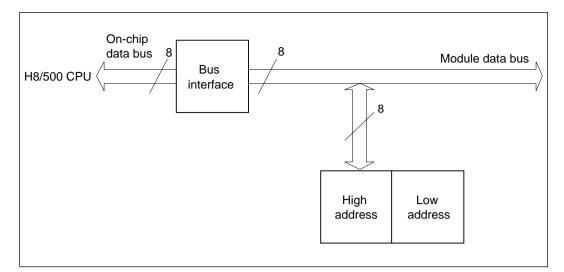

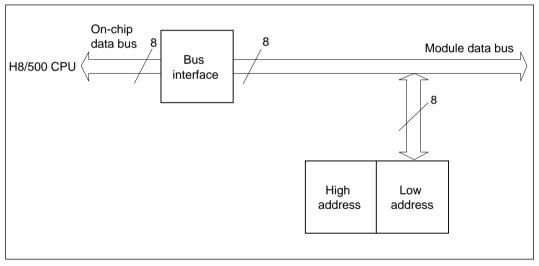

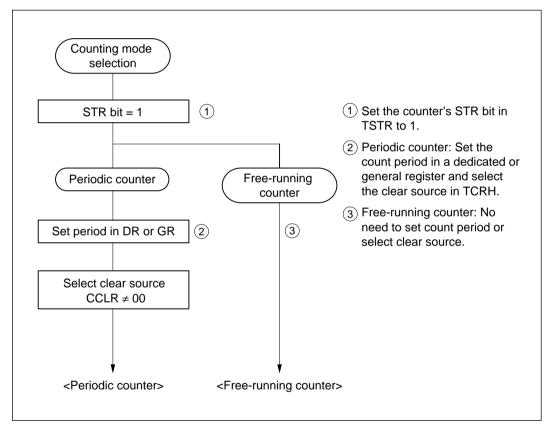

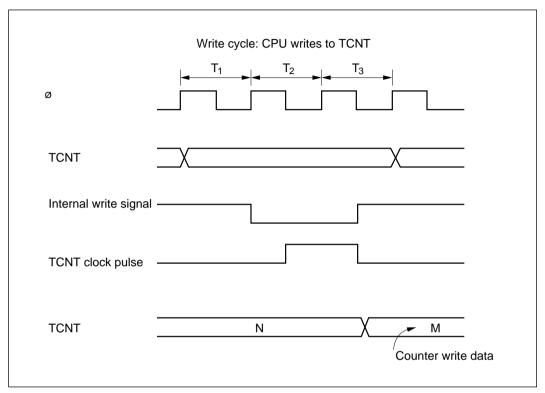

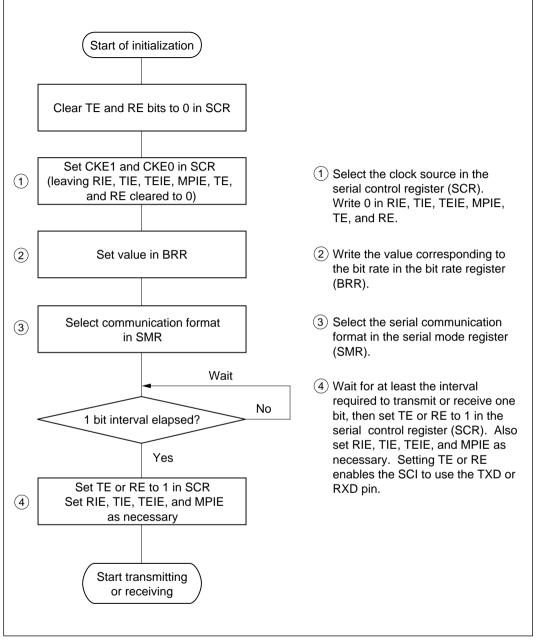

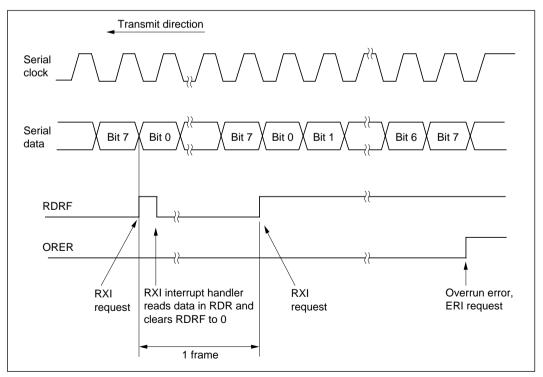

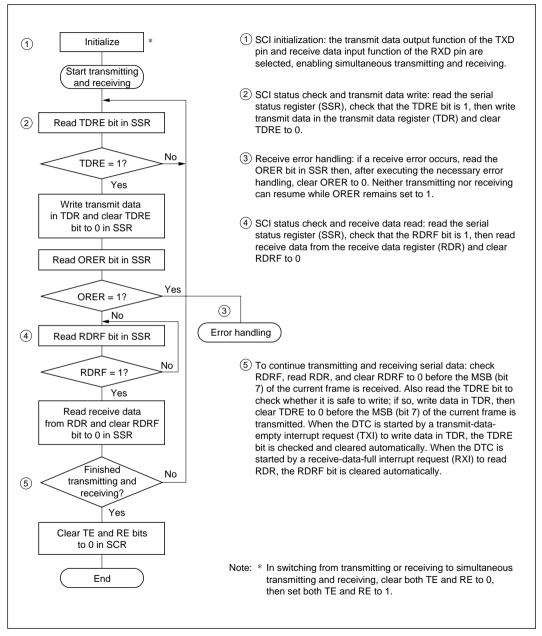

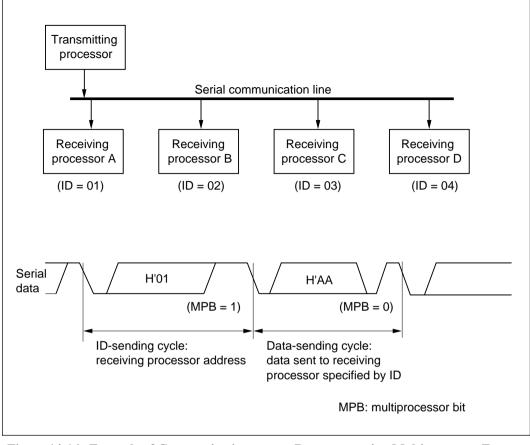

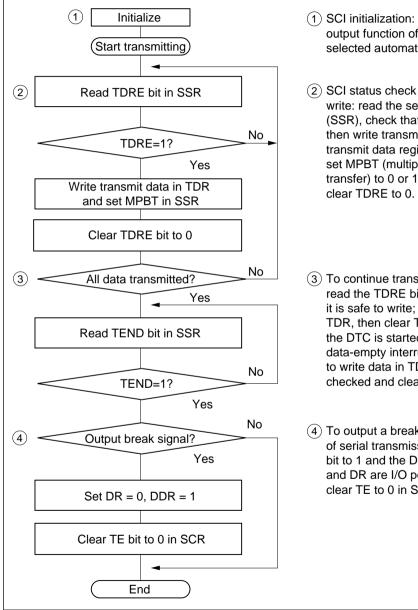

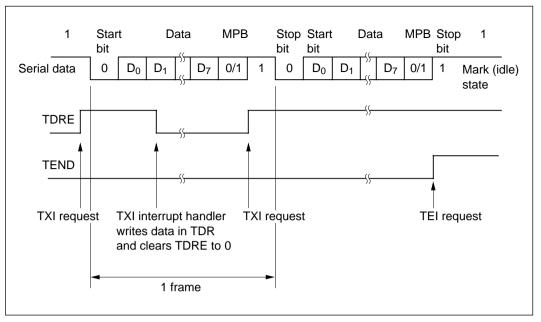

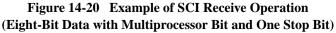

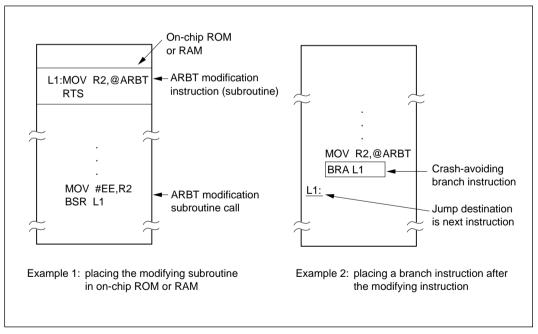

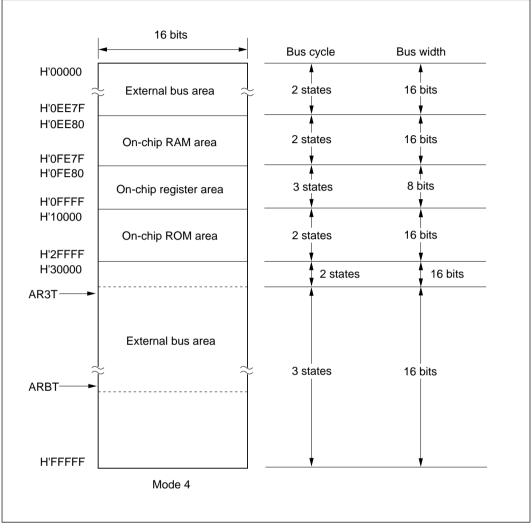

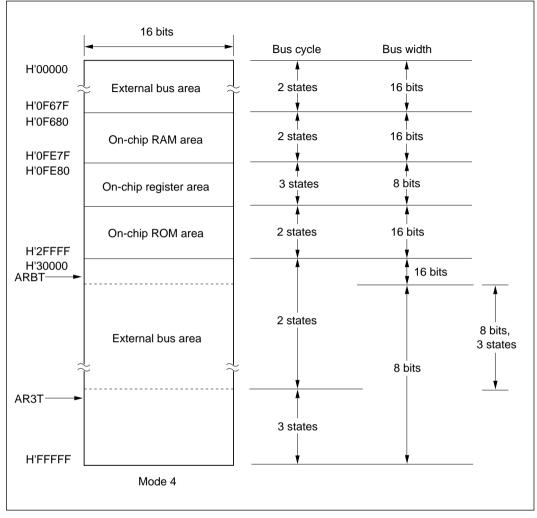

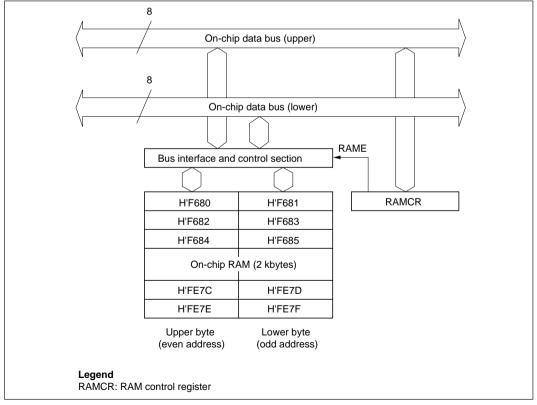

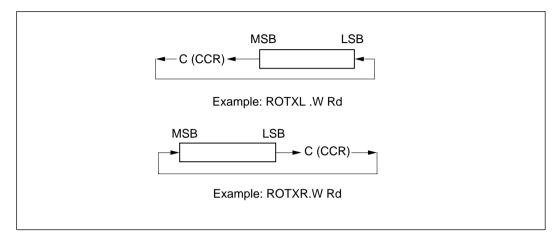

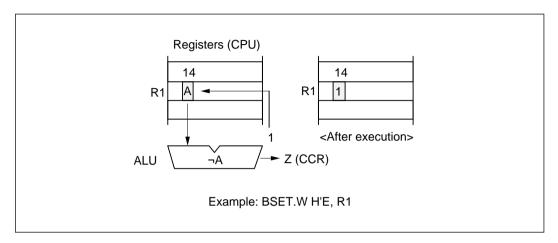

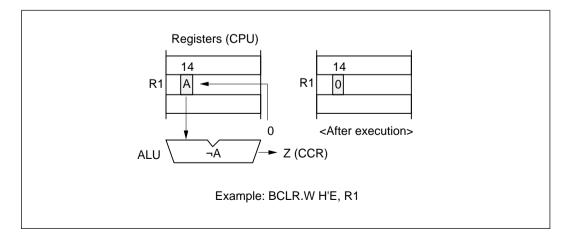

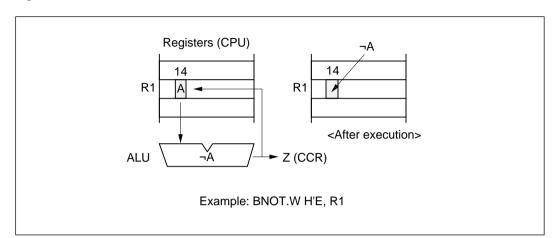

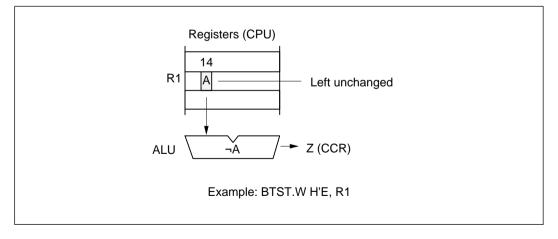

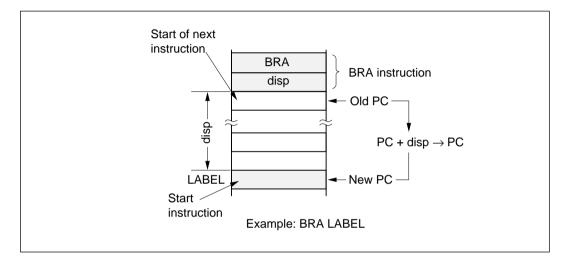

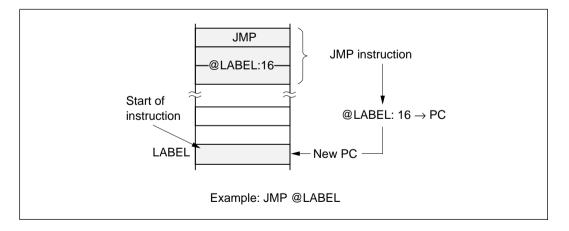

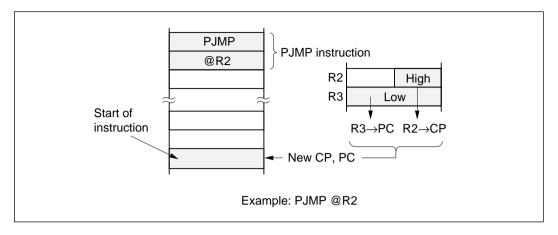

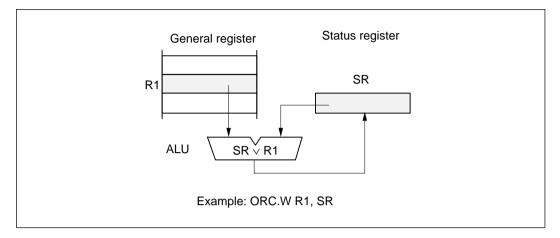

| No. | Modes<br>1 and 6                                          | Mode 2                                                                | Modes<br>3 and 5                                          | Mode 4                                                                | Mode 7                                                    | PROM<br>Mode    |