SONY

# CXA1386P/K

## 8-bit 75MSPS Flash A/D Converter

#### Description

The CXA1386P/K are 8-bit high-speed flash A/D converter ICs capable of digitizing analog signals at the maximum rate of 75MSPS. The digital I/O levels of these A/D converters are compatible with the ECL 100K/10KH/10K.

The CXA1386P/K is pin-compatible with the earlier models CXA1056P/K, CXA1016P/K, respectively. They can be replaced by the CXA1386P/K without any design changes, in most cases. Compared with the earlier models, these new models have been greatly improved in performance, by incorporating advanced process, new circuit design and carefully considered layout.

#### Features

- Differential linearity error: ±1/2LSB or less

- Integral linearity error: ±1/2LSB or less

- High-speed operation with maximum conversion rate of 75MSPS (Min.)

- Wide analog input bandwidth: 150MHz (Min. for full-scale input)

- Low Power consumption: 580mW (Typ.)

- Single power supply: -5.2V

- Low input capacitance: 17pF (Typ.)

- Built-in integral linearity conpensation circuit

- Low error rate

- Operable at 50% clock duty cycle

- · Good temperature characteristics

- Capable of driving 50Ω loads

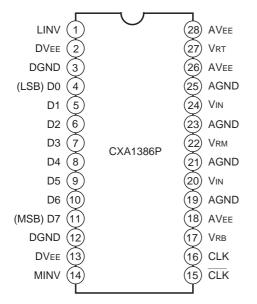

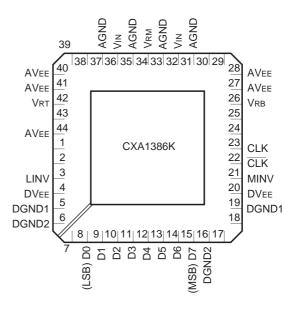

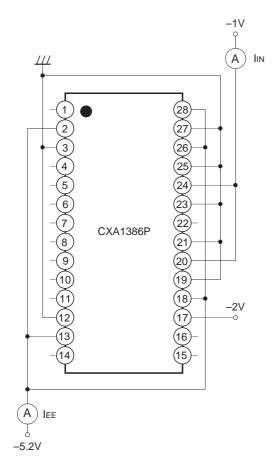

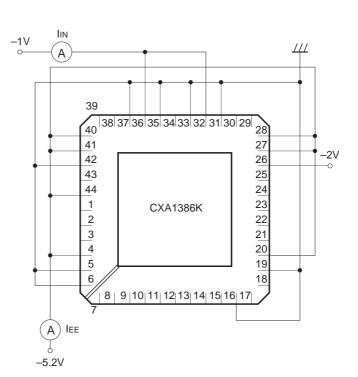

#### **Pin Configuration**

Pins with name are NC pins (not connected).

#### Structure

Bipolar silicon monolithic IC

#### **Applications**

- Digital oscilloscopes

- HDTV (high-definition TVs)

- Other apparatus requiring high-speed A/D conversion

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

| Absolute Maximum Ratin                      | <b>igs</b> (Ta = 25°C)             |       |      |              |      |  |

|---------------------------------------------|------------------------------------|-------|------|--------------|------|--|

| <ul> <li>Supply voltage</li> </ul>          | • Supply voltage AVEE, DVEE        |       |      | to +0.5      | V    |  |

| <ul> <li>Analog input voltage</li> </ul>    | Vin                                |       | -2.7 | -2.7 to +0.5 |      |  |

| <ul> <li>Reference input voltage</li> </ul> | Vrt, Vrb, Vrm                      |       | -2.7 | to +0.5      | V    |  |

|                                             | I Vrt – Vrb I                      |       |      | 2.5          | V    |  |

| <ul> <li>Digital input voltage</li> </ul>   | CLK, CLK, MINV,                    | LINV  | -4 1 | to +0.5      | V    |  |

|                                             | I CLK – CLK I                      |       |      | 2.7          | V    |  |

| • VRM pin input current                     | • Vrм pin input current Ivrм       |       |      | to +3        | mA   |  |

| <ul> <li>Digital output current</li> </ul>  | ID <sub>0</sub> to ID <sub>7</sub> |       | -3   | 0 to 0       | mA   |  |

| <ul> <li>Storage temperature</li> </ul>     | Tstg                               |       | -65  | to +150      | °C   |  |

|                                             |                                    |       |      |              |      |  |

| Recommended Operating                       | g Conditions                       | Min.  | Тур. | Max.         | Unit |  |

| <ul> <li>Supply voltage</li> </ul>          | AVEE, DVEE                         | -5.5  | -5.2 | -4.95        | V    |  |

|                                             | AVEE – DVEE                        | -0.05 | 0    | +0.05        | V    |  |

|                                             | AGND – DGND                        | -0.05 | 0    | +0.05        | V    |  |

| <ul> <li>Reference input voltage</li> </ul> | Vrt                                | -0.1  | 0    | +0.1         | V    |  |

|                                             | Vrb                                | -2.2  | -2.0 | -1.8         | V    |  |

| <ul> <li>Analog input voltage</li> </ul>    | Vin                                | Vrb   |      | Vrt          |      |  |

| <ul> <li>Pulse width of clock</li> </ul>    | TPW1                               | 6.6   |      |              | ns   |  |

|                                             | TPW0                               | 6.6   |      |              | ns   |  |

| <ul> <li>Operating temperature</li> </ul>   | Tc (CXA1386K)                      | -20   |      | +100         | °C   |  |

|                                             | Ta (CXA1386P)                      | -20   |      | +75          | °C   |  |

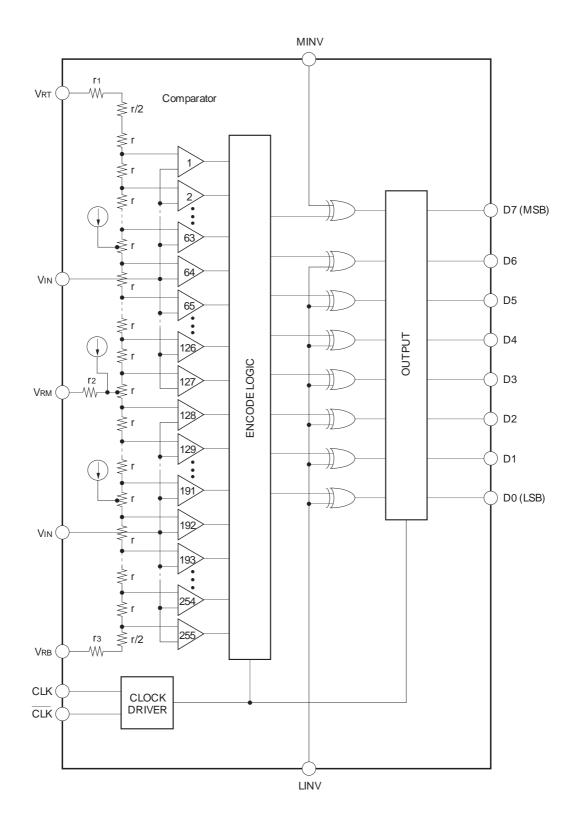

## **Block Diagram**

## Pin Description and I/O pin Equivalent circuit

| Pin                      | No                | Symbol | I/O | Standard<br>voltage | Equivalent circuit                       | Description                                                                                                                                                                                                                                                           |

|--------------------------|-------------------|--------|-----|---------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCC                      | DIP               | Symbol | 1/0 | level               |                                          | Description                                                                                                                                                                                                                                                           |

| 31, 33,<br>35, 37        | 19, 21,<br>23, 25 | AGND   | _   | 0V                  |                                          | Anlog GND.<br>Used as GND for input<br>buffers and latches of<br>comparators.<br>Isolated from DGND or<br>DGND 1/2.                                                                                                                                                   |

| 27, 28,<br>40, 41,<br>44 | 18, 26,<br>28     | AVee   |     | -5.2V               |                                          | Analog VEE<br>-5.2V (Typ.).<br>Internally connected<br>with DVEE<br>(resistance: 4 to $6\Omega$ ).<br>Ceramic chip<br>capacitors of at least<br>$0.1\mu$ F should be used<br>to connect to AGND<br>and be placed near<br>the pins.                                    |

| 23                       | 16                | CLK    |     |                     | DGND (DGND1)                             | CLK input                                                                                                                                                                                                                                                             |

| 22                       | 15                | CLK    | I   | ECL                 | LK C C C C C C C C C C C C C C C C C C C | Input complementary<br>to CLK.<br>With open connection,<br>kept at threshold<br>voltage (–1.3V).<br>Device is operable<br>without CLK input, but<br>use of complementary<br>inputs of CLK and CLK<br>is recommended to<br>obtain the stable high-<br>speed operation. |

| _                        | 3, 12             | DGND   | _   | 0V                  |                                          | Digital GND (Used for<br>internal circuits and<br>output transistors)                                                                                                                                                                                                 |

| 5, 19                    |                   | DGND1  | _   | 0V                  |                                          | Digital GND (Used for internal circuits)                                                                                                                                                                                                                              |

| 6, 16                    |                   | DGND2  |     | 0V                  |                                          | Digital GND (Used for output buffers)                                                                                                                                                                                                                                 |

| Pin   | No    | Ourseland | 1/0 | Standard         |                                      | Description                                                                                                                                                                                                  |

|-------|-------|-----------|-----|------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCC   | DIP   | Symbol    | I/O | voltage<br>level | Equivalent circuit                   | Description                                                                                                                                                                                                  |

| 4, 20 | 2, 13 | DVee      |     | -5.2V            |                                      | Digital VEE<br>Internally connected<br>with AVEE<br>(resistance: 4 to $6\Omega$ )<br>Ceramic chip<br>capacitors of at least<br>0.1µF should be used<br>to connect to DGND<br>and be placed near the<br>pins. |

| 8     | 4     | D0        |     |                  | DGND (DGND2)                         | LSB of data outputs.<br>External pull-down<br>resistor is required.                                                                                                                                          |

| 9     | 5     | D1        |     |                  |                                      |                                                                                                                                                                                                              |

| 10    | 6     | D2        |     |                  |                                      |                                                                                                                                                                                                              |

| 11    | 7     | D3        | 0   | ECL              |                                      | Data outputs.<br>External pull-down                                                                                                                                                                          |

| 12    | 8     | D4        | Ũ   |                  |                                      | resistors are required.                                                                                                                                                                                      |

| 13    | 9     | D5        |     |                  |                                      |                                                                                                                                                                                                              |

| 14    | 10    | D6        |     |                  |                                      |                                                                                                                                                                                                              |

| 15    | 11    | D7        |     |                  | DVEE                                 | MSB of data outputs.<br>External pull-down<br>resistor is required.                                                                                                                                          |

| 3     | 1     | LINV      | I   | ECL              | DGND (DGND1)                         | Input pin for D0 (LSB)<br>to D6 output polarity<br>inversion (see output<br>code table).<br>With open connection,<br>kept at "L" level.                                                                      |

| 21    | 14    | MINV      | I   | ECL              | MINV<br>r<br>-1.3V<br>DVEE<br>r<br>C | Input pin for D7 (MSB)<br>output polarity<br>inversion (see output<br>code table).<br>With open connection,<br>kept at "L" level.                                                                            |

| Pin                                                       | No.    | Symbol | I/O | Standard<br>voltage | Equivalent circuit                                                                 | Description                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------|--------|--------|-----|---------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCC                                                       | DIP    | Oymbol | 10  | level               |                                                                                    | Description                                                                                                                                                                                                                                                                               |

| 32, 36                                                    | 20, 24 | Vin    | I   | Vrt<br>to<br>Vrb    | AGND<br>VIN<br>VIN<br>VIN<br>VIN<br>VIN<br>VIN<br>VIN<br>VIN<br>VIN<br>VIN         | Analog input pins.<br>These two pins must<br>be connected<br>externally, since they<br>are not internally<br>connected.<br>See Application Note<br>for precautions.                                                                                                                       |

| 26                                                        | 17     | Vrb    | I   | -2V                 | VRT r1                                                                             | Reference voltage<br>(bottom)<br>Typically $-2V$<br>A ceramic capacitor of<br>at least $0.1\mu$ F and a<br>tantalus capacitor of at<br>least $10\mu$ F should be<br>used to connect to<br>AGND and be placed<br>near the pins.                                                            |

| 34                                                        | 22     | Vrm    | Ι   | Vrb/2               | V <sub>RM</sub> r <sub>2</sub> Comparator 127<br>• W F Comparator 128              | Reference voltage mid<br>point be used as a pin<br>for integral linearity<br>compensation                                                                                                                                                                                                 |

| 42                                                        | 27     | Vrt    | I   | ov                  | r<br>Comparator 129<br>r<br>Comparator 130<br>r<br>Comparator 255<br>VRB r3<br>r/2 | Reference voltage<br>(top) Typically 0V<br>When a voltage<br>different from AGND is<br>applied to this pin, a<br>ceramic capacitor of at<br>least $0.1\mu$ F and a<br>tantalus capacitor of at<br>least $10\mu$ F should be<br>used to connect to<br>AGND and be placed<br>near the pins. |

| 1, 2,<br>7, 17,<br>18, 24,<br>25, 29,<br>30, 38<br>39, 43 |        | NC     |     | _                   |                                                                                    | Unused pins<br>No internal connections<br>have been made to<br>these pins.<br>Connecting them to<br>AGND or DGND on PC<br>board is recommended.                                                                                                                                           |

#### **Electrical Characteristics**

$(Ta = 25^{\circ}C, AVee = DVee = -5.2V, Vrt = 0V, Vrb = -2V)$

| Item                                                                                                                                                          | Symbol                                  | Condition                                                                                                                                       | Min.                    | Тур.             | Max.              | Unit                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------|-------------------|------------------------------------|

| Resolution                                                                                                                                                    | n                                       |                                                                                                                                                 |                         | 8                |                   | bits                               |

| DC characteristics<br>Integral linearity error<br>Differential linearity error                                                                                | Eil<br>Edl                              | Fc = 75MSPS<br>Fc = 75MSPS                                                                                                                      |                         | ±0.3<br>±0.3     | ±0.5<br>±0.5      | LSB<br>LSB                         |

| Analg input<br>Analog input capacitance<br>Analog input resistance<br>Input bias current                                                                      | Cin<br>Rin<br>Iin                       | $V_{IN} = -1V + 0.07Vrms$<br>$V_{IN} = -1V$                                                                                                     |                         | 17<br>390        | 200               | pF<br>kΩ<br>μA                     |

| Reference inputs<br>Reference resistance<br>Offset voltage VRT<br>VRB                                                                                         | Rref<br>Еот<br>Еов                      |                                                                                                                                                 | 75<br>8<br>0            | 110<br>18<br>10  | 155<br>32<br>24   | Ω<br>mV<br>mV                      |

| Digital inputs<br>Logic H level<br>Logic L level<br>Logic H current<br>Logic L current<br>Input capacitance                                                   | Vih<br>Vil<br>Iih<br>Iil                | Input connected to –0.8V<br>Input connected to –1.6V                                                                                            | -1.13<br>0<br>-50       | 7                | -1.50<br>50<br>50 | V<br>V<br>μA<br>μA<br>pF           |

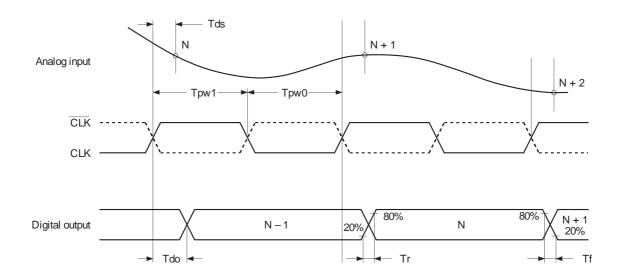

| Switching characteristics<br>Maximum conversion rate<br>Aperture jitter<br>Sampling delay<br>Output delay<br>H pulse width of clock<br>L pulse width of clock | Fc<br>Taj<br>Tds<br>Tdo<br>TPW1<br>TPW0 | Error rate 10 <sup>-9</sup> TPS <sup>*1</sup>                                                                                                   | 75<br>4.0<br>6.6<br>6.6 | 10<br>3.0<br>6.5 | 9.0               | MSPS<br>ps<br>ns<br>ns<br>ns<br>ns |

| Digital outputs<br>Logic H level<br>Logic L level<br>Output rising time<br>Output falling time                                                                | Vон<br>Vol<br>Tr<br>Tf                  | RL = 620Ω to DVEE<br>RL = 620Ω to DVEE<br>RL = 620Ω to DVEE, 20% to 80%<br>RL = 620Ω to DVEE, 80% to 20%                                        | -1.03                   | 0.9<br>2.1       | -1.62             | V<br>V<br>ns<br>ns                 |

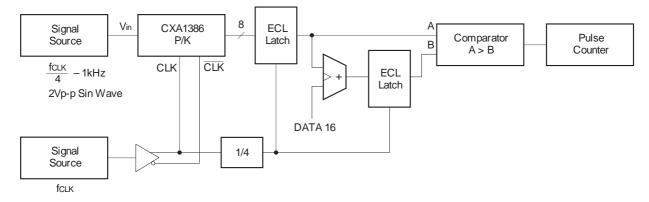

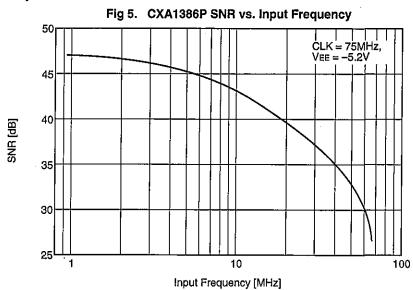

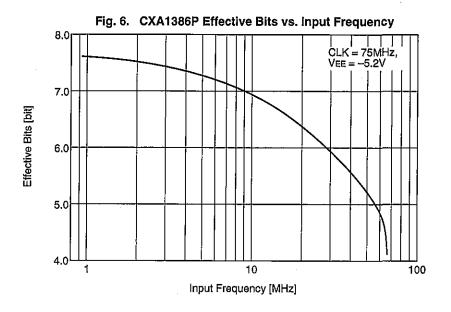

| Dynamic characteristics<br>Input bandwidth<br>S/N ratio                                                                                                       |                                         | $V_{IN} = 2Vp-p$ Input frequency at -3dB $\begin{cases} Input = 1MHz, FS \\ Clock = 75MHz \\ Input = 18.75MHz, FS \\ Clock = 75MHz \end{cases}$ | 150                     | 46<br>40         |                   | MHz<br>dB<br>dB                    |

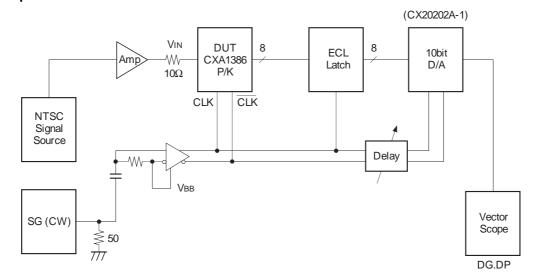

| Error rate<br>Differential gain error<br>Differential phase error                                                                                             | DG<br>DP                                | $ \begin{cases} Input = 18.749MHz, FS \\ Error > 16LSB \\ Clock = 75MHz \\ NTSC 40IRE mod. ramp, \\ Fc = 75MSPS \end{cases} $                   |                         | 1.0<br>0.5       | 10 <sup>_9</sup>  | TPS*1<br>%<br>deg                  |

| Power supply<br>Supply current<br>Power consumption* <sup>2</sup>                                                                                             | lee<br>Pd                               |                                                                                                                                                 | -150                    | -104<br>580      |                   | mA<br>mW                           |

\*1 TPS: Times Per Sample

\*2 Pd = IEE · VEE +

$$\frac{(V_{RT} - V_{RB})^2}{R_{REF}}$$

## Output Code Table

| Vin* | Step | MINV 1<br>LINV 1 | 0<br>1    | 1<br>0    | 0<br>0    |

|------|------|------------------|-----------|-----------|-----------|

|      |      | D7 D0            | D7 D0     | D7 D0     | D7 D0     |

| 0V   |      | 0 0 0 0 0        | 1 0 0 0 0 | 0 1 1 1 1 | 11111     |

|      | 0    | 0 0 0 0 0        | 10000     | 0 1 1 1 1 | 11111     |

|      | 1    | 0 0 0 0 1        | 1 0 0 0 1 | 01110     | 11110     |

|      |      | :                | :         | :         | :         |

|      |      | :                | :         | :         | :         |

| -1V  | 127  | 01111            | 11111     | 0 0 0 0 0 | 10000     |

|      | 128  | 10000            | 00000     | 11111     | 01111     |

|      |      | :                | :         | :         | :         |

|      |      | :                | :         | :         | :         |

|      | 254  | 11110            | 01110     | 1 0 0 0 1 | 0 0 0 0 1 |

|      | 255  | 11111            | 0 1 1 1 1 | 1 0 0 0 0 | 00000     |

| _2V  |      | 1 1 1 1 1        | 0 1 1 1 1 | 1 0 0 0 0 | 0 0 0 0 0 |

\* Vrt = 0V, Vrb = -2V

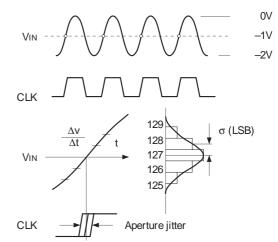

## Timing diagram

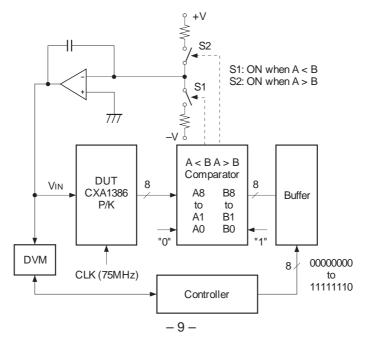

#### **Electrical Characteristics Test Circuit**

#### Maximum conversion rate test circuit

## Differential gain error test circuit Differential phase error test circuit

## Integral linearity error test circuit Differential linearity error test circuit

## Power Supply Current Test Circuit Analog input bias current test circuit

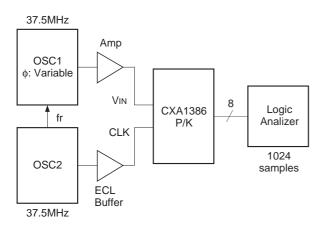

## Sampling delay test circuit Aperture jitter test circuit

#### Aperture jitter test method

Aperture jitter is defined as follows:

$$\label{eq:Taj} \text{Taj} = \sigma / \frac{\Delta \upsilon}{\Delta t} = \sigma / (\frac{256}{2} \times 2\pi f \ ),$$

Where  $\sigma$  (unit: LSB) is the deviation of the output codes when the input frequency is exactly the same as the clock and is sampled at the largest slew rate point.

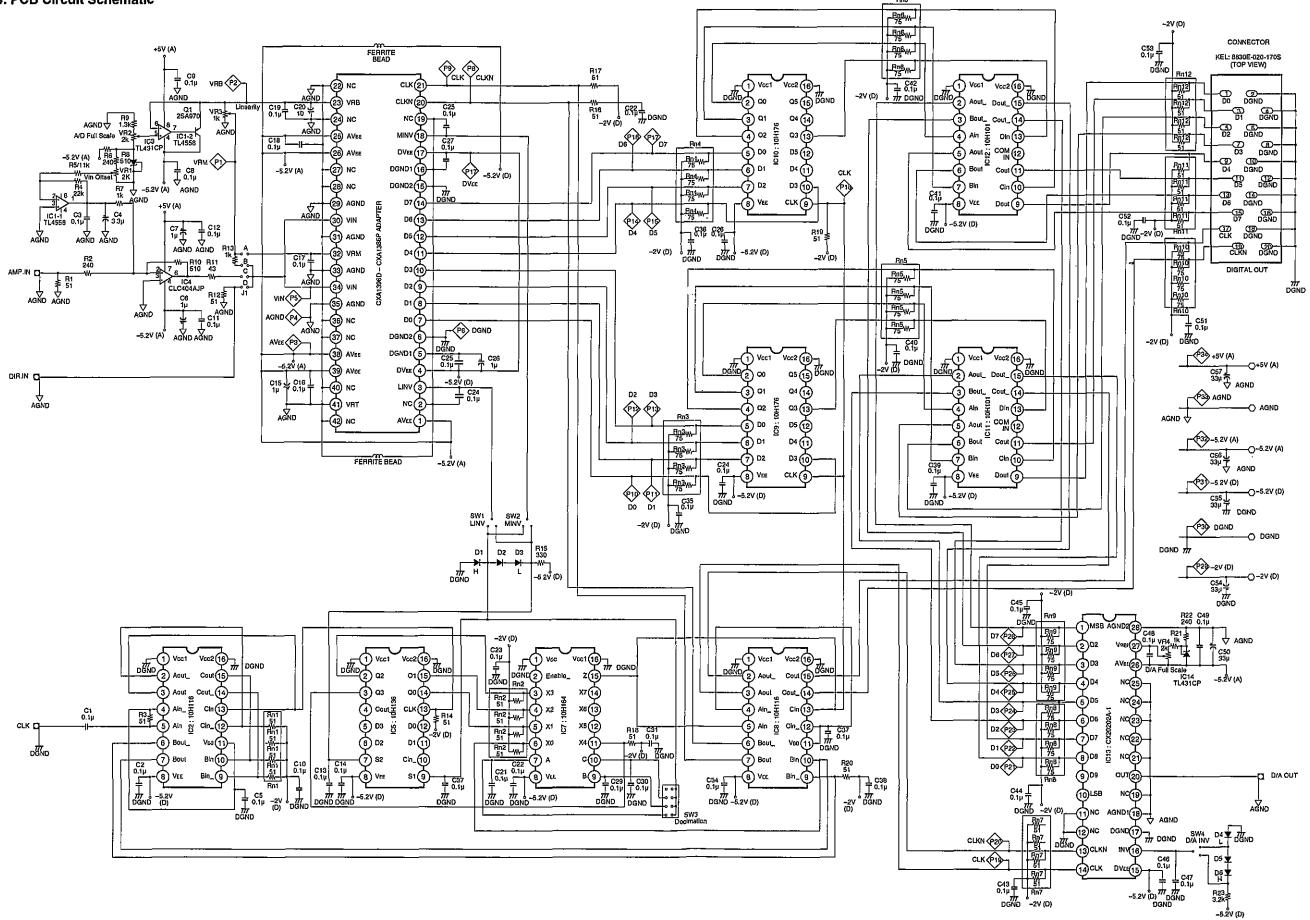

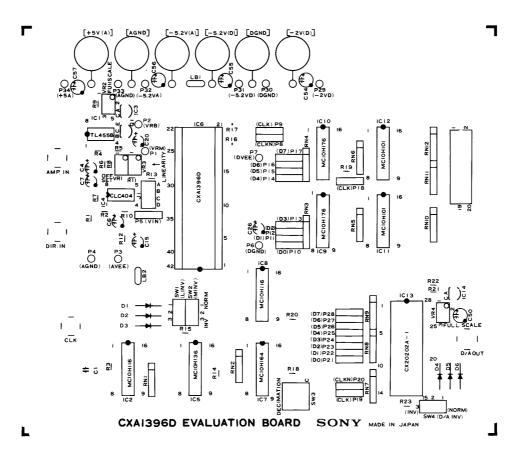

#### 8bit 75MSPS ADC and DAC Evaluation Board

It is necessary to equip "the CXA1396D/P EVALUATION BOARD WITH DAC" with "A1396D – A1386P ADAPTER" in order to evaluate CXA1386P.

In addition to indispensable features such as the reference voltage generator, this tool equips two sets of analog inputs (the direct input and the buffer amplifier input), the input voltage offset generator, the clock decimator, the output data latches, the 10-bit high-speed DAC, and the 20-pin cable connector for digital outputs. This evaluation board provides full performance of the CXA1386P and it is designed to facilitate evaluation.

#### Features

Resolution: 8bits Maximum conversion rate: 75MSPS Supply voltage: +5.0V, -5.2V, -2.0V Two analog inputs (Direct input, buffer amplifier input) Clock level converter: Sine wave to ECL level signal Reference voltage adjustment circuit for the A/D converter Built-in clock frequency decimation circuit: (1/1 to 1/16)

#### Fig. 1. Block Diagram

#### **Supply Current**

| Item  | Min. | Тур. | Max. | Unit |

|-------|------|------|------|------|

| -5.2V |      | 0.85 | 1.0  | Α    |

| +5.0V |      | 15   | 30   | mA   |

| -2.0V |      | 0.45 | 0.6  | A    |

(Note: Supply current -2.0V is the value when Rn10, Rn11 and Rn12 are not mounted.)

#### Analog Input (DIR. IN, AMP. IN)

| Item                                                                  | Min.         | Тур. | Max.      | Unit        |

|-----------------------------------------------------------------------|--------------|------|-----------|-------------|

| Input voltage (DIR. IN)<br>(AMP. IN) <sup>*1</sup><br>Input impedance | -2.0<br>-0.5 | 50   | 0<br>+0.5 | V<br>V<br>Ω |

(\*1: Adjustable by VR1)

## **Clock Input (CLK)**

| Item                            | Min. | Тур. | Max. | Unit |

|---------------------------------|------|------|------|------|

| Input voltage<br>(Peak to Peak) |      | 2.0  |      | Vp-р |

| Input impedance                 |      | 50   |      | Ω    |

## Digital Output (D0 to D7)

ECL 10KH level

#### **Clock Output**

ECL 10KH level, complementary output

## **Output Code Table**

|     | MINV | 0         | 0         | 1     | 1         |

|-----|------|-----------|-----------|-------|-----------|

|     | LINV | 0         |           | 0     | I         |

|     | 0V   | 11111     | 10000     | 01111 | 00000     |

|     | :    | 11110     | 10001     | 01110 | 0 0 0 0 1 |

|     | :    | :         | :         | :     | :         |

|     | :    | :         | :         | :     | :         |

| Vin | :    | 10000     | 11111     | 00000 | 01111     |

| VIN | :    | 0 1 1 1 1 | 00000     | 11111 | 10000     |

|     | :    | :         | :         | :     | :         |

|     | :    | :         | :         | :     | :         |

|     | :    | 0 0 0 0 1 | 01110     | 10001 | 11110     |

|     | -2V  | 0 0 0 0 0 | 0 1 1 1 1 | 10000 | 11111     |

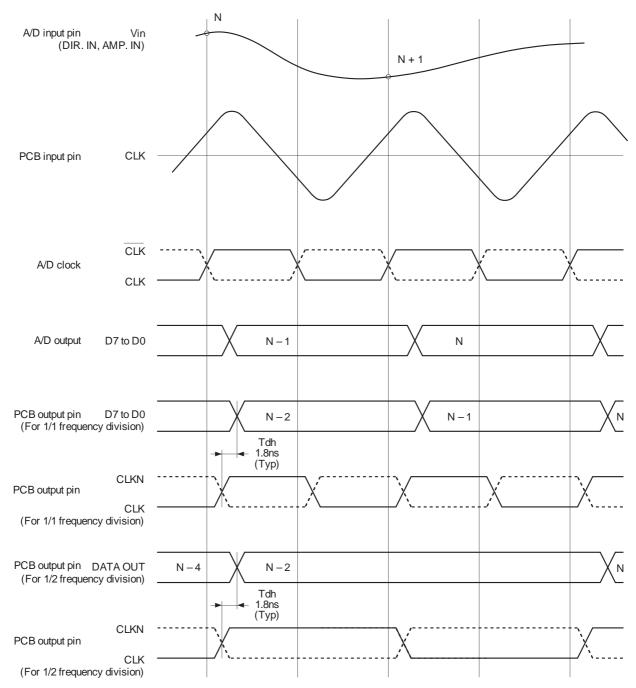

### Fig. 2. Timing Chart

#### Adjustment Methods and Notes on Operation

1) Vin Offset (VR1)

The volume to adjust the signal range (0V center assumed) with the A/D converter input range when a waveform is input through AMP. IN.

2) A/D Full Scale (VR2)

The volume to adjust A/D converter VRB voltage.

3) Linearity (VR3)

The volume to adjust VRM (linearity) voltage.

4) D/A Full Scale (VR4)

The volume to adjust D/A output full scale (-1V)

| 5) J1 (input selection)                | [Jumper Poisition at shipment] |

|----------------------------------------|--------------------------------|

| A: Shorts to adjust VRM voltage.       | J1                             |

| B: Shorts to supply DC voltage to Vin. | ΑΟΟ                            |

| C: Shorts to select AMP.IN input.      | BOO                            |

| D: Shorts to select DIR. IN input.     | COO                            |

|                                        | DOO                            |

|                                        |                                |

6) SW1

The switch for LINV High/Low

7) SW2

The switch for MINV High/Low

8) SW3 (Decimation)

The switch to select clock frequency decimation.

- Switch position: decimation ratio

- 0: 1/1

- 1: 1/2

- 2: 1/4

- 3: 1/8

- 4: 1/16

- 9) SW4 (D/A INV)

The switch for D/A converter output inversion.

- 10) Rn10, Rn11 and Rn12 are not mounted at shipment. They are not required during evaluation.

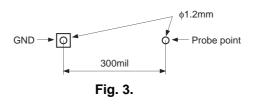

- 11) Waveform probe pins P5 and P8 through P28 are devised to facilitate GND connection in order to reduce the distortion. As shown in the diagram below, the distance between the probe point and the GND is 300 mils, and there is \u03c61.2mm throughhole at each. The signal and GND locations are suit for a Tektronix GND tip (part number 013-1185-00).

- 12) D/A converter (IC13) input data (waveform probe pins P21 through P28) are the complementary signals of the decimated A/D converter outputs. Those are inverted again in the D/A converter so that the direction of reproduced waveform can agree with the A/D input signal converter.

- 13) The part number of the digital output connector is KEL 8830E-020-170S. A corresponding connector and cable assembly is JUNKOSHA KB0020MCG50BI.

Fig. 4. PCB Circuit Schematic

- 16 --

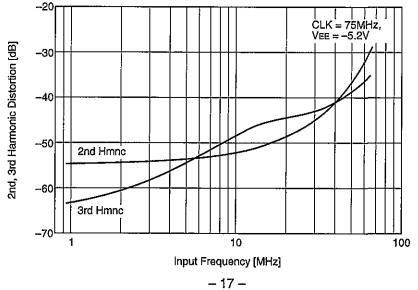

#### **Characteristics Graphs**

#### CXA1396D - CXA1386P ADAPTER (SCALE = 2/1)

TOP VIEW

#### Parts Layout

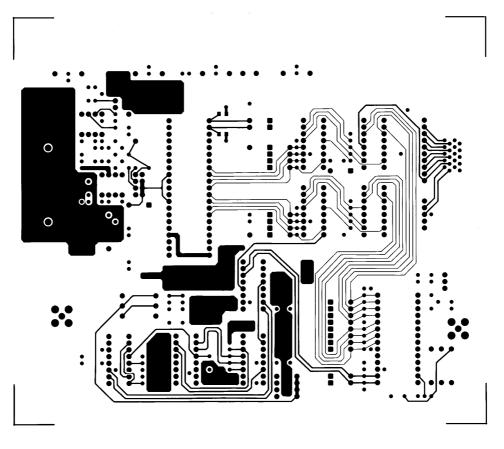

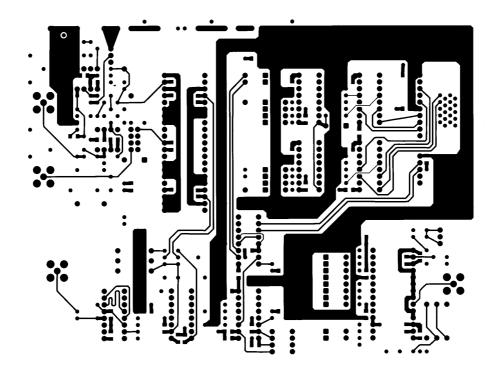

## **Printed Pattern**

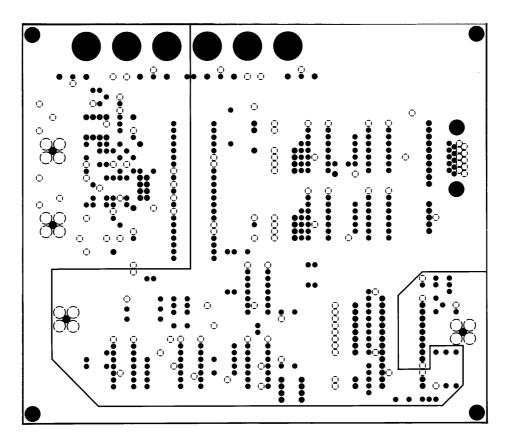

1st layer Component plane (Top View)

4th layer Solder plane (Top view)

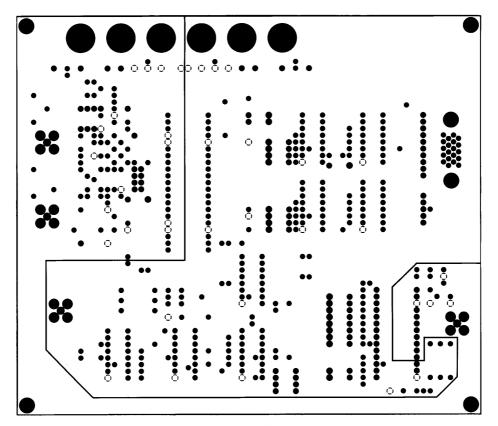

2nd layer GND plane (Top View)

3rd layer Power supply plane (Top View)

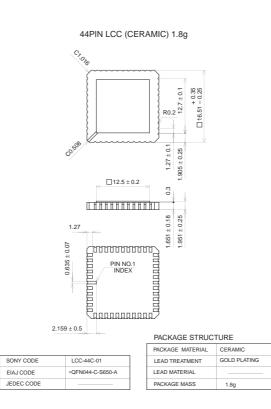

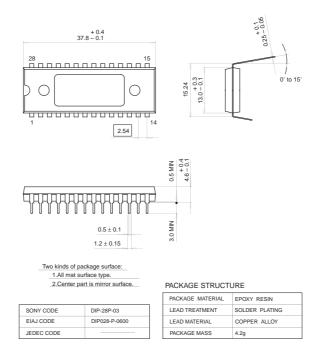

#### Package Outline Unit: mm

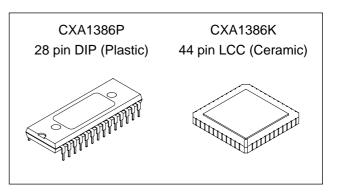

CXA1386P

28PIN DIP (PLASTIC)

#### 28PIN DIP (PLASTIC)

|            |               | PACKAGE MATE  |

|------------|---------------|---------------|

| SONY CODE  | DIP-28P-03    | LEAD TREATMEN |

| EIAJ CODE  | DIP028-P-0600 | LEAD MATERIAL |

| JEDEC CODE |               | PACKAGE MASS  |

| PACKAGE MATERIAL | EPOXY RESIN   |

|------------------|---------------|

| LEAD TREATMENT   | SOLDER PLATIN |

| LEAD TREATMENT | SOLDER PLATING |

|----------------|----------------|

| LEAD MATERIAL  | COPPER ALLOY   |

| PACKAGE MASS   | 4.2g           |

#### LEAD PLATING SPECIFICATIONS

| ITEM               | SPEC.           |

|--------------------|-----------------|

| LEAD MATERIAL      | COPPER ALLOY    |

| SOLDER COMPOSITION | Sn-Bi Bi:1-4wt% |

| PLATING THICKNESS  | 5-18µm          |

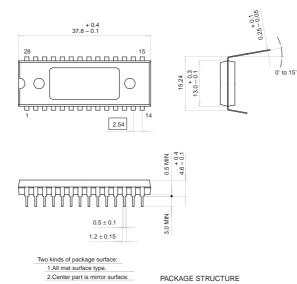

#### Package Outline Unit: mm

CXA1386K