# 12-Bit, 500kSPS, Sampling A/D Converter

# **Features**

- Monolithic CMOS A/D Converter

0.4 μs Track/Hold Amplifier

1.6 μs A/D Converter

2.5 V Voltage Reference

Parallel, Serial and Byte Interface.

- 12-Bit ADC Linearity Error: 0.5 LSB

- Low Distortion

Signal-to-Noise Ratio: 72.8 dB

Total Harmonic Distortion: 0.01 %

Spurious-Free-Dynamic-Range: -80dBc

- Low Power: 85 mW

- 60 ppm/°C Reference Drift

# General Description

The CS5032 is a complete monolithic CMOS analog-to-digital converter providing 500kSPS throughput. The part has an internal sample-and-hold, voltage reference, and can operate with an internal or external clock.

The CS5032 has a high-speed digital interface with three-state data outputs and standard control inputs allowing easy interfacing to common microprocessors and digital signal processors. Digital output data is available in either 12-bit parallel, two 8-bit bytes, or serial formats.

The CS5032 is available in a 24-pin, 0.3" plastic dual-in-line package (PDIP), Cerdip and small outline (SOIC) package.

**ORDERING INFORMATION:** Page 2-101

Preliminary Product Information

This document contains information for a new product. Crystal Semiconductor reserves the right to modify this product without notice.

**Crystal Semiconductor Corporation** P.O. Box 17847, Austin, TX 78760 (512) 445 7222 Fax: (512) 445 7581

Copyright © Crystal Semiconductor Corporation 1995 (All Rights Reserved) MAR '95 DS118PP3

2-81

# ANALOG CHARACTERISTICS(VA+ = +5V±5%; VA- = -5V±5%; AGND = DGND = 0V; CLKIN = 10MHz, unless otherwise specified. TA = TMIN to TMAX)

|                                                           |             |                  |            | В             |      |            | T        |      |                      |

|-----------------------------------------------------------|-------------|------------------|------------|---------------|------|------------|----------|------|----------------------|

| Parameter                                                 | (Note 1)    | Symbol           | Min        | Тур           | Max  | Min        | Тур      | Max  | Units                |

| Specified Temperature Range                               |             |                  |            | 40 to +8      | 5    | -5         | 5 to +12 | 25   | °C                   |

| Accuracy                                                  |             |                  |            |               |      |            |          |      | .,,                  |

| Integral Nonlinearity                                     |             | INL_             | -          | 0.25          | 0.5  | -          | 0.25     | 0.5  | LSB                  |

| Differential Nonlinearity                                 |             | DNL              | -          | -             | 0.5  | •          | <u> </u> | 0.5  | LSB                  |

| Unipolar Offset Error                                     |             | VUP              |            | 0.25          | 0.5  | -          | 0.25     | 0.5  | LSB                  |

| Bipolar Zero Error                                        |             | V <sub>BP</sub>  |            | 0.25          | 0.5  | -          | 0.25     | 0.5  | LSB                  |

| Positive Full Scale Error                                 | (Note 2)    | FSEP             | •          | 0.25          | 0.5  | -          | 0.25     | 0.5  | LSB                  |

| Bipolar Negative Full Scale Error                         | (Note 2)    | FSEN             | -          | 0.25          | 0.5  | -          | 0.25     | 0.5  | LSB                  |

| Dynamic Performance                                       | (Note 3)    |                  |            |               |      |            |          |      |                      |

| Signal-to-Noise-and-Distortion                            | (Note 4)    | SINAD            | 70         | 72            | -    | 70         | 72       | -    | dB                   |

| Signal-to-Noise Ratio                                     | <del></del> | SNR              | 70.5       | 72.8          | _    | 70.5       | 72.8     | -    | dB                   |

| Total Harmonic Distortion                                 |             | THD              | -          |               | 0.01 | -          |          | 0.01 | %                    |

| Spurious-Free-Dynamic-Range                               | (Note 5)    | SFDR             | -80        | -             | 0.01 | -<br>-80   | -        | 0.01 | %<br>dB <sub>c</sub> |

| Intermodulation Distortion<br>Second Order<br>Third Order | (Note 6)    | IMD              | -80<br>-80 | <u>-</u><br>- | -    | -80<br>-80 | -        | -    | dB <sub>c</sub>      |

| Analog Input                                              |             |                  |            |               |      |            |          |      | T                    |

| Input Voltage Range                                       |             | AIN              | -2.5       | •             | +2.5 | -2.5       | -        | +2.5 | V                    |

| Aperture Delay                                            |             | tapd             | -          | -             | 25   | -          | -        | 25   | ns                   |

| Aperture Jitter                                           |             | t <sub>apj</sub> |            |               | 100  | -          |          | 100  | ps                   |

| Input Capacitance                                         |             | Acin             |            | <u>-</u>      | 10   | <u></u>    | -        | 10   | pF                   |

- Notes: 1. All parameters are guaranteed by design, test, and/or characterization.

- 2. Measured with respect to internal reference and includes bipolar offset error.

- 3.  $A_{IN} = \pm 2.5 V_{pp}$

- 4. AIN = 10kHz Sine Wave, fsample = 500kSPS. Typically 71.5dB for 10kHz<AIN<250kHz.

- 5. AIN = 10kHz Sine Wave, fsample = 500kSPS. Typically -80dB for 0<AIN<250kHz.

- 6. fa = 9kHz, fb = 9.8kHz, fsample = 500kSPS.

<sup>\*</sup> Parameter definitions are given at the end of this data sheet prior to the package outline information.

# **ANALOG CHARACTERISTICS (Continued)**

|                                                                         |                  | В                                       |                  |                     | Т           |                  |                     |                          |

|-------------------------------------------------------------------------|------------------|-----------------------------------------|------------------|---------------------|-------------|------------------|---------------------|--------------------------|

| Parameter                                                               | Symbol           | Min                                     | Тур              | Max                 | Min         | Тур              | Max                 | Units                    |

| Specified Temperature Range                                             |                  | -                                       | 40 to +8         | 35                  | -5          | 5 to +1          | 25                  | °C                       |

| Reference Output                                                        |                  |                                         |                  |                     |             |                  |                     |                          |

| Output Voltage                                                          | VR               | 2.49                                    | -                | 2.51                | 2.49        | _                | 2.51                | V                        |

| REF OUT Tempco                                                          |                  | -                                       | 60               |                     | -           | 60               | _                   | ppm/°C                   |

| Load Regulation (Note 7)                                                | ΔVR/ΔΙ           | -                                       | 0.6              | 1                   | -           | 0.6              | 1                   | mV                       |

| Output Noise Voltage                                                    | eN               |                                         | 100              | -                   | -           | 100              |                     | μV <sub>rms</sub>        |

| Output Current Drive<br>Source Current<br>Sink Current                  | ISOURCE<br>ISINK | -                                       | 500<br>100       | -                   | -           | 500<br>100       | -                   | μ <b>Α</b><br>μ <b>Α</b> |

| Conversion & Throughput                                                 |                  |                                         |                  |                     |             |                  |                     | <del></del>              |

| Conversion Time<br>External Clock (cLKIN ≈ 10MHz)<br>Internal Clock     | tconv            | -<br>1.4                                | -                | 1.6<br>1.8          | -<br>1.4    | -                | 1.6<br>1.8          | MMC*<br>μs               |

| Acquisition Time                                                        | tacq             | -                                       | -                | 0.4                 | -           | -                | 0.4-                | μs                       |

| Throughput                                                              | ftp              | 500                                     | -                | -                   | 500         | -                | -                   | kSPS                     |

| Power Supplies                                                          |                  | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                  |                     | · · · · ·   |                  |                     |                          |

| Positive Supply Current<br>Negative Supply Current<br>Power Dissipation | ia+<br>Ia-<br>PD | -<br>-<br>-                             | 9.5<br>7.0<br>85 | 10.0<br>10.0<br>100 | -<br>-<br>- | 9.5<br>7.0<br>85 | 10.0<br>10.0<br>100 | mA<br>mA<br>mW           |

Note: 7. Reference Load Current Change (0-500 μA). Reference Load should not be changed during conversion

| LSB  | %FS   | ppm FS | mV   |

|------|-------|--------|------|

| 0.25 | .0061 | 61     | 0.31 |

| 0.50 | .0122 | 122    | 0.61 |

| 1.00 | .0244 | 244    | 1.22 |

| 2.00 | .0488 | 488    | 2.44 |

| 4.00 | .0976 | 976    | 4.88 |

Unit Conversion Factors:  $VIN = \pm 2.5V$

# **SWITCHING CHARACTERISTICS** (TA = T<sub>MIN</sub> to T<sub>MAX</sub>; VA+ = +5V±5%, VA- = -5V±5%; AGND = DGND = 0V, (Note 8)

|                        |                                         |                                        |     | В        |         |             | Т        |     |       |

|------------------------|-----------------------------------------|----------------------------------------|-----|----------|---------|-------------|----------|-----|-------|

|                        | Parameter                               | Symbol                                 | Min | Тур      | Max     | Min         | Тур      | Max | Units |

| Specified Temper       | ature Range                             |                                        | •   | 40 to +8 | 35      | -55 to +125 |          |     | °C    |

| CLKIN                  | Period                                  | tclk                                   | 100 | -        | 400     | 100         | -        | 400 |       |

| CLKIN                  | Low Time                                | tclkl                                  | 0.4 | -        | 0.6     | 0.4         | -        | 0.6 | MMC*  |

| CLKIN                  | High Time                               | tclkh                                  | 0.4 | -        | 0.6     | 0.4         | -        | 0.6 | ns    |

| Rise Times             | Any Digital Input<br>Any Digital Output | t <sub>rise</sub><br>t <sub>rise</sub> |     | -<br>20  | 20<br>- | -           | -<br>20  | 20  | ns    |

| Fall Times             | Any Digital Input                       | tfall                                  | -   |          | 20      | -           | -        | 20  | ns    |

|                        | Any Digital Output                      | tfall                                  | -   | 20       | -       | •           | 20       | -   | ns    |

| Mode 1 Timing          |                                         |                                        |     |          |         |             |          |     |       |

| Conversion Time        |                                         | tconv                                  | -   | -        | 16      | -           | -        | 16  | ns    |

| CONVST Pulse Width     |                                         | t <sub>cpw</sub>                       | 50  | •        | -       | 50          | -        |     |       |

| CS Active to RD Active |                                         | t <sub>css1</sub>                      | 0   | -        | -       | 0           | -        |     |       |

| RD Pulse Width         |                                         | trpw1                                  | 60  | -        | -       | 75          | -        |     | ļ     |

| RD Inactive to CS      | S Inactive                              | tcsh1                                  | 0   |          |         | 0           | -        | -   |       |

| RD Active to INT       | Inactive                                | trdd                                   | -   | -        | 70      | -           | -        | 70  | ns    |

| Data Access Time       | e after RD (Note 9)                     | t <sub>ra1</sub>                       | -   | -        | 57      | -           |          | 70  | ļ     |

| Output Float Dela      | ay: RD Rising to Hi-Z (Note 10)         | t <sub>fd1</sub>                       | 5   | •        | 50      | 5           | •        | 50  | ns    |

| HBEN to RD Acti        | ve                                      | thrs                                   | 0   | -        |         | 0           | -        | -   | ns    |

| RD Inactive to H       | BEN Hold Time                           | thrh                                   | 0   | •        | -       | 0           | -        | •   |       |

| Serial Clock Tim       | ning                                    |                                        |     |          |         |             |          |     |       |

| SCLK to SSTRB          | Falling Time (Note 11)                  | tss                                    | 25  | -        | 25      | 25          | -        | -   |       |

| Serial Clock           | Pulse Width High                        | tpwh                                   | 0.4 |          | 0.6     | 0.4         | -        | 0.6 | MCC*  |

| Pulse Width Low        |                                         | tpwi                                   | 0.4 | -        | 0.6     | 0.4         | <u>.</u> | 0.6 | MCC*  |

| SCLK rising to D       | ata Valid (Note 12)                     | tssl                                   |     |          | 30      | -           |          | 30  | ns    |

| SCLK rising to S       |                                         | tssri                                  | 10  | -        | 25_     | 10          | -        | 25  | ns    |

| SCLK rising to S       | DATA Hold Time                          | tsh                                    | 10  |          | 25      | 10          | -        | 25  | ns    |

MCC = Master Clock Cycles, 1 MCC = tclk

Notes: 8. All input signals are specified with  $t_{rise} = t_{fall} = 5$ ns (10% to 90% of 5V) and timed from a voltage level of 1.6V.

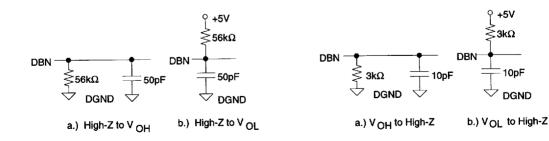

- 9. Measured with the load circuits of Figure 5 and defined as the time required for an output to cross 0.8V or 2.4V.

- 10. Defined as the time required for the data lines to change 0.5V when loaded with the circuits of Figure 6.

- 11.  $t_{SSS} = MCC/2 25$ ns.  $t_{SSS} = 25$ ns for  $t_{Clk} = 100$ ns.

- 12. CL = 35pF. SDATA will drive higher capacitive loads but this will add to tss.

**DS118PP3**

2-84

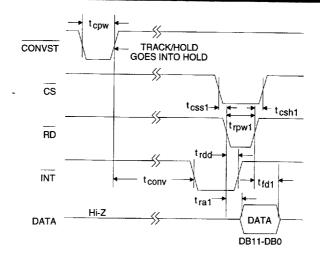

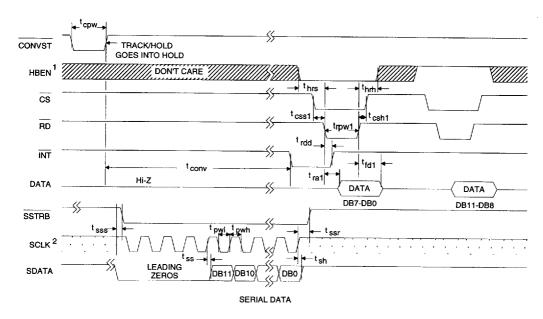

NOTE: FORMAT = +5V

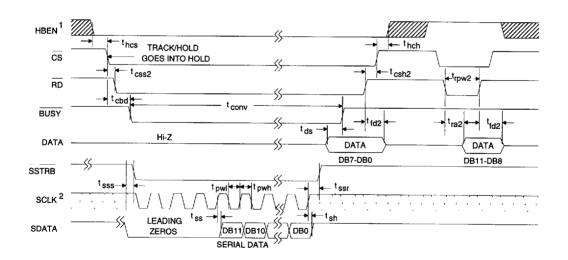

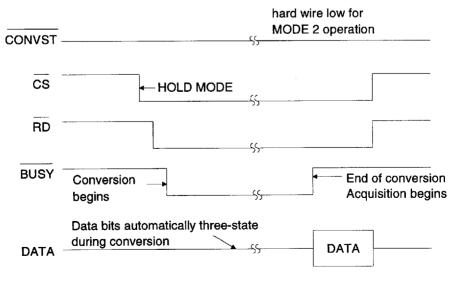

Figure 1. Mode 1 Timing Diagram, 12-Bit Parallel Read

NOTES: 1. Times t<sub>css1</sub>, t<sub>rpw1</sub>, t<sub>csh1</sub> and t<sub>hrh</sub> are the same for a high byte read as for a low byte read.

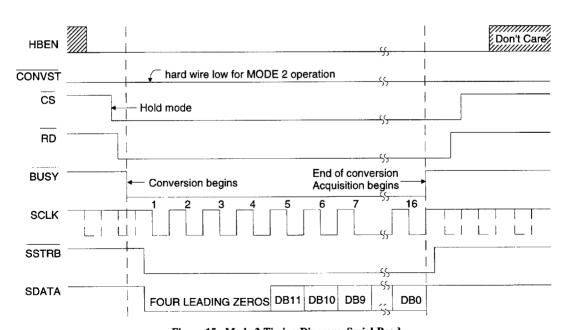

Continuous SCLK(Dashed line) when FORMAT = -5V Noncontinuous when FORMAT = 0V.

Figure 2. Mode 1 Timing Diagram, Byte or Serial Read

**DS118PP3**

2-85

# **SWITCHING CHARACTERISTICS** (Continued)

|                                      |           |                   |     | В        |     |          | Т       |     |       |

|--------------------------------------|-----------|-------------------|-----|----------|-----|----------|---------|-----|-------|

| Parameter                            |           | Symbol            | Min | Тур      | Max | Min      | Тур     | Max | Units |

| Specified Temperature Range          |           |                   | -   | 40 to +8 | 5   | -5       | 5 to +1 | 25  | °C    |

| Mode 2 Timing                        |           |                   |     |          |     |          |         |     |       |

| Conversion Time                      |           | tconv             | -   |          | 16  | -        | •       | 16  | MMC*  |

| CS Active to RD Active               |           | t <sub>css2</sub> | 10  | _        | -   | 10       | -       | -   | ns    |

| CS Active to BUSY Active             |           | tcbd              | -   | -        | 75  | -        |         | 75  | ns    |

| Data Setup Time to BUSY Inactive     |           | tds               | 50  | -        |     | 50       | -       | -   | ns    |

| RD Inactive to CS Inactive           |           | tcsh2             | 0   | -        | -   | 0-       | -       |     | ns    |

| Output Float Delay: RD Rising to Hi- | Z         | tfd2              | 5   | -        | 50  | 5        | -       | 50  | ns    |

| HBEN Low to CS Active Setup Time     | )         | thes              | 0   | -        |     | 0-       | -       | -   | ns    |

| CS Inactive to HBEN Hold Time        |           | thch              | 0   | -        | -   | 0        | •       | -   | ns    |

| RD Pulse Width                       |           | trpw2             | 60  | -        | •   | 75       | -       | -   | ns    |

| Data Access Time After RD            | (Note 10) | t <sub>ra2</sub>  | -   |          | 57  | <u>-</u> | -       | 70  | ns    |

| Serial Clock Timing                  |           |                   |     |          |     |          |         |     |       |

| Serial Clock Pulse Width Hig         |           | tpwh              | 0.4 | -        | 0.6 | 0.4      | -       | 0.6 | MCC*  |

| Pulse Width Low                      |           | tpwl              | 0.4 | -        | 0.6 | 0.4      |         | 0.6 | MCC*  |

| SCLK to SSTRB Falling Time (Note 12) |           | t <sub>sss</sub>  | 25  | -        | -   | 25       | -       | •   | ns    |

| SCLK rising to Data Valid (Note 13)  |           | tss               | -   | -        | 30  | -        | -       | 30  | ns    |

| SCLK rising to SSTRB Inactive        |           | tssr              | 10  |          | 25  | 10       | •       | 25  | ns    |

| SCLK rising to SDATA Hold Time       |           | tsh               | 10  | -        | 25  | 10       | -       | 25  | ns    |

<sup>\*</sup>MCC = Master Clock Cycles, 1 MCC = tclk

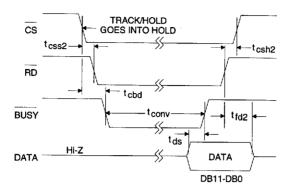

NOTE: FORMAT = +5V. Figure 3. Mode 2 Timing Diagram, 12-Bit Parallel Read

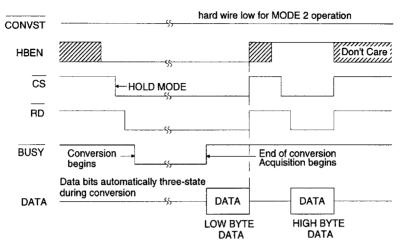

NOTES: 1.Times thcs, tcss2, tcsh2 and thch are the same for a high byte read as for a low byte read.

2. Continuous SCLK(Dashed line) when FORMAT = -5V

Noncontinuous when FORMAT = 0V.

Figure 4. Mode 2 Timing Diagram, Byte or Serial Read

# DIGITAL CHARACTERISTICS (TA = TMIN to TMAX: VA+ = +5V±5%; VA- = -5V±5%)

| Parameter                               |           | Symbol | Min | Тур | Max | Units |

|-----------------------------------------|-----------|--------|-----|-----|-----|-------|

| Logic Inputs                            |           |        |     |     |     |       |

| High-level Input Voltage                |           | ViH    | 3.3 |     |     | V     |

| Low-level Input Voltage                 |           | VIL    |     |     | 0.8 | V     |

| Input leakage current                   |           | lin    |     |     | 50  | μΑ    |

| Input Capacitance                       |           | Cin    |     |     | 10  | pF    |

| Logic Outputs                           |           |        |     |     |     |       |

| High-level Output Voltage               | (Note 13) | Voн    | 4.0 |     |     | V     |

| Low-level Output Voltage                | (Note 14) | Vol    |     |     | 0.4 | V     |

| DB11-DB0 Floating State leakage Current |           | loz    |     |     | 10  | μА    |

| DB11-DB0 Output Capacitance             | ***       | Cout   |     |     | 15  | pF    |

Notes:

13.  $I_{source} = -40\mu A$

14.  $I_{sink} = 1.6 \text{ mA}$

Figure 5. Load Circuits for Access Time

Figure 6. Load Circuits for Output Float Delay

# **RECOMMENDED OPERATING CONDITIONS** (AGND, DGND = 0V. All voltages with respect to ground)

| Parameter                          | Symbol | Min          | Тур | Max  | Units |

|------------------------------------|--------|--------------|-----|------|-------|

| Positive Analog Supply             | VA+    | 4.75         | 5.0 | 5.25 | V     |

| Negative Analog Supply             | VA-    | 4.75         | 5.0 | 5.25 | V     |

| Analog Input Voltage               | Ain    | -2.5         |     | +2.5 | V     |

| FORMAT Input Voltage Range         |        | VA-, 0V, VA+ |     | V    |       |

| CLKIN Input Voltage Range          |        | 0            |     | VA+  | V     |

| Other Digital Input Voltage Ranges |        | 0            |     | VA+  | V     |

| External Clock Frequency           |        |              | 10  |      | MHz   |

| External Clock Jitter              |        |              |     | 65   | ps    |

| AGND to DGND Voltage Differential  |        |              |     | 10   | mV    |

# ABSOLUTE MAXIMUM RATINGS (AGND = 0V, All voltages with respect to ground)

| Parameter                                                | Symbol          | Min        | Тур     | Max         | Units |  |

|----------------------------------------------------------|-----------------|------------|---------|-------------|-------|--|

| Positive Analog Supply                                   | VA+             | -0.3       | •       | 6.0         | V     |  |

| Negative Analog Supply                                   | VA-             | 0.3        |         | 6.0         | ٧     |  |

| Analog Input Voltage                                     | A <sub>in</sub> | (VA-)-0.3  |         | (VA+)+0.3   | ٧     |  |

| FORMAT Input Voltage Range                               |                 | (VA-)-0.3  |         | (VA+)+0.3   | ٧     |  |

| CLKIN Input Voltage Range                                |                 | (VA-)-0.3  |         | (VA+)+0.3   | ٧     |  |

| Other Digital Input Voltage Ranges                       |                 | (VA-)-0.3  |         | (VA+)+0.3   | ٧     |  |

| REF OUT Current                                          |                 |            |         | 10          | mA    |  |

| Sustained Digital Output Current                         |                 |            |         | 5           | mA    |  |

| AGND to DGND Voltage Differential                        |                 |            |         | 100         | mV    |  |

| Operating Temperature Range<br>CS5032-BP/BS<br>CS5032-TD |                 | -40<br>-55 | 1 0 000 | +85<br>+125 | °Ç    |  |

| Storage Temperature Range                                |                 | -65        |         | +150        | °C    |  |

| Lead Solder Temperature                                  |                 |            |         | +300        | °C    |  |

<sup>\*</sup> WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes

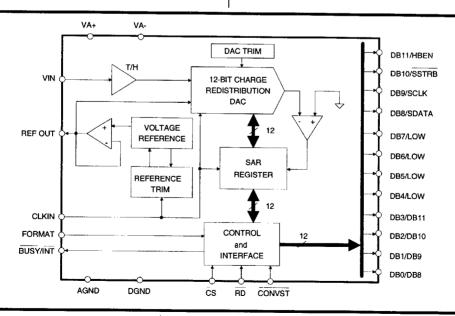

#### GENERAL DESCRIPTION

The CS5032 is a complete 12-bit 500 kSPS sampling ADC utilizing a successive approximation architecture. Factory calibration ensures 12-bit conversion accuracy over industrial and military temperature ranges. The analog input range is ±2.5 V, with the output data provided in parallel, byte or serial formats. The internal capacitor array DAC acts as an inherent sample-and-hold, and forms the heart of the CS5032. The on-chip +2.5 V reference is available at the REFOUT pin. Additionally, an on-chip 10 MHz clock oscillator can be used to control converter operations.

#### **OPERATIONAL OVERVIEW**

## Track-and-Hold Operation

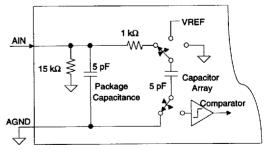

Track-and-hold operation within the CS5032 is transparent to the user. The capacitor array DAC acts as the hold capacitor. During tracking mode all elements of the capacitor array DAC are switched to the analog input for charging. The load capacitance of the entire array during tracking mode is typically 5 pF. The input bandwidth of the track-and-hold is typically 2 MHz. The ADC goes into hold mode on the rising edge of CONVST.

# Capacitor Array DAC Calibration

To achieve 12-bit accuracy from the capacitor array DAC, the CS5032 uses a novel calibration scheme. Each bit capacitor consists of several capacitors that are trimmed to optimize the overall bit weighting with an internal resolution of 14-bits, resulting in nearly ideal differential and integral linearity.

The calibration coefficients for the capacitive bit weights are stored in an on-chip EEPROM during the factory calibration. When the converter is subsequently powered-up these coefficients are applied to the capacitor array DAC. The low temperature coefficient of the capacitor array easily maintains 12-bit accuracy over the full temperature range without recalibration.

# Reference Operation

The reference voltage is available at the REF OUT pin and is capable of sourcing 500  $\mu$ A to peripheral devices. This pin must be decoupled with a parallel combination of a +10  $\mu$ F tantalum capacitor and a 0.1  $\mu$ F ceramic capacitor. The reference voltage is calibrated on power-up, with full accuracy achieved after 1.1 sec.

# Analog Input

The CS5032 provides a  $\pm 2.5$  V analog input voltage range. The equivalent analog input circuit is illustrated in Figure 7 (shown in track mode). During hold mode the input impedance to the device is typically 10 M $\Omega$ , and the various elements of the capacitor array DAC are connected to either AGND or VREF. In switching back from hold mode to track mode, some elements in the capacitor array must be charged by the analog input. For the CS5032, the worst case charging current occurs when the analog input changes from +2.5 V to -2.5 V.

Figure 7. Analog Input Model.

To ensure that the capacitor array DAC has settled to within 0.25 LSB during the allowed acquisition time, the external source resistance should be less than  $4 \text{ k}\Omega$ .

#### Output Coding

The digital output coding is 2's complement.

| Input Level | 2's Complement Output |

|-------------|-----------------------|

| +2.5 V      | 0111 1111 1111        |

| 0 V         | 0000 0000 0000        |

| -2.5 V      | 1000 0000 0000        |

# High-Speed System Clock

The CS5032 employs a high-speed clock (typically 10 MHz) to control internal operations. This high-speed clock can be generated internally with the on-chip oscillator, or it can be supplied from an external CMOS source. Connecting a CMOS clock signal to the CLKIN pin allows the converter to operate from an external clock. Alternatively, connecting the CLKIN pin to VA- activates the internal clock oscillator.

| External ClockCLKIN = External Clock Source |

|---------------------------------------------|

| Internal ClockCLKIN = VA-                   |

#### **CONVERT Clock Considerations**

When digitizing time varying signals, it is possible to create additional noise sources over and above those resulting from quantization noise and thermal noise. This is particularly true when high-speed conversion rates, or high-frequency analog input frequencies are involved. Special care must be taken to see that CONVST clock jitter does not undermine high-speed signal processing applications by introducing noise into the conversion process.

Simple quantization noise is a direct result of the finite LSB size, which is itself related to the number of digital output bits. Quantization noise places a hard limit on SNR for a 12-Bit ADC according to the following equation.

$SNR_{MAXQuantization} = (6.02dB)(\# of Bits) + 1.76dB$

... SNRMAXQuantization = 74 dB

Although SNR can never be better than the theoretical limit, it can certainly be worse. Jitter between the CONVST clock and the analog input signal is often one of the largest contributors to decreased SNR, particularly as frequencies increase.

To be considered insignificant, noise related to jitter (SNRMAXjitter) should be at least 12 dB below the other dominant noise sources, such as quantization noise (SNRMAXQuantization). The 12 dB target is somewhat arbitrary, but yield less than 4 % additional noise. In terms of the CS5032, a 250 kHz analog input signal requires less than 80 ps of jitter between the CONVST clock and the analog input signal to achieve full performance. The use of low-jitter CONVST clock source is the most common means of reducing the effects of jitter. Lower conversion rates and lower analog input frequencies are significantly less sensitive to jitter effects.

# Digital Output Formats

The CS5032 provides three digital output formats. These include 12-bit parallel, two 8-bit bytes, and a serial output mode. The output data

$$SNR_{MAX} = \sqrt{SNR_{MAXjitter}^2 + SNR_{MAXQuantization}^2}$$

$$SNR_{MAXjitter} (dB) = 20 Log \left[ \frac{1}{2\pi f_{IN} \text{ jitter}_{RMS}} \right]$$

jitter<sub>RMS</sub> =

$$\sqrt{\text{clock jitterRMS}^2 + \text{analog jitter RMS}^2}$$

format is controlled by the level applied to the FORMAT pin. All three of the digital output formats can be used with either of the convert start timing modes ... Mode 1 and Mode 2, which are described in the next two sections.

| FORMAT | Digital Outputs                    |

|--------|------------------------------------|

| +VA    | 12-Bit Parallel                    |

| GND    | Byte; Serial w/Non-Continuous SCLK |

| -VA    | Byte; Serial w/Continuous SCLK     |

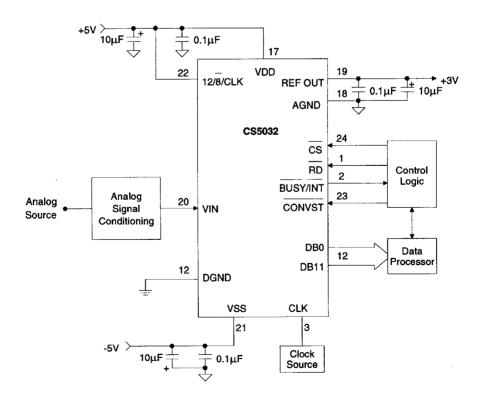

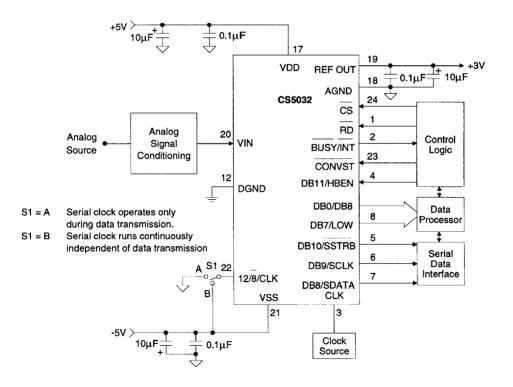

Figure 8 shows the schematic for the CS5032 in 12-bit parallel mode. The twelve bits of data are output simultaneously on DB11/(MSB) through DB0 (LSB).

In byte mode, two 8-bit read operations (four leading zeros with 4 data bits ... plus 8 more data bits) are required to collect the data as shown in Figure 9. In byte mode, the DB11/HBEN pin defers to the HBEN function, selecting the high or low byte of data to be read from the ADC. The lower eight bits of data are placed on the data bus when HBEN is held low. To access the four MSBs of data, HBEN must be held high. The 4 MSBs of the 12-bit data word are right justified with zeros in the upper nibble of the high byte.

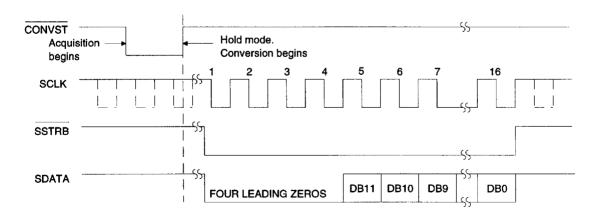

In serial mode, DB8/SDATA, DB9/SCLK and DB10/SSTRB defer to their serial functions. The serial strobe pin SSTRB provides a framing sig-

Figure 8. System Connection Diagram: Parallel Data Format

nal for serial data. Serial data is available at the SDATA pin when SSTRB falls low. SSTRB falls low within three clock cycles of CONVST. A total of sixteen bits (four leading zeros and twelve data bits starting with the MSB) are clocked out on the SDATA pin on the rising edge of SCLK. The data bits become valid no more than t<sub>ss</sub> after the rising edge of SCLK. SSTRB goes low during data transmission and automatically returns high when the LSB has been clocked out on the SDATA line. For serial op-

eration, 0V on the FORMAT pin causes the serial clock to run only when data is being clocked out of the device; SCLK goes high after data transmission is completed. If the FORMAT is connected to -VA, the SCLK output will run continuously, independent of data transmission. Serial data operation is identical for MODE 1 and MODE 2 timing control (see next two sections).

Figure 9. System Connection Diagram: Serial and Byte Data format

**DS118PP3**

#### MODE 1 Operation

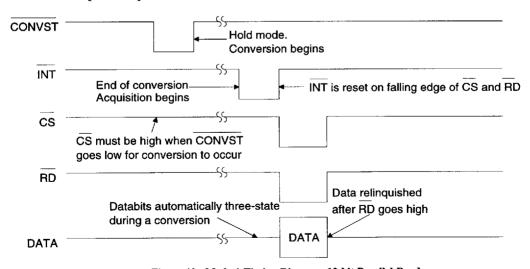

The rising edge of CONVST signal is used to put the device into hold mode and initiate a conversion. At the end of conversion the device returns to it's tracking mode. MODE 1 timing is primarily used in DSP type applications where precise control of CONVST timing is required.

Conversion begins on the rising edge of CONVST provided that CS is high. The BUSY/INT line performs the INT function and can be used to interrupt the microprocessor. INT is normally high and goes low at the end of conversion. The ADC returns to track mode when INT goes low. Bringing CS and RD low allows data to be read from the ADC, and also resets INT high. CONVST must be high when CS and RD are brought low for the ADC to operate correctly in this mode. Data cannot be read during a conversion cycle because the output data latches are disabled while a conversion is in progress.

#### **MODE 1 - 12-Bit Parallel Read**

Figure 10 shows the MODE 1 timing diagram for 12-bit parallel operation (FORMAT = +VA). A data read operation performed at the end of

conversion will read all twelve bits of data at the same time.

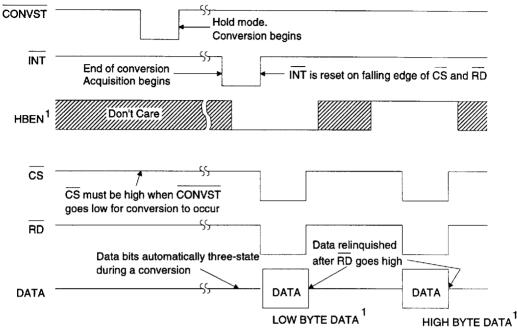

#### MODE 1 - Byte Read

Figure 11 shows the MODE 1 timing diagram for byte operation. At the end of conversion when INT goes low, either the low byte or the high byte of data can be read, depending on the status of HBEN. Bringing  $\overline{CS}$  and  $\overline{RD}$  low allows data to be read from the ADC and also resets  $\overline{INT}$  high.

#### MODE 1 - Serial Read

The MODE 1 timing diagram for serial operation is shown in Figure 12. Conversion begins on the rising edge of CONVST, and data is clocked out on SDATA immediately upon the falling edge of SSTRB. The data is output as four leading zeroes followed by the twelve data bits with the MSB first. The first zero should be latched into the external receiving circuitry on the first falling edge of SCLK after SSTRB goes low. A total of sixteen falling SCLK edges will latch all sixteen bits of output data. SSTRB automatically returns high after the last bit of data has been clocked out of the device.

Figure 10. Mode 1 Timing Diagram, 12-bit Parallel Read

NOTES: 1. In the above diagram HBEN is exercised to read the low byte first (DB7-DB0) and then the high byte (DB11-DB8). To change the order in which the bytes are read, simply invert the HBEN signal shown above.

Figure 11. Mode 1 Timing Diagram, Byte Read

Figure 12. Mode 1 Timing Diagram - Serial Read

**DS118PP3**

# MODE 2 Operation

Mode 2 operation allows the ADC conversion to be initiated by a read operation from a  $\mu C$ . The  $\overline{BUSY}$  signal can be used in this mode to halt  $\mu C$  operations by placing the  $\mu C$  in a WAIT state until the conversion is complete. This avoids having to handle interrupts and timing delays, assuring that the conversion cycle is complete before any attempted data read.

In this mode,  $\overline{\text{CONVST}}$  must be held permanently low. Bringing  $\overline{\text{CS}}$  low (while  $\overline{\text{HBEN}}$  is low) puts the device into hold mode and initiates a conversion. The  $\overline{\text{BUSY}}/\overline{\text{INT}}$  pin defers to the  $\overline{\text{BUSY}}$  function such that  $\overline{\text{BUSY}}$  goes low at the start of conversion and returns high at the end of conversion.

#### MODE 2 - 12-Bit Parallel Read

The MODE 2 timing diagrams for the parallel data output format are shown in Figure 13. This mode of operation forces the  $\mu$ C into a WAIT

state until the conversion has been completed. It removes the risk of inadvertently reading invalid data before the conversion cycle has been completed.

#### MODE 2 - Byte Read

Figure 14 shows the timing diagram for byte operation in MODE 2. Since HBEN must be low to initiate a conversion, the lower byte of data will be accessed first during the two-byte read operation. This is followed by a second byte read operation (with HBEN high) to complete the data transfer.

#### MODE 2 - Serial Read

The timing diagram for MODE 2 serial operation is shown in Figure 15. The device goes into hold mode on the falling edge of  $\overline{CS}$  and conversion begins when  $\overline{BUSY}$  goes low. The data is clocked out similarly as for MODE 1 serial operation. Upon clocking of the final data bit  $\overline{BUSY}$  returns high indicating end of conversion.

Figure 13. Mode 2 Timing Diagram, 12-bit Parallel Read

Figure 14. Mode 2 Timing Diagram, Byte Read

Figure 15. Mode 2 Timing Diagram, Serial Read

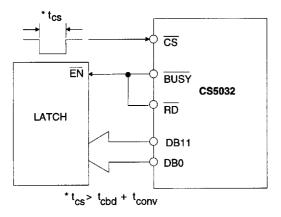

#### STAND-ALONE OPERATION

The CS5032 supports stand-alone conversion when used in MODE 2 parallel interface operation as shown in Figure 16. Conversion is initiated by pulse to the  $\overline{CS}$  input of the ADC. The duration of the pulse must be longer than the ADC conversion time. The  $\overline{BUSY}$  output drives the  $\overline{RD}$  input and data is latched on the rising edge of  $\overline{BUSY}$  to an external latch.

Figure 16. Stand-Alone Operation

#### Power Supplies, AGND, and DGND

Figure 8 illustrates the recommended power supply decoupling scheme with a 0.1  $\mu$ F ceramic and a +10  $\mu$ F tantalum capacitor for both the VA+ and the VA- pins. The capacitors should be located as close as practical to the supply pins. AGND is the power supply current return, and is also the preferred ground reference for the decoupling capacitors.

Typically a low-impedance ground plane is used around and under the ADC, with connections to both AGND and DGND. If a split ground is used, DGND is the ground reference for any digital circuits that follow the CS5032. When split grounds are used, the AGND to DGND voltage differential should be kept below ±10 mV for best operation.

If the power supply voltage is dropped below 3 V, the ADC may need to be reset by switching power off and then back on.

#### Layout considerations

The CS5032 is a high-speed component which requires adherence to standard high-frequency printed circuit board layout techniques to maintain optimum performance. These include proper supply decoupling, minimum length circuit traces, and physical separation of digital and analog components and circuit traces. See the CDB5032 evaluation board data sheet for more details.

#### PIN DESCRIPTIONS

| READ                  | RD              | <b>d</b> 1 | 24   | 3 | CS       | CHIP SELECT            |

|-----------------------|-----------------|------------|------|---|----------|------------------------|

| BUSY/INTERRUPT        | <b>BUSY/INT</b> | <b>2</b>   | 23   |   | CONVST   | CONVERT START          |

| CLOCK INPUT           | CLKIN           | □ 3        | 22   |   | FORMAT   | DATA OUTPUT FORMAT     |

| DB11/HIGH BYTE ENABLE | DB11/HBEN       | 4          | 21   |   | VA-      | NEGATIVE ANALOG SUPPLY |

| DB10/SERIAL STROBE    | DB10/SSTRB      | 5          | 20   |   | AIN      | ANALOG INPUT           |

| DB9/SERIAL CLOCK      | DB9/SCLK        | 6          | 19   |   | REF OUT  | VOLTAGE REF OUT        |

| DB8/SERIAL DATA       | DB8/SDATA       | 7          | 18   |   | AGND     | ANALOG GROUND          |

| DATA OUT              | DB7/LOW         | 8          | 17   |   | VA+      | POSITIVE ANALOG SUPPLY |

| DATA OUT              | DB6/LOW         | □ 9        | 16   |   | DB0/DB8  | DATA OUT               |

| DATA OUT              | DB5/LOW         | <b>1</b> 0 | 0 15 |   | DB1/DB9  | DATA OUT               |

| DATA OUT              | DB4/LOW         | <b>11</b>  | 1 14 | ] | DB2/DB10 | DATA OUT               |

| DIGITAL GROUND        | DGND            | 12         | 2 13 |   | DB3/DB11 | DATA OUT               |

|                       |                 | L          |      |   |          |                        |

Pinout applies to both DIP and SOIC packages.

#### Power Supply Connections

VA+ - Positive Supply, PIN 17. +5V±5%.

VA- - Negative Supply, PIN 21. -5V±5%.

# DGND - Digital Ground, PIN 12.

Ground reference for digital circuitry.

#### AGND - Analog Ground, PIN 18.

Ground reference for track-and-hold, reference and DAC.

#### Oscillator

# CLKIN - Clock Input, PIN 3.

An external 10MHz (CMOS compatible) clock is applied at this pin. Connecting this pin to VAenables the internal clock oscillator.

#### Digital Inputs

# CS - Chip Select, PIN 24.

Active low logic input. The device is selected when this input is active. With CONVST tied low, a new conversion is initiated when  $\overline{CS}$  goes low.

#### RD - Read, PIN 1.

Active low logic input. This input is used in conjunction with  $\overline{\text{CS}}$  low to enable the data outputs.

#### FORMAT - Output Mode Selection, PIN 22.

Defines the output data format and serial clock format. With FORMAT at +5V, the output data format is 12-bit parallel only. With FORMAT at 0V, either byte or serial data is available and SCLK is not continuous. With FORMAT at -5V, byte or serial data is again available but SCLK is now continuous.

#### **CONVST** – Convert Start, PIN 23.

A low to high transition on this input puts the track-and-hold into its hold mode and starts conversion. This input is asynchronous to the CLKIN and independent of  $\overline{CS}$  and  $\overline{RD}$ .

# Digital Outputs

# BUSY/INT - Busy/Interrupt, PIN 2.

Active low logic output indicating converter status. See timing diagrams.

#### DB11/HBEN - Data Bit 11/High Byte Enable, PIN 4.

The function of this pin is dependent on the state of the FORMAT input (see above). When 12-bit parallel data is selected, this pin provides the DB11 output. When byte data is selected, this pin becomes the HBEN logic input. HBEN is used for 8-bit bus interfacing. When HBEN is low, DB7/LOW to DB0/DB8 become DB7 to DB0. With HBEN high, DB7/LOW to DB0/DB8 are used for the upper byte of data (see Table 1).

#### DB10/SSTRB - Data Bit 10/Serial Strobe, PIN 5.

The function of this pin is dependent on the state of the FORMAT input (see above). When 12-bit parallel data is selected, this pin provides the DB10 output. If FORMAT is at either 0V or -5V, SSTRB provides a strobe or framing pulse for serial data.

#### DB9/SCLK - Data Bit 9/Serial Clock, PIN 6.

The function of this pin is dependent on the state of the FORMAT input (see above). When 12-bit parallel data is selected, this pin provides the DB9 output. SCLK is the gated serial clock output derived from the internal or external ADC clock. If FORMAT is at -5V, then SCLK runs continuously. If FORMAT is at 0V, then SCLK goes high after serial transmission is complete.

# DB8/SDATA - Data Bit 8/Serial Data, PIN 7.

The function of this pin is dependent on the state of the FORMAT input (see above). When 12-bit parallel data is selected, this pin provides the DB8 output. SDATA is used with SCLK and SSTRB for serial data transfer. Serial data is valid on the falling edge of SCLK while SSTRB is low.

2-100 DS118PP3

# DB7/LOW, DB6/LOW, DB5/LOW, DB4/LOW - Three-state data outputs, PINS 8, 9, 10, 11.

The outputs of these pins are controlled by  $\overline{CS}$  and  $\overline{RD}$ . Their function depends on the FORMAT and HBEN inputs. With FORMAT high, they are always DB7-DB4. With FORMAT low or -5V, their function is controlled by HBEN (see Table 1).

# DB3/DB11, DB2/DB10, DB1/DB9, DB0/DB8 - Three-state data outputs, PINS 13, 14, 15, 16.

The outputs of these pins are controlled by  $\overline{CS}$  and  $\overline{RD}$ . Their function depends on the FORMAT and HBEN inputs. With FORMAT high, they are always DB3-DB0. With FORMAT low or -5V, their function is controlled by HBEN (see Table 1).

| HBEN | DB7/LOW | DB6/LOW | DB5/LOW | DB4/LOW | DB3/DB11   | DB2/DB10 | DB1/DB9 | DB0/DB8   |

|------|---------|---------|---------|---------|------------|----------|---------|-----------|

| HIGH | LOW     | LOW     | LOW     | LOW     | DB11/(MSB) | DB10     | DB9     | DB8       |

| LOW  | DB7     | DB6     | DB5     | DB4     | DB3        | DB2      | DB1     | DB0/(LSB) |

Table 1. Output Data for Byte Interfacing

#### Analog Output

#### **REF OUT - Voltage Reference Output, PIN 19.**

The internal 2.5V reference is provided at this pin. The external load capability is  $500\mu A$ . This pin should be decoupled to AGND with a  $+10\mu F$  tantalum and a  $0.1\mu F$  ceramic capacitor. The REF OUT voltage has a settling time of approximately 1.1 sec.

# **Analog Input**

#### AIN - Analog Input, PIN 20.

The analog input range for the CS5032 is  $\pm 2.5$ V.

# **Ordering Guide**

| Model Number | Throughput<br>(kSPS) | Input<br>Range (V) | Linearity<br>Error (LSB) | Temp.<br>Range (°C) | Package            |

|--------------|----------------------|--------------------|--------------------------|---------------------|--------------------|

| CS5032-BP    | 500                  | ±2.5               | ±0.5                     | -40 to +85          | 24-Pin 0.3" PDIP   |

| CS5032-BS    | 500                  | ±2.5               | ±0.5                     | -40 to +85          | 24-Pin 0.3" SOIC   |

| CS5032-TD    | 500                  | ±2.5               | ±0.5                     | -55 to +125         | 24-Pin 0.3" CERDIP |

#### PARAMETER DEFINITIONS

# Integral Non-Linearity Error - INL

The deviation of a code from a straight line passing through the endpoints of the transfer function after zero- and full-scale errors have been accounted for. "Zero-scale" is a point 1/2 LSB below the first code transition and "full-scale" is a point 1/2 LSB beyond the code transition to all ones. The deviation is measured from the middle of each particular code.

#### **REF OUT Tempco**

REF OUT Tempco is the worst case slope that is calculated from the change in reference value at +25°C to the value at TMIN or TMAX

i.e. REF OUT Tempco =  $(V_{ref} @ 25^{\circ}C - V_{ref} @ T_{MAX})/(T_{MAX} - 25^{\circ}C)$  or REF OUT Tempco =  $(V_{ref} @ 25^{\circ}C - V_{ref} @ T_{MIN})/(25^{\circ}C - T_{MIN})$ .

### Differential Nonlinearity - DNL

The deviation of a code's width from the ideal. Units in LSBs.

#### Full-Scale Error - FSEP

The deviation of the last code transition from the ideal (VREF-3/2 LSB's). Units in LSB's.

# Bipolar Offset - VBP

The deviation of the mid-scale transition (011...111 to 100...000) from the ideal (1/2 LSB below AGND). Units in LSB's.

#### Bipolar Negative Full-Scale Error - FSEN

The deviation of the first code transition from the ideal. The ideal is defined as lying on a straight line which passes through the final and mid-scale code transitions. Units in LSB's.

#### Spurious-Free-Dynamic-Range - SFDR

The ratio of the rms value of the signal, to the rms value of the next largest spectral component (excepting dc). This component is often an aliased harmonic. Units in percent and dBc (decibels relative to the carrier).

#### **Total Harmonic Distortion - THD**

The ratio of the rms sum of the significant (2<sup>nd</sup> thru 5<sup>th</sup>) harmonics, to the rms value of the signal. Units in percent.

#### Signal-to-Noise-and-Distortion (s/n) - SNR

The ratio of the rms value of the signal, to the rms sum of all other spectral components (excepting dc and distortion terms). Expressed in decibels.

#### Signal-to-Noise-and-Distortion (s/[n+d]) - SINAD

The ratio of the rms value of the signal, to the rms sum of all other spectral components (excepting dc), including distortion components. Expressed in decibels.

#### **Intermodulation Distortion - IMD**

The ratio of the rms value of the larger of the two test frequencies, which are each 6dB down from full-scale, to the rms value of the largest 2<sup>nd</sup> order and 3<sup>rd</sup> order intermodulation component. Units in decibles relative to carrier.

# Aperture Delay Time - tapd

The time required, after the converter goes into hold mode, for the sampling switch to open fully. Effectively a sampling delay which can be nulled by advancing the sampling signal. Unit in nanoseconds.

# Aperture Jitter - tapj

The range of variation in the aperture time. Effectively the "sampling window" which ultimately dictates the maximum input signal slew rate acceptable for a given accuracy.

$$SNR_{MAXjitter} (dB) = 20Log \left[ \frac{1}{2\pi f_{IN} jitter_{RMS}} \right]$$

$$jitter_{RMS} = \sqrt{clock jitter_{RMS}^2 + analog jitter_{RMS}^2}$$

To ensure that jitter does not affect the quantized signal quality, the jitter induced noise (SNRMAXjitter) must be at least 12dB below other substantial noise sources, such as quantization noise, see *Clock Considerations*. Units in picoseconds.