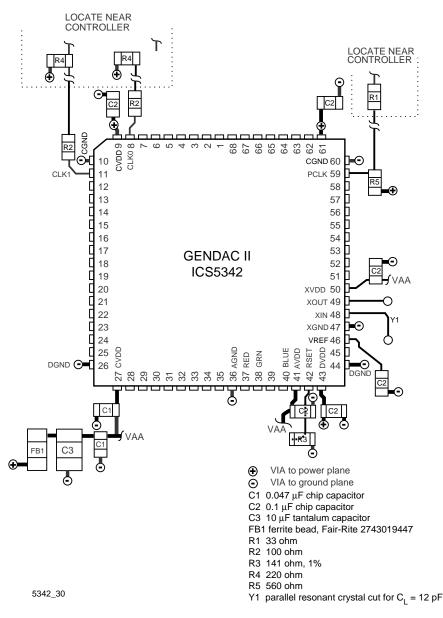

## **16-Bit Integrated Clock-LUT-DAC**

## DATA SHEET

### ICS5342

### **General Description**

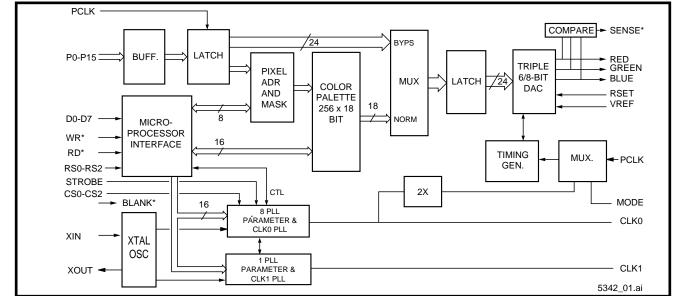

The ICS5342 GENDAC is a combination of dual programmable clock generators, a 256 x 18-bit RAM, and a triple 8-bit video DAC. The GENDAC supports 8-bit pseudo color applications, as well as 15-bit, 16-bit, and 24-bit True Color bypass for high speed, direct access to the DACs.

The RAM makes it possible to display 256 colors selected from a possible 262,144 colors. The dual clock generators use Phase Locked Loop (PLL) technology to provide programmable frequencies for use in the graphics subsystem. The video clock contains 8 frequencies, all of which are programmable by the user. The memory clock has two programmable frequency locations.

The three 8-bit DACs on the ICS5342 are capable of driving singly or doubly-terminated  $75\Omega$  loads to nominal 0 - 0.7 volts at pixel rates up to 135 MHz. Differential and integral linearity errors are less than 1 LSB over full temperature and VDD ranges. Monotonicity is guaranteed by design. On-chip pixel mask register allows displayed colors to be changed in a single write cycle rather than by modifying the color palette.

ICS is the world leader in all aspects of frequency (clock) generation for graphics, using patented techniques to produce low jitter video timing.

### Features

- Triple video DAC, dual clock generator, and 16 bit pixel port

- Dynamic mode switch allows switching of color depth on a pixel by pixel basis

- 24 (packed and sparse), 16, 15, or 8-bit pseudo color pixel mode supports True Color, Hi-Color, and VGA modes

- High speed 256 x 6 x 3 color palette (135 MHz) with bypass mode and 8-bit DACs

- Eight programmable video (pixel) clock frequencies (CLK0)

- DAC power down in blanking mode

- Anti-sparkle circuitry

- On-chip loop filters reduce external components

- Standard CPU interface

- Single external crystal (typically 14.318 MHz)

- Monitor sense

- Internal voltage reference

- 135 MHz (-3), 110 MHz (-2) & 80 MHz (-1) versions

- Very low clock jitter

- Two latched frequency select pins or three non-latched frequency select pins (programmable)

- Hardware video checksum for manufacturing tests

### **Block Schematic**

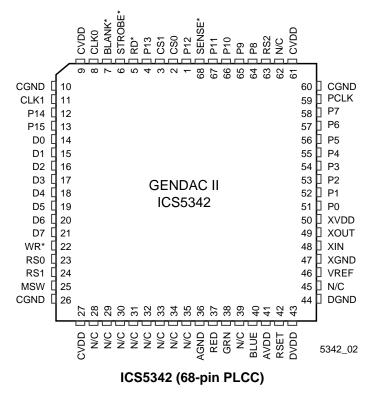

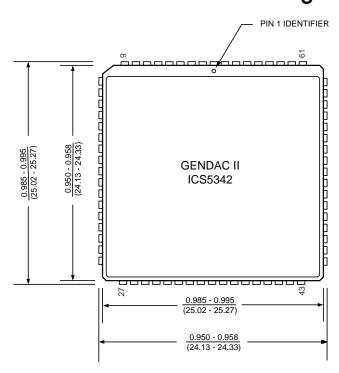

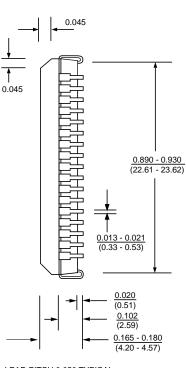

### **Pin Configuration**

### **Pin Description (68-pin PLCC)**

| Symbol  | Pin #    | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

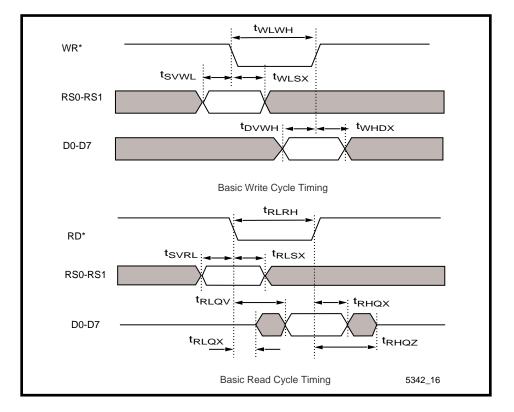

| D7 - D0 | 21-14    | I/O    | <ul> <li>Systems data bus bidirectional data I/O lines – used by host microprocessor for internal register read and write operations (using active low RD and WR respectively) for six internal registers: Pixel Address, Color Value, Pixel Mask, PLL</li> <li>Address, PLL Parameter, and Command</li> <li>During the write cycle, the rising edge of WR latches the data into the selected register (set by the status of the three RS pins).</li> <li>The rising edge of RD determines the end of the read cycle.</li> <li>The RD set logical high indicates that data I/O lines no longer contain information from the selected register and will be tri-stated.</li> </ul> |

| RD      | 5        | Input  | RAM/PLL read enable bus control signal – in active low state, any information present on the internal data bus is available on the Data I/O lines, D0-D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| WR      | 22       | Input  | Active low RAM/PLL write enable bus control signal – controls write timing on microprocessor interface inputs, D0-D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RS2-RS0 | 63,24,23 | Input  | Register address select 0 inputs – control selection of one of six internal registers – inputs are sampled on falling edge of active enable signal ( $\overline{RD}$ or $\overline{WR}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XIN     | 48       | Input  | Crystal input – connect to 14.318 MHz crystal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| XOUT    | 49       | Output | Crystal output – connect to 14.318 MHz crystal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MSW     | 25       | Input  | Mode switch – digital control for selecting primary and secondary pixel color<br>modes – low selects primary mode – connect to ground if not used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## Pin Description (68-pin PLCC)

| Symbol  | Pin #     | Туре          | Description                                                                                                                                                     |

|---------|-----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK1    | 11        | Output        | Memory clock output – used to time video memory                                                                                                                 |

| CLK0    | 8         | Output        | Video clock output – provides a CMOS level pixel or dot clock frequency to                                                                                      |

|         |           |               | graphics controller – output frequency is determined by values of PLL registers                                                                                 |

| CS0     | 2         | Input         | Clock select 0 – The status of CS0-1 determines which frequency is selected on                                                                                  |

|         |           |               | the CLK0 (video) output.                                                                                                                                        |

| CS1     | 3         | Input         | Clock select 1– status of CS0-1 determines which frequency is selected on CLK0                                                                                  |

|         |           | <b>X</b> (0)  | (video) output                                                                                                                                                  |

| VREF    | 46        | I/O           | Internal reference voltage – normally connects to a $0.1\mu f$ capacitor to ground – to                                                                         |

| DODT    | 42        | Innet         | use external Vref, connect 1.235V reference to this pin                                                                                                         |

| RSET    | 42        | Input         | Resistor set – pin used to set current level in analog outputs – usually connected through 1/4W, 1% resistor to ground                                          |

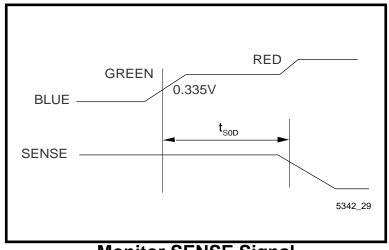

| SENSE*  | 68        | Output        | Monitor sense – Pin is active low when any of red, green, or blue outputs >385mV.                                                                               |

|         |           | - · · I · · · | Sense output is high when all analog outputs are < 275 mV. Chip has on-board                                                                                    |

|         |           |               | comparators and internal 1.235 V voltage reference. This signal is used to detect                                                                               |

|         |           |               | monitor type.                                                                                                                                                   |

| BLUE    | 40        | Output        | Color signals from DAC analog outputs - Each DAC comprises several current                                                                                      |

| GREEN   | 38        | Output        | sources of which outputs are added together according to the applied binary value.                                                                              |

| RED     | 37        | Output        | The outputs are typically used to drive a CRT monitor.                                                                                                          |

| P15- P0 | 13,12,4,1 | Input         | Pixel address lines – Byte-wide information is latched by the rising edge of PCLK                                                                               |

|         | ,         |               | when using the color palette, and is masked by the Pixel Mask register. Values are                                                                              |

|         | 67-64,    |               | used to specify the RAM word address in default mode (accessing RAM). In Hi-                                                                                    |

|         | 58-51     |               | Color XGA, and True Color modes, they represent color data for the DACs.                                                                                        |

|         | 50        | To a d        | Ground inputs if they are not used.                                                                                                                             |

| PCLK    | 59        | Input         | Pixel Clock – rising edge of PCLK controls latching of the Pixel Address and<br>PLANK* inputs – clock close controls programs of these values through the three |

|         |           |               | BLANK* inputs – clock also controls progress of these values through the three-<br>stage pipeline of the Color Palette RAM, DAC, and outputs                    |

| STROBE* | 6         | Input         | latches input clock select signals CS0-CS1                                                                                                                      |

| BLANK*  | 7         | Input         | Composite BLANK* Signal, active low. When BLANK* is asserted, outputs of                                                                                        |

| DLAINK  | /         | Input         | DACs are zero which blacks screen. DACs are automatically powered down to                                                                                       |

|         |           |               | save current during blanking. Color palette may still be updated through D0-D7                                                                                  |

|         |           |               | during blanking.                                                                                                                                                |

| CVDD    | 9         | -             | CLK1 Power Supply – connect to DVDD                                                                                                                             |

| CVDD    | 27        | -             | CLK0 power supply – connect to AVDD                                                                                                                             |

| AVDD    | 41        | -             | DAC power supply – Connect to AVDD                                                                                                                              |

| DVDD    | 43        | -             | Digital power supply                                                                                                                                            |

| XVDD    | 50        | -             | Crystal oscillator power supply– connect to AVDD                                                                                                                |

| CVDD    | 61        | -             | CLK power supply – connect to DVDD                                                                                                                              |

| CGND    | 10        | -             | VSS for CLK1 – connect to ground.                                                                                                                               |

| CGND    | 26        | -             | VSS for CLK0 – connect to ground                                                                                                                                |

| XGND    | 47        | -             | VSS for crystal oscillator                                                                                                                                      |

| AGND    | 36        | -             | DAC ground – connect to ground                                                                                                                                  |

| DGND    | 44        | -             | Digital ground – connect to ground                                                                                                                              |

| CGND    | 60        | -             | VSS for CLK – connect to ground                                                                                                                                 |

| N/C     | 28-35,    | -             | Not connected – leave floating or tie to ground                                                                                                                 |

|         | 39,45,    |               |                                                                                                                                                                 |

|         | 62        |               |                                                                                                                                                                 |

### **Internal Registers**

| RS2 | RS1 | RS0 | Register Name          | Description (all registers can be written to and read from)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-----|-----|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |     |     |                        | The GENDAC has a single pixel address register which can be accessed through either register address $0,0,0$ or $0,1,1$ – reading from either register gives the same result.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |     |     |                        | <ul> <li>Writing a value to address 0,0,0:</li> <li>specifies an address within the color palette RAM</li> <li>initializes the Color Value register</li> <li>Writing a value to address 0,1,1:</li> <li>specifies an address within the color palette RAM</li> <li>loads Color Value register with contents of location in addressed RAM palette and then:</li> <li>increments Pixel Address register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | 1   | 1   | Pixel Address<br>WRITE | Writing to this 8-bit register is done before writing one or more color values to color palette RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0   | 1   | 1   | Pixel Address<br>READ  | Writing to this 8-bit register is done before reading one or more color values from color palette RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0   | 0   | 1   | Color Value            | The 18-bit Color Value register acts as a buffer between the microprocessor interface and the color palette. A value may be read from or written to this register using a three-byte transfer sequence. The color value is contained in the least significant 6 bits, D0-D5, of the byte read – the most significant 2 bits are set to zero. The same 6 bits are used when writing a byte. When reading or writing, data is transferred in the same order – red byte first, then green, then blue. Each transfer between the Color Value register and the color palette replaces the normal pixel mapping operations of the GENDAC for a single pixel. After writing three definitions to this register, its contents are written to the location in the color palette RAM specified by the Pixel Address register, before that register increments. After reading three definitions from this register, the contents of the location in the color palette RAM specified by the Pixel Address registers are copied into the Color Value register, and the Pixel Address register increments. |

| 0   | 1   | 0   | Pixel Mask             | The 8-bit Pixel Mask register can be used to mask selected bits<br>of the Pixel Address value applied to the Pixel Address inputs<br>(P7-P0). A one in a position in the mask register leaves the corre-<br>sponding bit in the Pixel Address unaltered, while a zero sets<br>that bit to zero. The Pixel Mask register does not affect the Pixel<br>Address generated by the microprocessor interface when the pal-<br>ette RAM is being accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1   | 0   | 0   | PLL Address<br>WRITE   | Writing to this 8-bit register is performed prior to writing one or<br>more PLL programming values to the PLL Parameter register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1   | 1   | 1   | PLL Address<br>READ    | Writing to this 8-bit register is performed prior to reading one or more PLL programming values from the PLL Parameter register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

4

### **Internal Registers**

| RS2 | RS1 | RS0 | Register Name | Description (all registers can be written to and read from)         |

|-----|-----|-----|---------------|---------------------------------------------------------------------|

| 1   | 1   | 0   | Command       | This 8-bit register selects color mode, for instance 8-bit Pseudo   |

|     |     |     |               | Color, Hi-Color, True Color, or XGA, and DAC power down.            |

|     |     |     |               | The registers are reset to pseudo color mode on power up.           |

| 1   | 0   | 1   | PLL Parameter | There are 16 PLL parameter registers accessible as indexed by       |

|     |     |     |               | Read/Write registers. Parameter registers 0F and 0D-00 are two      |

|     |     |     |               | bytes long and 0E is one byte long. Register 0E is a control reg-   |

|     |     |     |               | ister. The bits of this register include clock select and enable    |

|     |     |     |               | functions, the rest contain PLL frequency parameters. After writ-   |

|     |     |     |               | ing the start index address in the PLL address register, these reg- |

|     |     |     |               | isters can be accessed in successive two (or one) bytes. The        |

|     |     |     |               | address register auto increments after one (0E) or two bytes to     |

|     |     |     |               | access the entire register                                          |

### **Absolute Maximum Ratings**

| Power Supply Voltage7 V                                   | DC Digital Output Current 25 mA |

|-----------------------------------------------------------|---------------------------------|

| Voltage on any other pin GND - $0.5V$ to VDD + $0.5V$     | Analog Output Current45 mA      |

| Temperature under bias – $40^{\circ}$ C to $85^{\circ}$ C | Reference Current15 mA          |

| Storage Temperature – $65^{\circ}$ C to $150^{\circ}$ C   | Power Dissipation 1.0 W         |

**Note:** Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### Electrical Characteristics DC CHARACTERISTICS (note: J)

| Parameter                                                             | Symbol              | Min.  | Max.                 | Units | Test Conditions                            |

|-----------------------------------------------------------------------|---------------------|-------|----------------------|-------|--------------------------------------------|

| Positive supply voltage                                               | V <sub>DD</sub>     | 4.75  | 5.25                 | V     |                                            |

| Input logic "1" voltage                                               | V <sub>IH</sub>     | 2.0   | V <sub>DD</sub> +0.5 | V     |                                            |

| Input logic "0" voltage                                               | V <sub>IL</sub>     | - 0.5 | 0.8                  | V     |                                            |

| Reference current                                                     | I <sub>REF</sub>    | -7.0  | -10                  | mA    |                                            |

| Reference voltage                                                     | V <sub>REF</sub>    | 1.10  | 1.35                 | V     |                                            |

| Digital input current                                                 | I <sub>IN</sub>     |       | ± 10                 | μA    | $V_{DD}=max, V_{DD}\geq V_{IN}\geq GND$    |

| Off-state digital output current                                      | I <sub>OZ</sub>     |       | ± 50                 | μA    | $V_{DD} = \max, V_{DD} \ge V_{IN} \ge GND$ |

| Average power supply current                                          | I <sub>DD</sub>     |       | 250                  | mA    | $I_{O} = max$ , Digital outputs            |

|                                                                       |                     |       |                      |       | unloaded                                   |

| DACs in power down mode                                               | I <sub>DACOFF</sub> |       | 50                   | mA    | no palette access                          |

| Sense logic "1"                                                       | V <sub>OHS</sub>    | 2.4   |                      | V     | I <sub>O</sub> = -0.4mA                    |

| Sense logic "0"                                                       | V <sub>OLS</sub>    |       | 0.4                  | V     | $I_{O} = 0.4 mA$                           |

| Clock logic "1"                                                       | V <sub>OHC</sub>    | 2.4   |                      | V     | I <sub>O</sub> = -12.0mA                   |

| Clock logic "0"                                                       | V <sub>OLC</sub>    |       | 0.4                  | V     | I <sub>O</sub> = 12.0mA                    |

| Logic "1"                                                             | V <sub>OH</sub>     | 2.4   |                      | V     | $I_{O} = -3.2$ mA, note K                  |

| Logic "0"                                                             | V <sub>OL</sub>     |       | 0.4                  | V     | $I_{O} = 3.2$ mA, note K                   |

| XIN input clock rise time                                             | XCLK <sub>r*</sub>  |       | 15                   | ns    | TTL levels                                 |

| XIN input clock fall time                                             | XCLK <sub>f*</sub>  |       | 15                   | ns    | TTL levels                                 |

| Frequency change of CLK0 and<br>CLK1 over supply and tempera-<br>ture | FD                  |       | 0.05                 | %     | with respect to typical frequency          |

TSD

### **DAC Characteristics**

| Parameter                        | Symbol               | Min | Max  | Units | Test Conditions         |

|----------------------------------|----------------------|-----|------|-------|-------------------------|

| Maximum output voltage           | V <sub>o</sub> (max) |     | 1.5  | V     | $I_0 \le 10 \text{ mA}$ |

| Maximum output current           | I <sub>o</sub> (max) |     | 21   | mA    | $V_0 \le 1V$            |

| Full scale error                 |                      |     | ± 5  | %     | note A, B               |

| DAC to DAC correlation           |                      |     | ±2   | %     | note B                  |

| Integral Linearity, 6-bit        |                      |     | ±0.5 | LSB   | note B                  |

| Integral Linearity, 8-bit        |                      |     | ±1   | LSB   | note B                  |

| Full scale settling time*, 6-bit |                      |     | 28   | ns    | note C                  |

| Full scale settling time*, 8-bit |                      |     | 20   | ns    | note C                  |

| Rise time (10% to 90%)*          |                      |     | 6    | ns    | note C                  |

| Glitch energy*                   |                      |     | 200  | pV.s  | note C                  |

### **PLL AC Characteristics**

| Parameter                  | Symbol           | Min     | Max    | Units | Test Conditions        |

|----------------------------|------------------|---------|--------|-------|------------------------|

| Clock 0 operating range    | f0               | 25      | 135    | MHz   |                        |

| Clock 1 operating range    | f <sub>1</sub>   | 25      | 135    | MHz   |                        |

| Output clocks rise time*   | t <sub>r</sub>   |         | 3      | ns    | 25 pF load, TTL levels |

| Output clocks fall time*   | t <sub>r</sub>   |         | 3      | ns    | 25 pF load, TTL levels |

| Duty Cycle*                | d <sub>t</sub>   | 40/60   | 60/40  | %     |                        |

| Jitter, one sigma*         | j <sub>1s</sub>  |         | 130 ps | ps    |                        |

| Jitter, absolute*          | j <sub>abs</sub> | -300 ps | 300 ps | ps    |                        |

| Input reference frequency* | f <sub>ref</sub> | 5       | 25     | MHz   | Typically 14.318 MHz   |

\* Characterized values only

### AC Electrical Characteristics (note: J)

| Parameter                | Symbol              | 80 MHZ |      | 110MHz |      | 135Mhz |     | Units | Test       |

|--------------------------|---------------------|--------|------|--------|------|--------|-----|-------|------------|

| Farameter                |                     | Min    | Max  | Min    | Max  | Min    | Max |       | Conditions |

| PCLK period              | t <sub>CHCH</sub>   | 12.5   |      | 9.09   |      | 7.4    |     | ns    |            |

| PCLK jitter              | $\Delta t_{CHCH}^*$ |        | ±2.5 |        | +2.5 |        |     | %     | note D     |

| PCLK width low           | t <sub>CLCH</sub>   | 5      |      | 3.6    |      | 3      |     | ns    |            |

| PCLK width high          | t <sub>CHCL</sub>   | 5      |      | 3.6    |      | 3      |     | ns    |            |

| Pixel word setup time    | t <sub>PVCH</sub>   | 3      |      | 3      |      | 2      |     | ns    | note E     |

| Pixel word hold time     | t <sub>CHPX</sub>   | 3      |      | 2      |      | 1      |     | ns    | note E     |

| BLANK* setup time        | t <sub>BVCH</sub>   | 3      |      | 3      |      | 2      |     | ns    | note E     |

| BLANK* hold time         | t <sub>CHBX</sub>   | 3      |      | 2      |      | 1      |     | ns    | note E     |

| PCLK to valid DAC output | t <sub>CHAV</sub> * |        | 20   |        | 20   |        | 20  | ns    | note F     |

| De                             | Symbol               | 80 MHZ                    |     | 110MHz                    |     | 135Mhz                    |     | TImita | Test        |

|--------------------------------|----------------------|---------------------------|-----|---------------------------|-----|---------------------------|-----|--------|-------------|

| Parameter                      |                      | Min                       | Max | Min                       | Max | Min                       | Max | Units  | Conditions  |

| Differential output delay      | $\Delta t_{CHAV}$    |                           | 2   |                           | 2   |                           | 2   | ns     | note G      |

| WR* pulse width low            | t <sub>WLWH</sub>    | 50                        |     | 50                        |     | 50                        |     | ns     |             |

| RD* pulse width low            | t <sub>RLRH</sub>    | 50                        |     | 50                        |     | 50                        |     | ns     |             |

| Register select setup time     | t <sub>SVWL</sub>    | 10                        |     | 10                        |     | 10                        |     | ns     | write cycle |

| Register select setup time     | t <sub>SVRL</sub>    | 10                        |     | 10                        |     | 10                        |     | ns     | read cycle  |

| Register select hold time      | t <sub>WLSX</sub>    | 10                        |     | 10                        |     | 10                        |     | ns     | write cycle |

| Register select hold time      | t <sub>RLSX</sub>    | 10                        |     | 10                        |     | 10                        |     | ns     | read cycle  |

| WR* data setup time            | t <sub>DVWH</sub>    | 10                        |     | 10                        |     | 10                        |     | ns     |             |

| WR* data hold time             | t <sub>WHDX</sub>    | 10                        |     | 10                        |     | 10                        |     | ns     |             |

| Output turn-on delay           | t <sub>RLQX</sub>    | 5                         |     | 5                         |     | 5                         |     | ns     |             |

| RD* enable access time         | t <sub>RLQV</sub>    |                           | 40  |                           | 40  |                           | 40  | ns     |             |

| Output hold time               | t <sub>RHQX</sub>    | 3                         |     | 3                         |     | 3                         |     | ns     |             |

| Output turn-off delay          | t <sub>RHQZ</sub>    |                           | 20  |                           | 20  |                           | 20  | ns     | note H      |

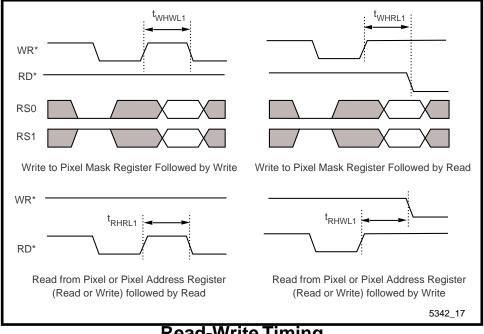

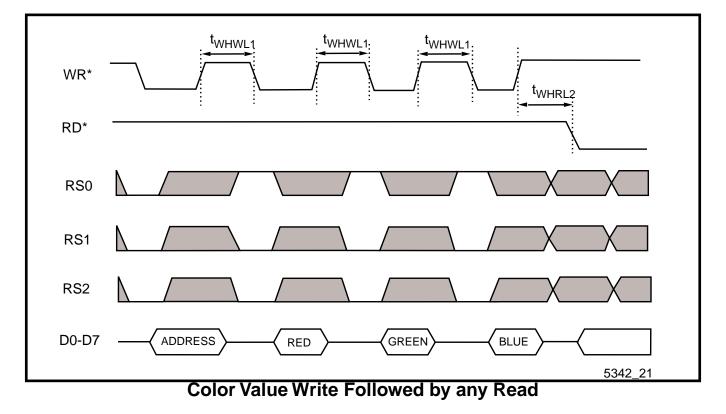

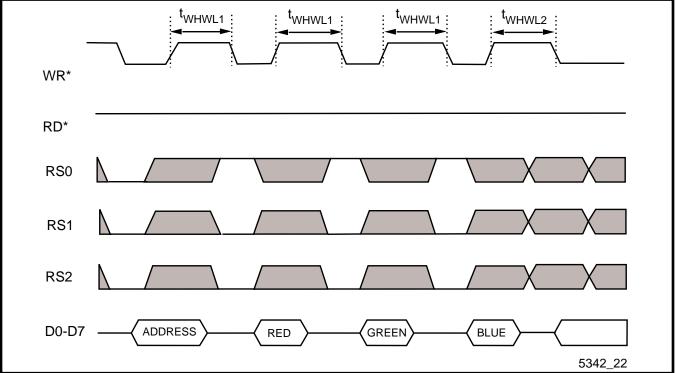

| Successive write inter-<br>val | t <sub>WHWL1</sub>   | 4<br>(t <sub>CHCH</sub> ) |     | 4<br>(t <sub>CHCH</sub> ) |     | 4<br>(t <sub>CHCH</sub> ) |     | cycle  | note I      |

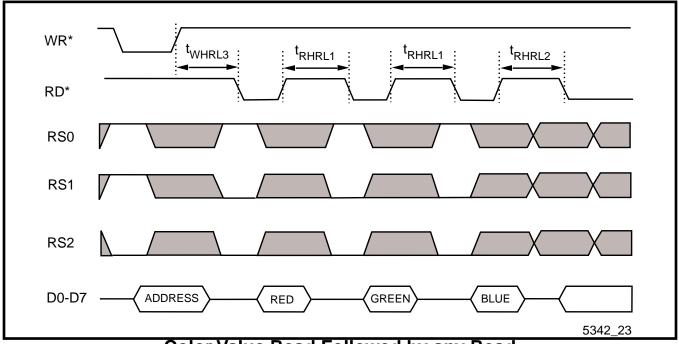

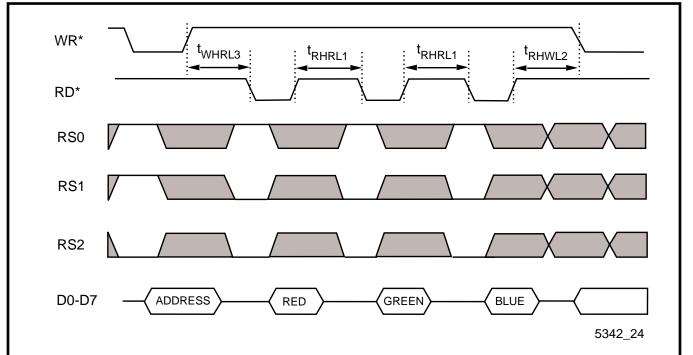

| WR* followed by read interval  | t <sub>WHRL1</sub>   | 4<br>(t <sub>CHCH</sub> ) |     | 4<br>(t <sub>CHCH</sub> ) |     | 4<br>(t <sub>CHCH</sub> ) |     | cycle  | note I      |

| Successive read interval       | t <sub>RHRL1</sub>   | 4<br>(t <sub>CHCH)</sub>  |     | 4<br>(t <sub>CHCH</sub> ) |     | 4<br>(t <sub>CHCH</sub> ) |     | cycle  | note I      |

| RD* followed by write interval | t <sub>RHWL1</sub>   | 4<br>(t <sub>CHCH)</sub>  |     | 4<br>(t <sub>CHCH</sub> ) |     | 4<br>(t <sub>CHCH</sub> ) |     | cycle  | note I      |

| WR* after color write          | t <sub>WHWL2</sub>   | 4<br>(t <sub>CHCH)</sub>  |     | 4<br>(t <sub>CHCH</sub> ) |     | 4<br>(t <sub>CHCH</sub> ) |     | cycle  | note I      |

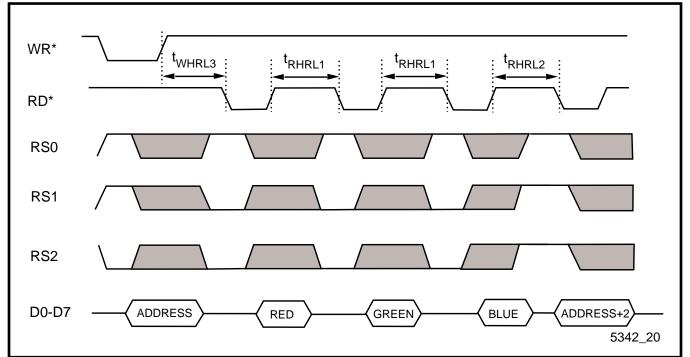

| RD* after color write          | t <sub>WHRL2</sub>   | 4<br>(t <sub>CHCH</sub> ) |     | 4<br>(t <sub>CHCH</sub> ) |     | 4<br>(t <sub>CHCH)</sub>  |     | cycle  | note I      |

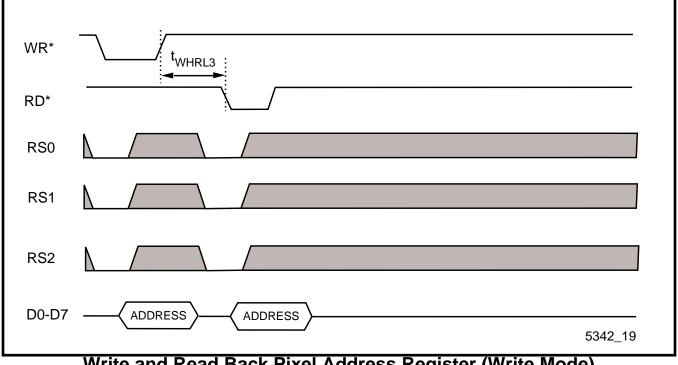

| RD* after color read           | t <sub>RHRL2</sub>   | 8<br>(t <sub>CHCH</sub> ) |     | 8<br>(t <sub>CHCH</sub> ) |     | 8<br>(t <sub>CHCH)</sub>  |     | cycle  | note I      |

| WR* after color read           | t <sub>RHWL2</sub>   | 8<br>(t <sub>CHCH</sub> ) |     | 8<br>(t <sub>CHCH</sub> ) |     | 8<br>(t <sub>CHCH</sub> ) |     | cycle  | note I      |

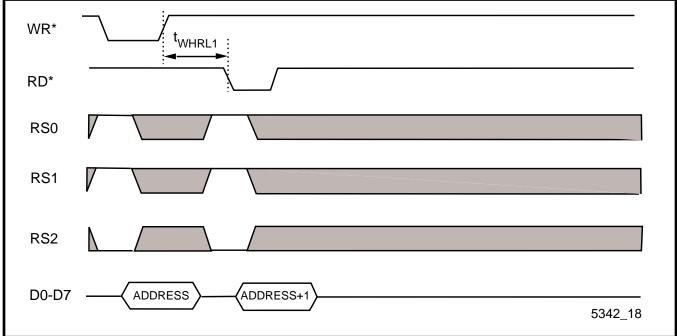

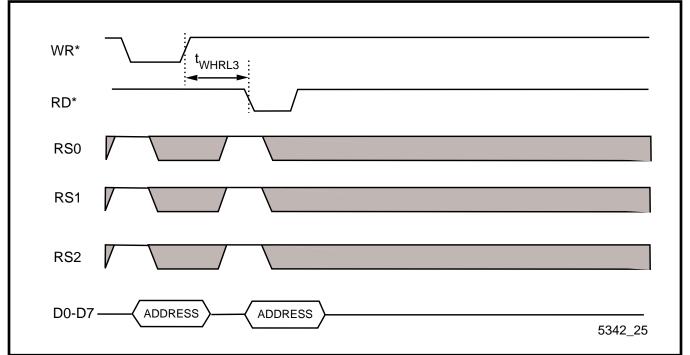

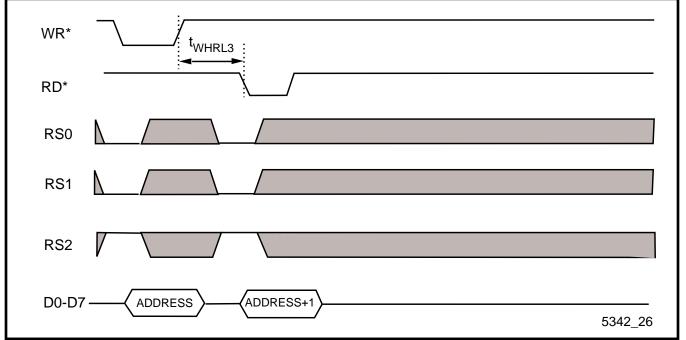

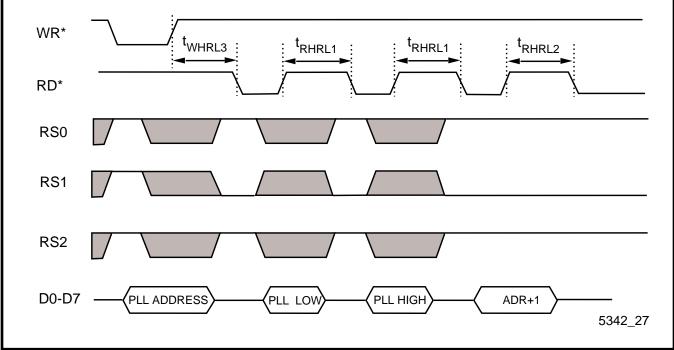

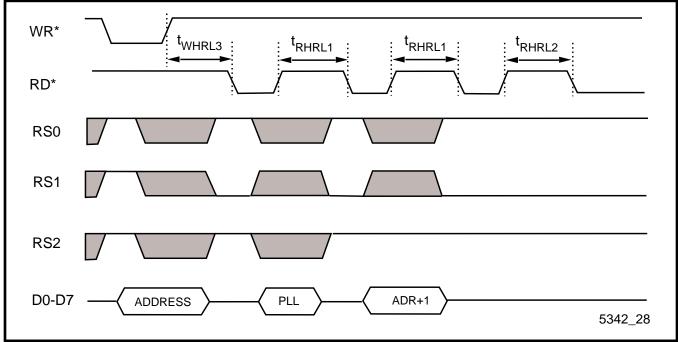

| RD* after read address write   | t <sub>WHRL3</sub>   | 8<br>(t <sub>CHCH)</sub>  |     | 8<br>(t <sub>CHCH</sub> ) |     | 8<br>(t <sub>CHCH</sub> ) |     | cycle  | note I      |

| SENSE* output delay            | t <sub>SOD</sub>     |                           | 1   | -                         | 1   | 1                         |     | μs     |             |

| XIN input clock rise time      | t <sub>XCLKR</sub> * |                           | 15  |                           | 15  |                           | 15  | ns     | TTL levels  |

### AC Electrical Characteristics (note: J)

| Parameter                    | Symbol               | 80 MHZ |     | 110MHz |     | 135Mhz |     | Units | Test       |

|------------------------------|----------------------|--------|-----|--------|-----|--------|-----|-------|------------|

| Parameter                    |                      | Min    | Max | Min    | Max | Min    | Max |       | Conditions |

| XIN input clock fall<br>time | t <sub>XCLKF</sub> * |        | 15  |        | 15  |        | 15  | ns    | TTL levels |

\* Characterized values only

Notes:

- A. Full scale error is derived from design equation:  $\{[(F.S.I_{OUT})R_L - 2.1(I_{REF})R_L] / [2.1(I_{REF})R_L]\} 100\%$   $V_{BLACK \ LEVEL} = 0 \ V$ F.S.I\_{OUT} = Actual full scale measured output

- B.  $R = 37.5 \Omega$ ,  $I_{REF} = -8.88 mA$

- C.  $Z_I = 37.5 \ \Omega + 30 \ pF$ ,  $I_{REF} = -8.88 \ mA$

- D. This parameter is the allowed Pixel Clock frequency variation. It does not permit the Pixel Clock period to vary outside the minimum values for Pixel Clock  $(t_{CHCH})$  period.

- E. The color palette's pixel address is required to be a valid logic level with the appropriate setup and hold times at each rising edge of PCLK (this requirement includes the blanking period).

- F. The output delay is measured from the 50% point of the rising edge of CLOCK to the valid analog output. A valid analog output is defined when the analog signal is halfway between its successive values.

- G. This applies to different analog outputs on the same device.

- H. Measured at  $\pm 200 \text{ mV}$  from steady state output voltage.

- I. This parameter allows synchronization between operations on the microprocessor interface and the pixel stream being processed by the color palette.

- J. The following specifications apply for  $V_{DD} = +5V \pm 0.5V$ , GND=0. Operating Temperature = 0°C to 70°C.

- K. Except for SENSE pin.

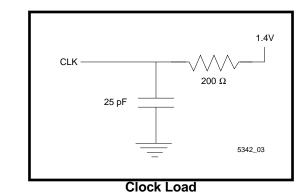

### **AC Test Conditions**

Input pulse levels ......  $V_{DD}$  to 3V

| Input rise and fall times (10% to 90%)             | ns  |

|----------------------------------------------------|-----|

| Digital input timing reference level 1.4           | 5 V |

| Digital output timing reference level0.8 V and 2.4 | 4 V |

### Capacitance

| C <sub>1</sub> Digital input  | 7 pF  |

|-------------------------------|-------|

| C <sub>0</sub> Digital output | 7 pF  |

| C <sub>0A</sub> Analog output | 10 pF |

### **General Operation**

The ICS5342 GENDAC is intended for use as the analog output stage of raster scan video systems. It contains a high-speed Random Access Memory of 256 x 18-bit words, three 6/8-bit high-speed DACs, a microprocessor/graphic controller interface, a pixel word mask, on-chip comparators, and two user programmable frequency generators.

An externally generated BLANK\* signal can be applied to pin 7 of the ICS5342. This signal acts on all three of the analog outputs. The BLANK\* signal is delayed internally so that it appears with the correct relationship to the pixel bit stream at the analog outputs.

A pixel word mask is included to allow the incoming pixel address to be masked. This permits rapid changes to the effec-

tive contents of the color palette RAM to facilitate such operations as animation and flashing objects. Operations on the contents of the mask register can also be totally asynchronous to the pixel stream.

The ICS5342 also includes dual PLL frequency generators providing a video clock (CLK0) and a memory clock (CLK1), both generated from a single 14.318 MHz crystal. There are eight selectable CLK0 frequencies. All eight are programmable. There are two selectable and programmable CLK1 frequencies (fA, fB). Default values (Shown in tables: "Video Clock Default Frequency Registers," and "Memory Clock Default Frequency Registers") are loaded into the appropriate registers on power up.

### Video Path

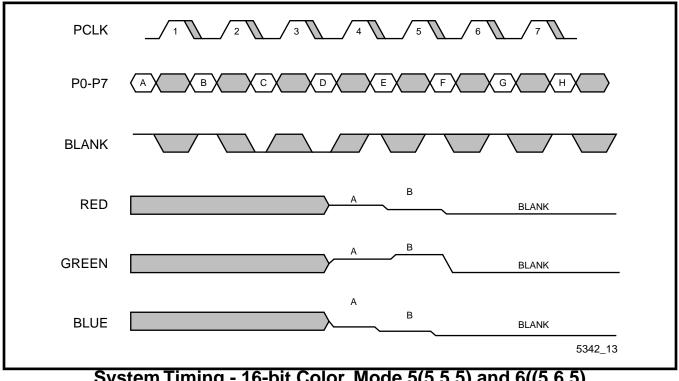

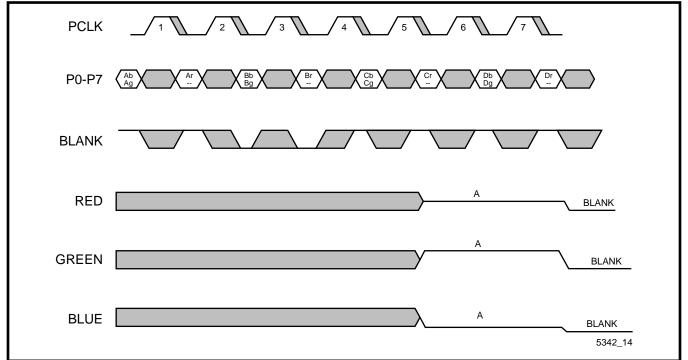

The GENDAC supports nine different video modes and is determined by bits 4-7 of the command register. The default mode is the 8-bit Pseudo Color mode. The other modes are the bypass 15-bit, 16-bit and 24 bit True Color modes in 8-bit and 16-bit interface, and the 16-bit Pseudo Color (2:1) mode with 2X Clock. The 24-bit True Color has sparse and packed modes.

### **Pseudo Color**

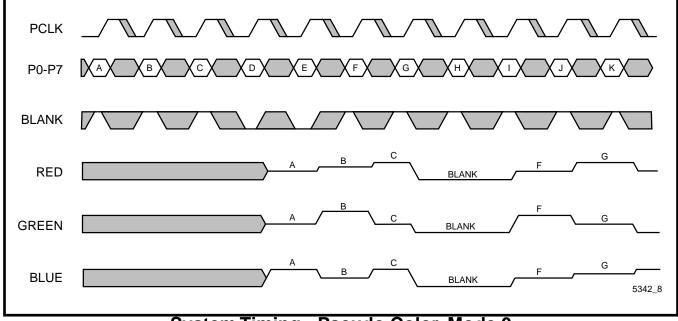

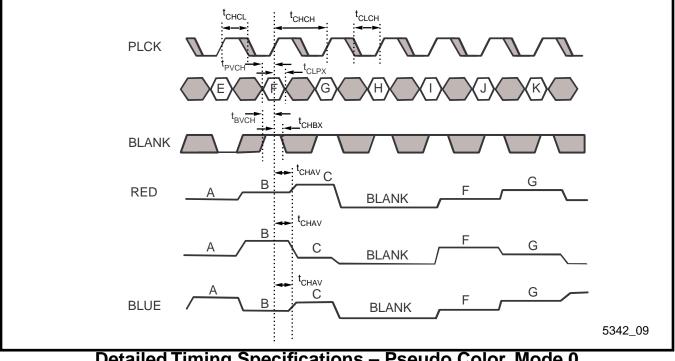

#### 8-bit Interface

In this mode, Pixel Address, P7-P0 and BLANK\* inputs are sampled on the rising edge of the clock (PCLK) and any change appears at the analog outputs after three succeeding rising edges of the PCLK. The DAC output depends on the data in the color palette RAM.

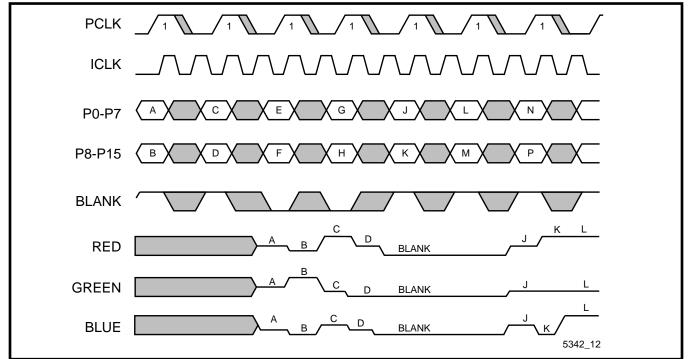

#### 16-bit Interface

In this mode, Pixel Address, P15-P0 and BLANK\* inputs are sampled on the rising edge of the clock (PCLK) and any change appears at the analog outputs after three succeeding rising edges of the 2 x ICLK. ICLK frequency is twice the PCLK input frequency. The DAC output depends on the data in the color palette RAM.

### **Bypass Mode**

The GENDAC supports seven different bypass modes: three for byte transfers and four for word transfers. In these modes, the address pins P0-P15 represent Color Data that is applied directly to the DAC. The internal look-up table RAM is ignored. During byte transfers, the P8-P15 inputs are"don't care." Data is always latched on the rising edge of PCLK. Byte or word framing is internally synchronized with the rising edge of BLANK\*.

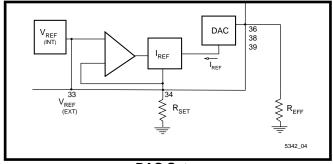

### **DAC Outputs**

The outputs of the DACs are designed to be capable of producing 0.7 V peak white amplitude with an I<sub>REF</sub> of 8.88 mA when driving a doubly-terminated 75  $\Omega$  load. This corresponds to an effective DAC output load (R<sub>EFFECTIVE</sub>) of 37.5  $\Omega$ . The formula for calculating I<sub>REF</sub> with various peak white voltage/output loading combinations is given below:

$$I_{REF} = \frac{V_{PEAKWHITE}}{2.1 \times R_{EFFECTIVE}}$$

Note that for all values of I<sub>REF</sub> and output loading:

$$V_{BLACKLEVEL} = 0$$

The reference current  $I_{REF}$  is determined by the reference voltage  $V_{REF}$  and the value of the resistor connected to  $R_{SET}$  pin.  $V_{REF}$  can be the internal band gap reference voltage or can be overridden by an external voltage. In both cases:

$$I_{REF} = V_{REF} / R_{SET}$$

**DAC Setup**

The BLANK\* input to the GENDAC acts on all three of the DAC outputs. When the BLANK\* input is low, the DACs are powered down.

The connection between the DAC outputs of the ICS5342 and the RGB inputs of the monitor should be regarded as a transmission line. Impedance changes along the transmission line will result in the reflection of part of the video signal back along the line. These reflections may result in a degradation of the picture displayed by the monitor.

RF techniques should be observed to ensure good fidelity. The PCB trace connecting the GENDAC to the off-board connector should be sized to form a transmission line of the correct impedance. Correctly matched RF connectors should be used for connection from the PCB to the monitor coaxial cable and from that cable to the monitor.

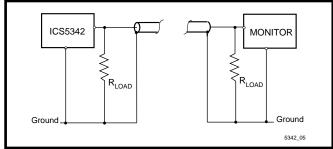

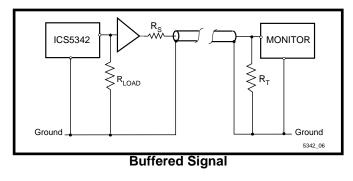

There are two recommended methods of DAC termination: double termination and buffered signal. Each is described below with its relative merits.

#### **Double Termination (Figure 1)**

For this termination scheme, a load resistor is placed at both the DAC output and the monitor input. The resistor values should be equal to the characteristic impedance of the line. Double termination of the DAC output allows both ends of the transmission line between the DAC outputs and the monitor inputs to be correctly matched. The result should be an ideal reflection-free system.

This arrangement is relatively tolerant of variations in transmission line impedance (e.g. a mismatched connector) since no reflections occur from either end of the line. A doubly terminated DAC output will rise faster than any singly terminated output because the rise time of the DAC outputs is dependent on the RC time constant of the load.

**Double Termination**

If the GENDAC drives large capacitive loads (for instance long cable runs), it may be necessary to buffer the DAC outputs. The buffer will have a relatively high input impedance. The connection between the DAC outputs and the buffer inputs should also be considered as a transmission line. The buffer output will have a relatively low impedance. It should be matched to the transmission line between it and the monitor with a series terminating resistor. The transmission line should be terminated at the monitor.

### SENSE Output

The GENDAC contains three comparators, one for each of the DAC output R, G and B lines. The reference voltage to the

comparators is proportional to the V<sub>REF</sub> (internal or external) and is typically 0.330 for V<sub>REF</sub>=1.235 Volts. The SENSE\* pin will be driven low when any analog video output is above 0.385 mV. SENSE\* output will be high when all analog outputs are below 275 mV. This signal is used to detect the type of (or lack of) monitor connected to the system.

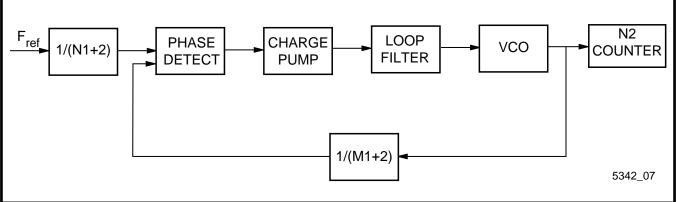

### PLL Clock

The ICS5342 has dual PLL frequency generators for generating the video clock (CLK0) and memory clock (CLK1) needed for graphics subsystems. Both of these clocks are generated from a single 14.318 MHz crystal or they can be driven from an external clock source. The chip includes the capacitors for the crystal and all of the components needed for the PLL loop filters, minimizing board component count.

There are eight possible video clock, CLK0, frequencies (f0f7) which can be selected by the external pins CS1-CS0. All clocks are software selectable by setting a bit in the PLL control register. Frequencies f0-f7 can be programmed for any frequency by writing appropriate parameter values to the PLL parameter registers. The default frequencies on power up are commonly used video frequencies (see table "Video Clock Default Frequency Registers"). At power up, the frequencies can be selected by pins CS2-CS0. There are two programmable memory clock frequencies (fA, fB). On power up this frequency defaults to the frequency given in the table: "MemoryClock Default Frequency Registers." The memory clock transition between frequencies is smooth and glitch free if the N2 PLL parameter is not changed from its previous setting.

| fn | VCLK   | M & N | Comments                 |  |  |  |  |  |  |  |  |

|----|--------|-------|--------------------------|--|--|--|--|--|--|--|--|

|    | (MHz)  | Code  |                          |  |  |  |  |  |  |  |  |

| f0 | 25.175 | 7D 50 | VGA0 (VGA Graphics)      |  |  |  |  |  |  |  |  |

| f1 | 28.322 | 55 49 | VGA1 (VGA Text)          |  |  |  |  |  |  |  |  |

| f2 | 31.500 | 2A 43 | VESA 640 x 480 @72 Hz    |  |  |  |  |  |  |  |  |

| f3 | 36.00  | 77 4A | VESA 800 x 600 @56 Hz    |  |  |  |  |  |  |  |  |

| f4 | 40.00  | 79 49 | VESA 800 x 600 @60 Hz    |  |  |  |  |  |  |  |  |

| f5 | 44.889 | 6F 47 | 1024 x 768 @43 Hz Inter- |  |  |  |  |  |  |  |  |

|    |        |       | laced                    |  |  |  |  |  |  |  |  |

| f6 | 65.00  | 74 2B | 1024 x 768 @ 60 Hz,      |  |  |  |  |  |  |  |  |

|    |        |       | 640 x 480 Hi-Color @ 72  |  |  |  |  |  |  |  |  |

|    |        |       | Hz                       |  |  |  |  |  |  |  |  |

| f7 | 75.00  | 71 29 | VESA 1024 x 768 @ 70     |  |  |  |  |  |  |  |  |

|    |        |       | Hz,                      |  |  |  |  |  |  |  |  |

|    |        |       | True Color 640 x 480     |  |  |  |  |  |  |  |  |

Video Clock (CLK0) Default Frequency Register \*

\* With 14.318 MHz input.

### TSD

| fn | MCLK<br>(MHz) | M & N<br>Code | Comments                            |

|----|---------------|---------------|-------------------------------------|

| fA | 45.00         | 4F 2B         | Memory and GUI sub-<br>system clock |

| fB | 55.00         | 79 2E         | Memory and GUI sub-<br>system clock |

#### Memory Clock (CLK1) Default Frequency Register

### **Microprocessor Interface**

Below are listed the six microprocessor interface registers within the ICS5342, and the register addresses through which they can be accessed.

| Microprocessor | Interface | Registers |

|----------------|-----------|-----------|

|----------------|-----------|-----------|

| RS2  | RS1 | RS0 | Register Name                |  |  |  |  |  |  |  |  |  |

|------|-----|-----|------------------------------|--|--|--|--|--|--|--|--|--|

| 0    | 0   | 0   | Pixel Address (write mode)   |  |  |  |  |  |  |  |  |  |

| 0    | 1   | 1   | Pixel Address (read mode)    |  |  |  |  |  |  |  |  |  |

| 0    | 0   | 1   | Color Value                  |  |  |  |  |  |  |  |  |  |

| 0    | 1   | 0   | Pixel Mask                   |  |  |  |  |  |  |  |  |  |

| 1    | 0   | 0   | PLL Address (write mode)     |  |  |  |  |  |  |  |  |  |

| 1    | 0   | 1   | PLL Parameter                |  |  |  |  |  |  |  |  |  |

| 1    | 1   | 0   | Command                      |  |  |  |  |  |  |  |  |  |

| 1    | 1   | 1   | PLL Address (read mode)      |  |  |  |  |  |  |  |  |  |

| 0/HF | 1   | 0   | Command Register accessed by |  |  |  |  |  |  |  |  |  |

|      |     |     | (hidden) flag after special  |  |  |  |  |  |  |  |  |  |

|      |     |     | sequence of events.          |  |  |  |  |  |  |  |  |  |

#### Asynchronous Access to Microprocessor Interface

Accesses to all registers may occur without reference to the high speed timing of the pixel bit stream being processed by the GENDAC. Data transfers between the color palette RAM and the Color Value register, as well as modifications to the Pixel Mask register, are synchronized to the Pixel Clock by internal logic. This is done in the period between microprocessor interface accesses. Thus, various minimum periods are specified between microprocessor interface accesses to allow the appropriate transfers or modifications to take place. Access to PLL address, PLL parameter and to the command register are asynchronous to the pixel clock.

The contents of the palette RAM can be accessed via the Color Value register and the Pixel Address registers.

#### Writing to the color palette RAM

To set a new color definition, a value specifying a location in the color palette RAM is first written to the Write mode Pixel Address register. The values for the red, green and blue intensities are then written in succession to the Color Value register. After the blue data is written to the Color Value register, the new color definition is transferred to the RAM, and the Pixel Address register is automatically incremented. Writing new color definitions to a set of consecutive locations in the RAM is made easy by this auto-incrementing feature. First, the start address of the set of locations is written to the write mode Pixel Address register, followed by the color definition of that location. Since the address is incremented after each color definition is written, the color definition for the next location can be written immediately. Thus, the color definitions for consecutive locations can be written sequentially to the Color Value register without re-writing to the Pixel Address register each time.

#### **Reading from the RAM**

To read a color definition, a value specifying the location in the palette RAM to be read is written to the read mode Pixel Address register. After this value has been written, the contents of the location specified are copied to the Color Value register, and the Pixel Address register automatically increments.

The red, green and blue intensity values can be read by a sequence of three reads from the Color Value register. After the blue value has been read, the location in the RAM currently specified by the Pixel Address register is copied to the Color Value register and the Pixel Address again automatically increments. A set of color values in consecutive locations can be read simply by writing the start address of the set to the read mode Pixel Address register and then sequentially reading the color values for each location in the set. Whenever the Pixel Address register is updated, any unfinished color definition read or write is aborted and a new one may begin.

#### The Pixel Mask Register

The pixel address used to access the RAM through the pixel interface is the result of the bitwise AND-ing of the incoming pixel address and of the contents of the Pixel Mask register. This pixel masking process can be used to alter the displayed colors without altering the video memory or the RAM contents. By partitioning the color definitions by one or more bits in the pixel address, such effects as rapid animation, overlays, and flashing objects can be produced.

The Pixel Mask register is independent of the Pixel Address and Color Value registers.

#### **The Command Register**

The Command register is used to select the various GENDAC color modes and to set the power down mode. On power up this register defaults to an 8-bit Pseudo Color mode. This register can be accessed by control pins RS2-RS0, or by a special sequence of events for graphics subsystems that do not have the control signal RS2. For graphic systems that do not have RS2, this pin is tied low and an internal flag (HF: Hidden Flag) is set when the pixel mask register is read four times

consecutively. Once the flag is set, the following Read or Write to the pixel mask register is directed to the command register. The flag is reset for read or write to any register other than the Pixel Mask register. The sequence has to be repeated for any subsequent access to the command register.

#### The PLL Parameter Register

The CLK0 and CLK1 of the ICS5342 can be programmed for different frequencies by writing different values to the PLL parameter register bank. There are eight registers in the parameter register; seven are two bytes long and one (0E) is one byte long.

#### Writing to the PLL parameter register

To write the PLL parameter data, the corresponding address location is first written to the PLL address register. For software compatibility with other chips, two address registers are defined: the write mode PLL address register and the read mode PLL address register. These are actually a single Read/ Write register in the ICS5342. The next PLL parameter write will be directed to the first byte of the address location specified by the PLL address register. The next write to the parameter register will automatically be to the second byte of this register. At the end of the second write the address is automatically incremented. For the one byte "0E" register the address location is incremented after the first byte write. If this frequency is selected while programming, the output frequency will change at the end of the second write.

#### Reading the PLL parameter register

To read one of the registers of the PLL parameter register the address value corresponding to the location is first written to the PLL address register. The next PLL parameter read will be directed to the first byte of the address location pointed by this index register. A next read of the parameter register will automatically be the second byte of this register. At the end of the second read, the address location is automatically incremented. The address register (0E) is incremented after the first byte read.

### **Functional Description**

This section describes the register address and bit definition for the RAMDAC and the Frequency Synthesizer sections.

### **Color Palette**

#### **Command Register**

(RS0-RS2 = 011)

(RS0-RS1 = 01 with hidden flag)

By setting bits 4 and 7-5 in the command register the ICS5342 can be programmed for different color modes and the DACs can be turned off for low power operation.

#### **Command Registers**

| 7 | 6 | 5 | 4 | 3      | 2      | 1         | 0      |

|---|---|---|---|--------|--------|-----------|--------|

| 2 | 1 | 0 | 3 | Reserv | ed = 0 | Test mode | Snooze |

- Bit 7-4 Color Mode Select These three bits select the Color Mode of RAMDAC operation as shown in the following table "Color Mode Select" (default is 0 at power up).

- Bit 3-2 (Reserved) Set to '0' for future compatibility.

- Bit 1 Test Mode When bit 1 is set checksum accumulation is enabled. If bit 0 is also set the oscillator and synthesizers are turned off for minimum noise.

- Bit 0 Power Down Mode of RAMDAC When this bit is set to 0 (default is 0), the device operates normally. If this bit is set to 1, the power and clock to the Color Palette RAM and DACs are turned off. The data in the Color Palette RAM are still preserved. The CPU can access without loss of data by internal automatic clock start/stop control. The DAC outputs become the same as BLANK\* (sync) level output during power down mode. This bit does not affect the PLL clock synthesizer function unless test mode is enabled.

### **Color Mode Select**

#### 8-BIT INTERFACE

| Mode<br>Number | CM3<br>(CR4) | CM2<br>(CR7) | CM1<br>(CR6) | CM0<br>(CR5) | Color Mode                                 | Clock Cycles/<br>Pixel Bits |

|----------------|--------------|--------------|--------------|--------------|--------------------------------------------|-----------------------------|

| 0              | 0            | 0            | 0            | 0            | 8-bit Pseudo Color With Palette (default)  | 1                           |

| 1              | 0            | 0            | 0            | 1            | 15-bit Direct Color With Bypass (Hi-Color) | 2                           |

| 3              | 0            | 0            | 1            | 0            | 24-Bit True Color With Bypass (True Color) | 3                           |

| 2              | 0            | 0            | 1            | 1            | 16-bit Direct Color With Bypass (XGA)      | 2                           |

| 1              | 0            | 1            | 0            | 0            | 15-bit Direct Color With Bypass (hi-color) | 2                           |

| 1              | 0            | 1            | 0            | 1            | 15-bit Direct Color With Bypass (Hi-Color) | 2                           |

| 2              | 0            | 1            | 1            | 0            | 15-bit Direct Color With Bypass (Hi-Color) | 2                           |

| 3              | 0            | 1            | 1            | 1            | 24-bit True Color With Bypass (True Color) | 3                           |

#### **16-BIT INTERFACE**

| Mode<br>Number | CM3<br>(CR4) | CM2<br>(CR7) | CM1<br>(CR6) | CM0<br>(CR5) | Color Mode                                   | Clock Cycles/<br>Pixel Bits |

|----------------|--------------|--------------|--------------|--------------|----------------------------------------------|-----------------------------|

| 4              | 1            | 0            | 0            | 0            | Multiplexed 16-bit Pseudo Color With Palette | 1/2                         |

| 5              | 1            | 0            | 0            | 1            | 15-bit Direct Color With Bypass (Hi-Color)   | 1                           |

| 6              | 1            | 0            | 1            | 0            | 16-bit Direct Color With Bypass (XGA         | 1                           |

| 7              | 1            | 0            | 1            | 1            | 24-bit True Color With Bypass (True Color)   | 2                           |

| 8              | 1            | 1            | 0            | 0            | 24-bit Packed True Color With Bypass         | 3/2                         |

|                |              |              |              |              | (true-color)                                 |                             |

|                | 1            | 1            | 0            | 1            | Reserved                                     |                             |

|                | 1            | 1            | 1            | 0            | Reserved                                     |                             |

|                | 1            | 1            | 1            | 1            | Reserved                                     |                             |

### **Color Modes**

The nine selectable color modes are described here. Four are eight-bit and five are 16-bit wide pixel input. Color Modes 0-3 are 8-bit interfaces with bits P0-P7; P8-P15 are "don't care" bits.

**Mode 0**: 8-bit Pseudo Color (one clock per pixel). This mode is the 8-bit per pixel Pseudo Color mode. In this mode, inputs P0-P7 are the pixel address for the color palette RAM and are latched on the rising edge of every PCLK. This is the default mode on power up and it is selected by setting bits CR7-CR4 to 0000.

#### 8-bit Pseudo Color - Mode 0

| PIXEL BYTE |    |    |    |    |    |    |   |  |  |  |  |  |  |

|------------|----|----|----|----|----|----|---|--|--|--|--|--|--|

| Р          | Р  | Р  | Р  | Р  | Р  | Р  | Р |  |  |  |  |  |  |

| 7          |    | -  |    | -  | 2  |    | 0 |  |  |  |  |  |  |

| 7          | 6  | 5  | 4  | 3  | 2  | 1  | 0 |  |  |  |  |  |  |

| L          | U' | ΓA | ٨D | DI | RE | SS |   |  |  |  |  |  |  |

**Mode 1:** (15-bit per color bypass Hi-Color mode). This mode is the 15-bit per pixel bypass mode. In this mode, inputs P0-P7 are the color DATA and are input directly to the DAC, bypassing the color palette. The two bytes of data are latched in two successive PCLK rising edges. ICS5342 supports only the two clock mode and does not support the mode where the data are latched on the rising and the falling edges. For compatibility, the 15/16 one clock modes are selected as two clock modes in this chip. The low-byte, high byte synchronization is internally done by the rising edge of BLANK\*. Each color is 5-bit wide and is packed into two bytes as shown below. This mode can be selected by setting bits CR7-CR4 to 0010, 1000 or 1010.

#### 15-Bit Color - Mode 1

| SI | EC | O  | ND | ) B | Y | ΓЕ | FIRST BYTE |     |   |   |   |    |    |   |   |

|----|----|----|----|-----|---|----|------------|-----|---|---|---|----|----|---|---|

| Р  | Р  | Р  | Р  | Р   | Р | Р  | Р          | Р   | Р | Р | Р | Р  | Р  | Р | Р |

| 7  | 6  | 5  | 4  | 3   | 2 | 1  | 0          | 7   | 6 | 5 | 4 | 3  | 2  | 1 | 0 |

| Х  | 7  | 6  | 5  | 4   | 3 | 7  | 6          | 5   | 4 | 3 | 7 | 6  | 5  | 4 | 3 |

| Χ  | R  | ED | )  |     |   | G  | RF         | EEI | Ν |   | B | LU | JE |   |   |

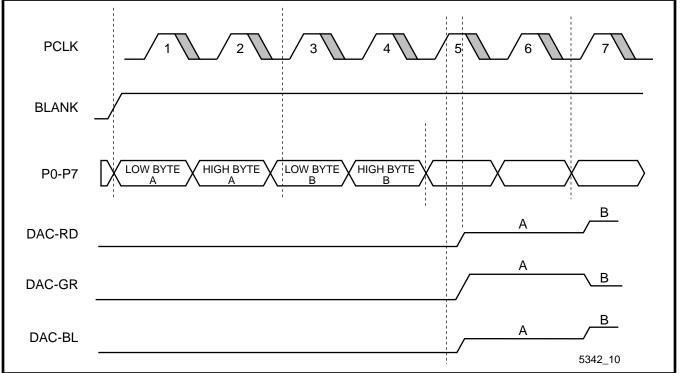

3LSB = set to zero

**Mode 2:** (16-bit per pixel bypass XGA mode). This mode is the 16-bit per pixel bypass mode and the P0-P7 inputs to go to the DAC directly, bypassing the color palette. The 2 bytes data is latched on two successive rising edges and the lowbyte, high-byte synchronization is internally done by the rising edge of BLANK\*. In this mode, blue and red colors are 5 bits wide and green is 6 bits wide. The 2 bytes of data are packed as shown below. This mode can be selected by setting bits CR7-CR4 to 0110 or 1100.

#### 16-Bit Color - Mode 2

|   |    |    | · · | _ | _ |   | FIRST BYTE |   |   |   |    |    |   |   |   |

|---|----|----|-----|---|---|---|------------|---|---|---|----|----|---|---|---|

| Р | Р  | Р  | Р   | Р | Р | Р | Р          | Р | Р | Р | Р  | Р  | Р | Р | Р |

| 7 |    |    |     |   |   |   |            |   |   |   |    |    |   |   |   |

| 7 | 6  | 5  | 4   | 3 | 7 | 6 | 5          | 4 | 3 | 2 | 7  | 6  | 5 | 4 | 3 |

|   | RE | ED |     |   |   | G | EEI        | N |   |   | BI | LU | E |   |   |

2LSB = set to zero (green) 3LSB = set to zero (blue, red)

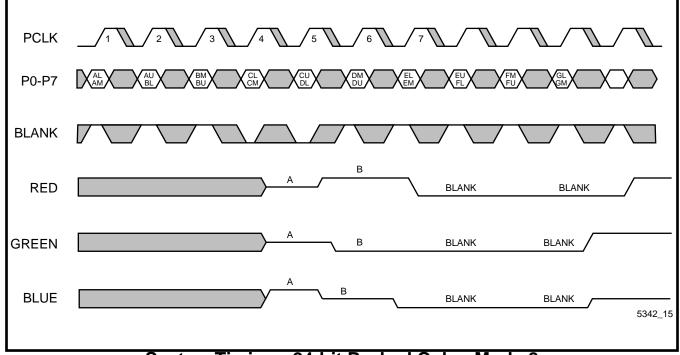

**Mode 3:** (24-bit per pixel True Color Mode). This mode is the 24-bit per pixel bypass mode. The three bytes of data are latched on three successive PCLK edges and the first byte is synchronized by the rising edge of BLANK\*. In this mode, each of the colors are 8-bit wide and the DAC is an 8-bit wide DAC. The first byte is blue followed by green and red. This mode can be selected by setting bits CR7-CR4 to 0100 or 1110. The DAC outputs changes every three cycles and the pipeline delay from the first byte to output is five cycles.

#### 24-bit Color - Mode 3

| T   |   |   |   | - |   |   |   | SECOND BYTE |                 |    |    |    |   |   |   |   |   |   |   |    |   |   |   |

|-----|---|---|---|---|---|---|---|-------------|-----------------|----|----|----|---|---|---|---|---|---|---|----|---|---|---|

| P   | Р | Р | Р | Р | Р | Р | Р | Р           | PPPPPPP         |    |    |    |   |   |   |   | Р | Р | Р | Р  | Р | Р | Р |

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7           | 7 6 5 4 3 2 1 0 |    |    |    |   |   |   | 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 |

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7           | 6               | 5  | 4  | 3  | 2 | 1 | 0 | 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 |

| RED |   |   |   |   |   |   |   |             |                 | GI | RE | EN | 1 |   |   |   |   | В | L | JE | r |   |   |

### 16 bit Color Modes

Modes 4 - 8 use the 16-bit pixel interface.

**Mode 4:** (8-bit Pseudo Color two pixels per clock) In this mode, inputs P0-P15 are latched on the rising edge of every PCLK. P0-7 and P8-P15 are used for successive addresses for the palette RAM using an internal clock (ICLK) that runs at twice the PCLK frequency. The DAC outputs change twice for every PCLK and the pipeline delay from the first word to output is one and one half cycles. This mode can be selected by setting bits CR7-CR4 to 0001.

Multiplexed 8-bit Pseudo Color Word - Mode 4

|    | PIXEL WORD |    |    |   |   |   |   |    |      |    |    |    |   |   |   |

|----|------------|----|----|---|---|---|---|----|------|----|----|----|---|---|---|

| Р  | Р          | Р  | Р  | Р | Р | Р | Р | Р  | Р    | Р  | Р  | Р  | Р | Р | Р |

| 1  | 1          | 1  | 1  | 1 | 1 | 9 | 8 | 7  | 6    | 5  | 4  | 3  | 2 | 1 | 0 |

| 5  | 4          | 3  | 2  | 1 | 0 |   |   |    |      |    |    |    |   |   |   |

| 7  | 6          | 5  | 4  | 3 | 2 | 1 | 0 | 7  | 6    | 5  | 4  | 3  | 2 | 1 | 0 |

| 2r | nd         | PĽ | XE | L |   |   |   | 15 | st F | ЧX | E  | L  |   |   |   |

| A  | DI         | DR | ES | S |   |   |   | A  | DI   | DR | ES | SS |   |   |   |

**Mode 5:** (16-bit pixel interface, 15-bit per color bypass Hi-Color Mode) In this mode inputs P0-P15 are the color data and are input directly to the DAC, bypassing the color palette. The data is latched by the rising edge of PCLK and is pipelined to the DAC. The pipeline delay from input to DAC output is three PCLK cycles. Each color is 5-bit wide as shown below. This mode is selected by setting bits CR7-CR4 to 0011.

#### 15-Bit Color Word - Mode 5

|   |       |   | F | ЧX | ΚE | L١ | NC | )R | D |   |   |   |    |   |   |

|---|-------|---|---|----|----|----|----|----|---|---|---|---|----|---|---|

| Р | Р     | Р | Р | Р  | Р  | Р  | Р  | Р  | Р | Р | Р | Р | Р  | Р | Р |

| 1 | 1     | 1 | 1 | 1  | 1  | 9  | 8  | 7  | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

| 5 | 4     | 3 | 2 | 1  | 0  |    |    |    |   |   |   |   |    |   |   |

| X | 7     | 6 | 5 | 5  | 4  | 7  | 6  | 5  | 4 | 3 | 7 | 6 | 5  | 4 | 3 |

| X | X RED |   |   |    |    | С  | R  | EE | N |   | В | L | JE | , |   |

3LSB = set to zero

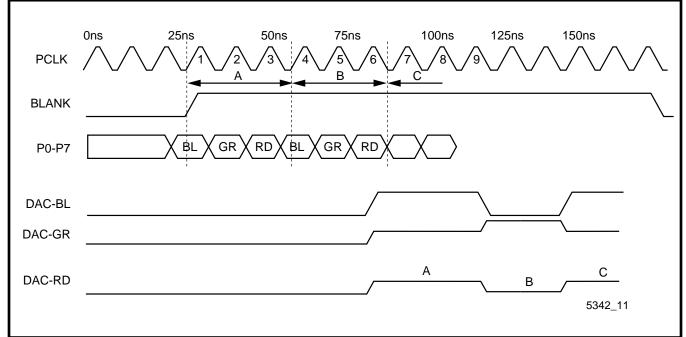

**Mode 6:** (16-bit pixel interface, 16-bit per color bypass XGA mode) In this mode input P0-P15 are the color data and are input directly to the DAC bypassing the color palette. The data is latched by the rising edge of PCLK and is pipelined to the DAC. The pipeline delay, from input to DAC output, is three PCLK cycles. In this mode Blue and Red colors are 5 bits wide, and Green is 6 bits wide. This mode is selected by setting bits CR7-CR4 to 0101.

#### 16-Bit Color Word - Mode 6

|   |    |    | D | <b>TT7</b> |    |            |    | D | _ |   |   |    |    |   |   |

|---|----|----|---|------------|----|------------|----|---|---|---|---|----|----|---|---|

|   |    |    | Ρ | IX         | EL | _ V        | ٧U | R | J |   |   |    |    |   |   |

| P | Р  | Р  | Р | Р          | Р  | Р          | Р  | Р | Р | Р | Р | Р  | Р  | Р | Р |

| 1 | 1  | 1  | 1 | 1          | 1  | 9          | 8  | 7 | 6 | 5 | 4 | 3  | 2  | 1 | 0 |

| 5 |    |    |   |            |    |            |    |   |   |   |   |    |    |   |   |

| 7 | 6  | 5  | 4 | 3          | 7  | 6          | 5  | 4 | 3 | 2 | 7 | 6  | 5  | 4 | 3 |

|   | RF | ED |   |            | C  | <b>B</b> R | EE | N |   |   | B | LU | JE | , |   |

2LSB = set to zero (GREEN) 3LSB = set to zero (BLUE, RED)

**Mode 7:** (16-bit pixel interface, 24-bit per color bypass TRUE color mode) In this mode inputs P0-P15 are the color data and are input directly to the DAC bypassing the color palette. Two words are latched on two successive rising edge of PCLK to form the 24-bit DAC input. The first word and the lower byte of the second word form the 24-bit pixel input to the DAC. The higher byte of the second word is ignored. The low and high word synchronization is internally done by the rising edge of BLANK\*. The pipeline delay from latching of the first word to DAC output is 4 cycles and each pixel is two pixel clocks wide. In this mode, each of the colors are 8-bits wide and the DAC is 8-bit wide DAC. The first byte is Blue followed by Green and Red. This mode is selected by setting bits CR7-CR4 to 0111.

#### 24-Bit Direct Color Word - Mode 7

|   |                 |    | _  |     |    |    |    |    | _  |    |    |   |   |   |   |

|---|-----------------|----|----|-----|----|----|----|----|----|----|----|---|---|---|---|

|   |                 |    | ł  | FIF | S. | ٢N | NC | )R | D  |    |    |   |   |   |   |

| Р | Р               | Р  | Р  | Р   | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р | Р | Р | Р |

| 1 | 1               | 1  | 1  | 1   | 1  | 9  | 8  | 7  | 6  | 5  | 4  | 3 | 2 | 1 | 0 |