**PRELIMINARY**

# NMC9816A 16,384-Bit (2k x 8) E<sup>2</sup>PROM

## General Description

The NMC9816A is a fast 5V-only E2PROM which offers many desired features, making it ideally suited for efficiency and ease in system design. The added features on the NMC9816A include: 5V-only operation provided by an onchip VPP generator during erase-write; address and data latches to reduce part count and to free the microprocessor while the chip is busy doing erase-write; and automatic erase before byte-write. It can meet applications requiring up to 104 write cycles per byte. The NMC9816A is a product of National's advanced E2PROM stepper technology and uses the powerful XMOSTM process for reliable, non-volatile data storage.

The NMC9816A sharply minimizes the interfacing hardware logic and firmware required to perform data writes. The device has complete self-timing which leaves the processor free to perform other tasks. With an automatic erase before write, the user benefits by saving an erase command contributing to efficient usage of system processing time. Onchip address and data latching further enhances system performance.

The NMC9816A also features DATA Polling, which enables the E2PROM to signal the processor that a write operation is complete without requiring the use of any external hard-

Improved data protection during V<sub>CC</sub> power up/down transitions is provided by an on-chip  $V_{\mbox{\footnotesize{CC}}}$  sensing circuit which disables the initiation of all 5V-only programmable modes when V<sub>CC</sub> is less than 4 volts.

The NMC9816A's very fast read access times make it compatible with high performance microprocessor applications. It uses the proven two line control architecture which eliminates bus contention in a system environment.

Addresses

Chip Enable

Output Enable

A0-A10

CE

ŌĒ

An optional high voltage chip erase feature is provided for quick erasure of the memory data pattern in a single 9 msec Chip Erase Cycle.

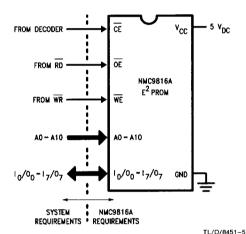

The density, and level of integrated control, make the NMC9816A suitable for users requiring minimum hardware overhead, high systems performance, minimal board space and design ease. Designing with and using the NMC9816A is extremely cost effective as the required high voltage and interfacing hardware required for other E2PROM devices has been eliminated by 5V-only operation and on-chip latches. See Figures 1, 2, and 3 for the NMC9816A block diagram, pinout, and simple interface requirements.

### **Features**

- Single 5V supply

- Self-timed byte-write with auto erase

- On-chip address and data latches

- On-chip power up/down protection

- Two line output control

- TRI-STATE® outputs

- Data polling verification

- High voltage chip erase

- Fast byte-writing

Write cycle (2 ms typical) E/W cycle (4 ms typical)

■ Very fast access time

NMC9816A-20-200 ns

NMC9816A-25-250 ns

NMC9816A-35-350 ns

- Direct microprocessor interface capability

- No support components needed

- Reliable E2PRØM XMOS stepper technology

### **Block and Connection Diagrams** DATA INPUTS/GUTPUTS VPP GENERATOR la / On - 17 / O7 CHIP ENABLE / DUTPUT INPUT/DUTPUT AUTOMATIC WRITE TIMING AUTOMATIC ERASE LOGIC A0-A10 Y GATING DECODER INPUTS LATCHES 16 384-BIT CELL MATRIX DECODER TL/D/8451-1 FIGURE 1 Pin Names

NMC9816A-25 or NMC9816A-35 See NS Package Number J24A or N24A

1-39

**Data Outputs**

Data Inputs

Write Enable

$O_0 - O_7$

lo−l7 WE

## Absolute Maximum Ratings

Temperature Under Bias

NMC9816A

-10°C to +80°C NMC9816AE -50°C to +95°C NMC9816AM -65°C to +135°C

Storage Temperature -65°C to +150°C

All Input or Output Voltages with +6V to -0.3V

Respect to Ground

Lead Temp. (Soldering, 10 seconds) 300°C

## Operating Conditions

Temperature Range

NMC9816A

NMC9816AE

-40°C to +85°C NMC9816AM -55°C to +125°C

V<sub>CC</sub> Power Supply (Notes 2 and 3)

NMC9816A 5V ±5% NMC9816AE 5V ± 10%

NMC9816AM 5V ± 10% Note: Stresses above those listed under "Absolute Maxi-

mum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# DC Electrical Characteristics $T_A$ for NMC9816A = 0°C to +70°C, $V_{CC}$ = 5V $\pm$ 5% (Note 7)

0°C to +70°C

| Symbol          | Parameter                                                            | Conditions                               | Min               | Typ<br>(Note 1) | Max                                                               | Units |

|-----------------|----------------------------------------------------------------------|------------------------------------------|-------------------|-----------------|-------------------------------------------------------------------|-------|

| READ OP         | ERATION                                                              |                                          |                   |                 | <del></del>                                                       |       |

| lu              | Input Leakage Current NMC9816A<br>NMC9816AE<br>NMC9816AM             | GND to V <sub>CC</sub>                   |                   |                 | 10<br>10<br>10                                                    | μΑ    |

| lo              | Output Leakage Current NMC9816A<br>NMC9816AE<br>NMC9816AM            | GND to V <sub>CC</sub>                   |                   |                 | 10<br>10<br>10                                                    | μΑ    |

| ICCA            | V <sub>CC</sub> Current (Active) NMC9816A<br>NMC9816AE<br>NMC9816AM  | $\overline{CE} = \overline{OE} = V_{IL}$ |                   | 40<br>40<br>40  | 80<br>100<br>100                                                  | mA    |

| Iccs            | V <sub>CC</sub> Current (Standby) NMC9816A<br>NMC9816AE<br>NMC9816AM | CE = V <sub>IH</sub>                     |                   | 12<br>12<br>12  | 25<br>30<br>30                                                    | mA    |

| $V_{IL}$        | Input Low Voltage                                                    |                                          | -0.1              |                 | 0.8                                                               | V     |

| V <sub>IH</sub> | Input High Voltage NMC9816A<br>NMC9816AE<br>NMC9816AM                |                                          | 2.0<br>2.2<br>2.2 |                 | V <sub>CC</sub> + 1<br>V <sub>CC</sub> + 1<br>V <sub>CC</sub> + 1 | V     |

| V <sub>OL</sub> | Output Low Voltage                                                   | I <sub>OL</sub> = 2.1 mA                 |                   |                 | 0.45                                                              | V     |

| V <sub>OH</sub> | Output High Voltage                                                  | I <sub>OH</sub> = – 400 μA               | 2.4               |                 |                                                                   | ٧     |

| WRITE OP        | ERATION                                                              |                                          |                   |                 |                                                                   |       |

| lccw            | V <sub>CC</sub> Current (Write) NMC9816A<br>NMC9816AE<br>NMC9816AM   |                                          |                   | 40<br>40<br>40  | 80<br>100<br>100                                                  | mA    |

| $V_{LKO}$       | V <sub>CC</sub> Level for Write Lockout                              |                                          | 4.0               |                 |                                                                   | ٧     |

| HIGH VOL        | TAGE CHIP ERASE                                                      | 7                                        |                   |                 | /*· · · · ·                                                       | ·     |

| v <sub>ER</sub> | OE and WE Voltage in Chip Erase Mode                                 |                                          | 12                |                 | 22                                                                |       |

# Capacitance $T_A = 25^{\circ}C$ , f = 1 MHz (Note 1)

| Symbol           | Parameter          | Conditions           | Min | Typ<br>(Note 1) | Max | Units |

|------------------|--------------------|----------------------|-----|-----------------|-----|-------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> =0V  |     | 5               | 10  | pF    |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> =0V |     |                 | 10  | ρF    |

### **AC Test Conditions**

Output Load Input Pulse Levels 1 TTL gate and  $C_L = 100 \ pF$

0.45V to 2.4V

Timing Measurement Reference Level

Input

Output

1V and 2V 0.8V and 2V

## Read Mode AC Electrical Characteristics TA = 0°C to 70°C, VCC = 5V ±5% (Notes 2, 3 & 7)

|                 |                                                                        |                            | NMC9816A-20 |                 |     | NMC9816A-25 |                 |     | NMC9816A-35 |                 |     |       |

|-----------------|------------------------------------------------------------------------|----------------------------|-------------|-----------------|-----|-------------|-----------------|-----|-------------|-----------------|-----|-------|

| Symbol          | Parameter                                                              | Conditions                 | Min         | Typ<br>(Note 1) | Max | Min         | Typ<br>(Note 1) | Max | Min         | Typ<br>(Note 1) | Max | Units |

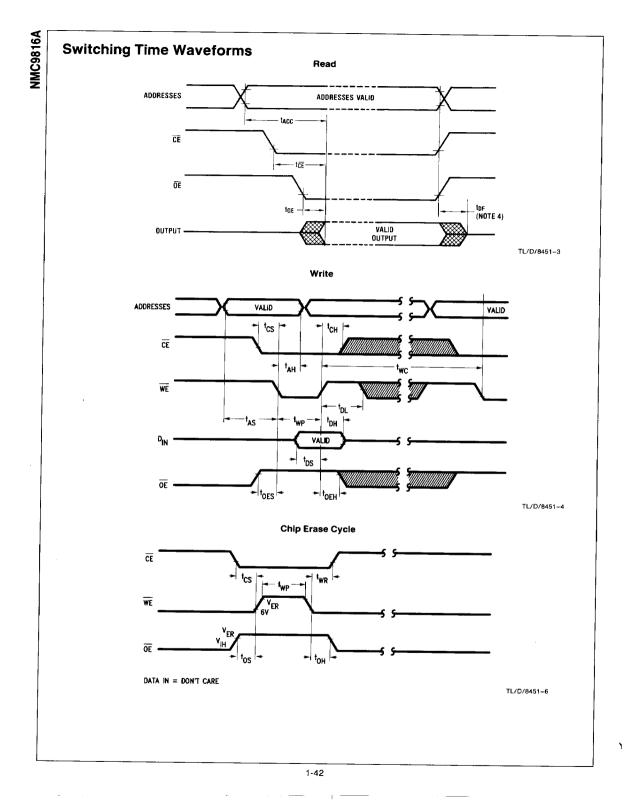

| TACC            | Address to Output<br>Delay                                             | CE = OE = V <sub>IL</sub>  |             | 150             | 200 |             | 200             | 250 | )           | 300             | 350 | ns    |

| tCE             | CE to Output Delay                                                     | OE = V <sub>IL</sub>       |             | 150             | 200 |             | 200             | 250 |             | 300             | 350 | ns    |

| t <sub>OE</sub> | Output Enable to<br>Output Delay                                       | CE=V <sub>IL</sub>         | 10          |                 | 75  | 10          |                 | 100 | 10          |                 | 120 | ns    |

| t <sub>DF</sub> | Output Disable to Output Float                                         | CE or OE = V <sub>IL</sub> | 0           |                 | 80  | 0           |                 | 100 | 0           |                 | 100 | ns    |

| <sup>t</sup> OH | Output Hold from<br>Addresses, CE or OE<br>Whichever Occurred<br>First | CE, OE = V <sub>IL</sub>   | 0           |                 |     | 0           |                 |     | 0           |                 |     | ns    |

## Write Mode AC Electrical Characteristics TA=0°C to 70°C, VCC=5V ±5% (Notes 2, 3 & 7)

| Symbol                   | Parameter                    | Conditions         | Min | Typ<br>(Note 1) | Max | Units |

|--------------------------|------------------------------|--------------------|-----|-----------------|-----|-------|

| t <sub>AS</sub>          | Address to Write Set-Up Time |                    | 20  |                 |     | ns    |

| tcs                      | CE to Write Set-Up Time      |                    | 20  |                 |     | ns    |

| t <sub>WP</sub> (Note 6) | Write Pulse Width            |                    | 150 |                 |     | ns    |

| t <sub>AH</sub>          | Address Hold Time            |                    | 50  |                 |     | ns    |

| t <sub>DS</sub>          | Data Set-Up Time             | ŌE=V <sub>IH</sub> | 50  |                 |     | ns    |

| t <sub>DH</sub>          | Data Hold Time               | ŌE=V <sub>IH</sub> | 20  |                 |     | ns    |

| t <sub>CH</sub>          | CE Hold Time                 |                    | 20  |                 |     | ns    |

| t <sub>DL</sub>          | Data Latch Time              |                    | 50  |                 |     | ns    |

| twc .                    | Byte-Write Cycle Time        |                    |     | 4               | 10  | ms    |

| <sup>t</sup> OES         | Output Enable Setup Time     |                    | 10  |                 |     | ns    |

| <sup>t</sup> OEH         | Output Enable Hold Time      |                    | 10  |                 |     | ns    |

## High Voltage Chip Erase AC Electrical Characteristics (Note 5)

$T_A = 0$ °C to +70°C,  $V_{CC} = 5V \pm 5\%$  (Notes 2, 3 & 7)

| Symbol          | Parameter                 | Conditions           | Min | Typ<br>(Note 1) | Max | Units |

|-----------------|---------------------------|----------------------|-----|-----------------|-----|-------|

| t <sub>CS</sub> | CE Set-Up Time            | WE = 6V              | 10  |                 |     | ns    |

| tos             | Output Enable Set-Up Time | WE = 6V              | 10  |                 |     | กร    |

| tон             | Output Enable Hold Time   | WE = 6V              | 1   |                 |     | μs    |

| twR             | Write Recovery Time       | ₩E = 6V              | 1   |                 |     | μs    |

| t <sub>WP</sub> | Chip Erase Pulse Width    | WE = V <sub>ER</sub> | 9   |                 | 15  | ms    |

Note 1: This parameter only sampled and not 100% tested.

Note 2: To prevent spurious device erase or write,  $\overline{WE}$  or  $\overline{CE} = V_{IH}$  must be applied simultaneously or before  $V_{CC} = 4V$ .  $\overline{WE}$  or  $\overline{CE} = V_{IH}$  must be removed simultaneously or after  $V_{CC}$  falls before 4V.

Note 3: To prevent damage to the device it must not be inserted into or removed from a board with power applied.

Note 4:  $t_{DF}$  is specified from  $\overline{OE}$  or  $\overline{CE}$ , whichever occurs first.

Note 5: Low voltage VCC sense circuit does not inhibit the high voltage Chip Erase feature.

Note 6: WE is noise protected. Less than a 20 ns write pulse will not activate a write cycle.

Note 7:  $T_A$  for NMC9816AE =  $-40^{\circ}$ C to  $+85^{\circ}$ C,  $V_{CC} = 5V \pm 10\%$ ,  $T_A$  for NMC9816AM =  $-55^{\circ}$ C to  $+125^{\circ}$ C,  $V_{CC} = 5V \pm 10\%$ .

## **Device Operation**

The NMC9816A has 6 modes of user operation which are detailed in Table I. All modes are designed to enhance the NMC9816A's functionality to the user and provide total microprocessor compatibility.

| 1 | ΓAB | LEI | . Vcc | = ; | 5V |

|---|-----|-----|-------|-----|----|

|   |     | _   |       |     |    |

| Pin<br>Mode  | CE              | ŌĒ              | WE       | I <sub>0</sub> /O <sub>0</sub> -I <sub>7</sub> /O <sub>7</sub> |  |  |  |  |

|--------------|-----------------|-----------------|----------|----------------------------------------------------------------|--|--|--|--|

| Read         | $V_{IL}$        | ٧ <sub>L</sub>  | $V_{IH}$ | D <sub>OUT</sub>                                               |  |  |  |  |

| Standby      | ٧               | X               | X        | Hi-Z                                                           |  |  |  |  |

| Write        | VIL             | $V_{IH}$        | Т        | D <sub>IN</sub>                                                |  |  |  |  |

| D            | VIH             | Х               | Х        | High-Z                                                         |  |  |  |  |

| Busy         | Х               | VIH             | Х        | High-Z                                                         |  |  |  |  |

| Data Polling | V <sub>IL</sub> | V <sub>IL</sub> | Х        | $I_7/O_7 = \overline{D_{1N}}$                                  |  |  |  |  |

| Chip Erase   | V <sub>IL</sub> | VER             | $V_{ER}$ | Х                                                              |  |  |  |  |

FIGURE 3. Simple NMC9816A Interface Requirements

#### WRITE MODE

The NMC9816A is programmed electrically in-circuit, yet it provides the non-volatility usually obtained by optical erasure in EPROMS and by batteries with CMOS RAM. Writing to non-volatile memory has never been easier as no high voltage, external latching, erasing or timing is needed. When commanded to byte-write, the NMC9816A automatically latches the address, data, and control signals and starts the write cycle. During the write cycle Vpp is generated on-chip to perform an automatic byte-erase, then write.

#### **DATA POLLING**

The NMC9816A features DATA Polling to signal the completion of a byte write cycle. During a write cycle, an attempted read of the last byte written results in the data complement of that byte at I/O<sub>7</sub>. After completion of the write cycle, true data is available. DATA Polling allows a simple read/compare operation to determine the status of the chip eliminating the need for external hardware.

# DATA PROTECTION ON $V_{CC}$ POWER UP AND POWER DOWN

An erase/write of a byte in the NMC9816A is accomplished with input signals  $\overline{CE}$ ,  $\overline{WE} = V_{IL}$ . During system ( $V_{CC}$ ) power up and power down, this condition may be present as  $V_{CC}$  ramps up to or down from its steady state value of 5V. To prevent the possibility of an inadvertant byte write during this power transition period, an on-chip sensing circuit disables the internal programming circuit if  $V_{CC}$  falls below 4V (VLKO).

#### OPTIONAL HIGH VOLTAGE CHIP ERASE CYCLE

All data can be changed to "1" or erase state in one 10 ms cycle by raising  $\overline{OE}$  to 12–22V and bringing  $\overline{WE}$  to 12–22V for  $t_{WP}$  msec.

#### **READ MODE**

One aspect of the NMC9816A's high performance is its very fast read access time—typically less than 200 ns. Its read cycle is similar to that of EPROMS and static RAMs. It offers a two line control architecture to eliminate bus contention. The NMC9816A can be selected using decoded system address lines to  $\overline{\text{CE}}$  and then the device can be read, within the device selection time, using the processor's  $\overline{\text{RD}}$  signal connected to  $\overline{\text{OE}}$ .

#### STANDBY MODE

The NMC9816A has a standby mode in which power consumption is reduced by 70%. This offers the user power supply cost benefits when designing a system with NMC9816A's. This mode occurs when the device is deselected ( $\overline{\text{CE}} = \text{V}_{\text{IH}}$ ). The data pins are put into the high impedance state regardless of the signals applied to  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  concurrent with the reading and writing of other devices.

#### SYSTEM IMPLEMENTATION AND APPLICATION

The NMC9816A is compatible with industry standard microprocessors. It requires no interface circuitry and no support circuitry.

The NMC9816A is ideal for non-volatile memory requirements in applications requiring storage of user defined functions, calibration constants, configuration parameters and accumulated totals. Soft key configuration in a graphics terminal is an example where user defined functions, such as protocol, color, margins and character fonts can be keved in by the user. Calibration constants could be stored by the NMC9816A in the smart interface for a robot's axis of movement. Movement constants, compensation algorithms and learned axis characteristics can be stored. In programmable controllers and data loggers, configuration parameters for polling time, sequence and location, could be stored in the NMC9816A. Accumulated totals for dollars, energy consumption, volume and even the logging of service done on computer boards or systems can be stored in the NMC9816A.

The NMC9816A is cost effective for lower density E²PROM applications and can therefore be used to provide a lower system cost to the user compared to the 2816 or 2817. The user will find that tangible cost savings per system include: board space and component reductions, reduced assembly costs, savings in inventory costs, handling costs and quality assurance. The designer will find the NMC9816A reduces design time by a sizable factor over the 2816 or 2817 due to the integration of timing, logic, latching and 5V-only operation.

## **Device Operation (Continued)**

The NMC9816A will also open up new applications in environments where flexible parameter/data storage could not be implemented before. For example, applications with board space constraints are ideal for the NMC9816A. Several NMC9816A's can reside in the same space as one (1) 2816 with its support circuits. This is due to the reduction of all components required including the Vpp generator.

### WRITE TIME CHARACTERISTICS

The NMC9816A's internal write cycle contains an automatic erase feature. The 2816 does not have this capability and must be given an external erase cycle prior to a write. The 2816 has a write time specification of 9 ms. Typically, these devices will write in times less than 9 ms, but the worst-case bit defines the minimum specification.

The NMC9816A's internal cycle consists of an automatic 2 ms (typical) erase followed by a 2 ms (typical) write. The total cycle is then typically 4 ms. The NMC9816A maximum specification is 10 ms.

### WRITE PROTECTION

There are three features that protect the nonvolatile data from an inadvertant write.

- Noise Protection A WE pulse of less than 20 ns will not initiate a write cycle.

- $\bullet$  VCC Sense When VCC is below approximately 4V all 5V-only write functions are inhibited.

- $\begin{tabular}{ll} \bullet \begin{tabular}{ll} Write Inhibit $-$ Holding $\overline{OE}$ low, $\overline{WE}$ high, or $\overline{CE}$ high, inhibits a write cycle during power-on and power-off (VCC). \end{tabular}$