#### **Features**

- Organization: 262,144 words  $\times$  32 or 36 bits

- $\bullet$   $\widetilde{NTD}^{^{TM}}$  architecture for efficient bus operation

- Fast clock speeds to 150 MHz in LVTTL/LVCMOS

- Fast clock to data access: 3.8/4/5 ns • Fast  $\overline{OE}$  access time: 3.5/3.8/4 ns

- Fully synchronous operation

- "Flow-through" mode

- Asynchronous output enable control

- Multiple packaging options

- Economical 100-pin TQFP package

- Chip-scale fBGA package for smallest footprint

- Byte write enables

- Clock enable for operation hold

- Multiple chip enables for easy expansion

- 3.3 core power supply

- $\bullet$  2.5V or 3.3V I/O operation with separate  $V_{DDO}$

- 10 mW typical standby power

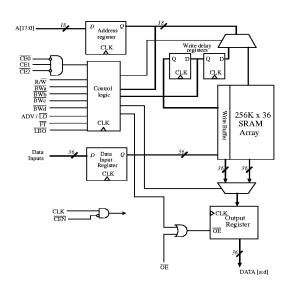

# Logic block diagram

### Pin arrangement

For information on the pin arrangement for the TQFP package, refer to the section entitled "Pin arrangement for TQFP (top view)" on page page 3.

For information on the pin arrangement for the chip-scale fBGA package, refer to the section entitled "Pin arrangement for chip-scale fBGA (top view)" on page page 3.

#### Selection guide

|                                     | 7C3256K36-3.8 | 7C3256K36-4 | 7C3256K36-5 | Units |

|-------------------------------------|---------------|-------------|-------------|-------|

| Minimum cycle time                  | 6.7           | 7.5         | 10          | ns    |

| Maximum pipelined clock frequency   | 150           | 133.3       | 100         | MHz   |

| Maximum pipelined clock access time | 3.8           | 4           | 5           | ns    |

| Maximum operating current           | 325           | 300         | 250         | mA    |

| Maximum standby current             | 60            | 60          | 60          | mA    |

| Maximum CMOS standby current (DC)   | 5             | 5           | 5           | mA    |

$NTD^{TM}$  is a trademark of Alliance Semiconductor Corporation.

ALLIANCE SEMICONDUCTOR DID 11-20029. 5/11/99

Copyright ©1998 Alliance Semiconductor. All rights reserved

#### Functional description

The AS7C3256K36Z family is a high performance CMOS 8 Mbit synchronous Static Random Access Memory (SRAM) organized as 262,144 words  $\times$  32 or 36 bits and incorporates a LATE LATE Write.

This variation of the 8Mb sychronous SRAM uses the No Turnaround Delay  $(NTD^{TM})$  architecture, featuring an enhanced write operation that improves bandwidth over pipeline burst devices. In a normal pipeline burst device, the write data, command, and address are all applied to the device on the same clock edge. If a read command follows this write information, the system must wait for two 'dead' cycles for valid data to become available. These dead cycles can significantly reduce overall bandwidth for applications requiring random access or read-modify-write operations.

$NTD^{TM}$  devices use the memory bus more efficiently by introducing a write 'latency' which matches the two cycle read latency. Write data is applied two cycles after the write command and address, allowing the read pipeline to clear. With  $NTD^{TM}$ , write and read operations can be used in any order without producing dead bus cycles.

The single register flow-through mode of the AS7C3256K36Z and AS7C3256K32Z can disable output circuit registers. This allows the device to operate in 2-1-1-1 mode rather than 3-1-1-1 found in two-stage pipeline architecture timing. The single register flow-through mode sacrifices access and cycle times for lower latency. Consult AC timing parameters for more details.

Assert R/W low to perform write cycles. Byte write enable controls write access to specific bytes, or can be tied low for full 32/36 bit writes. Write enable signals, along with the write address, are registered on a rising edge of the clock. Write data is applied to the device two clock cycles later. Unlike some asynchronous SRAMs, output enable  $\overline{OE}$  does not need to be toggled for write operations; it can be tied low for normal operations. Outputs go to a high impedance state when the device is de-selected by any of the three chip enable inputs In pipeline mode, a two cycle deselect latency allows pending read or write operations to be completed.

Use the ADV (burst advance) input to perform burst read and write operations. When ADV is high, external addresses are ignored, and internal address counters increment in the count sequence specified by the  $\overline{LBO}$  control. Any device operations, including burst, can be stalled using the  $\overline{CEN}$  clock enable input. If  $\overline{CEN}$  is high at the rising edge of clock, all operations are effectively stalled.

The AS7C3256K36Z and AS7C3256K32Z operate with a 3.3V  $\pm$  5% power supply for the device core (V<sub>DD</sub>). DQ circuits use a separate power supply (V<sub>DDQ</sub>) that operates across 3.3V or 2.5V ranges. These devices are available in a 100-pin 14×20 mm TQFP and 119 ball fine-pitch Ball-Grid-Array (fBGA) packaging.

## Capacitance 1

| Parameter         | Symbol           | Signals                  | Test conditions         | Max | Unit |

|-------------------|------------------|--------------------------|-------------------------|-----|------|

| Input capacitance | C <sub>IN</sub>  | Address and control pins | $V_{in} = 0V$           | 5   | рF   |

| I/O capacitance   | C <sub>I/O</sub> | I/O pins                 | $V_{in} = V_{out} = 0V$ | 7   | рF   |

$\mathcal{D}$

ALLIANCE SEMICONDUCTOR

DID 11-20029 5/11/99

# Pin arrangement for TQFP (top view)

Note: Pins 1,30,51,80 are NC for  $\times 32$

# Pin arrangement for chip-scale fBGA (top view)

|   | 1                  | 2                 | 3               | 4        | 5               | 6                 | 7                  |

|---|--------------------|-------------------|-----------------|----------|-----------------|-------------------|--------------------|

| Α | $V_{\mathrm{DDQ}}$ | Α                 | Α               | NC       | A               | Α                 | $V_{\mathrm{DDQ}}$ |

| В | NC                 | CE1               | Α               | ADV/LD   | Α               | Α                 | NC                 |

| C | NC                 | Α                 | Α               | $V_{DD}$ | Α               | Α                 | NC                 |

| D | DQc                | DQPc              | V <sub>SS</sub> | NC       | V <sub>SS</sub> | DQPb              | DQb                |

| E | DQc                | DQc               | V <sub>SS</sub> | CEO      | V <sub>SS</sub> | DQb               | DQb                |

| F | $V_{\mathrm{DDQ}}$ | DQc               | V <sub>SS</sub> | OE       | V <sub>SS</sub> | DQb               | $V_{\mathrm{DDQ}}$ |

| G | DQc                | DQc               | BWc             | NC       | ВWь             | DQb               | DQb                |

| Н | DQc                | DQc               | $V_{SS}$        | R/W      | $V_{SS}$        | DQb               | DQb                |

| J | $V_{\mathrm{DDQ}}$ | $V_{\mathrm{DD}}$ | NC              | $V_{DD}$ | NC              | $V_{\mathrm{DD}}$ | $V_{\mathrm{DDQ}}$ |

| K | DQd                | DQd               | $V_{SS}$        | Clk      | $V_{SS}$        | DQa               | DQa                |

| L | DQd                | DQd               | BWd             | NC       | BWa             | DQa               | DQa                |

| M | $V_{\mathrm{DDQ}}$ | DQd               | $V_{SS}$        | CEN      | $V_{SS}$        | DQa               | $V_{\mathrm{DDQ}}$ |

| N | DQd                | DQd               | $V_{SS}$        | A        | $V_{SS}$        | DQa               | DQa                |

| P | DQd                | DQPd              | $V_{SS}$        | A        | $V_{SS}$        | DQPa              | DQa                |

| R | NC                 | A                 | ĽBO             | $V_{DD}$ | FΤ              | A                 | NC                 |

| T | NC                 | NC                | Α               | A        | A               | NC                | ZZ                 |

| U | $V_{\mathrm{DDQ}}$ | NC                | NC              | NC       | NC              | NC                | $V_{\mathrm{DDQ}}$ |

Note: Pins 2D, 2P, 6D, 6P are NC for  $\times$ 32.

### Signal descriptions

| Signal           | 1/0 | Properties | Description                                                                                                                                                                               |

|------------------|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK              | I   | CLOCK      | Clock. All inputs except OE are synchronous to this clock.                                                                                                                                |

| CEN              | I   | SYNC       | Clock enable. When de-asserted HIGH, the clock input signal is masked.                                                                                                                    |

| A0-A17           | I   | SYNC       | Address. Sampled when all chip enables are active and LD is asserted.                                                                                                                     |

| DQ[a,b,c,d]      | I/O | SYNC       | Data. Driven as output when the chip is enabled and $\overline{\text{OE}}$ is active.                                                                                                     |

| CEO, CE1,<br>CE2 | Ι   | SYNC       | Synchronous chip enables. De-assertion of any chip enable causes power-down of the device.                                                                                                |

| ADV/LD           | I   | SYNC       | Advance or Load. When sampled HIGH, the internal burst address counter will increment in the order defined by the $\overline{\text{LBO}}$ input value. When LOW, a new address is loaded. |

| R/W              | Ι   | SYNC       | Write enable. Asserted LOW to initiate a write operation.                                                                                                                                 |

| BW[a,b,c,d]      | Ι   | SYNC       | Byte write enables. Used to control write of individual bytes. When sampled LOW with $\overline{WE}$ , data is accepted for write operations to DQ banks a,b,c, and d respectively.       |

| OE               | I   | ASYNC      | Asynchronous output enable. I/O pins are driven when $\overline{OE}$ is active and the chip is synchronously enabled.                                                                     |

| LBO              | I   | STATIC     | Count mode. When driven High, count sequence follows Intel XOR convention. When driven Low, count sequence follows linear convention. This input should be static.                        |

| FT               | I   | STATIC     | Flow-through mode. When low, enables single register flow-through mode. Connect to $V_{\mbox{\scriptsize DD}}$ if unused or for pipelined operation.                                      |

| ZZ               | I   | ASYNC      | Sleep. Places device in low power mode; data is retained. Connect to GND if unused.                                                                                                       |

| nc               | -   | _          | No connects. Note that pin 84 will be used for future address expansion to 16Mb density.                                                                                                  |

|                  |     |            |                                                                                                                                                                                           |

DID 11-20029 5/11/99

ALLIANCE SEMICONDUCTOR

K)

#### Absolute maximum ratings Parameter Symbol Min Max Unit V -0.5+4.6 Power supply voltage relative to GND $V_{DD}$ , $V_{DDO}$ V Input voltage relative to GND (input pins) $V_{IN}$ -0.5+4.6 Input voltage relative to GND (I/O pins) $V_{IN}$ -0.5 $V_{\mathrm{DDO}} + 0.5$ V 1.2 W Power dissipation $P_{\mathrm{D}}$ 30 DC output current mAI<sub>OUT</sub> °C $T_{stg}$ -65+150 Storage temperature (plastic) $T_{\text{bias}}$ °C Temperature under bias -65+135

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect reliability.

#### Synchronous truth table

| CEO | CE1 | CEZ | ADV/LD | R/W | $\overline{\mathrm{BW}[\mathrm{a};\mathrm{d}]}$ | OE | Address source | CLK    | Operation         |

|-----|-----|-----|--------|-----|-------------------------------------------------|----|----------------|--------|-------------------|

| Н   | X   | X   | (1)    | X   | X                                               | X  | NA             | L to H | Deselect, high-Z  |

| X   | L   | X   | (1)    | X   | X                                               | X  | NA             | L to H | Deselect, high-Z  |

| X   | X   | Н   | (1)    | X   | X                                               | X  | NA             | L to H | Deselect, high-Z  |

| L   | Н   | L   | L      | Н   | X                                               | X  | External       | L to H | Begin read        |

| L   | Н   | L   | Н      | Н   | X                                               | X  | External       | L to H | Begin burst read  |

| L   | Н   | L   | L      | L   | L(2)                                            | X  | External       | L to H | Begin write       |

| L   | Н   | L   | Н      | L   | L(2)                                            | X  | External       | L to H | Begin burst write |

Key: X = Don't Care, L = Low, H = High.

|                                              |                    | RRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRRR |       |         |                     |                 |  |

|----------------------------------------------|--------------------|----------------------------------------|-------|---------|---------------------|-----------------|--|

| Recommended                                  | operating conditio | ns                                     |       |         |                     |                 |  |

| Parameter                                    |                    | Symbol                                 | Min   | Nominal | Max                 | Unit            |  |

| Supply voltage                               |                    | $V_{ m DD}$                            | 3.0   | 3.3     | 3.6                 | V               |  |

|                                              |                    | GND                                    | 0.0   | 0.0     | 0.0                 | V               |  |

| 3.3V I/O supply                              |                    | $V_{\mathrm{DDQ}}$ 3.1                 |       | 3.3     | 3.465               | W               |  |

| voltage                                      |                    | $\overline{GND_{\mathrm{Q}}}$          | 0.0   | 0.0     | 0.0                 | — v             |  |

| 2.5V I/O supply                              |                    | $V_{ m DDQ}$                           | 2.35  | 2.5     | 2.65                | 17              |  |

| voltage                                      |                    | $\overline{GND_{\mathrm{Q}}}$          | 0.0   | 0.0     | 0.0                 | — v             |  |

|                                              | Address and        | V <sub>IH</sub>                        | 2.0   | _       | 4.5                 | V               |  |

| т , т, т                                     | control pins       | $\overline{ m V_{IL}}$                 | -0.5* | -       | 0.8                 | V               |  |

| Input voltages†                              | 1/0                | V <sub>IH</sub>                        | 2.0   | -       | $V_{\rm DDQ} + 0.5$ | V               |  |

|                                              | I/O pins           | $\overline{ m V_{IL}}$                 | -0.5* | _       | 0.8                 |                 |  |

| Ambient operating temperature T <sub>A</sub> |                    |                                        | 0     | _       | 70                  | ${\mathfrak C}$ |  |

<sup>\*</sup>  $V_{IL}$  min = -2.0V for pulse width less than 0.2 x  $t_{RC}.$

#### DC electrical characteristics

|                                |                     |                                                                                                                                                                                       | -3  | 8.8 |     | 4   | -   | 5   |      |

|--------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|------|

| Parameter                      | Symbol              | Test conditions                                                                                                                                                                       | Min | Max | Min | Max | Min | Max | Unit |

| Input leakage current          | I <sub>LI</sub>     | $V_{\mathrm{DD}}$ = Max, $V_{\mathrm{in}}$ = GND to $V_{\mathrm{DD}}$                                                                                                                 | _   | 2   | -   | 2   | _   | 2   | μA   |

| Output leakage current         | $\mid$ $I_{LO}\mid$ | $\overline{OE} \ge V_{IH,} V_{DD} = Max,$ $V_{out} = GND \text{ to } V_{DD}$                                                                                                          | -   | 2   | ı   | 2   | -   | 2   | μА   |

| Operating power supply current | $I_{CC}$            | $\overline{\text{CE}} = \text{V}_{\text{IL}}, \text{ CE} = \text{V}_{\text{IH}}, \overline{\text{CE}} = \text{V}_{\text{IL}},$<br>$f = f_{\text{max}}, I_{\text{out}} = 0 \text{ mA}$ | -   | 325 | ١   | 300 | _   | 250 | mA   |

| Standby narran                 | $I_{SB}$            | Deselected, $f = f_{\text{max}}$                                                                                                                                                      | _   | 60  | ı   | 60  | -   | 60  | mA   |

| Standby power supply current   | $I_{SB1}$           | Deselected, f = 0, all $V_{IN} \le 0.2V$ or $\ge V_{DD}$ - 0.2V                                                                                                                       | -   | 5   | ı   | 5   | -   | 5   | mA   |

| Outment and the me             | $V_{\rm OL}$        | $I_{OL} = 8 \text{ mA}, V_{DDO} = 3.6 \text{V}$                                                                                                                                       | _   | 0.4 | ı   | 0.4 | _   | 0.4 | V    |

| Output voltage                 | $V_{OH}$            | $I_{OH} = -4 \text{ mA}, V_{DDO} = 3.0 \text{V}$                                                                                                                                      | 2.4 | _   | 2.4 | _   | 2.4 | _   | V    |

# DC electrical characteristics for 2.5V I/O operation

|                           |                   |                                                                                 | - 1 | 66  | - 1 | 50  | -1  | 33  | - 1 | 00  |                                       |

|---------------------------|-------------------|---------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|---------------------------------------|

| Parameter                 | Symbol            | Test conditions                                                                 | Min | Max | Min | Max | Min | Max | Min | Max | Unit                                  |

| Output leakage<br>current | I <sub>LO</sub>   | $\overline{OE} \ge V_{IH_{.}} V_{DD} = Max,$ $V_{out} = GND \text{ to } V_{DD}$ | -1  | 1   | -1  | 1   | -1  | 1   | -1  | 1   | μΑ                                    |

| Output waltage            | $V_{\mathrm{OL}}$ | $I_{OL} = 2 \text{ mA}, V_{DDQ} = 2.65 \text{V}$                                | _   | 0.7 | _   | 0.7 | ı   | 0.7 | -   | 0.7 | W                                     |

| Output voltage            | $V_{OH}$          | $I_{OH} = -2 \text{ mA}, V_{DDO} = 2.35 \text{V}$                               | 1.7 | -   | 1.7 | -   | 1.7 | -   | 1.7 | -   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

DID 11-20029 5/11/99

ALLIANCE SEMICONDUCTOR

$<sup>^\</sup>dagger$  Input voltage ranges apply to 3.3V I/O operation. For 2.5V operation, contact factory for input specifications.

# Timing characteristics over operating range

|                                         | 0                 | -3.8 -4 |     | -5  |     |     |     |      |       |

|-----------------------------------------|-------------------|---------|-----|-----|-----|-----|-----|------|-------|

| Parameter                               | Symbol            | Min     | Max | Min | Max | Min | Max | Unit | Notes |

| Clock frequency                         | $F_{MAX}$         | -       | 150 | -   | 133 | -   | 100 | MHz  | 1     |

| Cycle time (pipelined mode)             | t <sub>CYC</sub>  | 6.6     | -   | 7.5 | -   | 10  | -   | ns   |       |

| Cycle time (flow-through mode)          | t <sub>CYCF</sub> | 10      | -   | 12  | -   | 15  | -   | ns   |       |

| Clock access time (pipelined mode)      | t <sub>CD</sub>   | -       | 3.8 | -   | 4   | -   | 5   | ns   |       |

| Clock access time (flow-through mode)   | t <sub>CDF</sub>  | -       | 6.6 | -   | 7.5 | -   | 10  | ns   |       |

| Output enable Low to data valid         | t <sub>OE</sub>   | -       | 3.5 | -   | 3.8 | -   | 4   | ns   |       |

| Clock High to output Low Z              | $t_{\rm LZC}$     | 0       | -   | 0   | -   | 0   | -   | ns   | 8     |

| Data output hold from clock High        | t <sub>OH</sub>   | 1.5     | -   | 1.5 | -   | 2   | -   | ns   | 8     |

| Output enable Low to output Low Z       | t <sub>LZOE</sub> | 1       | -   | 1.5 | -   | 2   | -   | ns   | 8     |

| Output enable High to output High Z     | t <sub>HZOE</sub> | -       | 3.5 | -   | 4   | -   | 4   | ns   | 8     |

| Clock High to output High Z             | t <sub>HZC</sub>  | -       | 3   | -   | 3.5 | -   | 3.5 | ns   | 8     |

| Clock High to output High Z             | t <sub>HZCN</sub> | -       | 1.5 | -   | 2   | -   | 2.5 | ns   | 1,9   |

| Clock High pulse width                  | t <sub>CH</sub>   | 2.6     | -   | 2.8 | -   | 3   | -   | ns   |       |

| Clock Low pulse width                   | $t_{\rm CL}$      | 2.6     | -   | 2.8 | -   | 3   | -   | ns   |       |

| Address and Control setup to clock High | t <sub>AS</sub>   | 1.3     | -   | 1.5 | -   | 1.5 | -   | ns   |       |

| Data setup to clock High                | t <sub>DS</sub>   | 1.3     | -   | 1.5 | -   | 1.5 | -   | ns   |       |

| Write setup to clock High               | t <sub>WS</sub>   | 1.3     | -   | 1.5 | -   | 1.5 | -   | ns   |       |

| Chip select setup to clock High         | t <sub>CSS</sub>  | 1.3     | -   | 1.5 | -   | 1.5 | -   | ns   |       |

| Address hold from clock High            | t <sub>AH</sub>   | 0.5     | -   | 0.5 | -   | 0.5 | -   | ns   |       |

| Data hold from clock High               | t <sub>DH</sub>   | 0.5     | -   | 0.5 | -   | 0.5 | -   | ns   |       |

| Write hold from clock High              | t <sub>WH</sub>   | 0.5     | -   | 0.5 | -   | 0.5 | -   | ns   |       |

| Chip select hold from clock High        | t <sub>CSH</sub>  | 0.5     | -   | 0.5 | -   | 0.5 | -   | ns   |       |

| Output rise time (0 pF load)            | t <sub>R</sub>    | 1.5     | -   | 1.5 | -   | 1.5 | -   | V/ns | 1     |

| Output fall time (0 pF load)            | t <sub>F</sub>    | 1.5     | -   | 1.5 | -   | 1.5 | -   | V/ns | 1     |

See "Notes" on page 9.

# Key to switching waveforms

Rising input Undefined output/don't care

ALLIANCE SEMICONDUCTOR

DID 11-20029-5/11/99

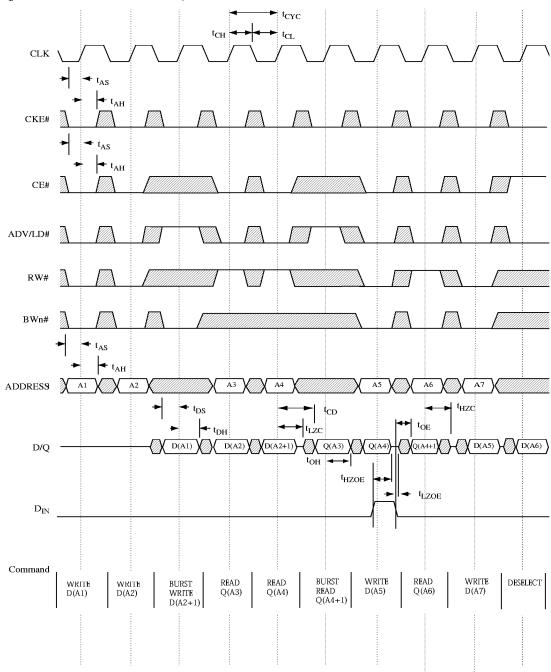

Timing waveform of read/write cycle

Note:  $\oplus$  = XOR when MODE = High/No Connect;  $\oplus$  = ADD when MODE = Low.  $\overline{WE}[0:3]$  is don't care.

DID 11-20029 5/11/99

ALLIANCE SEMICONDUCTOR

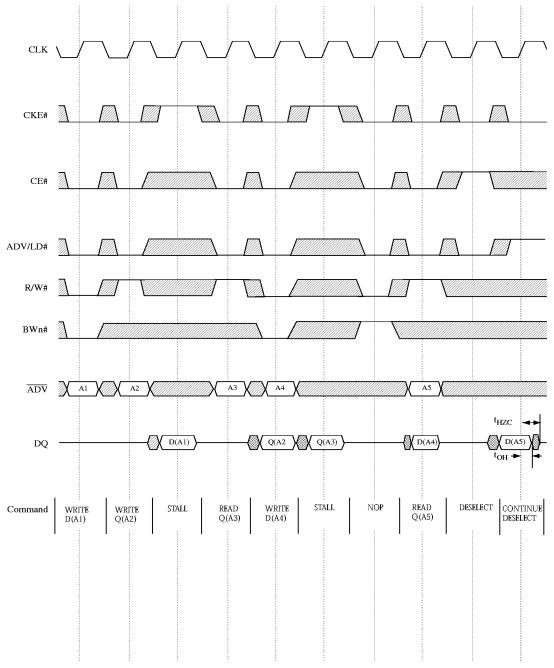

NOP, stall and deselect cycles

Note:  $\Theta$  = XOR when MODE = High/No Connect;  $\Theta$  = ADD when MODE = Low. Note:  $\Theta$  = XOR when MODE = High/No Connect;  $\Theta$  = ADD when MODE = Low.

Note:  $\overline{OE}$  is Low.

8

ALLIANCE SEMICONDUCTOR

DID 11-20029, 5/11/99

#### Notes

- 1 This parameter is guaranteed but not tested.

- 2 For test conditions, see AC Test Conditions, Figures A, B, C.

- 3 This parameter is sampled and not 100% tested.

- 4 This is a synchronous device. All addresses must meet the specified setup and hold times for all rising edges of CLK. All other synchronous inputs must meet the setup and hold times with stable logic levels for all rising edges of CLK when chip is enabled.

- 5 Typical values measured at 3.3V, 25  $^{\circ}$ C and 10 ns cycle time.

- 6~  $I_{\text{CC}}$  given with no output loading.  $I_{\text{CC}}$  increases with faster cycle times and greater output loading.

- 7 Transitions are measured  $\pm 500$  mV from steady state voltage. Output loading specified with  $C_L=5~\rm pF$  as in Figure C.

- 8  $~t_{HZOE}$  is less than  $t_{LZOE}$ ; and  $t_{HZC}$  is less than  $t_{LZC}$  at any given temperature and voltage.

- $9~~t_{\mbox{\scriptsize HZCN}}$  is a 'no load' parameter to indicate exactly when SRAM outputs have stopped driving.

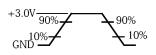

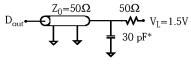

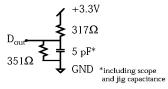

#### AC test conditions

- Output Load: see Figure B,

- except for  $t_{LZC}$ ,  $t_{LZOE}$ ,  $t_{HZOE}$ ,  $t_{HZC}$  see Figure C.

- Input pulse level: GND to 3V. See Figure A.

- Input rise and fall time (Measured at 0.3V and 2.7V): 2 ns. See Figure A.

- Input and output timing reference levels: 1.5V.

Figure A: Input waveform

Figure B: Output load (A)

Figure C: Output load (B)

# AS7C3256K32Z and AS7C3256K36Z ordering information

| Package | Width | 150 MHz             | 133 MHz           | 100 MHz           |

|---------|-------|---------------------|-------------------|-------------------|

| TQFP    | ×32   | AS7C3256K32Z-3.8TQC | AS7C3256K32Z-4TQC | AS7C3256K32Z-5TQC |

| TQFP    | ×36   | AS7C3256K36Z-3.8TQC | AS7C3256K36Z-4TQC | AS7C3256K36Z-5TQC |

| fBGA    | ×32   | AS7C3256K32Z-3.8BC  | AS7C3256K32Z-4BC  | AS7C3256K32Z-5BC  |

| fBGA    | ×36   | AS7C3256K36Z-3.8BC  | AS7C3256K36Z-4BC  | AS7C3256K36Z-5BC  |

### AS7C3256K32Z and AS7C3256K36Z part numbering system

| AS7C           | 3                    | 256K36                       | P                                               | XX                  | XX                                | С                                                           |

|----------------|----------------------|------------------------------|-------------------------------------------------|---------------------|-----------------------------------|-------------------------------------------------------------|

| SRAM<br>prefix | Operating<br>voltage | Part number,<br>organization | Timing<br>Z=NTD <sup>™</sup> timing<br>P=PBSRAM | Access time<br>(ns) | Package:<br>TQ = TQFP<br>B = fBGA | Commercial temperature, $0~{\mathbb C}$ to $70~{\mathbb C}$ |

DID 11-20029 5/11/99

ALLIANCE SEMICONDUCTOR

\*