#### **Features**

- Provides this functionality required to terminate a DS3 signal:

- Clock recovery and filter

- All line equalization

- LOS detection and AIS generation

- B3ZS decoding

- Satisfies Jitter Tolerance requirements on the DS-3 inputs

- Receives at STS-1 rate (51.84 MHz) as well as the DS-3 rate (44.736 MHz)

- Meets all applicabele ANSI/BellCore standards

- -T1.102, 107

- -TR-TSY-000009

- · Detects and indicates coding errors

- CMOS for low power and enhanced reliability

# DS-3 RECEIVE ONLY DS3RX Device TXC<sup>™</sup> -02003

#### PRELIMINARY DATA SHEET

TranSwitch © 1990

Patents Pending

#### **Description**

The DS3RX is similar in function with the DS3RT (TXC-02001). The DS3RX contains the receive path only, however, and this data sheet is therefore abbreviated.

Please see TXC-02001-AXXX-MB, the data sheet for the DS3RT for timing details and packaging. All of the receive side features of the DS3RT are included in the DS3RX.

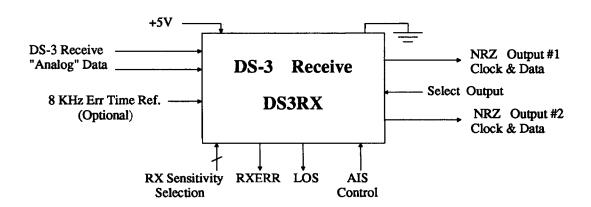

In summary, the DS3RX receives DS-3 B3ZS encoded line data, recovers the clock, decodes the B3ZS signal, counts and outputs coding violations, records the loss of DS-3 input data, and provides for the introduction of an AIS (blue) signal to be passed to the NRZ side of the chip.

### **Applications**

- DS-3 Monitoring

- SONET STS-1 Monitoring

- Retrofit changes / cost reduction

# **Functional Diagram**

TXC and TranSwitch are trademarks of TranSwitch Corporation

TXC-02003-AXXX-MA Ed. C, August, 1990

## DS3RX PIN I/O AND FUNCTION

|        | _ · T                                          |              |                                             |

|--------|------------------------------------------------|--------------|---------------------------------------------|

| NAME   | I/O                                            | PIN NO.      | FUNCTION                                    |

| AVDD   | P                                              | 23,24,37     | 5-volt supply voltage, +/- 5%, Analog       |

| DVDD   | P                                              | 10,42,43     | " " Digital                                 |

| AGND   | P                                              | 31,32,36     | VSS or ground, 0 volts reference, Analog    |

| AGND1  | P                                              | 16           | " " " Analog (PLL)                          |

| DGND   | P                                              | 6,11, 44     | " " " Digital                               |

| RXAIS  | I                                              | 3            | Strap to ground to enable receive AIS       |

| CLK8   | I                                              | 4            | 8 KHz clock input to estimate BER           |

| RXERR  | 0                                              | 5            | Approximate Indication of BER>10-6          |

| VCOC   | 0                                              | 7            | External capacitor connection               |

| DCK    | I                                              | 9            | DS-3 external clock for AIS                 |

| D3RD2  | 0                                              | 12           | NRZ DS3 Receive Data no. 2                  |

| D3RD1  | 0                                              | 13           | NRZ DS3 Receive Data output no. 1           |

| D3RC2  | 0                                              | 14           | Clock out for Receive DS3 data output no. 2 |

| DS3C1  | O                                              | 15           | Clock out for Receive DS3 data output no. 1 |

| RPLLC  | О                                              | 17           | External Capacitor Connection               |

| BPV    | O                                              | 19           | Coding Violation pulse output               |

| RXLOS  | 0                                              | 20           | Ground-true indication of Loss of Signal    |

| RXDIS  | I                                              | 21           | Strap to ground to disable the outputs      |

| SLCT   | I                                              | 22           | Strap to ground to enable NRZ I/O no. 2     |

| ASEL0  | I                                              | 26           | Receive Gain control LSB                    |

| ASEL1  | I                                              | 27           | Receive Gain control MSB                    |

| DS3IN1 | I                                              | 29           | DS-3 Line Input (1 of 2)                    |

| DS3IN2 | I                                              | 30           | DS-3 Line Input (2 of 2)                    |

|        |                                                | 1,3,8,18     |                                             |

| N.C.   |                                                | 26,27,33-35  | Not Connected                               |

|        |                                                | 38-41,44     |                                             |

|        | <u>.                                      </u> | <del> </del> |                                             |

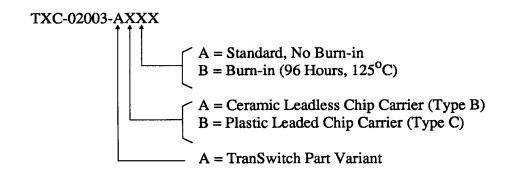

#### ORDERING INFORMATION

TranSwitch reserves the right to make changes to the product(s) or circuit(s) described herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product or circuit.

> TXC-02003-AXXX-MA Ed. C, 08/90

> > 021148 \_\_\_