# Synchronous Rectification DC/DC Converter Programmable Integrated Controller

The MC33470 is a digitally programmable switching voltage regulator, specifically designed for Microprocessor supply, Voltage Regulator Module and general purpose applications, to provide a high power regulated output voltage using a minimum of external parts. A 5-bit digital-to-analog converter defines the dc output voltage.

This product has three additional features. The first is a pair of high speed comparators which monitor the output voltage and expedite the circuit response to load current changes. The second feature is a soft start circuit which establishes a controlled response when input power is applied and when recovering from external circuit fault conditions. The third feature is two output drivers which provide synchronous rectification for optimum efficiency.

This product is ideally suited for computer, consumer, and industrial equipment where accuracy, efficiency and optimum regulation performance is desirable.

#### MC33470 Features:

- 5-Bit Digital-to-Analog Converter Allows Digital Control of Output Voltage

- High Speed Response to Transient Load Conditions

- Output Enable Pin Provides On/Off Control

- Programmable Soft Start Control

- High Current Output Drives for Synchronous Rectification

- Internally Trimmed Reference with Low Temperature Coefficient

- Programmable Overcurrent Protection

- Overvoltage Fault Indication

- Functionally Similar to the LTC1553

## MC33470

# SYNCHRONOUS RECTIFICATION DC/DC CONVERTER PROGRAMMABLE INTEGRATED CONTROLLER

## SEMICONDUCTOR TECHNICAL DATA

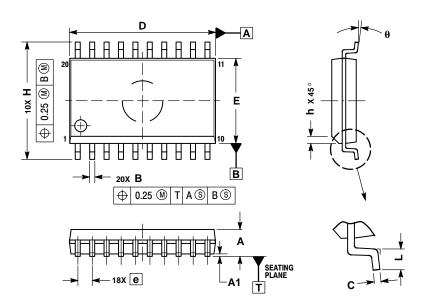

**DW SUFFIX**PLASTIC PACKAGE

CASE 751D

(SO-20L)

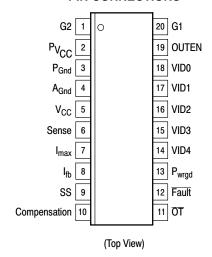

#### PIN CONNECTIONS

#### **ORDERING INFORMATION**

| Device    | Operating<br>Temperature Range                 | Package |  |

|-----------|------------------------------------------------|---------|--|

| MC33470DW | $T_A = 0^\circ \text{ to } +75^\circ \text{C}$ | SO-20L  |  |

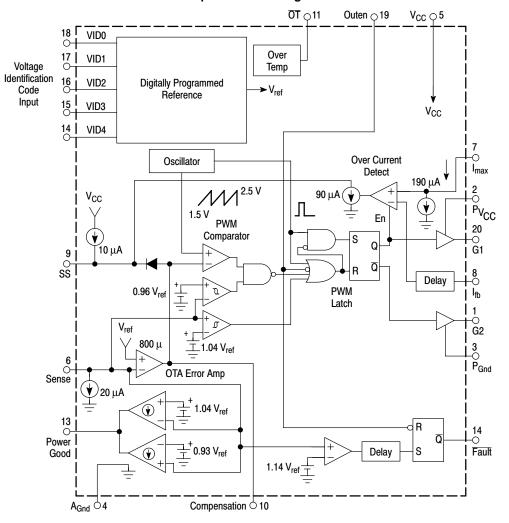

## **Simplified Block Diagram**

### **MAXIMUM RATINGS** ( $T_C = 25^{\circ}C$ , unless otherwise noted.)

| Rating                                                                                                                                                                                             | Symbol                                                 | Value                            | Unit              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------|-------------------|

| Power Supply Voltage                                                                                                                                                                               | V <sub>CC</sub>                                        | 7.0                              | V                 |

| Output Driver Supply Voltage (Operating)                                                                                                                                                           | P <sub>V</sub> cc                                      | 18                               | V                 |

| I <sub>max</sub> , I <sub>fb</sub> Inputs                                                                                                                                                          | V <sub>in</sub>                                        | -0.3 to 18                       | V                 |

| All Other Inputs and Digital (OT, Fault, Power Good) Outputs                                                                                                                                       | V <sub>in</sub>                                        | -0.3 to<br>V <sub>CC</sub> + 0.3 | V                 |

| Power Dissipation and Thermal Characteristics  Maximum Power Dissipation  Case 751D DW Suffix (T <sub>A</sub> = 70°C)  Thermal Resistance Junction–to–Ambient  Thermal Resistance Junction–to–Case | P <sub>D</sub><br>R <sub>θJA</sub><br>R <sub>θJC</sub> | 0.60<br>91<br>60                 | W<br>°C/W<br>°C/W |

| Operating Junction Temperature                                                                                                                                                                     | TJ                                                     | 125                              | °C                |

| Operating Ambient Temperature (Notes 1 and 2)                                                                                                                                                      | T <sub>A</sub>                                         | 0 to +70                         | °C                |

| Storage Temperature Range                                                                                                                                                                          | T <sub>stg</sub>                                       | -55 to +125                      | °C                |

NOTE: ESD data available upon request

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 5.0 \text{ V}$ ,  $P_{V_{CC}} = 12 \text{ V}$  for typical values  $T_A = Low$  to High [Notes 1, 2, 3], for min/max values  $T_A$  is the operating ambient temperature range that applies, unless otherwise noted.)

| Characteristic                                                                                                                                                                         | Symbol                                 | Min                    | Тур               | Max                    | Unit               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------|-------------------|------------------------|--------------------|

| OSCILLATOR                                                                                                                                                                             |                                        | •                      | •                 | •                      |                    |

| Frequency (V <sub>CC</sub> = 4.5 to 5.5 V)                                                                                                                                             | f <sub>osc</sub>                       | 210                    | 300               | 390                    | kHz                |

| FEEDBACK AMPLIFIER                                                                                                                                                                     | •                                      |                        | •                 | 1                      | · ·                |

| Voltage Feedback Input Threshold (Note 4) VID0, VID1, VID2 and VID4 = "1" and VID3 = "0" VID4 = "1" and VID0, VID1, VID2 and VID3 = "0"                                                | V <sub>sense</sub>                     | 1.764<br>2.744<br>3.43 | 1.8<br>2.8<br>3.5 | 1.836<br>2.856<br>3.57 | V<br>V<br>V        |

| Input Bias Current (V <sub>CM</sub> = 2.8 V)                                                                                                                                           | I <sub>IB</sub>                        | _                      | 20                | -                      | μΑ                 |

| Transconductance (V <sub>CM</sub> = 2.8 V, V <sub>COMP</sub> = 2.0 V)                                                                                                                  | G <sub>M</sub>                         | 400                    | 800               | 1200                   | μmho               |

| Open Loop Voltage Gain (V <sub>COMP</sub> = 2.0 V)                                                                                                                                     | A <sub>VOL</sub>                       | _                      | 67                | _                      | dB                 |

| Output Line Regulation (V <sub>CC</sub> = 4.5 to 5.5 V)                                                                                                                                | Reg <sub>line</sub>                    | _                      | 7.0               | _                      | mV                 |

| Output Load Regulation                                                                                                                                                                 | Reg <sub>load</sub>                    | _                      | 5.0               | _                      | mV                 |

| Output Current Source Sink                                                                                                                                                             | I <sub>OH</sub><br>I <sub>OL</sub>     | _<br>_                 | 120<br>120        | _<br>_                 | μА                 |

| PWM SECTION                                                                                                                                                                            |                                        | ,                      | •                 | ,                      |                    |

| Duty Cycle at G1 Output  Maximum  Minimum                                                                                                                                              | DC <sub>max</sub><br>DC <sub>min</sub> | 77<br>-                | 88<br>-           | 95<br>0                | %                  |

| Propagation Delay Comp Input to G1 Output, $T_J = 25^{\circ}C$ Comp Input to G2 Output, $T_J = 25^{\circ}C$                                                                            | <sup>t</sup> PLH1<br><sup>t</sup> PLH2 | -<br>-                 | 0.1<br>0.1        | -<br>-                 | μs                 |

| SOFT-START SECTION                                                                                                                                                                     |                                        |                        |                   |                        |                    |

| Charge Current (V <sub>Soft-Start</sub> = 0 V)                                                                                                                                         | I <sub>chg</sub>                       | 7.0                    | 10                | 13                     | μΑ                 |

| Discharge Current under Current Limit (Note 5) (V <sub>Soft-Start</sub> = 2.0 V, V <sub>sense</sub> = V <sub>out</sub> , V <sub>imax</sub> = V <sub>CC</sub> , V <sub>ifb</sub> = 0 V) | I <sub>SSIL</sub>                      | 30                     | 90                | 150                    | μА                 |

| Discharge Current under Hard Current Limit $(V_{Soft-Start} = 2.0 \text{ V}, V_{sense} < V_{out}/2, V_{imax} = V_{CC}, V_{ifb} = 0 \text{ V})$                                         | I <sub>SSHIL</sub>                     | 40                     | 64                | -                      | mA                 |

| Hard Current Limit Hold Time                                                                                                                                                           | t <sub>SSHIL</sub>                     | 100                    | 200               | 300                    | μs                 |

| IMAX INPUT                                                                                                                                                                             |                                        |                        |                   |                        |                    |

| Sink Current ( $V_{in max} = V_{CC}$ , $V_{ifb} = V_{CC}$ )                                                                                                                            | I <sub>OL</sub>                        | 133                    | 190               | 247                    | μΑ                 |

| POWER GOOD OUTPUT                                                                                                                                                                      |                                        |                        |                   |                        |                    |

| Threshold For Logic "1" to "0" Transition Upper Threshold Lower Threshold                                                                                                              | V <sub>th</sub>                        | -<br>0.93              | 1.04<br>0.96      | 1.07                   | V <sub>sense</sub> |

| Response Time Logic "0" to "1" (V <sub>sense</sub> changes from 0 V to V <sub>O</sub> ) Logic "1" to "0" (V <sub>sense</sub> changes from V <sub>O</sub> to 0 V)                       | t <sub>rPG</sub>                       | 200<br>50              | 400<br>100        | 600<br>150             | μs                 |

| Sink Current (V <sub>OL</sub> = 0.5 V)                                                                                                                                                 | I <sub>OLPG</sub>                      | _                      | 10                | -                      | mA                 |

| Output Low Voltage (I <sub>OL</sub> = 100 μA) (Note 6)                                                                                                                                 | V <sub>OLPG</sub>                      | _                      | 250               | 500                    | mV                 |

NOTES: 1. Maximum package power dissipation limits must be observed.

- 2. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

- 3. VID1, VID3, VID4 = logic 0, and VID0, VID2 = logic 1.

- 4.  $V_{sense}$  is provided from a low impedance voltage source or shorted to the output voltage. 5. Under a typical soft current limit, the net soft–start discharge current will be 90  $\mu$ A ( $I_{SSIL}$ ) 10  $\mu$ A ( $I_{chg}$ ) = 80  $\mu$ A. The softstart 5. Order a typical soft current limit, the net soft-start discharge current will be 90 μA (t<sub>SSIL</sub>) = 10 μA (t<sub>Chg</sub>) = 80 μA. The softstart sink to source current ratio is designed to be 9:1.

6 Sense (Pin 6) = 5.0 V, Comp (Pin 10) open, VID4, VID2, VID1, VID0 = 1.0, VID3 = 0.

7. OUTEN is internally pulled low if VID0, 1, 2, 3, and 4 are floating.

8. Due to internal pull–up resistors, there will be an additional 0.5 mA per pin if any of the VID0, 1, 2, 3, or 4 pins are pulled low.

**ELECTRICAL CHARACTERISTICS (continued)** ( $V_{CC} = 5.0 \text{ V}$ ,  $P_{V_{CC}} = 12 \text{ V}$  for typical values  $T_A = Low$  to High [Notes 1, 2, 3], for min/max values  $T_A$  is the operating ambient temperature range that applies, unless otherwise noted.)

| Characteristic                                                                                             | Symbol                | Min  | Тур  | Max  | Unit             |

|------------------------------------------------------------------------------------------------------------|-----------------------|------|------|------|------------------|

| FAULT OUTPUT                                                                                               |                       |      |      |      | •                |

| Threshold For Logic "0" to "1" Transition                                                                  | $V_{thF}$             | 1.12 | 1.14 | 1.2  | V <sub>ref</sub> |

| V <sub>sense</sub> Response Time Switches from 2.8 V to V <sub>CC</sub>                                    | t <sub>rF</sub>       | 50   | 100  | 150  | μs               |

| Sink Current (V <sub>OL</sub> = 0.5 V)                                                                     | I <sub>OLF</sub>      | _    | 10   | _    | mA               |

| OVERTEMPERATURE OUTPUT                                                                                     |                       | •    |      | •    |                  |

| Threshold For Logic "1" to "0" Transition (OUTEN Voltage Decreasing)                                       | $V_{thOUTEN}$         | 1.85 | 2.0  | 2.2  | V                |

| Delay Time                                                                                                 | t <sub>DOT</sub>      | 25   | 50   | 100  | μs               |

| Sink Current (V <sub>OL</sub> = 0.5 V)                                                                     | I <sub>OLF</sub>      | -    | 10   | _    | mA               |

| LOGIC INPUTS (VID0, VID1, VID2, VID3, VID4)                                                                |                       |      |      |      |                  |

| Input Low State                                                                                            | $V_{IL}$              | _    | _    | 0.8  | V                |

| Input High State                                                                                           | $V_{IH}$              | 3.5  | _    | _    | V                |

| Input Impedance                                                                                            | R <sub>in</sub>       | -    | 10   | _    | kΩ               |

| OUTPUT ENABLE CONTROL (OUTEN)                                                                              |                       |      |      |      |                  |

| Over–Temperature Driver Disable and Reset (OUTEN Voltage Decreasing) (Note 7)                              | $V_{OTDD}$            | 1.55 | 1.70 | 1.85 | V                |

| OUTPUT SECTIONS (G1, G2)                                                                                   |                       |      |      |      |                  |

| Source Resistance ( $V_{\text{sense}} = 2.0 \text{ V}, V_{\text{G}} = P_{V_{\text{CC}}} - 1.0 \text{ V}$ ) | R <sub>OH</sub>       | _    | 0.5  | _    | Ω                |

| Sink Resistance (V <sub>sense</sub> = 0 V, V <sub>G</sub> = 1.0 V)                                         | $R_{OL}$              | -    | 0.5  | _    |                  |

| Output Voltage with OUTEN Reset (I <sub>sink</sub> = 1.0 mA)                                               | V <sub>OL</sub>       | _    | 0.1  | 0.5  | V                |

| Output Voltage Rise Time (C <sub>L</sub> = 10 nF, T <sub>J</sub> = 25°C)                                   | t <sub>r</sub>        | -    | 70   | 140  | ns               |

| Output Voltage Fall Time (C <sub>L</sub> = 10 nF, T <sub>J</sub> = 25°C)                                   | t <sub>f</sub>        | -    | 70   | 140  | ns               |

| G1, G2 Non–Overlap Time (C <sub>L</sub> = 10 nF, T <sub>J</sub> = 25°C)                                    | t <sub>NOL</sub>      | 30   | 150  | 210  | ns               |

| TOTAL DEVICE                                                                                               |                       |      |      |      |                  |

| Minimum Operating Voltage After Turn-OnR <sub>VCC</sub> Decreasing)                                        | P <sub>V</sub> CC min | 10.8 | _    | _    | V                |

| Minimum Operating Voltage After Turn-On (V <sub>CC</sub> Decreasing)                                       | V <sub>CC min</sub>   | 3.0  | -    | 4.25 | V                |

| V <sub>CC</sub> Current (Note 8) (OUTEN and P <sub>VCC</sub> open,                                         | I <sub>CC</sub>       | -    | 3.7  | 8.0  | mA               |

| VID0, 1, 2, 3, 4 Floating)                                                                                 |                       |      |      |      |                  |

| P <sub>VCC</sub> Current (OUTEN = 5.0 V, VID0, 1, 2, 3, 4 Open,P <sub>VCC</sub> = 12 V)                    | P <sub>l</sub> cc     | -    | 15   | _    | mA               |

- NOTES: 1. Maximum package power dissipation limits must be observed.

2. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

3. VID1, VID3, VID4 = logic 0, and VID0, VID2 = logic 1.

4. V<sub>sense</sub> is provided from a low impedance voltage source or shorted to the output voltage.

5. Under a typical soft current limit, the net soft-start discharge current will be 90 μA (I<sub>SSIL</sub>) 10 μA (I<sub>chg</sub>) = 80 μA. The softstart sink to source current ratio is designed to be 9:1.

6 Sense (Pin 6) = 5.0 V, Comp (Pin 10) open, VID4, VID2, VID1, VID0 = 1.0, VID3 = 0.

7. OUTEN is internally pulled low if VID0, 1, 2, 3, and 4 are floating.

8 Due to internal pull-up resistors, there will be an additional 0.5 mA per pin if any of the VID0, 1, 2, 3 or 4 pins are pulled low.

- 8. Due to internal pull-up resistors, there will be an additional 0.5 mA per pin if any of the VID0, 1, 2, 3, or 4 pins are pulled low.

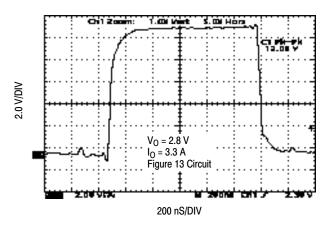

Figure 1. Output Drive Waveform

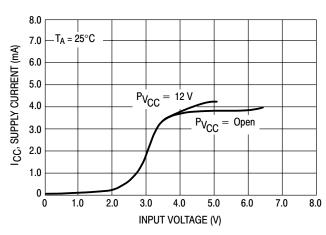

Figure 2. 5.0 V Supply Current

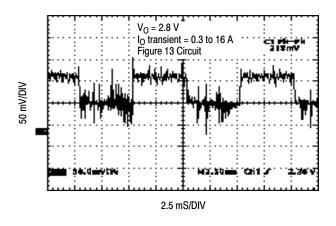

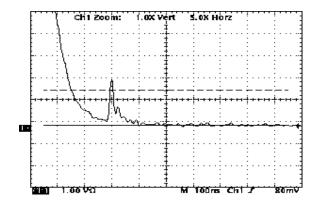

Figure 3. Error Amplifier Transient Response

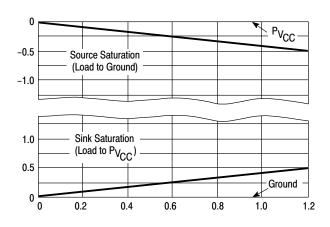

Figure 4. Drive Output Source/Sink Saturation Voltage versus Load Current

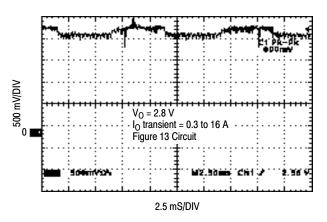

Figure 5. Feedback Circuit Load Transient Response

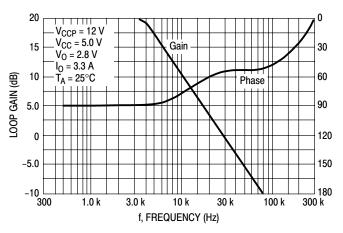

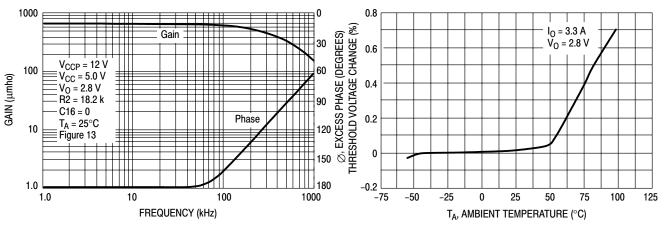

Figure 6. Feedback Loop Gain and Phase versus Frequency

Figure 7. Drive Output Source/Sink Saturation Voltage versus Load Current

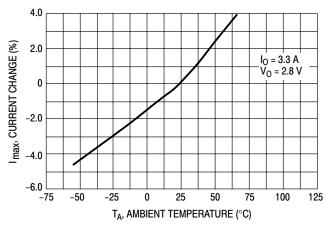

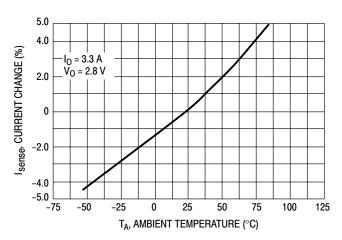

Figure 8. Feedback Threshold Voltage versus Temperature

Figure 9. I<sub>max</sub> Current versus Temperature

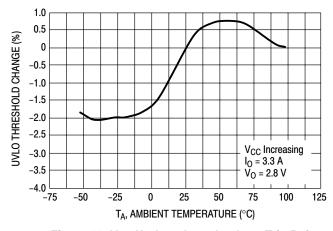

Figure 10. V<sub>sense</sub> Current Source versus Temperature

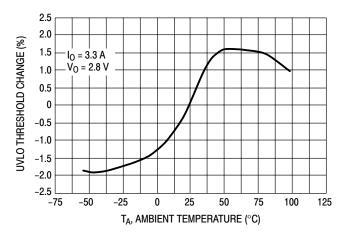

Figure 11. V<sub>CC</sub> Undervoltage Lockout Trip Point versus Temperature

Figure 12. Oscillator Frequency versus Temperature

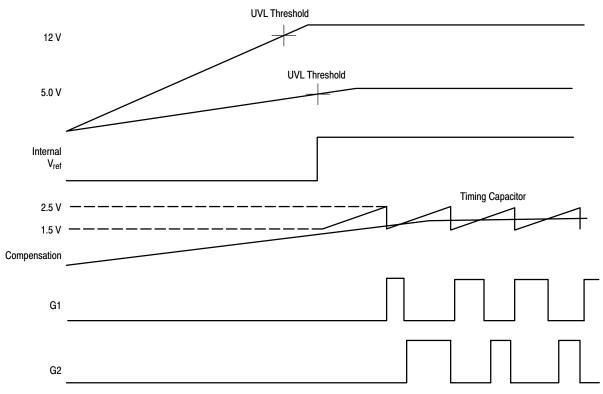

Figure 14. Timing Diagram

#### **OPERATING DESCRIPTION**

The MC33470 is a monolithic, fixed frequency power switching regulator specifically designed for dc-to-dc converter applications which provide a precise supply voltage for state of the art processors. The MC33470 operates as fixed frequency, voltage mode regulator containing all the active functions required to directly implement digitally programmable step-down synchronous rectification with a minimum number of external components.

#### Oscillator

The oscillator frequency is internally programmed to 300 kHz. The charge to discharge ratio is controlled to yield a 95% maximum duty cycle at the switch outputs. During the fall time of the internal sawtooth waveform, the oscillator generates an internal blanking pulse that disables the G1 output switching MOSFET. The internal sawtooth waveform has a nominal peak voltage of 2.5 V and a valley voltage of 1.5 V.

#### **Pulse Width Modulator**

The pulse width modulator consists of a comparator with the oscillator ramp voltage applied to the noninverting input, while the error amplifier output is applied to the inverting input. Output switch conduction is initiated when the ramp waveform is discharged to the valley voltage. As the ramp voltage increases to a voltage that exceeds the error amplifier output, the latch resets, terminating output G1 MOSFET conduction, and turning on output G2 MOSFET,

for the duration of the oscillator ramp. This PWM/latch combination prevents multiple output pulses during a given oscillator cycle.

The sense voltage input at Pin 6 is applied to the noninverting inputs of a pair of high speed comparators. The high speed comparators' inverting inputs are tied 0.96 x  $V_{ref}$  and 1.04 x  $V_{ref}$ , respectively, to provide an optimum response to load changes. When load transients which cause the output voltage to fall outside a  $\pm 4\%$  regulation window occur, the high speed comparators override the PWM comparator to force a zero or maximum duty cycle operating condition until the output voltage is once again within the linear window.

When voltages are initially provided to the supply pins,  $V_{CC}$  and  $P_{V_{CC}}$ , undervoltage lockout circuits monitor each of the supply voltage levels. Both G1 and G2 output pins are held low until the  $V_{CC}$  pin voltage exceeds 4.0 V and the  $P_{V_{CC}}$  pin voltage exceeds 9.0 V.

#### **Error Amplifier and Voltage Reference**

The error amplifier is a transconductance type amplifier, having a nominal transconductance of 800  $\mu$ mho. The transconductance has a negative temperature coefficient. Typical transconductance is 868  $\mu$ mho at 0°C and 620  $\mu$ mho at 125°C junction temperature. The amplifier has a cascode output stage which provides a typical 3.0 Mega–Ohms of

impedance. The typical error amplifier dc voltage gain is 67 dB.

External loop compensation is required for converter stability. Compensation components may be connected from the compensation pin to ground. The error amplifier input is tied to the sense pin which also has an internal  $20~\mu A$  current source to ground. The current source is intended to provide a 24~mV offset when an external 1.2~k resistor is placed between the output voltage and the sense pin. The 24~mV offset voltage is intended to allow a greater dynamic load regulation range within a given specified tolerance for the output voltage. The offset may be increased by increasing the resistor value. The offset can be eliminated by connecting the sense pin directly to the regulated output voltage.

The voltage reference consists of an internal, low temperature coefficient, reference circuit with an added offset voltage. The offset voltage level is the output of the digital–to–analog converter. Control bits VID0 through VID4 control the amount of offset voltage which sets the value of the voltage reference, as shown in Table 1. The VID0–4 input bits each have internal 10 k pullup resistances. Therefore, the reference voltage, and the output voltage, may be programmed by connecting the VID pins to ground for logic "0" or by an open for a logic "1". Typically, a logic "1" will be recognized by a voltage  $> 0.67 \ x \ V_{CC}$ . A logic "0" is a voltage  $< V_{CC}/3$ .

#### **MOSFET Switch Outputs**

The output MOSFETs are designed to switch a maximum of 18 V, with a peak drain current of 2.0 A. Both G1 and G2 output drives are designed to switch N-channel MOSFETs. Output drive controls to G1 and G2 are phased to prevent cross conduction of the internal IC output stages. Output dead time is typically 100 nanoseconds between G1 and G2 in order to minimize cross conduction of the external switching MOSFETs.

#### **Current Limit and Soft-Start Controls**

The soft–start circuit is used both for initial power application and during current limit operation. A single external capacitor and an internal 10  $\mu$ A current source control the rate of voltage increase at the error amplifier output, establishing the circuit turn on time. The G1 output will increase from zero duty cycle as the voltage across the soft–start capacitor increases beyond about 0.5 V. When the soft–start capacitor voltage has reached about 1.5 V, normal duty cycle operation of G1 will be allowed.

An overcurrent condition is detected by the current limit amplifier. The current limit amplifier is activated whenever the G1 output is high. The current limit amplifier compares the voltage drop across the external MOSFET driven by G1,

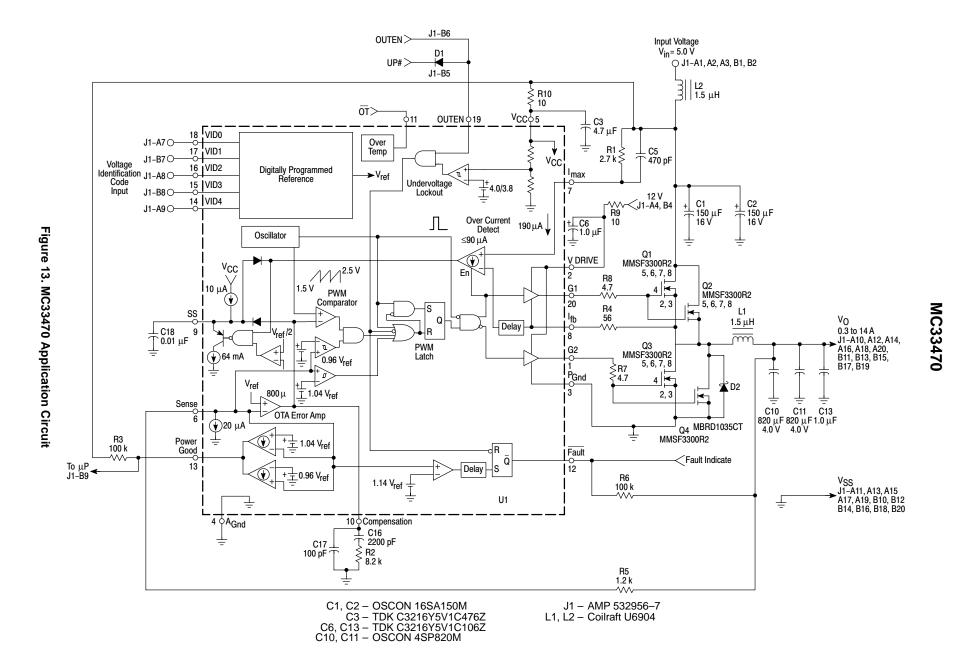

as measured at the  $I_{FB}$  pin, with the voltage at the  $I_{max}$  pin. Because the  $I_{max}$  pin draws 190  $\mu A$  of input current, the overcurrent threshold is programmed by an external resistor. Referring to Figure 13, the current limit resistor value can be determined from the following equation:

$$R1 = \frac{[(I_{L(max)})(R_{DS(on)})]}{(I_{max})}$$

where:

$$I_{L(max)} = \frac{I_O + I_{ripple}}{2}$$

I<sub>O</sub> = Maximum load current I<sub>ripple</sub> = Inductor peak to peak ripple current

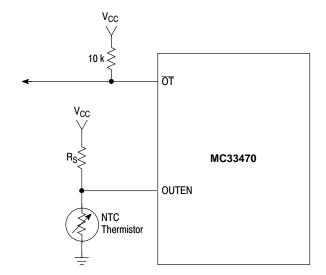

### **OUTEN Input and OT Output Pins**

On and off control of the MC33470 may be implemented with the OUTEN pin. A logic "1" applied the OUTEN pin, where a logic "1" is above 2.0 V, will allow normal operation of the MC33470. The OUTEN pin also has multiple thresholds to provide over temperature protection. An negative temperature coefficient thermistor can be connected to the OUTEN pin, as shown in Figure 15. Together with R<sub>S</sub>, a voltage divider is formed. The divider voltage will decrease as the thermistor temperature increases. Therefore, the thermistor should be mounted to the hottest part on the circuit board. When the OUTEN voltage drops below 2.0 V typically, the MC33470 OT pin open collector output will switch from a logic "1" to a logic "0", providing a warning to the system. If the OUTEN voltage drops below 1.7 V, both G1 and G2 output driver pins are latched to a logic "0" state.

Figure 15. OUTEN/OT Overtemperature Function

#### **APPLICATIONS INFORMATION**

#### **Design Example**

Given the following requirements, design a switching dc-to-dc converter:

$$V_{CC}$$

= 5.0 V

$V_{CCP}$  = 12 V

$V_{ID4-0 \text{ bits}}$  = 10111 – Output Voltage = 2.8 V

Output current = 0.3 A to 14 A

Efficiency  $\geq 80\%$  at full load

Output ripple voltage ≈ 1% of output voltage

1. Choose power MOSFETs.

In order to meet the efficiency requirement, MOSFETs should be chosen which have a low value of  $R_{DS(on)}$ . However, the threshold voltage rating of the MOSFET must also be greater than 1.5 V, to prevent turn on of the synchronous rectifier MOSFETs due to dv/dt coupling through the Miller capacitance of the MOSFET drain—to—source junction. Figure 16 shows the gate voltage transient due to this effect.

In this design, choose two parallel MMSF3300 MOSFETs for both the main switch and the synchronous rectifier to maximize efficiency.

2.

$$D \approx V_O/V_{in} = 2.8/5.0 = 0.56$$

3. Inductor selection

In order to maintain continuous mode operation at 10% of full load current, the minimum value of the inductor will be:

$$L_{min} = (V_{in} - V_{O})(DTs)/(2I_{O min})$$

$$= (5 - 2.8)(0.56 \times 3.3 \ \mu s)/(2 \times 1.4 \ A) = 1.45 \ \mu H$$

Coilcraft's U6904, or an equivalent, provides a surface mount 1.5  $\mu H$  choke which is rated for full load current.

4. Output capacitor selection

$V_{ripple} \approx \Delta I_L x ESR$ , where ESR is the equivalent series resistance of the output capacitance. Therefore:

$$ESR_{max} = V_{ripple}/\Delta I_L = 0.01 \times 2.8 \text{ V}/1.4 \text{ A} = 0.02 \Omega$$

The AVX TPS series of tantalum chip capacitors may be chosen. Or OSCON capacitors may be used if leaded parts are acceptable. In this case, the output capacitance consists of two parallel 820  $\mu F, 4.0$  V capacitors. Each capacitor has a maximum specified ESR of 0.012  $\Omega$

#### 5. Input Filter

As with all buck converters, input current is drawn in pulses. In this case, the current pulses may be 14 A peak. If a 1.5  $\mu$ H choke is used, two parallel OSCON 150  $\mu$ F, 16 V capacitors will provide a filter cutoff frequency of 7.5 kHz.

6. Feedback Loop Compensation

The corner frequency of the output filter with  $L=1.5~\mu H$  and  $C_o=1640~\mu F$  is 3.2 kHz. In addition, the ESR of each output capacitor creates a zero at:

$f_z=1/(2\pi~C~ESR)=1/(2\pi~x~820~\mu F~x~0.012)=16.2~kHz$  The dc gain of the PWM is: Gain =  $V_{in}/V_{pp}=5/1=5.0.$  Where  $V_{pp}$  is the peak–to–peak sawtooth voltage across the internal timing capacitor. In order to make the feedback loop as responsive as possible to load changes, choose the unity gain frequency to be 10% of the switching frequency, or 30 kHz. Plotting the PWM gain over frequency, at a frequency of 30 kHz the gain is about –16.5 dB = 0.15. Therefore, to have a 30 kHz unity gain loop, the error amplifier gain at 30 kHz should be 1/0.15=6.7. Choose a design phase margin for the loop of  $60^\circ$ . Also, choose the error amp type to be an integrator for best dc regulation performance. The phase boost needed by the error amplifier is then  $60^\circ$  for the desired phase margin. Then, the following calculations can be made:

$$\begin{split} &k = tan \; [Boost/2 + 45^\circ] = tan \; [60/2 + 45] = 3.73 \\ &Error \; Amp \; zero \; freq = f_c/K = 30 \; kHz/3.73 = 8.0 \; kHz \\ &Error \; Amp \; pole \; freq = K_{fc} = 3.73 \; x \; 30 \; kHz = 112 \; kHz \\ &R2 = Error \; Amp \; Gain/G_m = 6.7/800 \; \mu = 8.375 \; k - use \; an \\ &8.2 \; k \; standard \; value \\ &C16 = 1/(2\pi \; R2 \; f_z) = 1/(2\pi \; x \; 8.2 \; k \; x \; 8.0 \; kHz) \\ &= 2426 \; pF - use \; 2200 \; pF \\ &C17 = 1/(2\pi \; R2 \; f_p) = 1/(2\pi \; x \; 8.2 \; k \; x \; 112 \; kHz) \\ &= 173 \; pF - \; use \; 100 \; pF \end{split}$$

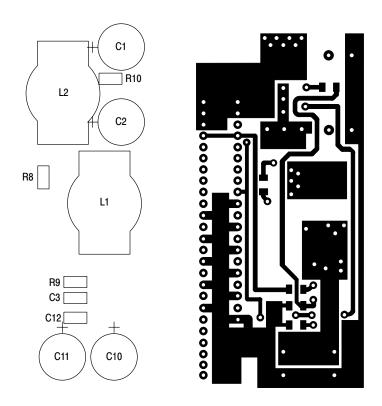

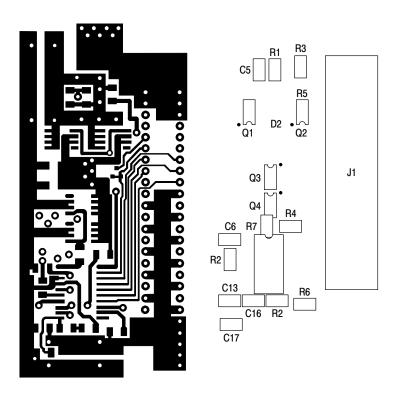

The complete design is shown in Figure 13. The PC board top and bottom views are shown in Figures 17 and 18.

Figure 16. Voltage Coupling Through Miller Capacitance

## PIN FUNCTION DESCRIPTION

| Pin | Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | G2                | This is a high current dual totem pole output Gate Drive for the Lower, or rectifier, N–channel MOSFET. Its output swings from ground to P <sub>VCC</sub> . During initial power application, both G2 and                                                                                                                                                                                                                                                                                                            |

|     |                   | G1 are held low until both V <sub>CC</sub> and P <sub>VCC</sub> have reached proper levels.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2   | P <sub>VCC</sub>  | This is a separate power source connection for driving N–channel MOSFETs from the G1 and G2 outputs. It may be connected to 12 V.                                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | P <sub>Gnd</sub>  | This is a separate power ground return that is connected back to the power source. It is used to reduce the effects of switching transient noise on the control circuitry.                                                                                                                                                                                                                                                                                                                                           |

| 4   | A <sub>Gnd</sub>  | This pin is the ground for the control circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5   | V <sub>CC</sub>   | This pin is the positive supply of the control IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6   | Sense             | This pin is used for feedback from the output of the power supply. It has a 20 $\mu$ A current source to ground which can be used to provide offset in the converter output voltage.                                                                                                                                                                                                                                                                                                                                 |

| 7   | I <sub>max</sub>  | This pin sets the current limit threshold. 190 $\mu$ A must be sourced into the pin. The external resistor is determined from the following equation: R = ([R <sub>DS(on)</sub> ] [I <sub>LIM</sub> ]/[190 $\mu$ A])                                                                                                                                                                                                                                                                                                 |

| 8   | I <sub>FB</sub>   | This pin has two functions. First, it provides cycle—by—cycle current limiting. Second, if the current is excessive, this pin will reinitiate a soft—start cycle. If the voltage at the $I_{FB}$ pin drops below the voltage at the $I_{max}$ pin when G1 is on, the controller will go into current limit. The current limit circuit can be disabled by floating the $I_{max}$ pin and shorting the $I_{FB}$ pin to $V_{CC}$ .                                                                                      |

| 9   | SS                | This is the soft–start pin. A capacitor at this pin, in conjunction with a 10 $\mu$ A internal current source, sets the soft–start time. During moderate overload (current limit with V <sub>O</sub> > 50% of the set value), the soft–start capacitor will be discharged by an internal 90 $\mu$ A current source in order to reduce the duty cycle of G1. During hard current limit (current limit with V <sub>O</sub> < 50% of set value), the soft–start capacitor will be discharged by a 64 mA current source. |

| 10  | Comp              | This pin is provided for compensating the error amp for poles and zeros encountered in the power supply system, mostly the output LC filter.                                                                                                                                                                                                                                                                                                                                                                         |

| 11  | ОТ                | This is the over temperature fault pin. $\overline{\text{OT}}$ is an open drain output that will be pulled low if the OUTEN pin is less than 2.0 V.                                                                                                                                                                                                                                                                                                                                                                  |

| 12  | Fault             | This pin indicates a fault condition. Fault is an open drain output that switches low if V <sub>O</sub> exceeds 115% of its set value. Once triggered, the controller will remain in this state until the power supply is recycled or the OUTEN pin is toggled.                                                                                                                                                                                                                                                      |

| 13  | P <sub>wrgd</sub> | This pin is an open drain output which indicates that $V_O$ is properly regulated. A high level on $P_{wrgd}$ indicates that $V_O$ is within $\pm 4\%$ of its set value for more than 400 $\mu$ s. $P_{wrgd}$ will switch low if $V_O$ is outside $\pm 4\%$ for more than 100 $\mu$ s.                                                                                                                                                                                                                               |

| 14  | VID4              | Voltage ID pin. This CMOS–compatible input programs the output voltage as shown in Table 2. This pin has an internal 10 k pull—up resistor to $V_{\rm CC}$ .                                                                                                                                                                                                                                                                                                                                                         |

| 15  | VID3              | Voltage ID pin. This CMOS–compatible input programs the output voltage as shown in Table 2. This pin has an internal 10 k pull–up resistor to $V_{\rm CC}$ .                                                                                                                                                                                                                                                                                                                                                         |

| 16  | VID2              | Voltage ID pin. This CMOS–compatible input programs the output voltage as shown in Table 2. This pin has an internal 10 k pull–up resistor to $V_{\rm CC}$ .                                                                                                                                                                                                                                                                                                                                                         |

| 17  | VID1              | Voltage ID pin. This CMOS–compatible input programs the output voltage as shown in Table 2. This pin has an internal 10 k pull–up resistor to $V_{\rm CC}$ .                                                                                                                                                                                                                                                                                                                                                         |

| 18  | VID0              | Voltage ID pin. This CMOS–compatible input programs the output voltage as shown in Table 2. This pin has an internal 10 k pull–up resistor to $V_{\rm CC}$ .                                                                                                                                                                                                                                                                                                                                                         |

| 19  | OUTEN             | This is the on/off control pin. A CMOS–compatible logic "1" allows the controller to operate. This pin can also be used as a temperature sensor to trigger the $\overline{OT}$ pin (when OUTEN drops below 2.0 V $\overline{OT}$ pulls low). When OUTEN drops below 1.7 V for longer than 50 $\mu$ s, the controller will shut down.                                                                                                                                                                                 |

| 20  | G1                | This is a high current dual totem pole output Gate Drive for the Upper, or switching, N–channel MOSFET. Its output swings from ground to $P_{VCC}$ . During initial power application, both G2 and G1 are held low until both $V_{CC}$ and $P_{VCC}$ have reached proper levels.                                                                                                                                                                                                                                     |

**Table 1. Voltage Identification Code**

| VID4 | VID3 | VID2 | VID1 | VID0 | v <sub>o</sub> |

|------|------|------|------|------|----------------|

| 0    | 1    | 1    | 1    | 1    | -              |

| 0    | 1    | 1    | 1    | 0    | -              |

| 0    | 1    | 1    | 0    | 1    | -              |

| 0    | 1    | 1    | 0    | 0    |                |

| 0    | 1    | 0    | 1    | 0    | -              |

| 0    | 1    | 0    | 0    | 1    | _              |

| 0    | 1    | 0    | 0    | 0    | -              |

| 0    | 0    | 1    | 1    | 1    | _              |

| 0    | 0    | 1    | 1    | 0    | -              |

| 0    | 0    | 1    | 0    | 1    | 1.8            |

| 0    | 0    | 1    | 0    | 0    | 1.85           |

| 0    | 0    | 0    | 1    | 1    | 1.9            |

| 0    | 0    | 0    | 1    | 0    | 1.95           |

| 0    | 0    | 0    | 0    | 1    | 2.0            |

| 0    | 0    | 0    | 0    | 0    | 2.05           |

| 1    | 1    | 1    | 1    | 1    | No CPU         |

| 1    | 1    | 1    | 1    | 0    | 2.1            |

| 1    | 1    | 1    | 0    | 1    | 2.2            |

| 1    | 1    | 1    | 0    | 0    | 2.3            |

| 1    | 1    | 0    | 1    | 1    | 2.4            |

| 1    | 1    | 0    | 1    | 0    | 2.5            |

| 1    | 1    | 0    | 0    | 1    | 2.6            |

| 1    | 1    | 0    | 0    | 0    | 2.7            |

| 1    | 0    | 1    | 1    | 1    | 2.8            |

| 1    | 0    | 1    | 1    | 0    | 2.9            |

| 1    | 0    | 1    | 0    | 1    | 3.0            |

| 1    | 0    | 1    | 0    | 0    | 3.1            |

| 1    | 0    | 0    | 1    | 1    | 3.2            |

| 1    | 0    | 0    | 1    | 0    | 3.3            |

| 1    | 0    | 0    | 0    | 1    | 3.4            |

| 1    | 0    | 0    | 0    | 0    | 3.5            |

**Table 2. Connector Pin Function**

| PIN | ROW A               | ROW B               |

|-----|---------------------|---------------------|

| 1   | 5.0 V <sub>in</sub> | 5.0 V <sub>in</sub> |

| 2   | 5.0 V <sub>in</sub> | 5.0 V <sub>in</sub> |

| 3   | 5.0 V <sub>in</sub> | Reserved            |

| 4   | 12 V <sub>in</sub>  | 12 V <sub>in</sub>  |

| 5   | Reserved            | UP#                 |

| 6   | I <sub>share</sub>  | OUTEN               |

| 7   | VID0                | VID1                |

| 8   | VID2                | VID3                |

| 9   | VID4                | P <sub>wrgd</sub>   |

| 10  | V <sub>CCP</sub>    | V <sub>SS</sub>     |

| 11  | V <sub>SS</sub>     | V <sub>CCP</sub>    |

| 12  | V <sub>CCP</sub>    | V <sub>SS</sub>     |

| 13  | V <sub>SS</sub>     | V <sub>CCP</sub>    |

| 14  | V <sub>CCP</sub>    | V <sub>SS</sub>     |

| 15  | V <sub>SS</sub>     | V <sub>CCP</sub>    |

| 16  | V <sub>CCP</sub>    | V <sub>SS</sub>     |

| 17  | V <sub>SS</sub>     | V <sub>CCP</sub>    |

| 18  | V <sub>CCP</sub>    | V <sub>SS</sub>     |

| 19  | V <sub>SS</sub>     | V <sub>CCP</sub>    |

| 20  | V <sub>CCP</sub>    | V <sub>SS</sub>     |

Figure 17. PC Board Top View

Figure 18. PC Board Bottom View

## **PACKAGE DIMENSIONS**

#### **DW SUFFIX** PLASTIC PACKAGE CASE 751D-05 ISSUE F

- NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

3. DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

5. DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       |  |

|-----|-------------|-------|--|

| DIM | MIN         | MAX   |  |

| Α   | 2.35        | 2.65  |  |

| A1  | 0.10        | 0.25  |  |

| В   | 0.35        | 0.49  |  |

| С   | 0.23        | 0.32  |  |

| D   | 12.65       | 12.95 |  |

| E   | 7.40        | 7.60  |  |

| е   | 1.27 BSC    |       |  |

| Н   | 10.05       | 10.55 |  |

| h   | 0.25        | 0.75  |  |

| L   | 0.50        | 0.90  |  |

| θ   | 0 °         | 7 °   |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

**JAPAN**: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031

Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.