# **1** AMD-K5<sup>™</sup> Processor Features

- Four-issue superscalar core with six parallel execution units arranged in a five-stage pipeline

- 16-Kbyte, dual-tagged, four-way, set-associative instruction cache

- 8-Kbyte, dual-tagged, dual-ported with four banks, four-way set-associative, writeback data cache

- Full, out-of-order speculative execution and completion

- Dynamic cache line-oriented branch prediction with 1-Kbyte branch predictions and low 3-cycle branch mispredict penalty

- Integrated, high-performance floating-point unit (FPU) with low-latency add/multiply and single-cycle issue

- Static clock control with Phase Lock Loop (PLL) circuitry

- 3.3-V operation and System Management Mode (SMM) for lower power consumption

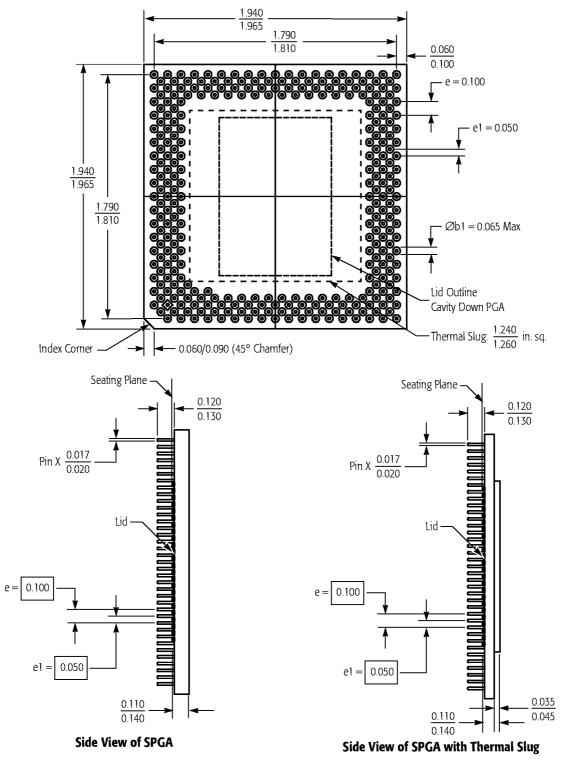

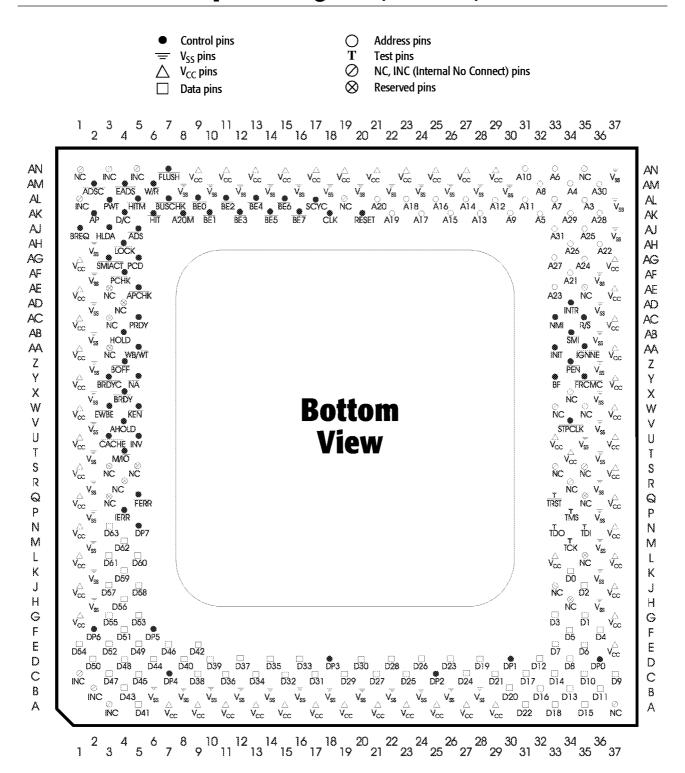

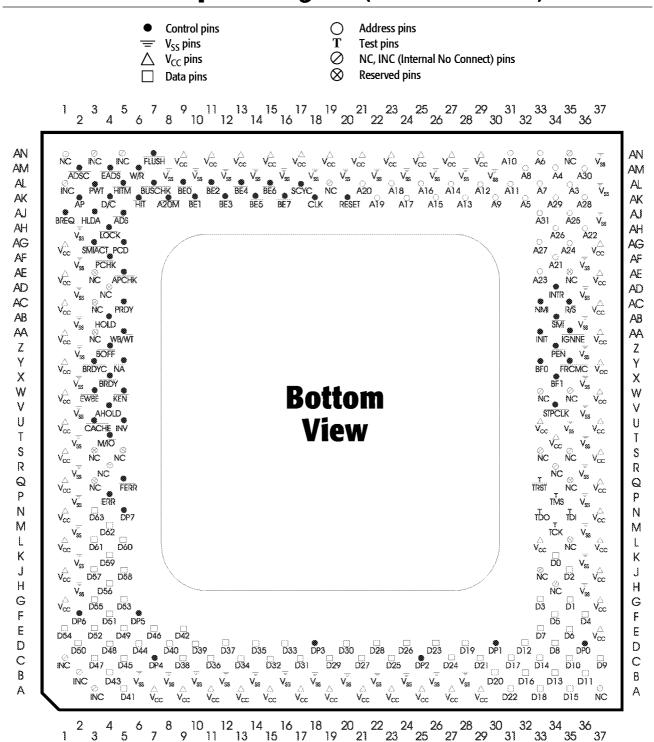

- 64-bit Pentium-compatible bus and system interface in a 296-pin SPGA package

- Compatible with existing Pentium (P54C) support infrastructure and system designs

- Fully compatible with the Microsoft® Windows® operating systems and the large installed library of x86 software

# 1.1 Redefining the Next Generation

AMD continues to bring superior, high-performance processor solutions to the personal computer market. The AMD-K5 processor offers superior price/performance value over other 5th-generation processors—making it an ideal solution for main-stream desktop computers. Compatible with the entire installed library of x86 software, the AMD-K5 processor is a superior engine for the Microsoft Windows operating systems.

The AMD-K5 processor uses an independently developed "superscalar RISC-based design" manufactured in AMD's 0.35-micron complementary metal-oxide semiconductor (CMOS) process. The design stems from a rich history of experience in RISC and x86 technology, providing a solid foundation for the development of our proprietary 4.3-million-transistor AMD-K5 processor.

# 1.2 High-Performance Design

The superscalar RISC design techniques provide next-generation performance levels and the power to run complex 32-bit operating systems and applications. The AMD-K5 processor features a four-issue superscalar core that incorporates dynamic branch prediction and out-of-order speculative execution. While other 5th-generation processors feature a two-issue core, the AMD-K5 processor's RISC core is four-issue.

# 1.3 Compatibility

The AMD-K5 processor's compatibility is established using a rigorous testing procedure that begins with software simulation before the design is first committed to silicon. Throughout the design and manufacturing process, industry-standard tools and systems are used for compatibility testing.

Extended compatibility and qualification testing are provided by industry-leading personal computer and chip set manufacturers. Testing culminates with certification from XXCAL, Inc., an independent third-party testing lab. This combination of differentiating features is responsible for the AMD-K5 processor's overall design and performance advantages.

Compatibility with the Microsoft Windows operating system and the immense library of x86 software furthers these advantages, and is the foundation of the AMD-K5 processor's leading-edge solution.

# **Revision History**

| Date      | Revision | Description                                                                                          |

|-----------|----------|------------------------------------------------------------------------------------------------------|

|           |          | The PR166 OPN added to Ordering Information in Section 3 on page 5.                                  |

|           |          | The valid combinations are updated in the Ordering Information in Section 3 on page 5.               |

|           |          | Model 2 added to the CPU Identification in Section 5 on page 12.                                     |

|           |          | P-Rating information added to the CPU Identification in Section 5 on page 12.                        |

|           | F        | Manufacturer in JTAG ID code changed to bits 11-1 in CPU Identification in Section 5 on page 12.     |

| Jan. 1997 |          | 1.75 multiplier added to the BF1-BF0 pin description in Signal Descriptions in Section 7 on page 14. |

|           |          | New data cache write allocate information added beginning on page 34                                 |

|           |          | Pipelining information added beginning on page 47.                                                   |

|           |          | $V_{\text{CC}}$ changes in Operating Ranges on page 57.                                              |

|           |          | $I_{\text{CC}}$ updated in Table 14 on page 58.                                                      |

|           |          | The package thermal specifications on page 82 are updated for new models and $I_{\text{CC}}$ specs.  |

|           |          | All references to model 1 are changed to models 1 and 2.                                             |

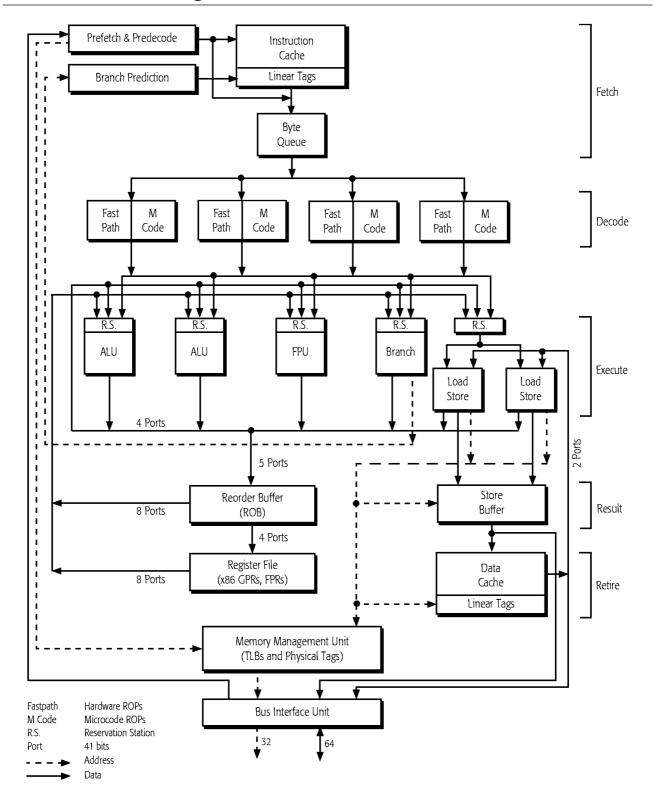

# 2 Block Diagram

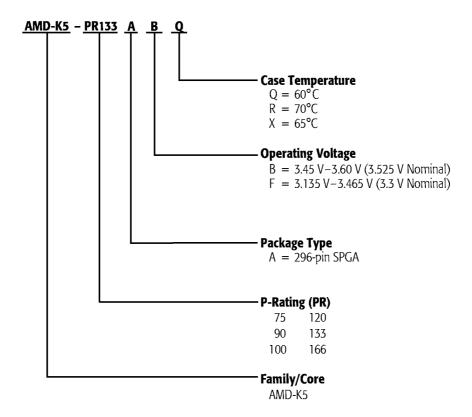

# **3 Ordering Information**

# **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

#### **Valid Combinations**

| OPN             | Package Type | Operating Voltage | Case Temperature |

|-----------------|--------------|-------------------|------------------|

| AMD-K5-PR166ABX | 296-pin SPGA | 3.45 V-3.60 V     | 65°C             |

| AMD-K5-PR133ABR | 296-pin SPGA | 3.45 V-3.60 V     | 70°C             |

| AMD-K5-PR133ABQ | 296-pin SPGA | 3.45 V-3.60 V     | 60°C             |

| AMD-K5-PR120ABR | 296-pin SPGA | 3.45 V-3.60 V     | 70°C             |

| AMD-K5-PR100ABQ | 296-pin SPGA | 3.45 V-3.60 V     | 60°C             |

| AMD-K5-PR90ABQ  | 296-pin SPGA | 3.45 V-3.60 V     | 60°C             |

| AMD-K5-PR75ABR  | 296-pin SPGA | 3.45 V-3.60 V     | 70°C             |

#### Notes:

Valid combinations lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

# 4 Architectural Introduction

The x86 architecture is the dominant standard for the personal computer marketplace. However, maintaining backwards compatibility with previous generations of x86 processors carries several inherent limitations associated with the x86 architecture: variable-length instruction set, fewer general-purpose registers, and complex addressing modes. The AMD-K5 processor overcomes these burdens by providing superscalar architecture that incorporates innovative technology: instruction predecoding, improved cache architecture, branch prediction with speculative execution, a superscalar RISC core, out-of-order execution, and register renaming.

# 4.1 Superscalar RISC Core

The AMD-K5 processor's superscalar RISC core consists of six execution units: two arithmetic logic units (ALU), two load/ store units, one branch unit, and one floating-point unit (FPU). This superscalar core is fully decoupled from the x86 bus through the conversion of variable-length x86 instructions into simple, fixed-length RISC operations (ROPs) that are easier to handle and execute faster. Once the x86 instruction has been converted, a dispatcher issues four ROPs at a time to the superscalar core. The processor's superscalar core can execute at a peak rate of six ROPs per cycle. The superscalar core supports data forwarding and data bypassing to immediately forward the results of an execution to successive instructions. This eliminates the delay of writing the results to output registers or memory and reading them back to the instruction needing the results.

# 4.2 Out-of-Order Execution

The AMD-K5 processor implements out-of-order execution to eliminate delays due to pipeline dependencies. Each execution unit has two reservation stations that hold ROPs prior to execution (except the FPU, which has one reservation station). ROPs can be issued out of order from the reservation stations and executed out of order. Some execution units will empty their reservation stations before others. Since each execution

unit can operate independently, other units can continue execution when one or more units are stalled. A 16-entry reorder buffer keeps track of the original instruction sequence and ensures that the results are retired in program order.

# 4.3 Register Renaming

The x86 architecture has only eight general-purpose registers. This significantly increases register reuse (loads and stores) and register dependencies. The register reuse is addressed with multiple load/store execution units and a dual-ported data cache. The AMD-K5 processor uses register renaming to overcome register dependencies. Multiple logical registers for each physical register allow execution units to use the same physical name registers simultaneously.

## 4.4 64-Bit Data Bus Interface Unit

The AMD-K5 processor uses a 64-bit data bus that provides higher throughput and support for 64-bit data paths, and a cache/burst-oriented line refill for loading the processor's internal separate instruction and data caches. As code and data enter the bus interface unit, the internal cache refills continually as fast as five clock cycles per cache line. The enhanced bandwidth of the processor's data bus and the continuous cache refill process reduces processing delays and supports superior processor and overall system performance.

# 4.5 Innovative x86 Instruction Predecoding

While processing variable-length instructions is manageable in single-issue 4th-generation and dual-issue 5th-generation CPUs, only the AMD-K5 processor employs the necessary innovative techniques to issue as many as four x86 instructions per clock cycle.

Every byte of code that enters the AMD-K5 processor is tagged with associated predecode information that identifies the x86 instruction boundaries and enables multiple x86 instructions (varying in length from 8 to 120 bits) to be aligned. Once aligned, the instructions are assigned issue positions for the most efficient instruction processing—contributing to the pro-

cessor's high performance. In addition to indicating where the x86 instruction begins and ends, the predecode information identifies the position of the opcode and the number of simple RISC-like operations (ROPs) the individual x86 instruction requires for later translation.

After the x86 instructions are predecoded, they are loaded into the instruction cache. When accessed from the instruction cache, the *speculative* instructions (x86 instructions from a predicted branch stream) are pushed into the byte queue and await further decoding. The byte queue not only contains the x86 instructions but also the associated predecode tags that mark each instruction's position and operation type.

# 4.6 Cache Architecture

Much of the AMD-K5 processor's performance advantage can be credited to the processor's instruction cache architecture and its ability to feed the processor core. Using separate instruction and data caches eliminates the internal conflicts over simultaneous instruction cache access and x86 loads and stores. The processor's 16-Kbyte instruction cache is dualtagged, avoiding the linear-to-physical address translation required to access every entry and allowing faster cache access. In addition, the processor maintains a separate set of physical instruction tags for snooping and aliasing, and through a special protocol, prevents flushing the cache even during Translation Lookaside Buffer (TLB) flushes or context switches.

The processor's instruction cache implements a four-way setassociative structure for maximum cache performance in a given size and maintains branch prediction information with every cache line.

The 8-Kbyte data cache allows two cache lines of data to be accessed simultaneously in a single clock cycle, as long as separate banks within the data cache are accessed. Supporting two accesses per clock enables the data cache to overcome the load/store bottlenecks inherent in the x86 architecture.

The AMD-K5 processor's data cache uses a modified, exclusive, shared, invalid (MESI) protocol to maintain data coherency with other caches in the system and to ensure that a read from

a given memory location returns valid data. Each cache line is assigned one of the four protocol states to identify the status of the information stored in the cache. The writeback cache design updates memory only when necessary. This keeps the system bus free for use by other devices and improves the overall system performance.

# 4.7 Branch Prediction

A branch occurs on average once every seven x86 instructions. When a branch is encountered, the processor predicts which direction the instruction flow will follow. The AMD-K5 processor adds branch prediction information to each instruction cache line in the form of a predicted address tag that indicates the target address of the first branch that is predicted to be taken in the cache line. The processor's dynamic branch prediction mechanism allows for 1024 branch targets and a 75% branch prediction accuracy. Combined with a minimal 3-cycle mispredict penalty, the branch prediction mechanism optimizes the processor's speculative execution of x86 software, such as the Microsoft Windows operating system and associated applications.

The dynamic branch prediction of the processor enables instructions to be fetched and fed into the processor's execution core, eliminating many pipeline bubbles and contributing to the superior performance of the AMD-K5 processor.

# 4.8 Unique x86 Instruction Conversion and Decoding

The logical instruction flow within the AMD-K5 processor continues as up to 32-bytes of predecoded x86 instructions are fetched from the byte queue of the instruction cache and forwarded in order to the decoder.

The processor's decoder converts complex x86 instructions into relatively simple, fast-executing ROPs that are of fixed length and easy to process. Simultaneously, the operands needed to perform the ROPs' operations are fetched from the register file or from the reorder buffer.

At the beginning of the decode process, the decoder scans the x86 instructions and allocates the instructions to the appropriate decode position. This allocation depends on the 5-bit tag given to each x86 instruction during predecode. When the predecoded instruction passes through the AMD-K5 processor's decoder, the number of ROPs needed to equate to the x86 instruction is already known from predecoding, saving valuable processing time.

During allocation, the instruction's pathways are identified. If an x86 instruction requires less than four ROPs for conversion, it is sent immediately to any of the four decode positions (Fastpath). Complex x86 instructions requiring four or more ROPs (or ROP sequences) are transferred to the Microcode ROM (MROM) for conversion.

Once through the decode position, the ROPs are dispatched in parallel to reservation stations that reside in each of the processor's six execution units. A reservation station precedes the input to individual execution units. Each execution unit has a pair of reservation stations.

The processor sends ROPs to the reservation stations in order, but when the ROPs are passed on to the execution units they can be executed out of order because the reservation stations can empty at different times. Out-of-order execution eliminates the need for compiler-specific optimization and reduces dependencies. The ROPs wait in the reservation stations for the execution unit processing to complete and for the needed operands, which come from the register file, the data cache, or are forwarded from other execution units. As an execution unit finishes processing one instruction, it receives another instruction from the reservation station. Using reservation stations in this manner, the processor minimizes instruction stalls due to dependencies on execution resources and allows a higher issue rate to be maintained.

# 4.9 Reorder Buffer

The AMD-K5 processor uses a central reorder buffer—a key to supporting speculative out-of-order execution (issue and completion). The central reorder buffer is used to rename registers, provide subsequent forwarding of requested intermediate

results, recover from mispredictions and exceptions, and hold the relative speculative state.

The processor's 16-entry reorder buffer stores results from x86 instructions that have been speculatively executed at the time a branch was predicted. When ROPs are dispatched to one of the processor's six independent execution units, an entry at the top of the reorder buffer is allocated for each ROP. Up to four entries are allocated simultaneously. The reorder buffer keeps track of the original instruction sequence and ensures that results are retired in program order, writing the results of the executed instruction to the register file. If a branch is mispredicted, the results of the instructions along the mispredicted path are invalidated in the reorder buffer before there is any effect on the x86 registers or memory system.

# 4.10 Register File

A problem with the x86 architecture has been its limited number of general-purpose registers. Fewer registers means frequent reuse of registers, which potentially leads to a reduction in performance. The AMD-K5 CPU utilizes register renaming and avoids this performance reduction.

Because the movement of values between registers and memory locations is unavoidable with the x86 instruction set, a key advantage of the AMD-K5 CPU is its single-cycle load from the data cache. This, in combination with the multiported register file and renaming in the reorder buffer, gives near optimal speculative performance within the constraints of the x86 instruction set.

# 4.11 The Right Combination—Compatibility and Performance

While each feature has a significant function, it is the combination of all features that is responsible for the AMD-K5 processor's overall design and performance advantages. Compatibility with the Microsoft Windows operating system and the immense library of x86 software furthers these advantages, and is the foundation of the AMD-K5 processor's leading-edge solution.

# **5 CPU Identification**

Upon completion of RESET, the DX register contains a component identification. The upper byte of DX (DH) will contain 05h. The lower byte of DX (DL) will contain a CPU model (0h-2h)/stepping identifier (xh).

| CPU ID            |                                 |                                                    |    |              |                 |     |  |  |

|-------------------|---------------------------------|----------------------------------------------------|----|--------------|-----------------|-----|--|--|

| Family ID<br>(DH) | Model ID<br>(DL, top<br>4 bits) | CPU Frequency (MHz)  Bus Speed  Processor P-Rating |    | BF<br>Pin    | BF1-BF0<br>Pins |     |  |  |

|                   | 0                               | 75                                                 | 50 | AMD-K5-PR75  | 1               | N/A |  |  |

|                   |                                 | 90                                                 | 60 | AMD-K5-PR90  | 1               | N/A |  |  |

| 5                 |                                 | 100                                                | 66 | AMD-K5-PR100 | 1               | N/A |  |  |

| )                 | 1                               | 90                                                 | 60 | AMD-K5-PR120 | N/A             | 10  |  |  |

|                   |                                 | 100                                                | 66 | AMD-K5-PR133 | N/A             | 10  |  |  |

|                   | 2                               | 116.7                                              | 66 | AMD-K5-PR166 | N/A             | 00  |  |  |

#### Notes:

This table does not constitute product announcements. Instead, the information in the table represents possible product offerings. AMD will announce actual products based on availability and market demand

The boundary scan test access port (TAP) returns the following information in the device identification register (DIR).

|                           | JTAG ID Code            |                        |                                                    |                             |                |  |  |  |  |

|---------------------------|-------------------------|------------------------|----------------------------------------------------|-----------------------------|----------------|--|--|--|--|

| Version<br>(Bits 31 – 28) | Bond Option<br>(Bit 27) | Unused<br>(Bits 26–24) | Part Number<br>(Bits 23–12)                        | Manufacturer<br>(Bits 11–1) | LSB<br>(Bit 0) |  |  |  |  |

| ×h                        | хb                      | 000b                   | 50xh (Model 0)<br>51xh (Model 1)<br>52xh (Model 2) | 00000000001b                | 1b             |  |  |  |  |

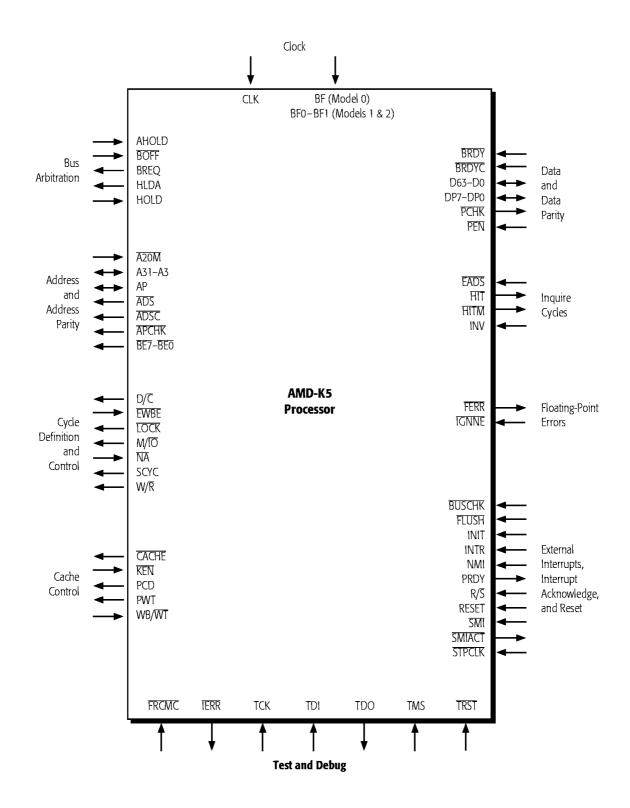

# 6 Logic Symbol Diagram

# **7** Signal Descriptions

#### A31-A5/A4-A3

#### Address Lines

## Input/Output

A31–A3 are used with  $\overline{BE7}$ – $\overline{BE0}$  to form the address bus. These signals are outputs to address memory space, I/O space, and system management memory. A31–A5 are used as inputs for inquire cycles. A4–A3 are not used during the inquire cycle, but must be driven to valid levels. During bus hold, address hold, or back-off, A31–A3 are floated. (See Switching Characteristics  $t_{14}$  and  $t_{15}$ .)

#### A20M Address Bit 20 Mask

### Input

Asserting  $\overline{A20M}$  will mask address bit 20 internally for internal cache accesses or driving memory cycles on the external bus.  $\overline{A20M}$  should be asserted only in Real mode. Its effect is not defined in Protected mode. The state of  $\overline{A20M}$  is ignored during transfers to and from SMM memory.  $\overline{A20M}$  is sampled on every rising clock edge. (See Switching Characteristics  $t_{26}$  and  $t_{27}$ .)

#### **ADS** Address Status

#### **Output**

$\overline{ADS}$  indicates the beginning of a new bus cycle. Valid addresses and cycle information are available on the address bus simultaneously with the assertion of  $\overline{ADS}$ .  $\overline{ADS}$  is floated during bus hold or back-off.

#### **ADSC** Address Status Copy

#### Output

ADSC performs the same function as ADS. It permits greater fanout. ADSC is normally used to directly drive the cache to achieve greater speed.

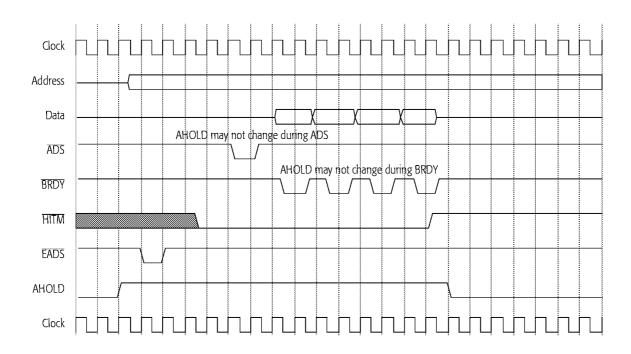

#### AHOLD Address Hold

#### Input

A31–A3 and AP are floated on the clock after AHOLD is recognized as asserted. Other signals remain active. This allows another bus master to access the processor's address bus for a cache inquire cycle. AHOLD has a small internal pulldown resistor. (See Switching Characteristics  $t_{22}$  and  $t_{23}$ .)

#### AP Address Parity

## Input/Output

The AP signal provides even parity for the address bus. This signal is driven simultaneously with the address bus. Inquire cycles that do not provide even parity in the same clock cycle as EADS will result in the assertion of APCHK. (See APCHK.)

#### **APCHK**

## **Address Parity Check**

#### Output

If the processor detects an address parity error on the address bus for inquire cycles,  $\overline{APCHK}$  is asserted on the second clock after  $\overline{EADS}$  is sampled. It remains active for one clock.

#### BE7-BE0

## Byte Enables

#### **Output**

The BE7-BE0 signals indicate active bytes during read and write cycles. The eight byte-enable signals correspond to the eight bytes of the data bus as follows:

■ BE7: D63–D56 ■ BE3: D31–D24

■ BE6: D55–D48 ■ BE2: D23–D16

■ BE5: D47–D40 ■ BE1: D15–D8

■ BE4: D39–D32 ■ BE0: D7–D0

These signals are driven at the same time as the address bus. The byte-enable signals are also used to decode special cycles as defined in Table 6.

#### BF (Model 0)

#### **Bus Frequency**

#### Input

For the AMD-K5 Model 0 processor, the BF signal determines the internal operating speed of the processor. The frequency of the CLK signal is multiplied internally by a ratio determined by the state of the BF signal during RESET. If BF is sampled High at RESET, the clock frequency is 1.5x the bus frequency. If BF is sampled Low at RESET, the clock frequency is 2x the bus frequency.

| BF Pin | <b>Internal Clock Multiplier</b> |

|--------|----------------------------------|

| 0      | 2                                |

| 1      | 1.5                              |

AMD-K5 Processor Data Sheet

18522F/0-Jan1997

# BF1-BF0 (Model 1 and Model 2)

## Bus Frequency

For the AMD-K5 model 1 and model 2 processors, the BF1 and BF0 signals determine the internal operating speed of the processor. The frequency of the CLK signal is multiplied internally by a ratio determined by the states of the BF1 and BF0 signals during RESET. The processor speed multiplier is determined as shown below:

Input

| <u>BF1 Pin</u> | <u>BF0 Pin</u> | Internal Clock Multiplier |

|----------------|----------------|---------------------------|

| 0              | 0              | 1.75                      |

| 0              | 1              | Reserved                  |

| 1              | 0              | 1.5                       |

| 1              | 1              | 1.5                       |

**BOFF** Backoff Input

The processor will transition to a bus hold state and float the associated signals on the clock that BOFF is sampled as asserted. An alternate master may drive the bus signals on the clock after BOFF is sampled asserted. When BOFF is negated, the processor will restart any bus cycle from the beginning. Burst cycles interrupted by BOFF will restart from the beginning of the burst cycle. BOFF takes priority over BRDY. If BRDY is sampled asserted in the same cycle as BOFF, the cycle will be restarted. (See Switching Characteristics t<sub>22</sub> and t<sub>23</sub>.)

# **BRDY** Burst Ready Input

BRDY is sampled on the second and following clocks of a bus cycle to indicate completion of a data transfer cycle. BRDY is ignored at the end of the first clock of a bus cycle and when the bus is in an idle state. The data bus is sampled when BRDY is asserted. Up to four assertions of BRDY are needed to complete the bus cycle. (See Switching Characteristics  $t_{20}$  and  $t_{21}$ .)

## BRDYC Burst Ready Copy Input

BRDYC is functionally identical to BRDY. These signals are connected internally by an OR gate. BRDYC is typically used by level two cache. At the falling edge of RESET, the states of BRDYC and BUSCHK control the drive strength on the A21–A3 (not including A31–A22), ADS, HITM, and W/R signals. The drive strength is weak for all states of BRDYC and BUSCHK except when BRDYC and BUSCHK are both Low, in which case

the drive strength is strong. The A31–A22 signals use the weak drive strength at all times.

### **BREQ** Bus Request Pending Output

The processor asserts the BREQ signal to indicate a request for the bus. This signal is driven even when the processor floats the bus (except in Test mode). (See FLUSH.)

## BUSCHK Bus Check Input

The BUSCHK signal allows the external system to indicate bus cycle errors. This signal, when asserted, latchs the address bus. The control signals in the machine check registers will also latch. If the MCE bit in CR4 is set, the processor will vector to the machine check exception at the end of the bus cycle. At the falling edge of RESET, the states of BRDYC and BUSCHK control the drive strength on the A21–A3 (not including A31–A22), ADS, HITM, and W/R signals. The drive strength is weak for all states of BRDYC and BUSCHK except BRDYC and BUSCHK both Low, in which case drive strength is strong. A31–A22 use the weak drive strength at all times.

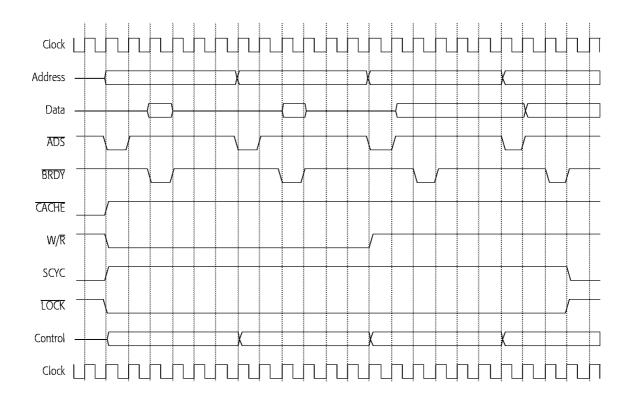

## **CACHE** Cache Status Output

The CACHE signal is asserted for cacheable read cycles or burst writeback cycles. A burst access is always four 64-bit transfers associated with a line refill or a cache write back. Read data will not be cached if CACHE is negated during a read cycle, or if KEN is negated. KEN must be asserted during the first access of a burst transfer. If KEN is negated, a single access occurs.

## CLK Clock Input

The CLK signal is the bus clock for the processor, and is the primary reference for all bus cycle timings (except for test signals). It is used with the BF signal to determine the internal operating speed of the processor. The processor multiplies the clock input by 1.5 or 2. (See BF.)

# D/C Data/Code Output

The D/C signal, driven active with  $\overline{ADS}$ , is used with other control signals to determine bus cycle and special cycle types. It is floated with  $\overline{BOFF}$  and bus hold. These cycles are defined in Table 5 and Table 6 on page 27.

AMD-K5 Processor Data Sheet

18522F/0-Jan1997

## D63-D0 Data Lines Input/Output

The D63–D0 signals are the 64-bit data bus. These signals are driven during the second and subsequent clocks of write cycles, with valid bytes indicated by  $\overline{BE7}$ – $\overline{BE0}$ . They are sampled when the  $\overline{BRDY}$  signal is asserted for read cycles. (See Switching Characteristics  $t_{34}$  and  $t_{35}$ .)

## DP7-DP0 Data Parity Input/Output

The DP7–DP0 signals provide even parity, one for each of the eight bytes of the data bus. The eight data parity signals correspond to the eight bytes of the data bus as follows:

DP7: D63-D56

DP3: D31-D24

DP6: D55-D48

DP2: D23-D16

DP5: D47-D40

DP1: D15-D8

DP4: D39-D32

DP0: D7-D0

These signals are driven with the data bus. Read cycles that do not provide even parity when the read data is driven result in the assertion of PCHK. Byte enables are negated for invalid data bytes. For systems that do not use parity, DP7–DP0 should be connected to  $V_{CC}$  through a pull-up resistor. (See PCHK and Switching Characteristics  $t_{34}$  and  $t_{35}$ .)

### **EADS** Valid External Address Input

The EADS signal indicates that a valid address is driven on the address bus during inquire cycles. EADS has an internal pull-up resistor. (See Switching Characteristics  $t_{16a}$  and  $t_{17}$ .)

#### **EWBE** External Write Buffer Empty Input

External system logic notifies the processor of pending buffered write cycles by negating the EWBE signal. The processor will hold writes to exclusive or modified cache lines until EWBE is asserted.

### FERR Floating-Point Error Output

The FERR signal is asserted as a result of an unmasked floating-point error. It is only floated during test.

## FLUSH Cache Flush Input

Asserting FLUSH will flush the internal caches. For acceptance, FLUSH must meet the required setup and hold times for one or more clocks. Instruction and data caches will be invalidated. Any modified data in the data cache will be written back. A flush acknowledge cycle will follow the invalidation to notify external logic that the internal caches have been flushed. The FLUSH signal is also sampled at the falling edge of RESET. If sampled Low, the processor will operate in Tri-State Test mode.

# FRCMC Functional Redundancy Check

Master/Checker Input

FRCMC is used to configure the processor as a Master or Checker. FRCMC is only sampled at RESET. Sampling FRCMC High configures the AMD-K5 processor for Master mode operation, and sampling FRCMC Low configures the processor for Checker operation. The processor follows standard bus protocol in Master mode. It floats all outputs, with the exception of IERR and TDO, in Checker mode. In Checker mode, all signals are inputs and their values are compared with predicted values.

HIT Hit Output

The HIT signal is asserted when an inquire cycle hits a valid line in the instruction or data cache. This signal can be sampled two clock cycles after EADS has been sampled as asserted.

**HITM** Hit to a Modified Line Output

The HITM signal is asserted when an inquire cycle hits a modified line in the data cache. This signal can be sampled two clock cycles after EADS has been sampled as asserted. HITM will remain asserted until the modified line has been written back.

HLDA Hold Acknowledge Output

The HLDA signal is driven to acknowledge a bus hold request. The bus is floated when HLDA is asserted. HLDA will be negated one clock cycle after HOLD is negated. (See HOLD.)

AMD-K5 Processor Data Sheet

18522F/0-Jan1997

## HOLD Bus Hold Request Input

The HOLD signal is used to request the processor bus. When this signal is asserted, the processor will complete all pending bus cycles, float the bus, and assert the HLDA signal. This signal is not recognized during locked cycles. (See Switching Characteristics  $t_{24}$  and  $t_{25b}$ .)

## **IERR** Internal Error Output

IERR indicates internal parity errors and functional redundancy errors. Internal parity errors will cause IERR to be asserted for one clock, and the processor will halt. Functional redundancy errors, when configured as a Checker, will cause IERR to be asserted in the second clock after the mismatched output value was detected.

#### **IGNNE** Ignore Numeric Error Input

The IGNNE signal is used in conjunction with the NE bit in CR0 to control response to numeric errors in the floating-point unit. Numeric errors are handled internally when the NE bit is set. When the NE bit is not set, errors are reported if  $\overline{\text{IGNNE}}$  is asserted and ignored when negated. (See Switching Characteristics  $t_{28}$  and  $t_{29}$ .)

#### INIT Initialize Input

The processor will perform a warm initialization when the INIT signal is asserted. The INIT signal is similar to the RESET signal except that the data buffers, data cache, floating-point registers, instruction cache, and SMBASE registers are not modified. The processor will perform a self-test if the INIT signal is sampled High at the falling edge of RESET.

#### INTR Maskable Interrupt Input

The INTR signal is used to generate interrupts. The interrupt number is transferred to the processor during the interrupt acknowledge cycle. To ensure that interrupts are acknowledged, the INTR signal must be asserted until a locked interrupt acknowledge cycle is complete. The INTR can be masked by clearing the IF bit in the EFLAGS register. (See Switching Characteristics  $t_{26}$  and  $t_{27}$ .)

INV Invalidation Input

The INV signal is used to designate the MESI protocol state of the cache line for inquire cycles that result in hits. This signal is sampled on the same clock that EADS is asserted. Sampling INV Low will result in the shared state, while sampling INV High will result in the invalid state.

**KEN** Cache Enable Input

KEN is asserted to enable caching. Caching is disabled when KEN is negated. Returning KEN asserted with the first BRDY or NA of a cacheable cycle causes the line to be placed in the cache. Returning it negated transforms the cycle into a non-cacheable, single-cycle read. KEN has a small internal pull-up resistor. (See Switching Characteristics  $t_{18a}$  and  $t_{19}$ .)

**LOCK** Bus Lock Output

The LOCK signal is asserted to indicate locked cycles, and is asserted during the first clock of a locked cycle. It is negated after BRDY is sampled for the last locked bus cycle. A HOLD request will not be acknowledged during locked cycles, but AHOLD and BOFF are allowed during locked cycles.

M/IO Memory/Input-Output OUTPUT

The M/IO signal is used with other control signals to determine bus cycle type. These cycles are defined in Table 5 and Table 6 on page 27. M/IO is driven active with ADS.

**NA** Next Address Input

NA is asserted when external memory is prepared to accept a pipelined cycle. NA does not generate pipelined cycles when LOCK is asserted, during writeback cycles, or when there are no pending internal cycles. Furthermore, locked or writeback cycles are not pipelined. KEN and WB/WT are sampled when NA or BRDY is asserted, whichever comes first.

NMI Non-maskable Interrupt Input

Asserting the NMI signal generates a non-maskable interrupt. The NMI input is rising-edge sensitive. The NMI signal must be held Low for at least one clock before its rising edge.

AMD-K5 Processor Data Sheet

18522F/0-Jan1997

## **PCD** Page Cache Disable Output

The PCD signal provides cacheability status by reporting the contents of the PCD bit in CR3, the page directory, or the page table entry. PCD reflects the state of the PCD bit in CR3 if non-paged cycles occur. In Real mode or Protected mode when paging is disabled, PCD reflects the state of the CD bit in CR0.

## **PCHK** Parity Status Output

The PCHK signal is asserted to indicate a data parity error for data read cycles. It may be sampled for parity status on the second clock after BRDY is sampled as asserted. Except during Test mode, PCHK is never floated.

## **PEN** Parity Enable Input

PEN, when asserted on a parity error, causes the address and control signals of the cycle to be latched into the machine check registers. The MCE bit in CR4, if set, will cause a vector to the machine check exception before another instruction is executed.

## PRDY Probe Ready Output

The processor asserts PRDY to acknowledge the system logic's assertion of R/S or execution of the Test Access Port (TAP) instruction, USEHDT, and to indicate the processor's entry into the Hardware Debug Tool (HDT) mode for debugging.

## PWT Page Write-Through Output

The PWT signal provides writeback status by reporting the contents of the PWT bit in CR3, the page directory, or the page table entry. The PWT signal reflects the state of the PWT bit in CR3 when non-paged cycles occur or paging is disabled. In Real mode or Protected mode, when paging is disabled, PWT will be zero.

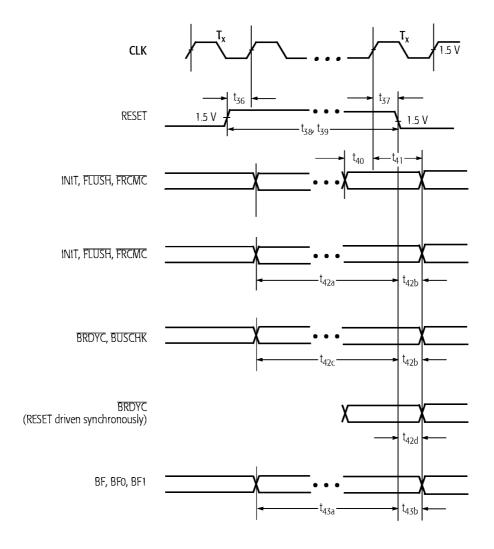

#### **RESET** Reset Input

The processor will reset when the RESET signal is asserted. The processor cannot begin execution until at least 1 ms after  $V_{CC}$ , BF, and CLK have stabilized. The operating mode is determined by the state of the FLUSH, INIT, and FRCMC signals during the falling edge of RESET. (See FLUSH, INIT, FRCMC, and Switching Characteristics  $t_{36}$  and  $t_{37}$ .)

R/S Run/STOP Input

The R/S signal provides an edge-sensitive interrupt to stop normal execution. A falling-edge transition halts execution at the next instruction boundary. A rising-edge transition, which must not occur before PRDY is asserted, resumes execution.

SCYC Split Cycle Output

SCYC indicates split cycles when  $\overline{LOCK}$  is asserted. This signal indicates that more than two cycles will be locked together for misaligned locked transfers.

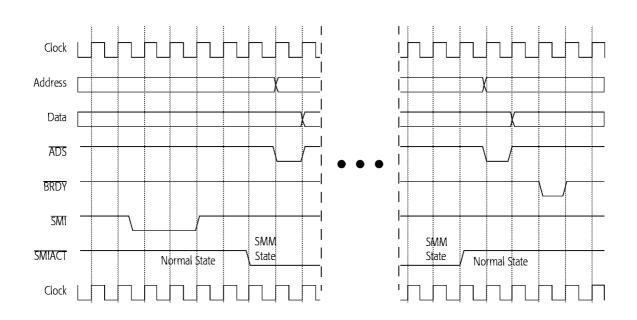

SMI System Management Interrupt Input

SMI allows external logic to request a non-maskable system management interrupt. Asserting this signal will cause the processor to suspend normal execution and enter System Management Mode (SMM) at the next instruction boundary.

SMIACT SMI Active Output

SMIACT is asserted when the processor is operating in SMM.

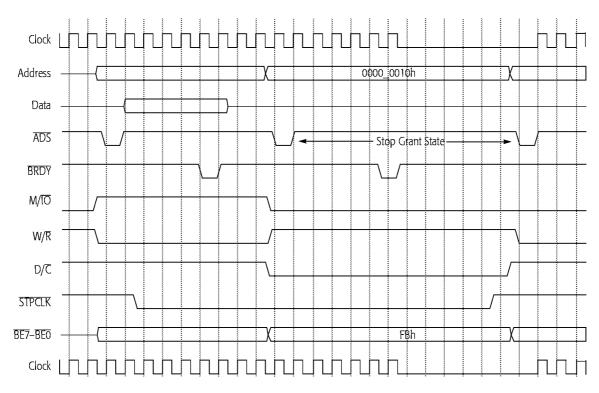

STPCLK Stop Clock Input

STPCLK, when asserted, causes the processor to complete the current instruction and issue a stop grant bus cycle. Once the stop grant is issued, the processor stops the clock, retaining the ability to execute inquire cycles.

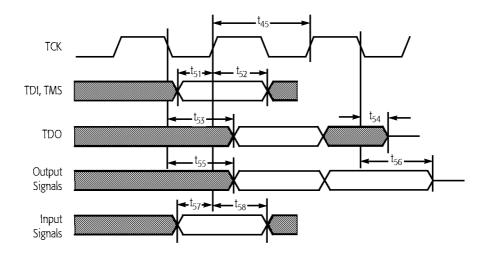

TCK Test Clock Input

TCK is a test clock signal. It conforms to the IEEE-1149.1 boundary scan interface.

**TDI** Test Data Input Input

The TDI signal is a serial input for test data and TAP instructions. The instructions or data are sampled on the rising edge of the TCK signal.

TDO Test Data Output Output

The TDO signal is a serial output for test data and TAP instructions. TDO is updated on the falling edge of the TCK signal.

TMS Test Mode Select Input

The TMS signal is used to select the TAP Test modes. This signal is sampled on the rising edge of the TCK. TMS has an internal pull-up resistor.

TRST Test Reset Input

Asserting TRST initializes the TAP controller.

W/R Write/Read Output

The W/R signal is used with other control signals to distinguish bus cycles and special cycles. These cycles are defined in Table 5 and Table 6 on page 27. W/R is driven active with ADS, and floated with BOFF and bus hold.

WB/WT Writeback/Writethrough Input

The state of WB/WT determines the MESI cache protocol state of a data line during cache line fills. When the signal is driven High, the cache line will be loaded in the exclusive state. When the signal is driven Low, the cache line will be loaded in the shared state.

Table 1. Input Pins

| Name   | Туре         | Note   | Name  | Туре         | Note   |

|--------|--------------|--------|-------|--------------|--------|

| A20M   | Asynchronous | Note 1 | IGNNE | Asynchronous |        |

| AHOLD  | Synchronous  |        | INIT  | Asynchronous |        |

| BF     | Synchronous  | Note 2 | INTR  | Asynchronous |        |

| BOFF   | Synchronous  |        | INV   | Synchronous  | Note 5 |

| BRDY   | Synchronous  |        | KEN   | Synchronous  | Note 6 |

| BRDYC  | Synchronous  |        | NA    | Synchronous  |        |

| BUSCHK | Synchronous  | Note 3 | NMI   | Asynchronous |        |

#### Notes:

- 1. A20M may change during RESET or during a serializing event like an I/O write. A state change at other times will result in incorrect address generation on subsequent memory cycles.

- 2. BF and  $\overline{FRCMC}$  are normally connected to  $V_{CC}$  or  $V_{SS}$  by a jumper. For correct operation, any change on these signals should be followed by a RESET.

- 3. BUSCHK is sampled in every clock. Any asserted sample is remembered and takes effect on the same clock as the last BRDY.

- 4. These are sampled in the same clock as BRDY.

- 5. This is sampled in the same clock as EADS.

- 6. These are sampled with the first  $\overline{BRDY}$  or  $\overline{NA}$  and must meet setup to every clock

**Table 1. Input Pins (continued)**

| Name  | Туре         | Note   | Name   | Туре         | Note   |

|-------|--------------|--------|--------|--------------|--------|

| CLK   | Clock        |        | PEN    | Synchronous  | Note 4 |

| EADS  | Synchronous  |        | RESET  | Asynchronous |        |

| EWBE  | Synchronous  | Note 4 | R/S    | Asynchronous |        |

| FLUSH | Asynchronous |        | SMI    | Asynchronous |        |

| FRCMC | Asynchronous | Note 2 | STPCLK | Asynchronous |        |

| HOLD  | Synchronous  |        | WB/WT  | Synchronous  | Note 6 |

#### Notes:

- 1. A20M may change during RESET or during a serializing event like an I/O write. A state change at other times will result in incorrect address generation on subsequent memory cycles.

- 2. BF and  $\overline{FRCMC}$  are normally connected to  $V_{CC}$  or  $V_{SS}$  by a jumper. For correct operation, any change on these signals should be followed by a RESET.

- 3. BUSCHK is sampled in every clock. Any asserted sample is remembered and takes effect on the same clock as the last BRDY.

- 4. These are sampled in the same clock as BRDY.

- 5. This is sampled in the same clock as EADS.

- 6. These are sampled with the first  $\overline{BRDY}$  or  $\overline{NA}$  and must meet setup to every clock

### Table 2. Output Pins

| Name    | Floated At (Note 1)          | Name   | Floated At (Note 1)               |

|---------|------------------------------|--------|-----------------------------------|

| A4-A3   | Bus Hold, Address Hold, BOFF | HLDA   | Always Driven                     |

| ADS     | Bus Hold, BOFF               | ĪERR   | Always Driven                     |

| ADSC    | Bus Hold, BOFF               | LOCK   | Bus Hold, BOFF                    |

| APCHK   | Always Driven                | M/IO   | Bus Hold, BOFF                    |

| BE7-BEO | Bus Hold, BOFF               | PCD    | Bus Hold, BOFF                    |

| BREQ    | Always Driven                | PCHK   | Always Driven                     |

| CACHE   | Bus Hold, BOFF               | PRDY   | Always Driven                     |

| D/C     | Bus Hold, BOFF               | PWT    | Bus Hold, BOFF                    |

| FERR    | Always Driven                | SCYC   | LOCK not asserted, Bus Hold, BOFF |

| HIT     | Always Driven                | SMIACT | Always Driven                     |

| нтм     | Always Driven                | W/R    | Bus Hold, BOFF                    |

| Notes:  |                              | II I   |                                   |

#### Notes.

1. All outputs float during Tri-State test mode.

Table 3. Input/Output Pins

| Name    | When Floated                 |

|---------|------------------------------|

| A31-A5  | Bus Hold, Address Hold, BOFF |

| AP      | Bus Hold, Address Hold, BOFF |

| D63-D0  | Bus Hold, BOFF               |

| DP7-DP0 | Bus Hold, BOFF               |

Table 4. Test Pins

| Name | Туре   | Note                               |

|------|--------|------------------------------------|

| TCK  | Input  |                                    |

| TDI  | Input  | Sampled on the rising edge of TCK. |

| TDO  | Output | Driven on the falling edge of TCK. |

| TMS  | Input  | Sampled on the rising edge of TCK. |

| TRST | Input  |                                    |

**Table 5. Bus Cycle Definition**

| Bus Cycle Initiated                    |      | Generated<br>by System |     |       |     |

|----------------------------------------|------|------------------------|-----|-------|-----|

| ·                                      | M/IO | D/C                    | W/R | CACHE | KEN |

| Code Read, Instruction Cache Line Fill | 1    | 0                      | 0   | 0     | 0   |

| Code Read, Noncacheable                | 1    | 0                      | 0   | 1     | Х   |

| Code Read, Noncacheable                | 1    | 0                      | 0   | х     | 1   |

| Encoding for Special Cycle             | 0    | 0                      | 1   | 1     | Х   |

| Interrupt Acknowledge                  | 0    | 0                      | 0   | 1     | Х   |

| I/O Read, Noncacheable                 | 0    | 1                      | 0   | 1     | Х   |

| I/O Write, Noncacheable                | 0    | 1                      | 1   | 1     | Х   |

| Memory Read, Data Cache Line Fill      | 1    | 1                      | 0   | 0     | 0   |

| Memory Read, Noncacheable              | 1    | 1                      | 0   | 1     | Х   |

| Memory Read, Noncacheable              | 1    | 1                      | 0   | х     | 1   |

| Memory Write, Data Cache Writeback     | 1    | 1                      | 1   | 0     | Х   |

| Memory Write, Noncacheable             | 1    | 1                      | 1   | 1     | х   |

Table 6. Special Cycles

| Special Cycle                             | A4 | BE7 | BE6 | BE5 | BE4 | BE3 | BE2 | BE1 | <b>BEO</b> | M/IO | D/C | W/R | CACHE | KEN |

|-------------------------------------------|----|-----|-----|-----|-----|-----|-----|-----|------------|------|-----|-----|-------|-----|

| Branch Trace                              | 0  | 1   | 1   | 0   | 1   | 1   | 1   | 1   | 1          | 0    | 0   | 1   | 1     | х   |

| Flush (INVD, WBINVD execution)            | 0  | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 1          | 0    | 0   | 1   | 1     | х   |

| Flush Acknowledge<br>(FLUSH asserted Low) | 0  | 1   | 1   | 1   | 0   | 1   | 1   | 1   | 1          | 0    | 0   | 1   | 1     | х   |

| Halt                                      | 0  | 1   | 1   | 1   | 1   | 1   | 0   | 1   | 1          | 0    | 0   | 1   | 1     | х   |

| Shutdown                                  | 0  | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0          | 0    | 0   | 1   | 1     | х   |

| Stop Clock Acknowledge                    | 1  | 1   | 1   | 1   | 1   | 1   | 0   | 1   | 1          | 0    | 0   | 1   | 1     | х   |

| Writeback (WBINVD execution)              | 0  | 1   | 1   | 1   | 1   | 0   | 1   | 1   | 1          | 0    | 0   | 1   | 1     | х   |

# **8** Processor Operation

# 8.1 Power-On Configuration

The AMD-K5 processor signals at reset are listed in Table 7.

Table 7. Signals at Reset

| Output  | State at<br>Reset | Output | State at<br>Reset |  |

|---------|-------------------|--------|-------------------|--|

| Address | Float             | FERR   | 1                 |  |

| ADS     | 1                 | HIT    | 1                 |  |

| APCHK   | 1                 | нтм    | 1                 |  |

| BE7-BEO | Undefined         | HLDA   | 0                 |  |

| BRDY    | 1                 | LOCK   | 1                 |  |

| BRDYC   | 1                 | M/IO   | Undefined         |  |

| BREQ    | 0                 | PCD    | Undefined         |  |

| CACHE   | Undefined         | PCHK   | 1                 |  |

| D/C     | Undefined         | PRDY   | 0                 |  |

| Data    | Float             | PWT    | Undefined         |  |

| DP7-DP0 | Float             | W/R    | Undefined         |  |

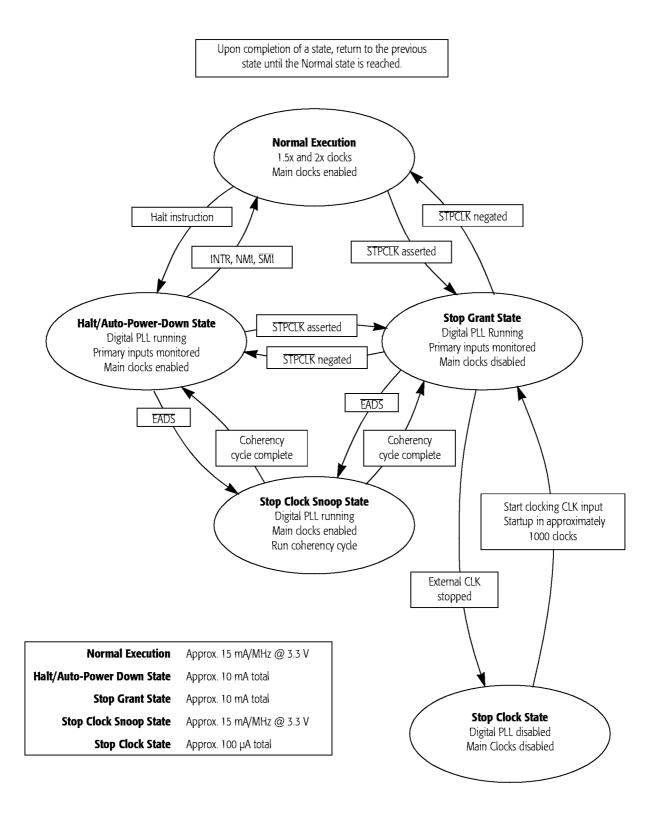

# 8.2 Clock State

The AMD-K5 processor uses the Enhanced 486 protocol to control the clock. This protocol provides for stopping the clock from hardware using the STPCLK control signal, or from software using the HALT instruction. During the clock-stopped states, cache coherency is maintained by temporarily enabling the clock for snoop processing and recognizing HOLD/HLDA arbitration sequences.

A state transition diagram for a stop clock state machine implementing five clocking states—the Enhanced 486 protocol—is illustrated in Figure 3 on page 29.

Figure 3. State Transition Diagram for Stop Clock State Machine

AMD-K5 Processor Data Sheet

18522F/0-Jan1997

# Normal Execution State

In this state, the AMD-K5 processor operates at full speed. All clocks are running.

## Halt/Auto-Power-Down State

In this state, most internal clocks are stopped. The Phase Lock Loop (PLL) is operating and certain bus interface components are clocked. Instruction execution is disabled. This aids in timely detection of inquire cycles and HOLD/HLDA sequences, while greatly reducing power consumption.

The Halt/Auto-Power-Down State is entered from normal execution state by executing the HALT instruction in Real mode or Protected mode. The clock state will return to normal execution state when an interrupt, non-maskable interrupt, system management interrupt, power-on reset, or soft reset is detected (INTR, NMI,  $\overline{\text{SMI}}$ , RESET, or INIT, respectively). The clock state may temporarily transition from Halt/Auto-Power-Down State to Stop Clock Snoop State to process an inquire cycle or to Stop Grant State in response to a  $\overline{\text{STPCLK}}$ . In these cases, the clock state will return to Halt/Auto-Power-Down State and wait for one of the interrupt conditions when the secondary condition is removed.

## **Stop Grant State**

In this state, most internal clocks are stopped. The PLL is operating and certain bus interface components are clocked. Instruction execution is disabled. This allows timely detection of inquire cycles and HOLD/HLDA sequences, while greatly reducing power consumption.

The Stop Grant State is entered from Normal Execution State or Halt/Auto-Power-Down State by asserting the STPCLK pin. When STPCLK is sampled as asserted, the current instruction is completed, all processing is stopped, a Stop Grant bus cycle is generated, and the clock is shut down. The clock state will return to its previous state when STPCLK is negated. Once asserted, STPCLK must not be negated until the Stop Grant Acknowledge special cycle is seen. The clock state may temporarily transition from Stop Grant State to Stop Clock Snoop State to process an inquire cycle, or to Stop Clock State to process a Stop Clock request. In these cases, the clock state will return to Stop Grant State when the secondary condition is removed.

STPCLK is treated as the lowest priority external interrupt. If a higher priority external interrupt exists (power-on reset, soft reset, flush, system management interrupt, non-maskable

interrupt, or maskable interrupt), recognition of STPCLK is delayed until the interrupt processing is complete. However, assertion of a higher priority interrupt will not cause the Stop Grant State to be exited.

### Stop Clock Snoop State

In this state, all internal clocks are running and an inquire cycle is being performed. Instruction execution is disabled and HOLD/HLDA operate normally.

Stop Clock Snoop State is entered from Halt/Auto-Power-Down State or Stop Grant State when an inquire cycle is detected. This is a temporary state, lasting only until the coherency operation (snoop/miss, snoop/invalidate or snoop/writeback) is complete. The clock state will then return to the previous state. (See Figure 24 on page 72.)

## **Stop Clock State**

In this state, all internal clocks are stopped, the PLL is shut down, and all execution is disabled. If HOLD is asserted while the clock is running, HLDA will be generated and the buses floated. If HOLD is negated, HLDA will be negated and the buses will be driven to their previous state without regard to whether the clock is running. This is the lowest power state.

The Stop Clock State is entered from the Stop Grant State by stopping the CLK. The clock state returns to Stop Grant State when the CLK is again started. The time required to restart the CLK and enter the Stop Clock State is approximately 1000 clock cycles.

# 8.3 Cache Protocol

#### **Internal Cache**

The AMD-K5 processor has a 16-Kbyte dual-tagged instruction cache with 32-byte lines and an 8-Kbyte dual-tagged data cache of 32-byte lines. Cache lines refill in four transfer burst cycles from memory and align along 32-byte lines.

The operating mode is software-controlled, and on-chip caches must be enabled by software. This is accomplished by clearing or setting the CD and NW bits of CR0.

Any area of memory can be cached. Software can prevent areas of memory from being cached by setting the PCD bit in the corresponding page table entry. Hardware can prevent areas of memory from being cached through the KEN pin.

The AMD-K5 processor uses the MESI protocol—2 bits per cache line—in its data cache to ensure consistency in multiprocessing systems. The physical tags of both the instruction and data cache are accessed and compared during each inquire cycle to maintain a consistent copy of data.

#### **Cacheability**

The PCD and PWT bits in the page directory and page-table entry control caching on a page-by-page basis. The PCD and PWT bits manage page caching and drive processor PCD and PWT output pins.

PCD affects the cacheability of pages in the internal cache. The PWT bit determines whether the writethrough or writeback policy is used for this particular page.

## **Copy-Back Buffers**

A one-line copy-back buffer is employed within the AMD-K5 processor to temporarily hold a modified entry being replaced in the data cache. The replaced line is stored in the copy-back buffer at the same time the read request for the replacement line is sent externally. Following completion of the read access, the modified line in the copy-back buffer is written back to memory. The copy-back buffer is snooped during inquire cycles.

A requested-word-first protocol is implemented by the AMD-K5 processor. Following receipt of the first data item, execution continues while the following three entries of the line are being fetched. The line is not marked valid until the last entry is stored in the cache.

# 8.4 Data Cache Coherency

Throughout this discussion, the MESI states may be abbreviated as follows:

M—Modified Exclusive State

E-Exclusive State

S—Shared State

I-Invalid State

#### **Cache Invalidation**

FLUSH writes back all modified lines and then invalidates all cache lines and generates a Flush Acknowledge special cycle to instruct the L2 cache to invalidate all lines.

The INVD instruction invalidates the entire cache and generates a Flush special cycle to instruct the L2 cache to invalidate all lines.

The WBINVD instruction writes back and invalidates all cache lines, generates a Write Back special cycle to instruct the L2 cache to write back all lines, and then generates a Flush special cycle to instruct the L2 cache to invalidate all lines.

## **Read Cycles**

The cache response to processor-generated reads is described in Table 8. Processor reads that hit in the data cache require no external data cycle. The data is provided by the cache. Processor reads that miss in the data cache generate a read-allocate operation, including an external bus cycle. The action of the cache is dependent on the system response to that cycle. The cache state transition for read cycles is also described in Table 8.

A read allocate begins by selecting the way in the cache to be replaced at random.

| State | CACHE | KEN | WB/WT | PWT | Next State | Note |

|-------|-------|-----|-------|-----|------------|------|

| М     | х     | х   | х     | х   | М          | 1    |

| E     | х     | х   | х     | х   | E          | 1    |

| S     | х     | х   | х     | х   | S          | 1    |

| 1     | 0     | 0   | 1     | 0   | E          | 2    |

| 1     | 0     | 0   | 0     | х   | S          | 3    |

| 1     | 1     | х   | х     | х   | 1          | 4    |

| 1     | х     | 1   | Х     | х   | 1          | 4, 5 |

**Table 8. Processor Reads to Data Cache**

#### Notes:

- 1. A read cycle hit: Data is provided directly from the cache.

- 2. A read cycle miss: Selects the line for replacement; writes back the replaced line if it is modified (otherwise, discards the line). The line is cached as writeback.

- 3. A read cycle miss: Selects the line for replacement; writes back the replaced line if it is modified (otherwise discards the line). The line is cached as writethrough.

- 4. A read cycle miss: The line is not cacheable.

- 5. Within the cache directory, the Invalid state indicates that the cache entry contains no valid data. For purposes of hit/miss determination, the Invalid state indicates that the referenced cache line is not present in the cache. When a line is selected for replacement, all invalid ways are selected before any valid data is displaced from the cache.

If the selected line is *not* modified, the data is discarded and the read of the new line is begun. When the first quad word of

the new line is received, it is forwarded to the execution units. When all four quad words are available, they are copied to the cache line at the selected way and the cache status is updated.

If the selected line is modified, the read of the new line is begun at the same time the contents of the replaced line are copied to the copy-back buffer. When the first quad word of the new line is received, it is forwarded to the execution units. Execution continues concurrently as the rest of the block is received. When all four quad words are available, they are copied to the cache line at the selected way and the cache status is updated. Concurrently, the contents of the replaced line are written to memory.

#### **Write Cycles**

Processor writes that hit in modified or exclusive lines in the data cache require no external data cycle. The data is updated in the cache. Processor writes that hit shared lines of the data cache update the data cache and memory. The status returned with the writethrough bus cycle determines the final state of the line.

If write allocate is enabled in the AMD-K5 processor, processor writes that miss in the data cache generate an external data cache read cycle followed by a write hit. If write allocate is not enabled in the AMD-K5 processor, write misses generate an external write cycle only.

#### **Write Allocate**

Write allocate is an operating mode of the AMD-K5 processor that causes cache write misses to either proceed as normal write misses or to be converted to data cache line fills followed by cache write hits. The write allocate feature provides improved performance on repeat accesses to write-allocated data cache lines. The load/store unit in the processor determines whether each cache write miss is write-allocatable by whether it falls in or out of the ranges specified in the memory range registers.

For details on the implementation of write allocate, refer to the *AMD-K5 Processor Software Development Guide*, order# 20007.

Before the write cycle occurs for a write miss with write allocate enabled, an external data cache read cycle occurs that follows the normal rules for read allocate, and the intermediate state of the filled data cache line depends on the result of the

read cycle as shown in Table 8. The final state of the data cache line is determined as shown in Table 9 by the transition from the intermediate read state (M, E, S, or I) to the final state (M, E, S, or I) after the write hit to the cache line.

**Note:** In write allocate mode, replaced data cache lines are handled in the same way as during read allocate.

| Table 9 | 9. | writes | to | vata | Cacne |  |

|---------|----|--------|----|------|-------|--|

|         |    |        |    |      |       |  |

Multan to Data Cooks

| State | CACHE | KEN | WB/WT | PWT | Next State | Note |

|-------|-------|-----|-------|-----|------------|------|

| M     | x     | x   | х     | x   | M          | 1    |

| Е     | x     | х   | x     | x   | M          | 2    |

| S     | 0     | 0   | 1     | 0   | Е          | 3    |

| S     | 0     | 0   | 0     | х   | S          | 3    |

| 3     | 0     | 0   | х     | 1   | 3          | ,    |

| I     | х     | х   | х     | х   | I          | 4    |

#### Notes:

- 1. A write hit to modified line: writes data to the cache.

- 2. A write hit to exclusive line: writes data to the cache.

- 3. A write hit to shared line: writes data to the cache and memory; invalidates any shared copy in the other cache.

- 4. If write allocate mode is not enabled, an invalid line always remains invalid. If write allocate mode is enabled, the intermediate state of the filled data cache line depends on the result of the read cycle as shown in Table 8, and the final state of the data cache line is determined by the intermediate state as applied to this table.

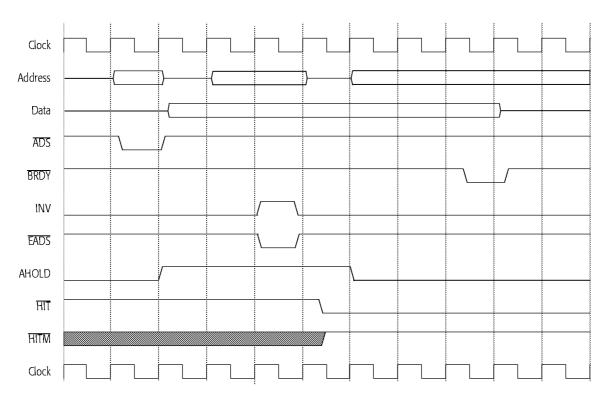

# External Inquire Cycles

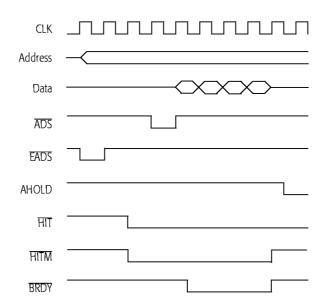

The processor supports inquire cycles for both instruction and data caches to maintain cache coherency. Inquire cycles are initiated with the assertion of EADS and result in a snoop to both the instruction and data caches. The snoop operation is performed using the physical tag arrays that are maintained for this purpose. The snoop operation runs concurrently with internal processor operation. The results of the snoop operation are indicated on the HIT and HITM pins. The results of the inquire cycles are described in Table 10. (See Figure 25 on page 72 and Figure 26 on page 73.)

State INV **Next State** Note 0 S Snoop hit to modified line: Assert HIT and HITM, Write back modified data to М memory. Negate HITM. Transition cache state when 1 1 complete. S 0 Snoop hit to unmodified line: Ε Assert HIT, Transition cache state 1 1 S 0 Snoop hit to unmodified line: S Assert HIT. Transition cache state 1 1 1 1 Snoop miss: Negate HIT. χ

Table 10. Inquire Cycles to Data Cache

## Instruction Cache Coherency

The instruction cache protocol is a subset of the data cache protocol where only Invalid and Shared states are implemented. Read hits provide the data to the processor. Read misses result in a read allocate operation that loads the line into the cache and the data is provided to the processor. The first data is provided as soon as it arrives from memory.

Write cycles are never generated to the instruction cache, but inquire cycles may hit in the instruction cache, resulting in the cache line being invalidated.

# **Self-Modifying Code** and the Cache

A snoop write hit to the instruction cache is treated as self-modifying code. The cache line is invalidated and all instructions in the instruction pipeline are flushed. Execution restarts at the instruction following the one causing the snoop. This guarantees exact execution of cacheable self-modifying code. For non-cacheable code, a jump should be placed between the modification of the code and its execution.

# 8.5 External Bus Description

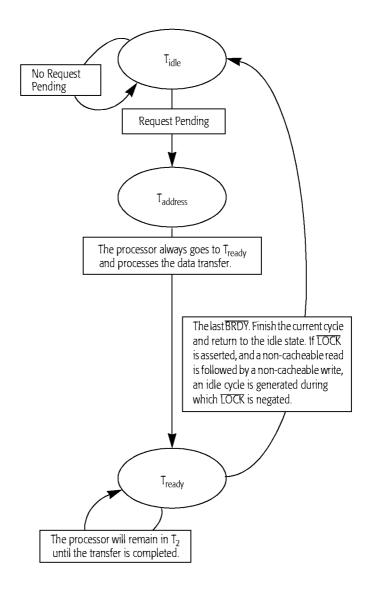

The AMD-K5 processor external bus is identical to the P54C 64-bit bus, and will run at 1.5x or 2.0x multiples of the external bus frequency. The bus state transitions are illustrated in Figure 4.

Figure 4. Bus State Transitions

#### Memory Organization

Physical memory address space ranges from 0000\_0000h to FFFF\_FFFFh. Memory space is organized in 64-bit sections. Each 64-bit section has 8 bytes at consecutive memory addresses. The first address of each group is evenly divisible by 8, and each group is addressed by A31–A3. Since the protocol does not implement A2–A0 when interfacing to 32-bit, 16-bit, or 8-bit memories, the lower portions of the address must be determined by decoding the eight byte-enable signals. The address space of I/O begins at 0000\_0000h and ends at 0000\_FFFFh. I/O space is organized as a sequence of 8-bit quantities.

Memory objects can be 8, 16, 32, or 64 bits. I/O objects are 8, 16, or 32 bits. Both appear as fields on the 64-bit data bus.

Data is transferred on the byte lines corresponding to the address. 16-bit or 32-bit objects crossing a 32-bit boundary, or 64-bit objects crossing a 64-bit boundary, are misaligned and will require multiple cycles to transfer.

The byte-enable signals and the data lines correspond in the following manner:

BE7: D63-D56

BE6: D55-D48

BE5: D47-D40

BE4: D39-D32

BE3: D31-D24

BE2: D23-D16

BE1: D15-D8

BE0: D7-D0

### 8.6 Bus Cycles

Bus cycles encode normal read and write accesses to code or data space and handle special events such as interrupt acknowledge. The type of cycle is determined by the  $\overline{CACHE}$ , D/C, M/ $\overline{IO}$ , and W/ $\overline{R}$  outputs. The processor encodes information with the byte-enable signals for special bus cycles. (See Table 6 on page 27.)

If M/IO is asserted Low or PCD is driven High in any cycle, CACHE is not asserted. The processor uses a burst transfer of four 64-bit accesses, corresponding to the 32-byte line size of the caches, for bus cycles involving cache line movement.

Table 11 shows the order of burst accesses expected by the external protocol.

Table 11. Addressing of the AMD-K5 Processor Burst Order

| If 1st Address = 0  | then 8  | then 10 | then 18 |

|---------------------|---------|---------|---------|

| If 1st Address = 8  | then 0  | then 18 | then 10 |

| If 1st Address = 10 | then 18 | then 0  | then 8  |

| If 1st Address = 18 | then 10 | then 8  | then 0  |

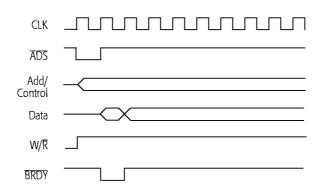

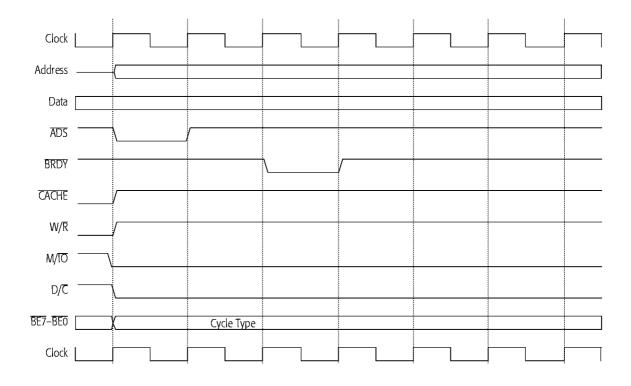

## Single Transfer Cycles

Single transfer cycles are initiated with the assertion of  $\overline{ADS}$  while negating the cache signal. The cycle is completed when the  $\overline{BRDY}$  signal is asserted by the external system. A single transfer cycle requires a minimum of two external clock cycles.

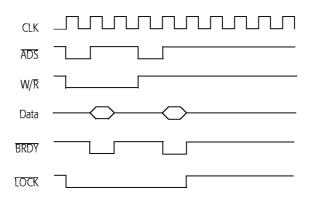

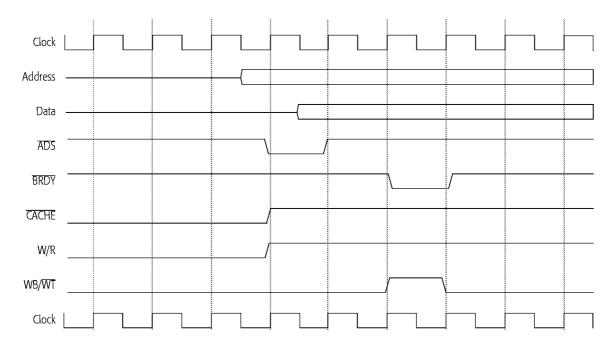

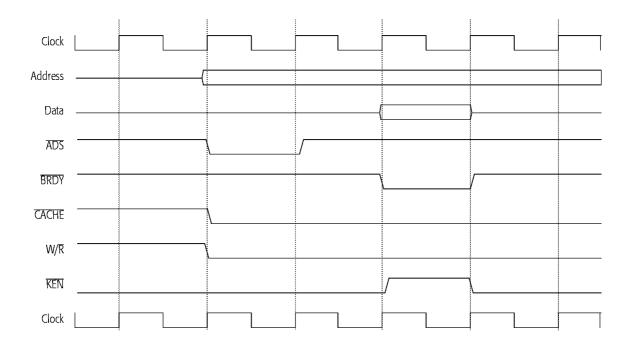

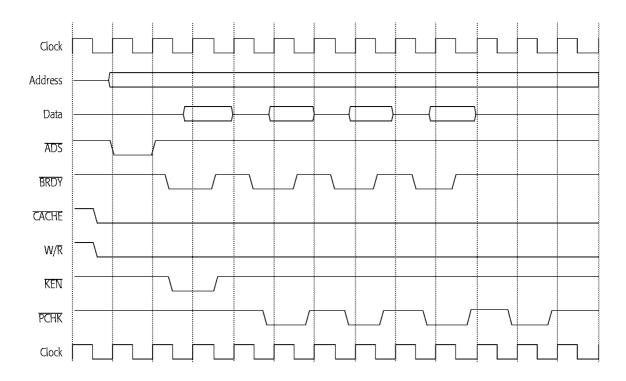

Timing for a single write transfer cycle is illustrated in Figure 5. (See Figures 28, 29, 30, and 31 beginning on page 74.)

Figure 5. Single Writes (Zero Wait States)

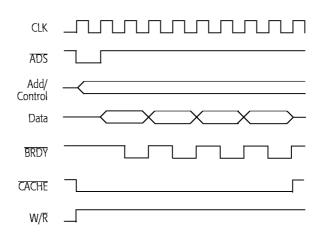

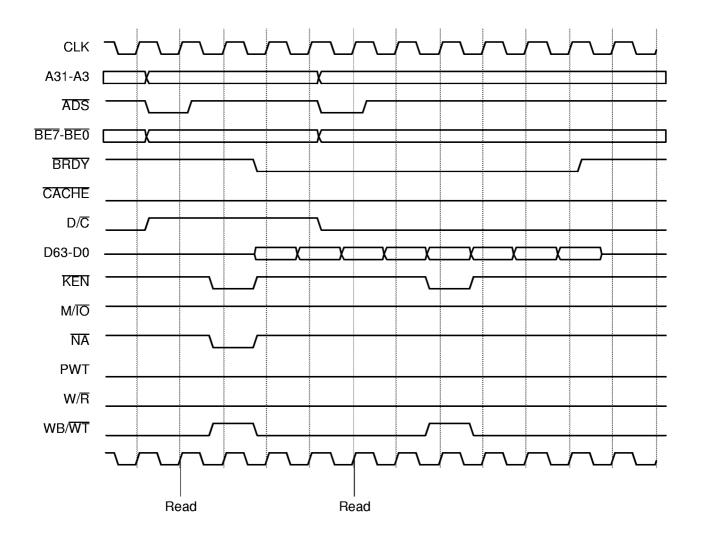

#### **Burst Read Cycles**

The size of a burst read access is always 32 bytes sent as four 64-bit transfers. A burst read access is indicated by the assertion of the CACHE signal, but if the external memory system subsequently does not assert KEN, the access will be converted to a single access. Data is sampled during the same clock that BRDY is asserted. Wait states can be added by negating BRDY.

The initial address and the byte enables are not changed after the initial access of a burst. External hardware must be configured to determine the subsequent addresses of the burst in accordance with the ordering specified in Table 11. PCHK is driven two clocks following an associated data transfer to the processor to indicate a data parity error. (See Figure 31 on page 75 and Figure 32 on page 76.)

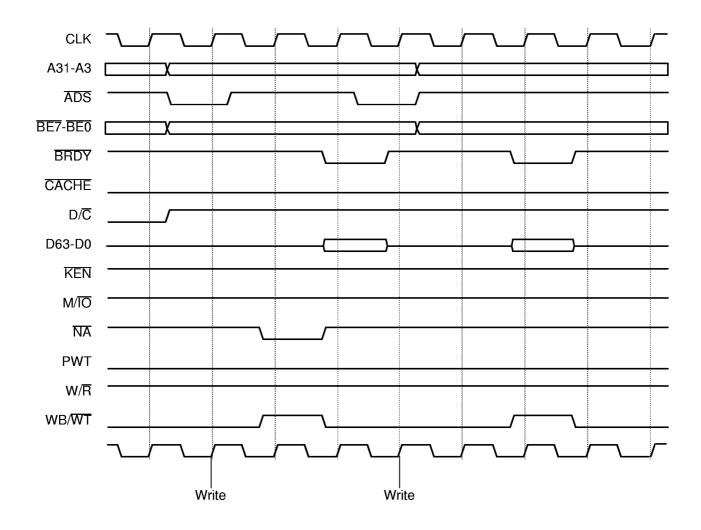

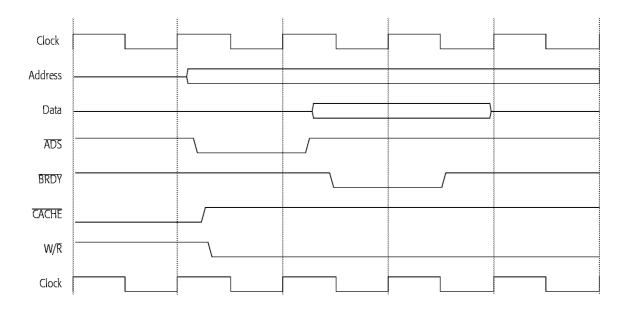

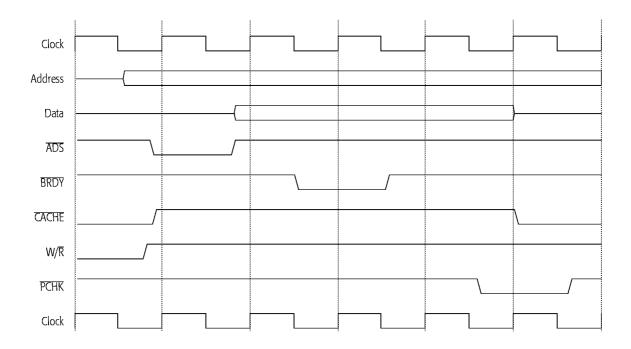

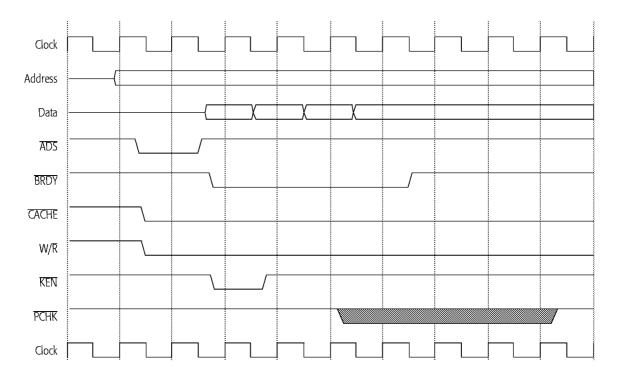

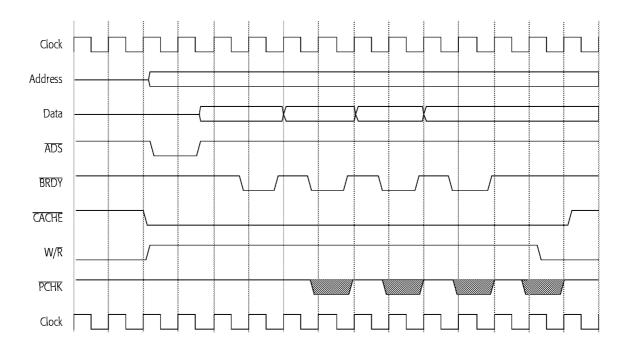

#### **Burst Write Cycles**

Like a burst read access, a burst write access is indicated by the assertion of the CACHE pin. Burst write cycles (an example of which is given in Figure 6) only occur for writebacks of modified lines in the processor data cache. These transfers are always four accesses. The address order for writeback cycles is always 0, 8, 10, 18. All other accesses, including unaligned accesses that cross 64-bit aligned boundaries, are sent as single accesses or a series of single accesses. Negating BRDY until

the external memory system is ready to receive data adds additional wait states, if they are needed. The processor ceases driving the current data element upon receiving the BRDY signal. (See Figure 33 on page 76.)

Figure 6. Burst Write (One Wait State)

The external signal KEN is ignored for burst write cycles since these are previously cached lines. Writebacks can occur as a result of the following:

- Replacement of a data cache entry that is modified

- An inquire cycle that hits in a modified line

- Assertion of the WBINVD instruction

- Assertion of the external signal FLUSH

Only one line is sent for inquire or replacement accesses. Assertion of FLUSH or execution of WBINVD results in the modified lines in the entire cache being written back as a series of single line writes. An inquire or replacement access results in a writeback of only one line.

#### BOFF or AHOLD/ HOLD/HLDA During Burst Transfers

BOFF or AHOLD can be asserted during a burst transfer. The processor will abort a cycle if BOFF is asserted in the middle of the cycle. When BOFF is negated, the cycle is restarted from the beginning.

If AHOLD is asserted, the processor responds by floating the address pins in the next clock cycle. The system can then drive the address and assert EADS to generate an inquire cycle

while the data cycle continues. Assertion of HOLD can occur at any time, but HLDA will not be asserted until pending cycles are completed.

To avoid excessive power drain, AHOLD should not be negated when  $\overline{BRDY}$  is asserted during a write cycle, and when  $\overline{ADS}$  is asserted at the beginning of a writeback cycle.

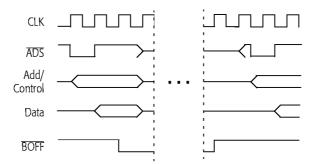

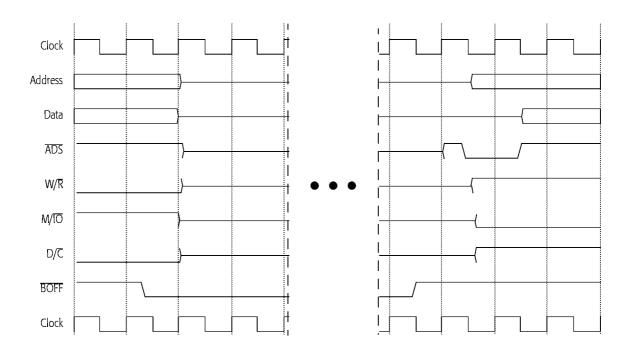

Use of BOFF

BOFF causes the processor to float its local bus on the next clock cycle and to terminate the current bus cycle (see Figure 7). BOFF is sampled every clock cycle. If both BOFF and BRDY are asserted during the same clock cycle, BRDY is ignored and the associated data transfer must be re-initiated. If BOFF is asserted while ADS is asserted, the processor floats ADS, even though it is in its asserted state. This situation must not be interpreted as the start of a cycle by the system.

Figure 7. BOFF Timing

KEN must be reasserted by the system to enable caching on any cycle that was previously aborted by BOFF. If a burst cycle is aborted by the assertion of BOFF in the middle of the access, the initial state of KEN when the access began will be used when the cycle is restarted. KEN should be reasserted if caching is enabled for the cycle.

Any cycles aborted due to BOFF are recorded behind a pending writeback cycle that is scheduled in response to a snoop hit to a modified line. For example, if a cache line fill is aborted due to BOFF, and an external cycle hits a modified line, the cache line fill is completed after the modified line is written back.

AMD-K5 Processor Data Sheet

18522F/0-Jan1997

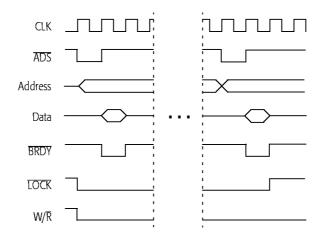

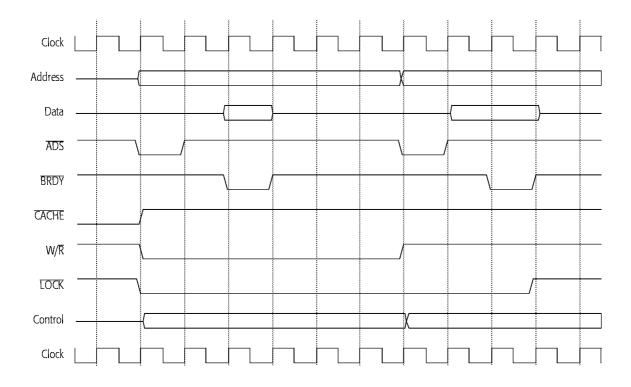

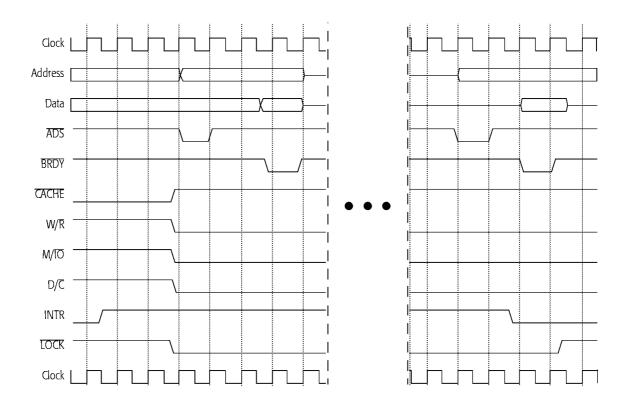

#### **Locked Operations**

A locked cycle, illustrated in Figure 8, uses the LOCK pin to indicate that the processor is performing a read-modify-write, and that both the read operation and write operation must be allowed to complete as a combined operation. (See Figure 36, 40, and 42 beginning on page 78.)

Figure 8. Locked Cycles

When the program generates a locked access, the processor first looks in the data cache. If the locked object is modified in the cache, it is written back to memory and invalidated. It is then accessed using a locked memory cycle. Since combined operations can access misaligned objects, locked operations can result in multiple writebacks, multiple locked reads, and multiple locked writes. When unaligned locked operations are performed, SCYC is asserted

## **LOCK during HOLD** and **BOFF**

An assertion of HOLD after a locked operation has initiated is ignored by the processor until after the entire locked operation has completed. Following completion, HLDA is asserted.

If BOFF is asserted during the read portion of a locked access, LOCK will float and the entire locked access will be restarted after BOFF is negated. If BOFF is asserted during the write portion of a locked access, LOCK will float and only the write will be restarted after BOFF is negated.

#### **LOCK Operations during Inquire Cycles**

Inquire cycles can be performed as usual during locked operations. Inquire cycles during atomic locked read and write operations are only allowed from the external inquire. No writebacks will be seen because the processor has already evicted the modified line.

The LOCK pin is asserted for the duration of locked accesses. Note also that at least one dead cycle will always be present between consecutive locked atomic read-modify-write operations. This will be noted by the negating of the LOCK pin for at least one clock period between consecutive locked accesses.

## **Locked Operation to Cached Lines**

When a locked operation to a cached line occurs, the processor invalidates the line and determines whether the line is modified. If the line is modified, it is written back to memory.  $\overline{LOCK}$  is not asserted during the writeback operation.  $\overline{LOCK}$  is then asserted and the locked read-modify-write operations are performed. The line is not cached during these operations. SCYC is asserted for misaligned locked transfers.

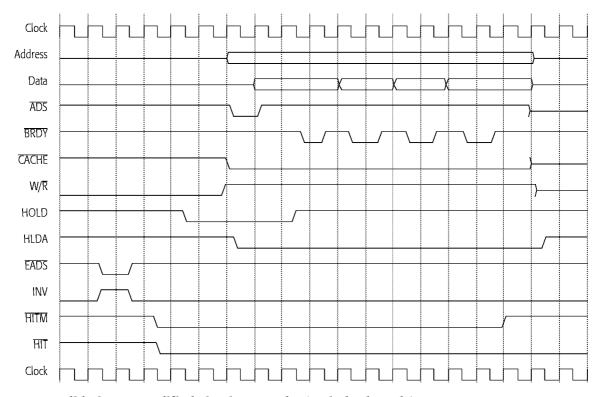

#### **Bus Hold**

HOLD, illustrated in Figure 9 on page 44, is used to inform the processor that another bus device desires to be bus master. If HOLD is asserted, the processor completes all pending bus cycles and acknowledges release of the bus by asserting HLDA. When the bus is released, the processor floats the following outputs:

| • | A31-A3           | • | DP7-DP0                  |

|---|------------------|---|--------------------------|

|   | ADS              |   | $\overline{\text{LOCK}}$ |

|   | AP               |   | $M/\overline{IO}$        |

|   | BE7-BE3          |   | PCD                      |

|   | CACHE            |   | PWT                      |

|   | $D/\overline{C}$ |   | SCYC                     |

|   | D63-D0           | _ | W/R                      |

These are the same outputs that are floated when BOFF is asserted. These outputs provide status information, but do not participate in the external memory system access.

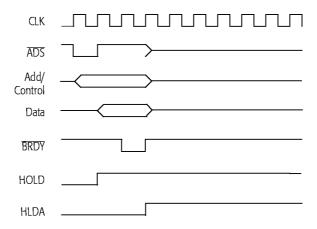

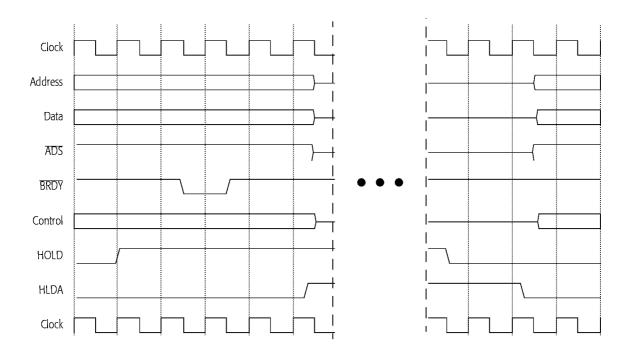

Figure 9. HOLD/HLDA Cycle

HLDA is negated one clock after HOLD is negated. Hold is not recognized during locked cycles, but is recognized during BOFF. An external master must monitor BOFF as well as HLDA to determine bus ownership.

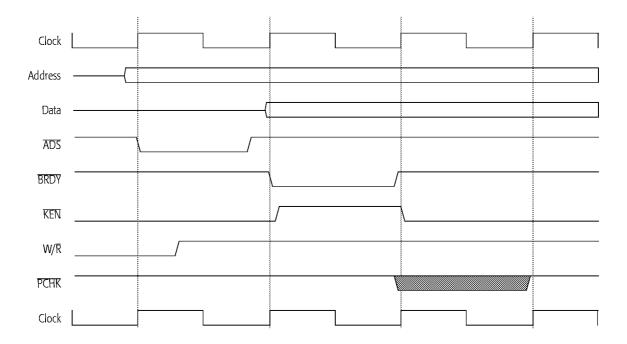

# Bus Error Support using PCHK and APCHK

PCHK and APCHK are used for checking data parity and address parity. Data parity is driven into the processor on pins DP7–DP0 during reads, and is driven out of the same pins during writes. The processor indicates a data parity error by asserting PCHK two clocks after the validation of parity by BRDY.

The AP signal provides even parity for the address bus. The processor indicates an inquire parity error by asserting APCHK two clock cycles after the address is validated by EADS.

#### **Special Bus Cycles**

Several bus cycles are supported by the AMD-K5 processor, as illustrated in Table 6 on page 27. The byte enables are encoded to define the type of cycle. Figure 39 on page 79 is a timing diagram of a generic special bus cycle.

#### **Flush Operations**

The FLUSH input is used by external logic to cause the processor to write back any modified lines in the data cache, and to invalidate all entries in both the data cache and the instruction cache. A special cycle is executed by the processor to indicate completion of the FLUSH operation. The FLUSH input is treated as a high-priority asynchronous interrupt, and is acknowledged only on instruction boundaries.

#### Interrupt Acknowledge

An interrupt acknowledge cycle, shown in Figure 10 on page 45, is a special cycle generated to acknowledge receipt of an interrupt at the INTR input. The processor generates an interrupt acknowledge cycle in a locked pair of transactions. The first transaction acknowledges the interrupt to the external system. The second transaction provides the interrupt vector to the processor. An idle cycle is generated between the transactions. An interrupt acknowledge cycle is completed upon assertion of BRDY. (See Figure 40.)

Figure 10. Interrupt Acknowledge Cycles

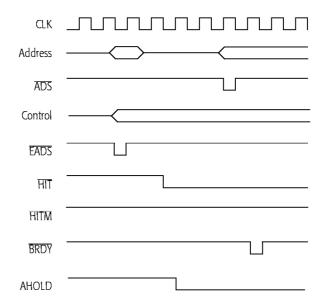

#### **Inquire Cycles**

An inquire cycle is employed to allow the system to determine whether a particular line is cached and modified. After obtaining ownership of the address bus using BOFF, AHOLD, or HOLD, the system drives the physical address of the line on A31–A5, and marks the address valid with EADS.