# HT80C51 User Manual

Handshake Solutions

| Document Information     |                                                                                                                       |                                                                                                             |  |  |  |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Document Title           | HT80C51 User Manual                                                                                                   |                                                                                                             |  |  |  |  |  |  |  |

| Date of Creation         | 27/06/2005                                                                                                            |                                                                                                             |  |  |  |  |  |  |  |

| Date of last change      | 27/06/2005                                                                                                            | 27/06/2005                                                                                                  |  |  |  |  |  |  |  |

| File name                | IT80C51-UserManual.doc                                                                                                |                                                                                                             |  |  |  |  |  |  |  |

| Status                   | Release                                                                                                               |                                                                                                             |  |  |  |  |  |  |  |

| Version Number           | 1.7                                                                                                                   |                                                                                                             |  |  |  |  |  |  |  |

| Client / Target Audience | System architects, and software dev                                                                                   | elopers using the HT80C51                                                                                   |  |  |  |  |  |  |  |

| Summary                  | This document describes and illustandard peripherals and the instruct                                                 | strates the general architecture, the ction set for the HT80C51.                                            |  |  |  |  |  |  |  |

| Contact                  | Handshake Solutions<br>High Tech Campus<br>Prof. Holstlaan 4<br>Mailbox WAM01<br>5656 AA Eindhoven<br>The Netherlands | phone: +31-40-27 46114<br>fax: +31-40-27 46526<br>info@handshakesolutions.com<br>www.handshakesolutions.com |  |  |  |  |  |  |  |

© 2005 Koninklijke Philips Electronics N.V.

All rights reserved. Reproduction in whole or in part in any way, shape or form, is prohibited without the written consent of the copyright owner. All information in this document is subject to change without notice.

# **Table of Contents**

| 1. | Introdu | uction to | HT80C51                                                | 5  |

|----|---------|-----------|--------------------------------------------------------|----|

|    | 1.1.    | Compat    | ibility                                                | 5  |

|    | 1.2.    | Module    | S                                                      | 6  |

| 2. | Memo    | ry Organi | ization                                                | 9  |

|    | 2.1.    | -         | / Мар                                                  |    |

|    | 2.2.    | Access    | ing Program Memory                                     | 10 |

|    | 2.3.    | Access    | ing External Data Memory                               | 10 |

|    | 2.4.    | Internal  | Data Memory: Direct and Indirect Address Area          | 11 |

|    | 2.5.    | Special   | Function Registers                                     | 13 |

|    |         | 2.5.1.    | Accumulator ACC                                        | 14 |

|    |         | 2.5.2.    | Register B                                             | 14 |

|    |         | 2.5.3.    | Program Status Word PSW                                | 14 |

|    |         | 2.5.4.    | Stack Pointer SP                                       | 14 |

|    |         | 2.5.5.    | Data Pointer DPTR DPH DPL                              | 15 |

|    |         | 2.5.6.    | Power Saving Modes PCON                                | 15 |

|    |         | 2.5.7.    | External RAM Page XRAMP (option HT80C51_CPU_XRAMP)     | 17 |

|    | 2.6.    | MOVC p    | protection (option HT80C51_CPU_MOVCP)                  | 17 |

| 3. | Reset   |           |                                                        | 18 |

| 4. | Clocks  | \$        |                                                        | 19 |

|    | 4.1.    | CPU Co    | ck                                                     |    |

|    |         | 4.1.1.    | Clockless (Aynchronous) Cnfiguration                   | 19 |

|    |         | 4.1.2.    | Clock synchronization (Option HT80C51_CPU_SYNC)        | 19 |

|    | 4.2.    | Periphe   | ral clocks                                             | 19 |

| 5. | Periph  |           | ules                                                   |    |

|    | 5.1.    | Interrup  | ot Controller                                          | 20 |

|    |         | 5.1.1.    | Options                                                |    |

|    |         | 5.1.2.    | Special function registers (IEN0 IEN1 IP0 IP1)         | 20 |

|    |         | 5.1.3.    | Operation                                              |    |

|    |         | 5.1.4.    | Setting up the Interrupt Controller                    | 25 |

|    | 5.2.    | Timers    | 0 and 1                                                | 26 |

|    |         | 5.2.1.    | Options                                                | 26 |

|    |         | 5.2.2.    | Special function registers (TMOD TCON TL0 TL1 TH0 TH1) | 26 |

|    |         | 5.2.3.    | Interrupts                                             | 28 |

|    |         | 5.2.4.    | Operation                                              | 29 |

|    |         | 5.2.5.    | Setting up the Timers                                  | 31 |

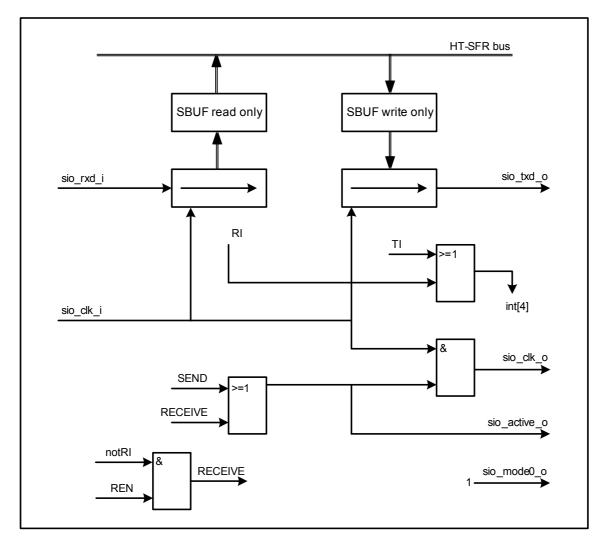

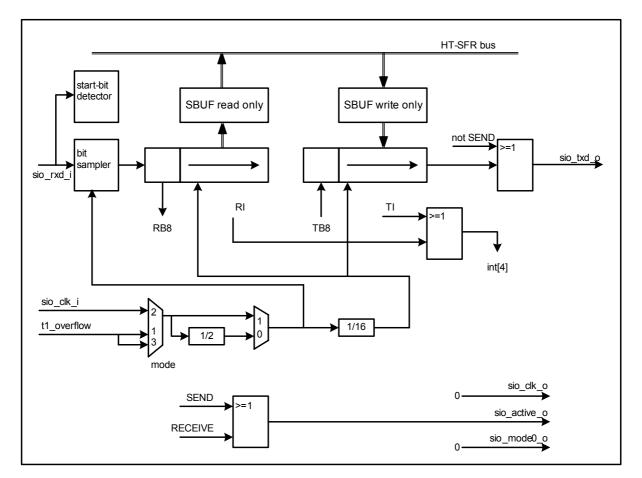

|    | 5.3.    | Standar   | d Serial Interface (SIO0)                              | 33 |

|    |         | 5.3.1.    | Options                                                | 33 |

|    |         | 5.3.2.    | Special function registers (SCON SBUF SMOD)            | 33 |

|     | A3:   | Docume               | ent History                                          | 132 |

|-----|-------|----------------------|------------------------------------------------------|-----|

|     | A2:   | List of F            | -igures                                              | 131 |

|     | A1:   |                      | Tables                                               |     |

| App | -     |                      |                                                      |     |

|     | 6.2.  |                      | ion definitions                                      |     |

|     | 6.1.  |                      | nstruction Set Summary                               |     |

| 6.  | 80C51 |                      | nstruction Set                                       |     |

|     |       | 5.8.5.               | Software view                                        |     |

|     |       | 5.8.4.               | Operation                                            |     |

|     |       | 5.8.3.               | Interrupts                                           |     |

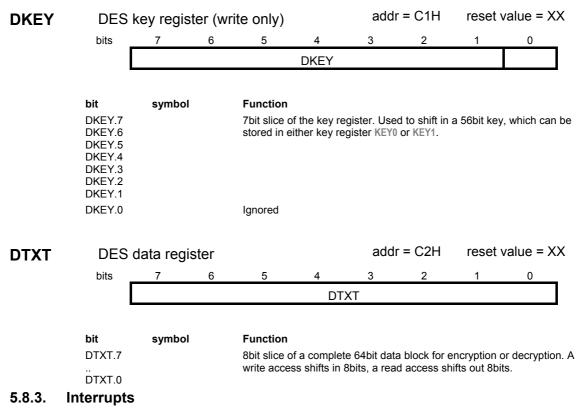

|     |       | 5.8.2.               | Special function registers (DCON DKEY DTXT)          |     |

|     | J.O.  | 5.8.1.               | Options                                              |     |

|     | 5.8.  |                      | Des Converter                                        |     |

|     |       | 5.7.3.<br>5.7.4.     | Operation                                            |     |

|     |       | 5.7.2.<br>5.7.3.     | Special function registers (13)                      |     |

|     |       | 5.7.1.<br>5.7.2.     | Options<br>Special function registers (T3)           |     |

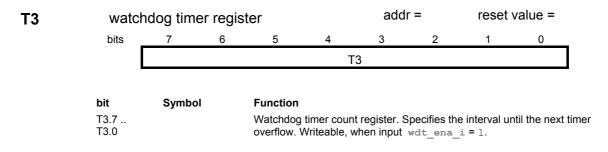

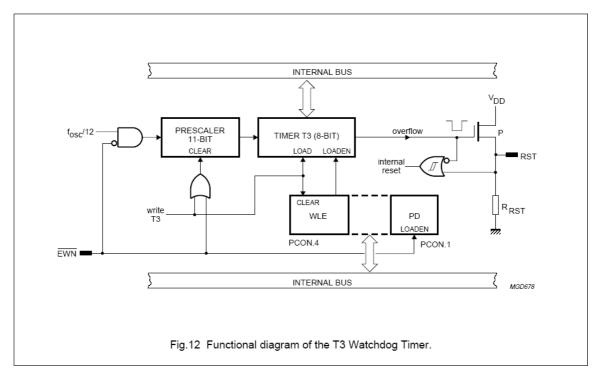

|     | 5.7.  | <b>watchd</b> 5.7.1. | og Timer (under development)                         |     |

|     | E 7   | 5.6.4.               | Operation                                            |     |

|     |       | 5.6.3.               | Interrupts                                           |     |

|     |       | 5.6.2.               | Special function registers (SPCR SPSR SPDR)          |     |

|     |       | 5.6.1.               | Options                                              |     |

|     | 5.6.  |                      | eripheral Interface (SPI)                            |     |

|     |       | 5.5.6.               | Application notes                                    |     |

|     |       | 5.5.5.               | Slave-only version                                   |     |

|     |       | 5.5.4.               | Operation                                            |     |

|     |       | 5.5.3.               | Interrupts                                           |     |

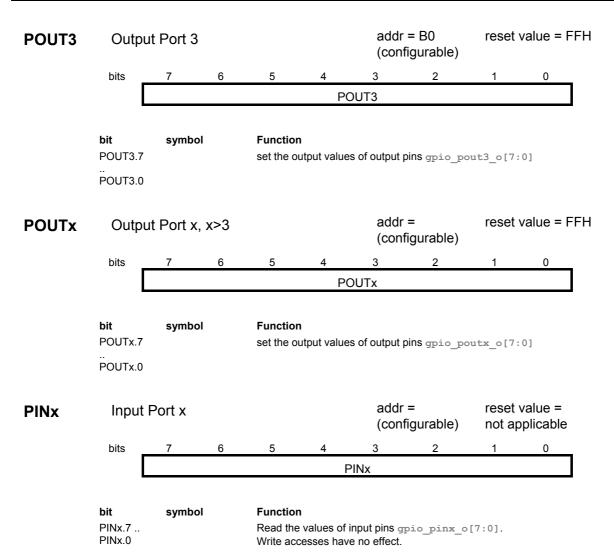

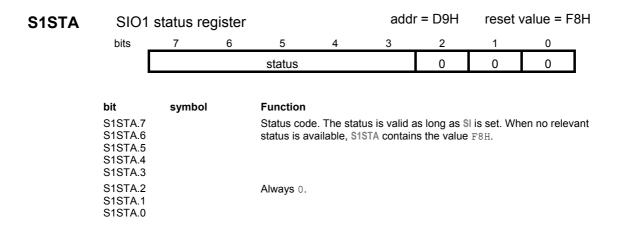

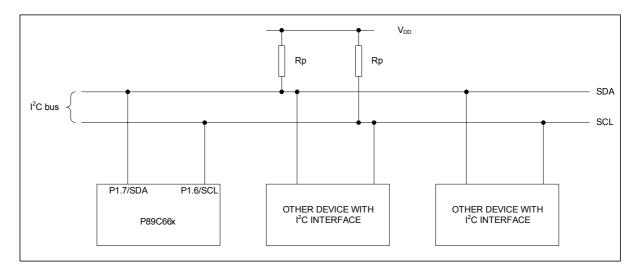

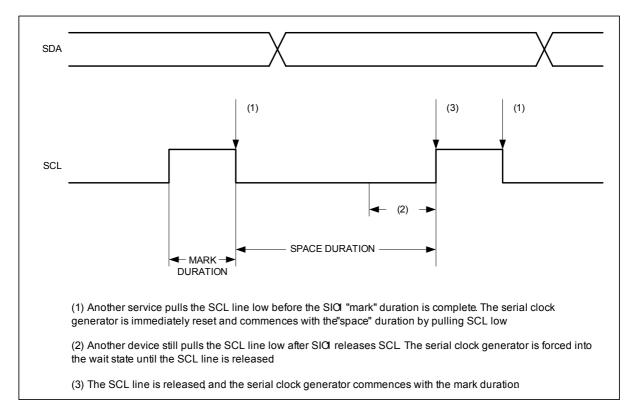

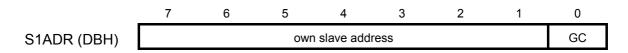

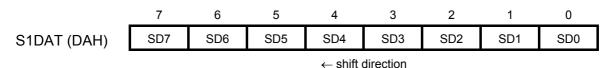

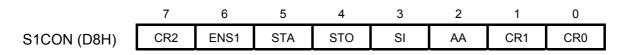

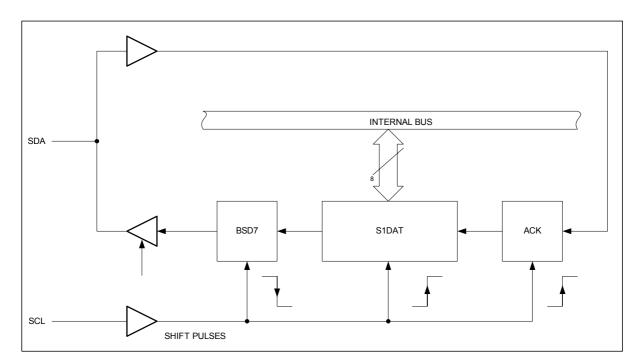

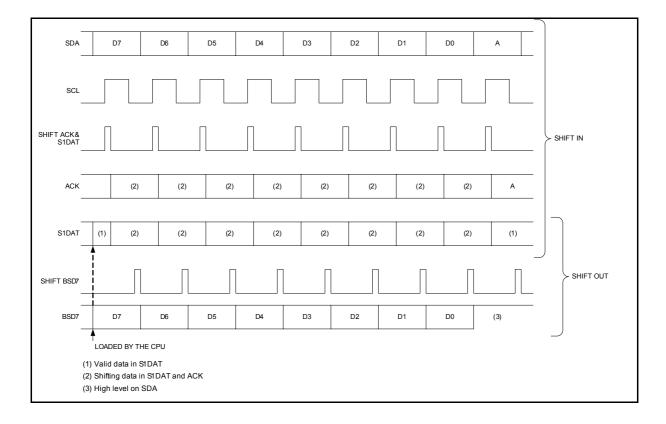

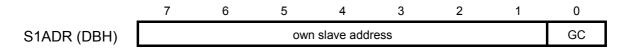

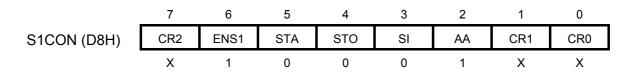

|     |       | 5.5.2.               | Special function registers (S1CON S1ADR S1DAT S1STA) |     |

|     |       | 5.5.1.               | Options                                              |     |

|     | 5.5.  |                      | face (SIO1)                                          |     |

|     |       | 5.4.4.               | Operation                                            |     |

|     |       | 5.4.3.               | Interrupts                                           |     |

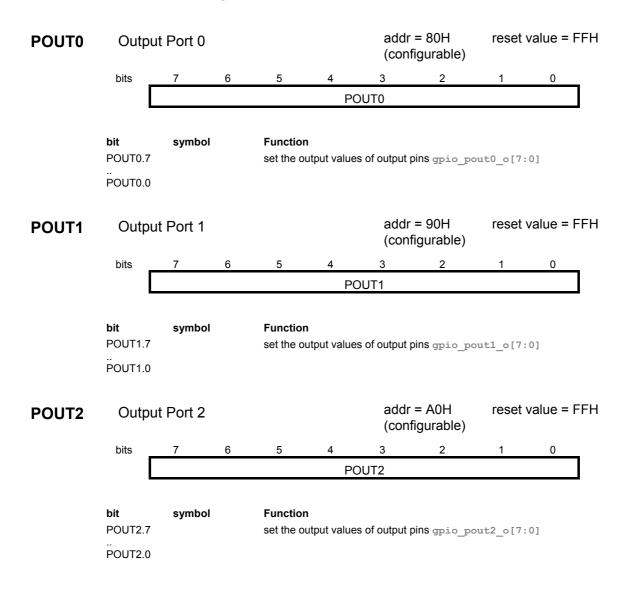

|     |       | 5.4.2.               | Special function registers (POUTx PINx)              | 42  |

|     |       | 5.4.1.               | Options                                              |     |

|     | 5.4.  | General              | Purpose IOs                                          | 42  |

|     |       | 5.3.5.               | Setting up the serial port                           | 40  |

|     |       | 5.3.4.               | Operation                                            |     |

|     |       | 5.3.3.               | Interrupts                                           | 34  |

# 1. Introduction to HT80C51

The Handshake Technology 80C51 (referred to as HT80C51) is an improved version of the ultra lowpower 80C51 (known as ulp80C51). This ulp80C51 has been used in several products such as pagers, game controllers, telephony controllers, and Mifare ProX and SmartMX smart card controllers. Millions of these ICs have been shipped.

The HT80C51 implementation offers several unique features, which are detailed below.

- The HT80C51 is extremely low power (the CPU consumes only 0.1 nano joules per instruction).

- The HT80C51 has very low electromagnetic emission (EME).

- The HT80C51 has low supply-current peaks (at least a factor five lower than traditional, clocked implementations), thus facilitating integration with analog and RF circuitry.

- The HT80C51 CPU consumes zero stand-by power while in sleep mode, yet is immediately available for full-speed full-functional operation.

- The HT80C51 has an asynchronous and optionally a synchronous mode of operation. When both are present, the actual mode can be dynamically selected on an instruction-per-instruction base. This is controlled via a dedicated input.

- In *asynchronous* mode of operation, the CPU runs at its natural speed, and a slow core clock does not slow it down.

- In *synchronous* mode, the CPU synchronizes with a clock on a machine cycle basis after each instruction in such a way that the number of clock cycles for that instruction is the same as the number of machine cycles for a synchronous implementation.

- The HT80C51 core is configurable, and has a range of configuration options, offering selective instantiations of 80C51 peripherals and customization of memory interfaces.

- The HT80C51 peripherals consume zero power when not actively used.

- Optional dual datapointer (for more compact code).

- Optional MOVC protection (only grants program code from lower program memory permission to read lower program memory).

# 1.1. Compatibility

The HT80C51 implementation is functionally compatible to the instruction set and the peripherals of the original 80C51.

The HT80C51 and its peripherals have been designed in Haste, which is the high-level programming language of the Handshake Technology design flow. This design flow is to a large extent technology independent. Mapping onto various VLSI technologies from different vendors is supported.

For production testing, both functional and scan-test version are supported. The scan-test version is compatible with standard ATPG tools.

•

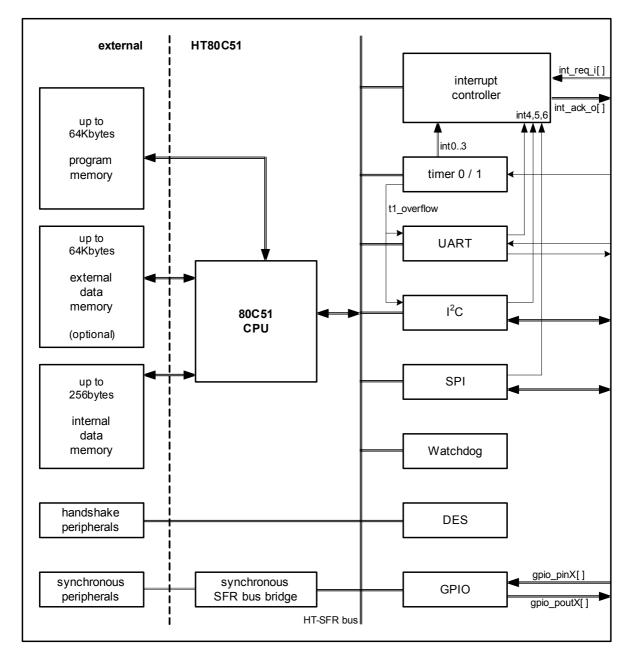

# 1.2. Modules

Following modules are currently available for a HT80C51 microcontroller system

- HT80C51 CPU with optional

- Prefetch unit to increase performance

- Dual datapointer

- MOVC protection

- Synchronization to external clock

- Interrupt controller

- With configurable number of interrupt lines (1 to 15)

- Timer 0 and timer1

- UART

- SPI

- I2C

- Master/slave or

- Slave only

- Watchdog Timer

- DES

- Bridge to synchronous SFR bus

- Supports legacy synchronous peripheral units

Other peripherals are being developed or can be implemented on demand.

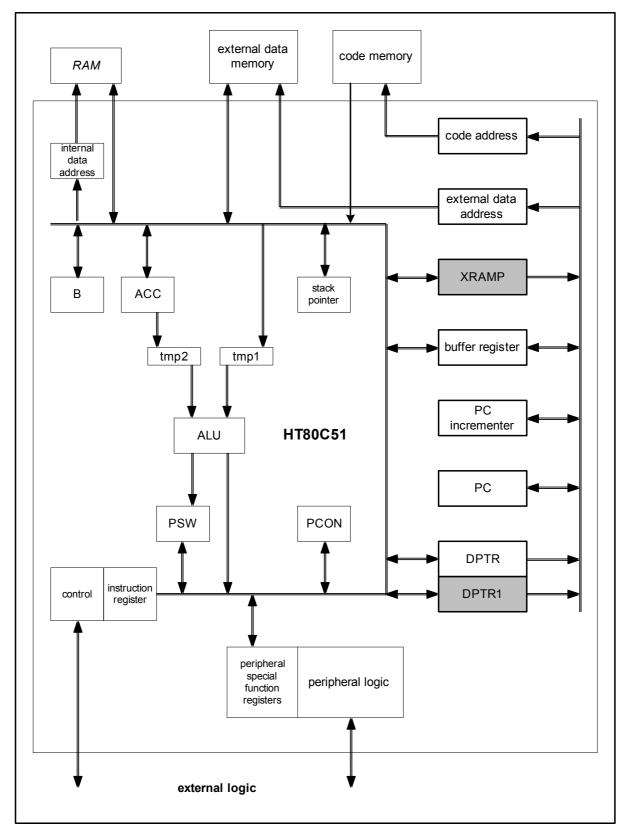

[Figure 1] HT80C51 Architecture (CPU centered)

[Figure 2] HT80C51 Achitecture

# 2. Memory Organization

The 80C51 architecture comprises several different and separated address areas. The following chapter describes the map of these memory areas, which are described in more detail thereafter.

# 2.1. Memory Map

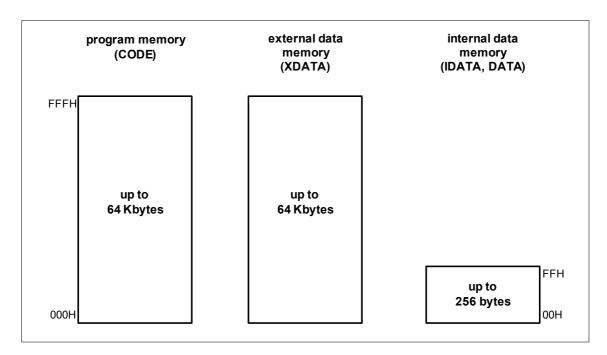

The 80C51 has separate address spaces for program memory, external and internal data memory. [Figure 3] shows a map of the 80C51 memory areas.

[Figure 3] HT80C51 Memory Map

The Program memory (CODE) can be up to 64Kbytes. It can be accessed by instruction fetches and by the MOVC instruction.

The 80C51 can address up to 64k bytes of external data memory (XDATA). Historically this area was located outside the chip (hence the name external), which is usually not the case for embedded systems. The MOVX instruction is used to access the external data memory.

The 80C51 can address up to 256 bytes of on-chip RAM, plus a number of Special Function Registers (SFRs).

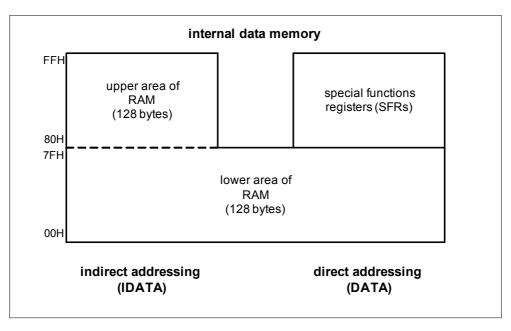

The lower 128 bytes of RAM can be accessed either by direct addressing (MOV data addr) or by indirect addressing (MOV @Ri). The upper 128 bytes of RAM can be accessed by indirect addressing only. Using addresses 80H to FFH with direct addressing accesses the special function registers. [Figure 4] shows the internal data memory organization.

[Figure 4] Memory map of Internal Data

# 2.2. Accessing Program Memory

The program memory is readable only and can be accessed by two access methods:

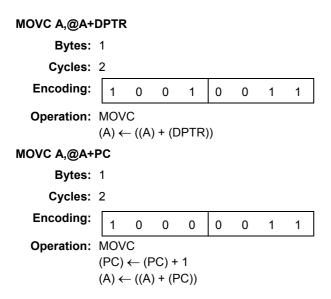

Instruction fetches using the 16bit program counter (PC) as the address or move-code instructions using the 16bit data pointer (MOVC @DPTR) or again the PC (MOVC @PC) as reference.

# 2.3. Accessing External Data Memory

In contrast to the program memory the external data memory is read- and writeable. Accesses to external data memory can be done thru the MOVX-instruction only, which comes in two flavors:

${\tt MOVX} \ {\tt @DPTR}$   $\$ uses the data pointer to form the 16bit address.

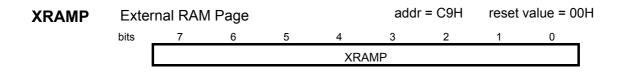

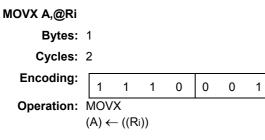

MOVX @Ri uses one of the index registers to form the lower 8bits of the address with the upper part of the address being defined by the SFR XRAMP.

The first variant is usually faster and a more general access method. The second variant (MOVX @Ri) can be used as a paging access to a rather small area of data.

# 2.4. Internal Data Memory: Direct and Indirect Address Area

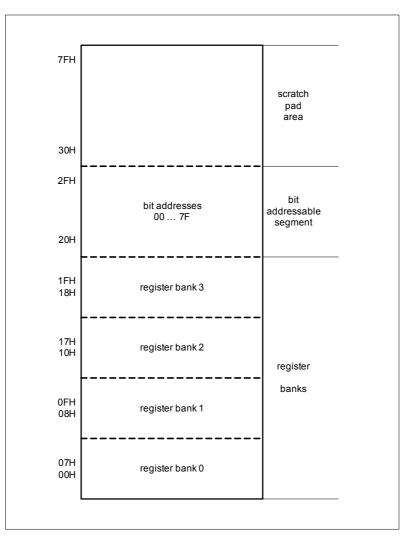

The lower 128 bytes of RAM can be accessed by both direct and indirect addressing and they can be divided into three segments as listed below and shown in [Figure 5].

[Figure 5] Lower 128 bytes of RAM, direct and indirect addressing

# 1. Register Banks 0-3:

Locations 00H through 1FH (32 bytes). The device after reset defaults to register bank 0. To use the other register banks, the user must select them in software. Each register bank contains eight 1-byte registers 0 through 7. Reset initializes the stack pointer to location 07H, and it is incremented once to start from location 08H, which is the first register (R0) of the second register bank. Thus, in order to use more than one register bank, the SP should be initialized to a different location of the RAM where it is not used for data storage (i.e., the higher part of the RAM).

The register bank is selected by bits RS0 and RS1 in the program status word.

### 2. Bit Addressable Area:

16 bytes have been assigned for this segment, 20H-2FH. Each one of the 128 bits of this segment can be directly addressed (0-7FH). The bits can be referred to in two ways, both of which are accept-

able by most assemblers. One way is to refer to their address (i.e., 0-7FH). The other way is with reference to bytes 20H to 2FH. Thus, bits 0-7 can also be referred to as bits 20.0-20.7, and bits 8-FH are the same as 21.0-21.7, and so on. Each of the 16 bytes in this segment can also be addressed as a byte.

#### 3. Scratch Pad Area:

30H through 7FH are available to the user as data RAM. However, if the stack pointer has been initialized to this area, enough bytes should be left aside to prevent overwriting of stack data.

# 2.5. Special Function Registers

The upper address range of the direct addressable data memory is occupied by the special function registers (SFRs). These registers not only serve as data storage, they also have special function for the CPU or peripherals they are attached to. A map of this area is shown in [Figure 6].

| F8 |       |            |          |             |           |      |      |      | FF |

|----|-------|------------|----------|-------------|-----------|------|------|------|----|

| F0 | В     |            |          |             |           | SPCR | SPSR | SPDR | F7 |

| E8 |       |            |          |             |           |      |      |      | EF |

| E0 | ACC   |            |          |             |           |      |      |      | E7 |

| D8 | S1CON | S1STA      | S1DAT    | S1ADR       |           |      |      |      | DF |

| D0 | PSW   |            |          |             |           |      |      |      | D7 |

| C8 |       | XRAMP      |          |             |           |      |      |      | CF |

| C0 |       |            |          |             |           |      |      |      | C7 |

| B8 | IP    |            |          |             |           |      |      |      | BF |

| B0 |       |            |          |             |           |      |      |      | B7 |

| A8 | IE    |            |          |             |           |      |      |      | AF |

| A0 |       |            |          |             |           |      |      |      | A7 |

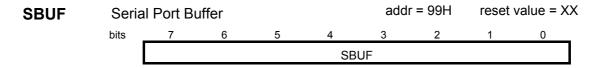

| 98 | SCON  | SBUF       |          |             |           |      |      |      | 9F |

| 90 |       |            |          |             |           |      |      |      | 97 |

| 88 | TCON  | TMOD       | TL0      | TL1         | TH0       | TH1  |      |      | 8F |

| 80 |       | SP         | DPL      | DPH         |           |      |      | PCON | 87 |

|    | ↑ s   | FRs in thi | s column | are bit ado | dressable |      |      |      |    |

[Figure 6] SFR memory map

Note that in the SFR-map not all of the addresses are occupied. Unoccupied addresses are not implemented on the chip. Read accesses to these unimplemented SFR locations will in general return random data, and write accesses will have no effect. User software should not write 1s to these unimplemented locations, since they may be used in other 80C51 Family derivative products to invoke new features.

There are two types of special functions registers: registers, which are part of the CPU and often directly used by certain instructions, and SFRs, which are implemented in peripheral blocks. The SFRs of the CPU are available in all derivatives of this microcontroller and are described in the text below. Peripheral blocks are optional and so are the SFRs, which are implemented inside these peripherals. Therefore the peripheral SFRs are described with the peripheral blocks in Chapter 5.

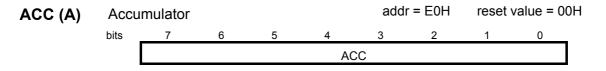

# 2.5.1. Accumulator ACC

ACC is the Accumulator register. The mnemonics for Accumulator-Specific instructions, however, refer to the Accumulator simply as A.

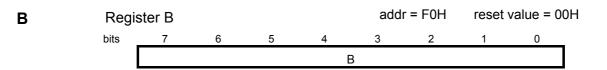

### 2.5.2. Register B

The B-register is used during multiply and divide operations. For other instructions it can be treated as another scratch pad register.

# 2.5.3. Program Status Word PSW

The program status word (PSW) register contains program status information as detailed below.

| PSW | Progr          | am Statu   | us Word                  | ł                                                              |                                                               | addi          | addr = D0H    |          | reset value = 00H                 |  |  |  |

|-----|----------------|------------|--------------------------|----------------------------------------------------------------|---------------------------------------------------------------|---------------|---------------|----------|-----------------------------------|--|--|--|

|     | bits           | 7          | 6                        | 5                                                              | 4                                                             | 3             | 2             | 1        | 0                                 |  |  |  |

|     |                | CY         | AC                       | F0                                                             | RS1                                                           | RS0           | OV            | -        | Р                                 |  |  |  |

|     | L.14           |            |                          | 6                                                              |                                                               |               |               |          |                                   |  |  |  |

|     | bit            | symbol     |                          | function                                                       |                                                               |               |               |          |                                   |  |  |  |

|     | PSW.7          | CY         |                          | Carry Flag                                                     | Carry Flag.                                                   |               |               |          |                                   |  |  |  |

|     | PSW.6          | AC         |                          | Auxiliary C                                                    | Carry Flag.                                                   |               |               |          |                                   |  |  |  |

|     | PSW.5          | F0         |                          | Flag 0 av                                                      | ailable to                                                    | the user fo   | or general    | purpose. |                                   |  |  |  |

|     | PSW.4<br>PSW.3 | RS1<br>RS0 |                          | Register Bank selector bit 1.<br>Register Bank selector bit 0. |                                                               |               |               |          |                                   |  |  |  |

|     |                |            | 0 0<br>0 1<br>1 0<br>1 1 | (RS1, RS0<br>Bank 0<br>Bank 1<br>Bank 2<br>Bank 3              | 0) select the<br>(00H 07F<br>(08H 0FF<br>(10H 17F<br>(18H 1FF | H)<br>H)      | ank as follov | vs:      |                                   |  |  |  |

|     | PSW.3          | RS0        |                          | Register E                                                     | Bank selecto                                                  | or bit 0 (see | note).        |          |                                   |  |  |  |

|     | PSW.2          | OV         |                          | Overflow I                                                     | Flag.                                                         |               |               |          |                                   |  |  |  |

|     | PSW.1          | -          |                          | Usable as                                                      | a general-p                                                   | ourpose flag  | <b>]</b> .    |          |                                   |  |  |  |

|     | PSW.0          | Ρ          |                          |                                                                |                                                               |               |               |          | cle to indicate<br>ans even parit |  |  |  |

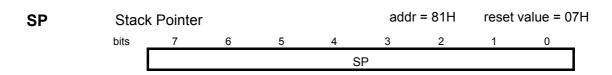

### 2.5.4. Stack Pointer SP

The Stack Pointer (SP) register is 8 bits wide. It is incremented before data is stored during PUSH and CALL executions. While the stack may reside anywhere in on-chip RAM, the Stack Pointer is initialized to 07H after a reset. This causes the stack to begin at locations 08H.

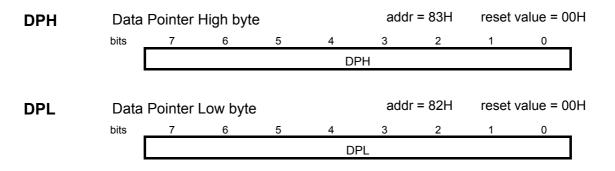

# 2.5.5. Data Pointer DPTR DPH DPL

The Data Pointer (DPTR) consists of a high byte (DPH) and a low byte (DPL). Its intended function is to hold a 16-bit address for MOVX and MOVC instructions. It may be manipulated as a 16-bit register or as two independent 8-bit registers.

### 2.5.5.1. Dual data pointer (option HT80C51\_CPU\_DUALDPTR)

Optional two data pointer registers can be implemented, **DPTR0** and **DPTR1**. Only one data pointer can be used at a time. This can be selected by bit **DPS** in SFR **PCON** (see below).

All instructions using the DPTR, DPL or DPH use either DPTR0 or DPTR1 as selected by SFR bit DPS.

The DPS bit should be saved by software when switching between DPTR0 and DPTR1 within procedures or interrupt routines.

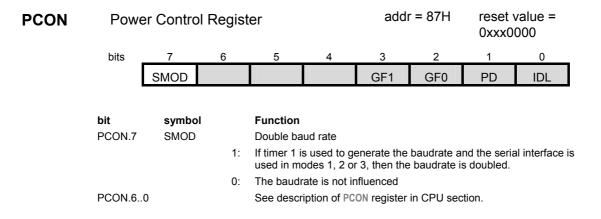

### 2.5.6. Power Saving Modes PCON

The HT80C51 has two power reducing modes, Idle and Power Down. The input through which backup power is supplied during these operations is **VDD**.

In the Idle mode (IDL = 1), the oscillator continues to run and the Interrupt, Serial Port, and Timer blocks continue to be clocked, but the clock signal is gated off to the CPU.

In Power Down (PD = 1), the oscillator is frozen.

Since switching on or off the oscillator is done outside the microcontroller, dedicated output pins indicate idle mode (cpu\_idle\_o) and power down (cpu\_powerdown\_o). External circuits needs to observe these signals to switch off the clocks (in power down) or to change the supply voltage.

Setting bits in Special Function Register PCON activate the Idle and Power Down Modes.

| PCON | Powe             | ver Control Register |          |                                                                                                                                   |                                   |             | r = 87H     |               | reset value =<br>0XX00000 |      |  |

|------|------------------|----------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------|-------------|---------------|---------------------------|------|--|

|      | Bits             | 7                    | 6        | 5                                                                                                                                 | 4                                 | 3           | 2           | 1             | 0                         |      |  |

|      |                  | SMOD                 | -        | -                                                                                                                                 | (DPS)                             | GF1         | GF0         | PD            | IDL                       |      |  |

|      |                  |                      |          |                                                                                                                                   |                                   |             |             |               |                           |      |  |

|      | Bit              | symbol               |          | Function                                                                                                                          |                                   |             |             |               |                           |      |  |

|      | PCON.7           | SMOD                 |          | Double ba                                                                                                                         | ud rate (se                       | e chapter 5 | .3 "Standar | d Serial Inte | erface")                  |      |  |

|      |                  |                      | 1:       | 1: If timer 1 is used to generate the baudrate and the serial interface is used in modes 1, 2 or 3, then the baudrate is doubled. |                                   |             |             |               |                           |      |  |

|      |                  |                      | 0:       | 0: The baudrate is not influenced                                                                                                 |                                   |             |             |               |                           |      |  |

|      | PCON.6<br>PCON.5 | -                    |          | Reserved (write 0, reads 0)                                                                                                       |                                   |             |             |               |                           |      |  |

|      | PCON.4           | (DPS)                |          | Data pointer select; implemented with dual data pointer option, only, otherwise reserved bit (write 0, reads 0)                   |                                   |             |             |               |                           | Ι,   |  |

|      |                  |                      | 1:<br>0: |                                                                                                                                   | rrant for all Di<br>R0 for all DF |             |             |               |                           |      |  |

|      | PCON.3           | GF1                  |          | General-p                                                                                                                         | urpose flag                       | bit.        |             |               |                           |      |  |

|      | PCON.2           | GF0                  |          | General-p                                                                                                                         | urpose flag                       | bit.        |             |               |                           |      |  |

|      | PCON.1           | PD                   |          |                                                                                                                                   | wn bit. Sett<br>icated at ou      |             |             |               | operation, w              | hich |  |

|      | PCON.0           | IDL                  |          |                                                                                                                                   | bit. Setting ated at outp         |             |             | node opera    | tion, which is            | 5    |  |

Note: If 1s are written to PD and IDL at the same time, PD takes precedence.

User software should never write 1s to unimplemented bits, since they may be used in other 80C51 Family products.

#### 2.5.6.1. Idle Mode

An instruction that sets **PCON.0** immediately switches into the idle mode, so no further instruction is executed. The clock signal is gated off from the CPU but not to the Timer and Serial Port functions. The CPU status is preserved in its entirety; the Stack Pointer, Program Counter, Program Status Word, Accumulator, and all other registers maintain their data during Idle.

The port pins hold the logical states they had at the time Idle was activated.

There are two ways to terminate the Idle. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating the idle mode. The interrupt will be serviced, and following RETI, the next instruction to be executed will be the one following the instruction that put the device into Idle. The flag bits GF0 and GF1 can be used to give an indication if an interrupt occurred during normal operation or during an Idle. For example, an instruction that activates Idle can also set one or both flag bits. When Idle is terminated by an interrupt, the interrupt service routine can examine the flag bits.

The other way of terminating the idle mode is with a hardware reset, which starts the processor in the same manner as a power-on reset.

#### 2.5.6.2. Power-Down Mode

An instruction that sets **PCON.1** immediately switches into the Power Down mode. In the Power Down mode, the CPU clock and all peripheral clocks can be stopped completely to lower the power consumption. This has to be done be external circuits, which observe the output pin cpu\_powerdown\_o, that indicates the power down mode. With the clocks frozen, all functions are stopped, the contents of the on-chip RAM and Special Function Registers are maintained. The port pins output the values held by their respective SFRs.

The only exit from Power Down is a hardware reset. Reset redefines all the SFRs, but does not change the on-chip RAM.

In the Power Down mode of operation, VDD can be reduced to a level that is still sufficient for logic and RAM to keep their contents. Care must be taken, however, to ensure that VDD is not reduced before the Power Down mode is invoked, and that VDD is restored to its normal operating level, before the Power Down mode is terminated. The reset that terminates Power Down also should switch on the core clock again. The reset should not be activated before VDD is restored to its normal operating level, and must be held active long enough to allow an oscillator to restart and stabilize.

# 2.5.7. External RAM Page XRAMP (option HT80C51\_CPU\_XRAMP)

The MOVX-instruction comes in two flavors: MOVX @DPTR and MOVX @Ri. For the second version (MOVX @Ri) the contents of one index register Ri specify the lower half of the 16bit address for the access to the external data memory. The upper half is not specified by the instruction, but the SFR XRAMP supplies it. In other words, the external data memory is divided into pages of 256bytes, with XRAMP selecting the page and @Ri addressing within this page.

# 2.6. MOVC protection (option HT80C51\_CPU\_MOVCP)

This optional feature protects a memory region in program memory from being read out by a program outside this region. Thus any MOVC instruction, that is executed outside the protected region and tries to access the protected region, will return the value 00H instead of the real memory content. The protection is only one-way, so a protected program can read the complete program memory area.

The protected region is defined to start at address 0000H. The upper limit of the protected region is defined by static inputs ht80c51\_movcp\_uaddr\_i, so the protected code memory region is from 0000H <= addr < ht80c51\_movcp\_uaddr\_i. The value of this upper limit is under control of the customer, but must not change during execution. Usually it is hard wired to a constant value.

# 3. Reset

The reset input is the  $z_R$  pin. An asynchronous reset is accomplished by holding the  $z_R$  pin low. The minimum low time is not depending on the clock frequency but it depends on the standard cell library, placement and routing. However, usually a reset pulse of about 100ns is sufficient.

A reset initializes most of the SFRs. The following table lists the SFR reset values. The internal RAM is not affected by reset. On power up the RAM content is not defined.

| register             | reset value                      |

|----------------------|----------------------------------|

| PC                   | 0000H                            |

| ACC                  | 00H                              |

| B                    | 00H                              |

| PSW                  | 00H                              |

| SP                   | 07H                              |

| DPTR                 | 0000H                            |

| PCON                 | 0xx0 000                         |

| IEN0                 | оон                              |

| IEN1                 | оон                              |

| IP0                  | оон                              |

| IP1                  | оон                              |

| TMOD                 | 00H                              |

| TCON                 | 00H                              |

| TH0                  | 00H                              |

| TL0                  | 00H                              |

| TH1                  | 00H                              |

| TL1                  | 00H                              |

| SCON                 | оон                              |

| SBUF                 | ХХ                               |

| POUT0                | FFH                              |

| POUT1                | FFH                              |

| POUT2                | FFH                              |

| POUT3                | FFH                              |

| S1CON                | 00H                              |

| S1STA                | F8H                              |

| S1DAT                | 00H                              |

| S1ADR                | 00H                              |

| SPCR                 | 0000 0100                        |

| SPSR                 | 00Н                              |

| SPDR                 | 00Н                              |

| DCON<br>DKEY<br>DTXT | XX<br>XX<br>XX<br>XX             |

| Note: "XX" me        | eans no initialization on reset. |

[Table 1] 80C51 SFR Reset Values

# 4. Clocks

# 4.1. CPU Cock

# 4.1.1. Clockless (Aynchronous) Cnfiguration

A handshake circuit does not require a clock to work, it simply adapts its speed to the environment (other blocks, supply voltage, temperature, etc.). This is a complete asynchronous mode of operation and our standard configuration of the core.

# 4.1.2. Clock synchronization (Option HT80C51\_CPU\_SYNC)

Some applications or programs require a precisely defined timing behavior of the instruction execution, for instance, when timing or waiting loops are used. For this case an optional synchronization feature is offered.

With this feature come two additional input pins: cpu\_clk\_i and cpu\_sync\_i.

cpu\_clk\_i delivers the machine clock and thus the speed of the CPU, input cpu\_sync\_i decides, whether the CPU should be synchronized to cpu\_clk\_i or not:

- In synchronous mode (cpu\_sync\_i=1), the CPU synchronizes with cpu\_clk\_i on a machine cycle basis after each instruction in such a way that the number of clock cycles for that instruction is the same as the number of machine cycles for a synchronous implementation. Since there are no clock dividers attached, one cpu\_clk\_i cycle equals to one machine cycle.

- In *asynchronous* mode of operation (cpu\_sync\_i=0), the CPU runs at its natural speed, and a slow cpu\_clk\_i does not slow it down.

# 4.2. Peripheral clocks

In a traditional (synchronous) 80C51 system, all clocks for peripherals are derived from the clock for the CPU or from the CPU's machine cycle, which is usually 1/12 or 1/6 of the CPU clock frequency, depending on the implementation of the CPU. Hence all timing specifications like timer overflow times or baud rates were specified in relation to the CPU clock.

In a handshake design no single, global clock source is needed, the clock for the CPU can even be omitted (which is the standard configuration for the HT80C51). Thus for each peripheral that needs a clock, e.g. timers, serial interfaces or the synchronous SFR bus, a dedicated clock input is provided. So the optimum clock frequency can be supplied to each peripheral, completely independent from all other clock frequencies. Also note, that there is no internal clock divider implemented (divide by 12 or 6). Thus, compared to a synchronous design, the same timings (e.g. baud rates) can be achieved with a lower input clock frequency resulting in lower power consumption.

The timing specifications of the peripherals are related to their specific input clock frequencies.

# 5. Peripheral Modules

For the HT80C51 a number of standard peripherals like timers and serial interfaces exist. They are compatible to the standard peripherals in synchronous implementations. The peripherals can be ordered along with the CPU and are then part of a combined delivery. The following chapters describe these peripherals in detail with further options (if available) and their SFRs.

# 5.1. Interrupt Controller

This module handles the enabling and priority decoding of interrupt requests as well as entering and leaving the interrupt routines. The number of interrupt inputs can be configured from 0 up to 15.

# 5.1.1. Options

The interrupt controller can be ordered by option HT80C51\_INT.

The number of interrupt inputs int\_req\_i can be selected (ordered) by using option HT80C51\_INT\_COUNT.

# 5.1.2. Special function registers (IEN0 IEN1 IP0 IP1)

The number of implemented SFRs for the interrupt controller and even the number of bits within these SFRs depends on the selected number of interrupt inputs. For each interrupt input int\_req\_i[x] one interrupt enable bit and one interrupt priority bit exists. All interrupt enable bits are collected in two SFRs: IEN0 and IEN1. All interrupt priority bits are collected in further two SFRs: IP0 and IP1.

If the number of interrupt inputs is greater than 0, SFRs IEN0 and IP0 exist.

If the number of interrupt inputs is greater than 7, SFRs IEN1 and IP1 exist, too.

| IEN0<br>(IE) | Interrupt enable regist |            |            |                                                                                                |               | addı                                                          | addr = A8H     |               | reset value = 00H |    |  |  |

|--------------|-------------------------|------------|------------|------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------|----------------|---------------|-------------------|----|--|--|

|              | bits                    | 7          | 6          | 5                                                                                              | 4             | 3                                                             | 2              | 1             | 0                 |    |  |  |

|              |                         | EA         | IEN0.6     | ES1                                                                                            | ES0           | ET1                                                           | EX1            | ET0           | EX0               |    |  |  |

|              |                         |            |            |                                                                                                |               |                                                               |                |               |                   |    |  |  |

|              | bit                     | symbo      | bl         | Function                                                                                       |               |                                                               |                |               |                   |    |  |  |

|              | IEN0.7                  | EA         | 1:<br>0:   | Any indivi                                                                                     |               | e control. If EA = 0,<br>ed interrupt will be accepted.<br>d. |                |               |                   |    |  |  |

|              | IEN0.6                  |            |            | Enable int                                                                                     | errupt input  | int_req_                                                      | int_req_i[6].  |               |                   |    |  |  |

|              | IEN0.5                  | ES1        |            | Enable I20                                                                                     | C interrupt ( | if available)                                                 | or interrup    | t input int_  | _req_i[5].        |    |  |  |

|              | IEN0.4                  | ES0        |            | Enable UA                                                                                      | ART interrup  | ot (if availab                                                | ole) or interr | upt input in  | nt_req_i[4        | ]. |  |  |

|              | IEN0.3                  | ET1        |            | Enable tin                                                                                     |               | ow interrupt                                                  | (if available  | e) or interru | pt input          |    |  |  |

|              | IEN0.2                  | EX1        |            | Enable external interrupt from timer 1 (IE1) (if available) or interrupt input int req i[2].   |               |                                                               |                |               |                   |    |  |  |

|              | IEN0.1                  | ET0        |            | Enable timer 0 overflow interrupt (if available) or interrupt input int_req_i[1].              |               |                                                               |                |               |                   |    |  |  |

|              | IEN0.0                  | EX0        |            | Enable external interrupt from timer 0 (IE0) (if available) or interrup<br>input int_req_i[0]. |               |                                                               |                |               |                   |    |  |  |

|              | Bit value               | s: 0 = int | errupt dis | sabled; 1                                                                                      | = interru     | ot enable                                                     | d.             |               |                   |    |  |  |

| IEN1 | Interr    | upt enal   | ble regis  | ter 1                                                                                                                             |               | add            | addr = E8H     |                                   | reset value = 00H |      |

|------|-----------|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|----------------|-----------------------------------|-------------------|------|

|      | bits      | 7          | 6          | 5                                                                                                                                 | 4             | 3              | 2              | 1                                 | 0                 |      |

|      | ſ         | IEN1.7     | IEN1.6     | IEN1.5                                                                                                                            | IEN1.4        | IEN1.3         | IEN1.2         | IEN1.1                            | IEN1.0            |      |

|      | •         |            | •          |                                                                                                                                   |               |                |                |                                   |                   |      |

|      | bit       | symbo      | N          | Function                                                                                                                          |               |                |                |                                   |                   |      |

|      | IEN1.7    | Symbo      | <i>,</i>   |                                                                                                                                   | errunt innut  | t "int_req_i[  | 141"           |                                   |                   |      |

|      | IEN1.6    |            |            |                                                                                                                                   |               | t "int reg if  |                |                                   |                   |      |

|      | IEN1.5    |            |            |                                                                                                                                   | • •           | t "int_req_i[  | -              |                                   |                   |      |

|      | IEN1.4    |            |            |                                                                                                                                   |               | t "int_req_i[  |                |                                   |                   |      |

|      | IEN1.3    |            |            |                                                                                                                                   |               | "int_req_i     | -              |                                   |                   |      |

|      | IEN1.2    |            |            |                                                                                                                                   |               | "int_req_i     | -              |                                   |                   |      |

|      | IEN1.1    |            |            |                                                                                                                                   |               | t "int_req_i   | -              |                                   |                   |      |

|      | IEN1.0    |            |            | Enable int                                                                                                                        | errupt input  | t "int_req_i[  | -<br>7]".      |                                   |                   |      |

|      | Bit value | s: 0 = int | errupt dis | sabled; 1                                                                                                                         | = interru     | ot enable      | d.             |                                   |                   |      |

|      |           |            |            |                                                                                                                                   |               |                |                |                                   |                   |      |

|      | latorr    | unt prio   | it roaio   | tor 0                                                                                                                             |               | bhe            | r = B8H        | reset                             | value = 00        | าน   |

| IP0  | Intern    | upt prio   | rity regis |                                                                                                                                   |               | auu            |                | 10301                             |                   | ///  |

| (IP) |           |            |            |                                                                                                                                   |               |                |                |                                   |                   |      |

|      | bits      | 7          | 6          | 5                                                                                                                                 | 4             | 3              | 2              | 1                                 | 0                 |      |

|      |           | -          | IP0.6      | PS1                                                                                                                               | PS0           | PT1            | PX1            | PT0                               | PX0               |      |

|      |           |            |            |                                                                                                                                   |               |                |                |                                   |                   |      |

|      | bit       | symbo      | bl         | Function                                                                                                                          |               |                |                |                                   |                   |      |

|      | IP0.7     | -          |            | reserved.                                                                                                                         |               |                |                |                                   |                   |      |

|      | IP0.6     |            |            | Priority lev                                                                                                                      | el for interr | upt input in   | nt_req_i[      | 6].                               |                   |      |

|      | IP0.5     | ES1        |            |                                                                                                                                   |               | nterrupt (if a | available) or  | interrupt ir                      | nput              |      |

|      |           |            |            | int_req_                                                                                                                          |               |                |                |                                   |                   |      |

|      | IP0.4     | ES0        |            | Priority lev                                                                                                                      |               | I interrupt (  | (if available) | or interrup                       | t input           |      |

|      | IP0.3     | ET1        |            |                                                                                                                                   | _             | 1 overflow     | interrupt (if  | available)                        | or interrupt i    | nput |

|      |           |            |            | int_req_                                                                                                                          |               |                |                | ,                                 |                   |      |

|      | IP0.2     | EX1        |            | Priority level for external interrupt from timer 1 (IE1) (if available) or<br>interrupt input int_req_i[2].                       |               |                |                |                                   |                   |      |

|      | IP0.1     | ET0        |            | Priority lev                                                                                                                      | el for timer  | _              | interrupt (if  | (if available) or interrupt input |                   |      |

|      | IP0.0     | EX0        |            | <pre>int_req_i[1]. Priority level for external interrupt from timer 0 (IE0) (if available) or interrupt input int_req_i[0].</pre> |               |                |                |                                   |                   |      |

Bit values: 0 = 1 low priority; 1 = 1 high priority.

| IP1 | Interr    | upt prior  | ity regis  | ter 1                                             |               | addi         | r = F8H   | reset value = 00H |       |  |  |  |

|-----|-----------|------------|------------|---------------------------------------------------|---------------|--------------|-----------|-------------------|-------|--|--|--|

|     | bits      | 7          | 6          | 5                                                 | 4             | 3            | 2         | 1                 | 0     |  |  |  |

|     |           | IP1.7      | IP1.6      | IP1.5                                             | IP1.4         | IP1.3        | IP1.2     | IP1.1             | IP1.0 |  |  |  |

|     |           |            |            |                                                   |               |              |           |                   |       |  |  |  |

|     | bit       | symbo      | )          | Function                                          |               |              |           |                   |       |  |  |  |

|     | IP1.7     |            |            | Priority level for interrupt input int_req_i[14]. |               |              |           |                   |       |  |  |  |

|     | IP1.6     |            |            | Priority level for interrupt input int_req_i[13]. |               |              |           |                   |       |  |  |  |

|     | IP1.5     |            |            | Priority level for interrupt input int_req_i[12]. |               |              |           |                   |       |  |  |  |

|     | IP1.4     |            |            | Priority lev                                      | el for interr | upt input in | nt_req_i[ | 11].              |       |  |  |  |

|     | IP1.3     |            |            | Priority level for interrupt input int req i[10]. |               |              |           |                   |       |  |  |  |

|     | IP1.2     |            |            | Priority level for interrupt input int req i [9]. |               |              |           |                   |       |  |  |  |

|     | IP1.1     |            |            | Priority lev                                      | el for interr | upt input ir | nt_req_i[ | 8].               |       |  |  |  |

|     | IP1.0     |            |            | Priority lev                                      | el for interr | upt input ir | nt_req_i[ | 7].               |       |  |  |  |

|     | Bit value | s: 0 = lov | v priority | ; 1 = high                                        | priority.     |              |           |                   |       |  |  |  |

#### 5.1.3. Operation

The HT80C51 provides up to 15 interrupt inputs. Depending on the configuration of standard peripherals, some of these inputs are already internally connected to interrupt sources in these peripherals. For a description of these interrupt sources, please, see the description of the peripheral blocks. [Table 2] shows these default connections.

All of the bits that generate interrupts can be set or cleared by software, with the same result as though it had been set or cleared by hardware. That is, interrupts can be generated or pending interrupts can be canceled in software.

Each of these interrupt sources can be individually enabled or disabled by setting or clearing a bit in Special Function Registers IEN0 and IEN1. IEN0 also contains a global disable bit, EA, which disables all interrupts at once.

#### 5.1.3.1. Interrupt Priority Level Structure

Each interrupt source can also be individually programmed to one of two priority levels by setting or clearing a bit in Special Function Registers IP0 and IP1. A low-priority interrupt can itself be interrupted by a high-priority interrupt, but not by another low-priority interrupt. A high-priority interrupt can't be interrupted by any other interrupt source.

If two requests of different priority levels are received simultaneously, the request of higher priority level is serviced. If requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence, as summarized in [Table 2].

| interrupt | interrupt<br>input | cor      | ard internal<br>nection<br>eral is selected) | vector<br>address | enable | priority<br>select | priority<br>within<br>level |

|-----------|--------------------|----------|----------------------------------------------|-------------------|--------|--------------------|-----------------------------|

| int 0     | int_req_i[0]       | IE0      | timer 0                                      | 0003H             | IEN0.0 | IP0.0              | highest                     |

| int 1     | int_req_i[1]       | TF0      | timer 0                                      | 000BH             | IEN0.1 | IP0.1              |                             |

| int 2     | int_req_i[2]       | IE1      | timer 1                                      | 0013H             | IEN0.2 | IP0.2              |                             |

| int 3     | int_req_i[3]       | TF1      | timer 1                                      | 001BH             | IEN0.3 | IP0.3              |                             |

| int 4     | int_req_i[4]       | RI or TI | SI0(UART)                                    | 0023H             | IEN0.4 | IP0.4              |                             |

| int 5     | int_req_i[5]       | SI       | I2C                                          | 002BH             | IEN0.5 | IP0.5              |                             |

| int 6     | int_req_i[6]       | SPIF     | SPI                                          | 0033H             | IEN0.6 | IP0.6              |                             |

| int 7     | int_req_i[7]       |          |                                              | 003BH             | IEN1.0 | IP1.0              |                             |

| int 8     | int_req_i[8]       |          |                                              | 0043H             | IEN1.1 | IP1.1              |                             |

| int 9     | int_req_i[9]       |          |                                              | 004BH             | IEN1.2 | IP1.2              |                             |

| int 10    | int_req_i[10]      |          |                                              | 0053H             | IEN1.3 | IP1.3              |                             |

| int 11    | int_req_i[11]      |          |                                              | 005BH             | IEN1.4 | IP1.4              |                             |

| int 12    | int_req_i[12]      |          |                                              | 0063H             | IEN1.5 | IP1.5              |                             |

| int 13    | int_req_i[13]      |          |                                              | 006BH             | IEN1.6 | IP1.6              |                             |

| int 14    | int_req_i[14]      |          |                                              | 0073H             | IEN1.7 | IP1.7              | lowest                      |

Note: The "priority within level" structure is only used to resolve simultaneous requests of the same priority level.

| Table 21 | Interrupt Signals, Vectors and Priorities. |  |

|----------|--------------------------------------------|--|

|          |                                            |  |

### 5.1.3.2. How Interrupts Are Handled

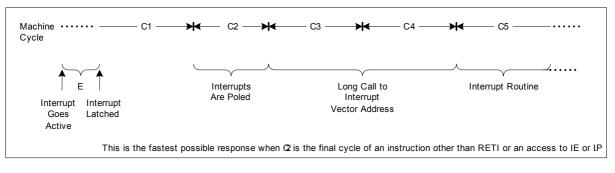

The interrupt flags are sampled at every start of an instruction. The samples are polled at the start of the following instruction. If one of the flags was in a set condition at the preceding cycle, the polling cycle will find it and the interrupt system will generate an LCALL to the appropriate service routine, provided this hardware-generated LCALL is not blocked by any of the following conditions:

- 1. An interrupt of equal or higher priority level is already in progress.

- 2. The instruction in progress is RETI or any write to the IENx or IPx registers.

Any of these two conditions will block the generation of the LCALL to the interrupt service routine. Condition 2 ensures that if the instruction in progress is RETI or any access to IENx or IPx, then at least one more instruction will be executed before any interrupt is vectored to.

The polling cycle is repeated with each new instruction, and the values polled are the values that were present at the start of the previous instruction. Note that if an interrupt flag is active but not being responded to for one of the above conditions, if the flag is not still active when the blocking condition is removed, the denied interrupt will not be serviced. In other words, the fact that the interrupt flag was once active but not serviced is not remembered. Every polling cycle is new.

[Figure 7] Interrupt Response Timing Diagram

The polling cycle/LCALL sequence is illustrated in [Figure 7]. Note that if an interrupt of higher priority level goes active prior to the instruction labeled C3 in [Figure 7], then in accordance with the above rules it will be vectored to during C5 and C6, without any instruction of the lower priority routine having been executed.

Thus the processor acknowledges an interrupt request by executing a hardware-generated LCALL to the appropriate servicing routine. In some cases it also clears the flag that generated the interrupt, and in other cases it doesn't. It never clears the Serial Port flag. This has to be done in the user's software. It clears an external interrupt flag (IE0 or IE1) only if it was transition-activated. The hardware-generated LCALL pushes the contents of the Program Counter on to the stack (but it does not save the **PSW**) and reloads the PC with an address that depends on the source of the interrupt being vectored to, as shown in column "vector address" in [Table 2].

Execution proceeds from that location until the RETI instruction is encountered. The RETI instruction informs the processor that this interrupt routine is no longer in progress, then pops the top two bytes from the stack and reloads the Program Counter. Execution of the interrupted program continues from where it left off. Note that a simple RET instruction would also have returned execution to the interrupted program, but it would have left the interrupt control system thinking an interrupt was still in progress, making future interrupts impossible.

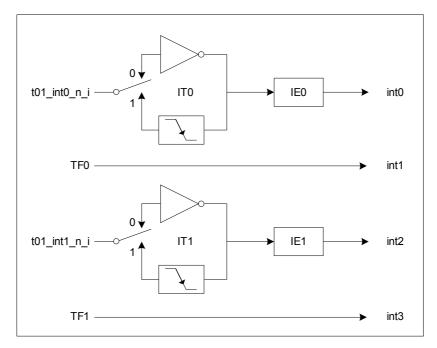

### 5.1.3.3. External Interrupts

The external sources can be programmed to be level-activated or transition-activated by setting or clearing bit IT1 or IT0 in Register TCON. If ITx = 0, external interrupt x is triggered by a detected low at the t01\_intx\_n\_i pin. If ITx = 1, external interrupt x is edge triggered. In this mode if the interrupt input (t01\_int0\_n\_i for IT0, t01\_int1\_n\_i for IT1) shows a high to low transition, interrupt request flag IEx in TCON is set. Flag bit IEx then requests the interrupt. Since the external interrupt pins are not sampled, there is no minimum low duration specified. IEx will be automatically cleared by the CPU when the service routine is called.

If the external interrupt is level-activated, the external source has to hold the request active until the requested interrupt is actually generated. Then it has to deactivate the request before the interrupt service routine is completed, or else another interrupt will be generated.

# 5.1.3.4. Response Time

The t01\_int0\_n\_i and t01\_int1\_n\_i levels are inverted and latched into IE0 and IE1. The values are not actually polled by the circuitry until the next start of an instruction. If a request is active and conditions are right for it to be acknowledged, a hardware subroutine call to the requested service routine will be the next instruction to be executed. The call itself takes two cycles. Thus, a minimum of three complete machine cycles elapse between activation of an external interrupt request and the beginning of execution of the first instruction of the service routine.

A longer response time would result if the request were blocked by one of the 2 previously listed conditions. If an interrupt of equal or higher priority level is already in progress, the additional wait time obviously depends on the nature of the other interrupt's service routine. If the instruction in progress is not in its final cycle, the additional wait time cannot be more the 3 cycles, since the longest instructions (MUL and DIV) are only 4 cycles long, and if the instruction in progress is RETI or an access to IE or IP, the additional wait time cannot be more than 5 cycles (a maximum of one more cycle to complete the instruction in progress, plus 4 cycles to complete the next instruction if the instruction is MUL or DIV).

Thus, in a single-interrupt system, the response time is always more than 3 cycles and less than 9 cycles.

# 5.1.4. Setting up the Interrupt Controller

To use any of the interrupts in the 80C51 Family, the following three steps must be taken.

- 1. Set the EA (enable all) bit in the IE register to 1.

- 2. Set the corresponding individual interrupt enable bit in the IE register to 1.

- 3. Begin the interrupt service routine at the corresponding Vector Address of that interrupt (see [Table 2]).

In addition, for external interrupts (input pins  $t01\_int0\_n\_i$  and  $t01\_int1\_n\_i$ ) depending on whether the interrupt is to be level or transition activated, bits IT0 or IT1 in the TCON register may need to be set to 1.

ITx = 0 level activated

ITx = 1 transition activated

### 5.1.4.1. Assigning a Higher Priority to One or More Interrupts

In order to assign higher priority to an interrupt, the corresponding bit in the IPx register must be set to 1.

Remember that while an interrupt service is in progress, it cannot be interrupted by a lower or same level interrupt.

# 5.2. Timers 0 and 1

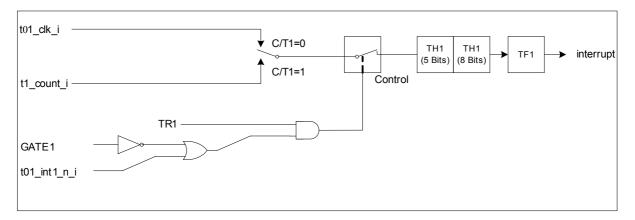

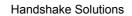

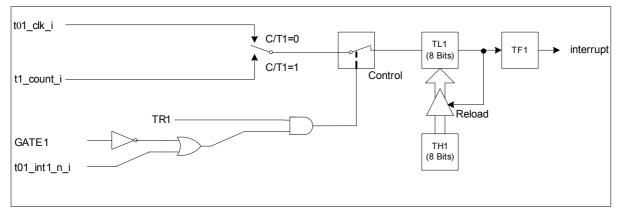

This module comprises two 16bit timers/counters: timer0 and timer1. Both can be configured to operate either as timers or event counters.

In the "Timer" function, the register is incremented every timer clock cycle (clock input t01\_clk\_i). Thus, if the operation of the CPU is synchronized to the same clock, one can think of it as counting machine cycles of the CPU.

In the "Counter" function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, to\_count\_i or t1\_count\_i. By design there are no restrictions on the duty cycle or the frequency of the external input signals. However, depending on the standard cell library, that is used, and the actual layout some maximum limits will apply.

# 5.2.1. Options

This module can be enabled (ordered) by using option HT80C51\_T01.

### 5.2.2. Special function registers (TMOD TCON TL0 TL1 TH0 TH1)

| TMOD | Time             | r/Counter              | Mode                     | Control                                                                                                                                                                                                                                                       |                                                              | addr = 89H                                  |                                            | reset value = 00H                         |                                     |

|------|------------------|------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------|--------------------------------------------|-------------------------------------------|-------------------------------------|

|      | bits             | 7                      | 6                        | 5                                                                                                                                                                                                                                                             | 4                                                            | 3                                           | 2                                          | 1                                         | 0                                   |

|      |                  | GATE1                  | C/T1                     | T1M1                                                                                                                                                                                                                                                          | T1M0                                                         | GATE0                                       | C/T0                                       | T0M1                                      | томо                                |

|      |                  |                        |                          |                                                                                                                                                                                                                                                               |                                                              |                                             |                                            |                                           |                                     |

|      | bit<br>TMOD.7    | <b>symbol</b><br>GATE1 | 1:                       |                                                                                                                                                                                                                                                               | ating contro<br>Inter 1 is er                                |                                             | while input                                | pin t01_ir                                | nt1_n_i is high                     |

|      |                  |                        | 0:                       |                                                                                                                                                                                                                                                               | inter 1 is er                                                | abled if TR1                                | is set.                                    |                                           |                                     |

|      | TMOD.6           | C/T1                   | 1:<br>0:                 | counter op                                                                                                                                                                                                                                                    |                                                              | ection<br>ock source is<br>source is th     |                                            |                                           |                                     |

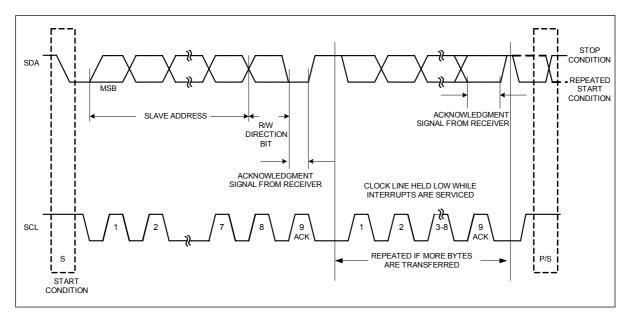

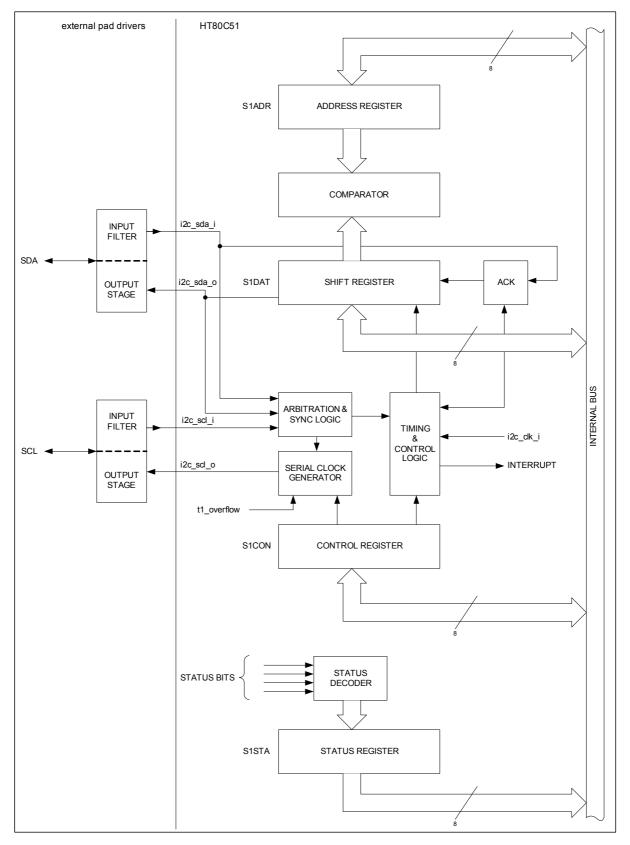

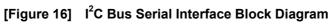

|      | TMOD.5<br>TMOD.4 | T1M1<br>T1M0           | 00:<br>01:<br>10:<br>11: | Timer 1 mode selection<br>8048 timer mode, TL1 serves as a 5bit prescaler<br>16bit timer/counter: TH1 and TL1 are cascaded; no prescaler<br>8bit auto-reload timer/counter: TH1 holds the value which is loaded into<br>TL1 each time it overflows<br>stopped |                                                              |                                             |                                            |                                           |                                     |