# Am2964B

# **Dynamic Memory Controller**

#### DISTINCTIVE CHARACTERISTICS

- Dynamic Memory Controller for 16K and 64K MOS dynamic RAMs

- 8-Bit Refresh Counter for refresh address generation, has clear input and terminal count output

- Refresh Counter terminal count selectable at 256 or 128

- Latch input RAS Decoder provides 4 RAS outputs, all active during refresh

- Dual 8-Bit Address Latches plus separate RAS Decoder

Latches

- Burst mode, distributed refresh or transparent refresh mode determined by user

# **GENERAL DESCRIPTION**

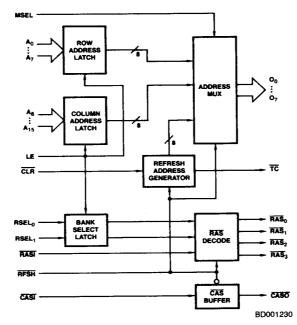

The Am2964B Dynamic Memory Controller (DMC) replaces a dozen MSI devices by grouping several unique functions. Two 8-bit latches capture and hold the memory address. These latches and a clearable, 8-bit refresh counter feed into an 8-bit, 3-input, Schottky speed MUX for output to the dynamic RAM address lines.

The same silicon chip also includes a special RAS decoder and CAS buffer. Placing these functions on the same chip minimizes the time skew between output functions which would otherwise be separate MSI chips, and therefore allows a faster memory cycle time by the amount of skew eliminated.

The RAS Decoder allows upper addresses to select one-offour banks of RAM by determining which bank receives a RAS input. During refresh (RFSH = LOW) the decoder mode is changed to four-of-four and all banks of memory receive a RAS input for refresh in response to a RASI active LOW input. CAS is inhibited during refresh.

Burst mode refresh is accomplished by holding  $\overline{\text{RFSH}}$  LOW and toggling  $\overline{\text{RASI}}$ .

$A_{15}$  is a dual function input which controls the refresh counter's range. For 64K RAMs it is an address input. For 66K RAMs it can be pulled to +12V through  $1K\Omega$  to terminate the refresh count at 128 instead of 256.

# **BLOCK DIAGRAM**

IMOX is a trademark of Advanced Micro Devices, Inc.

Publication# 03527 Rev. C Amendment 70 Issue Date: January 1990

6-66

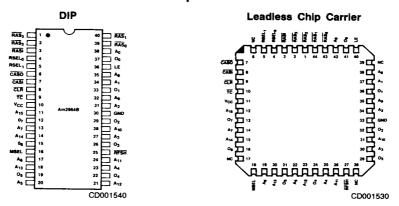

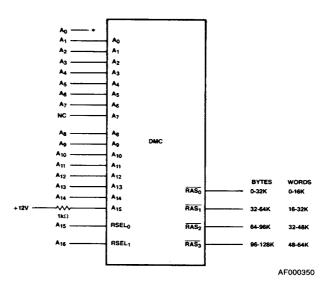

# CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation.

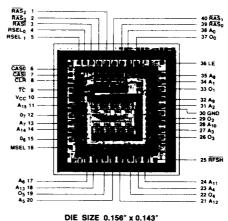

# **METALLIZATION AND PAD LAYOUT**

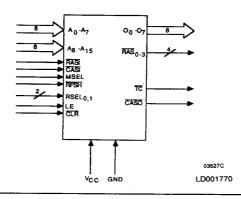

LOGIC SYMBOL

Am2964B

6-67

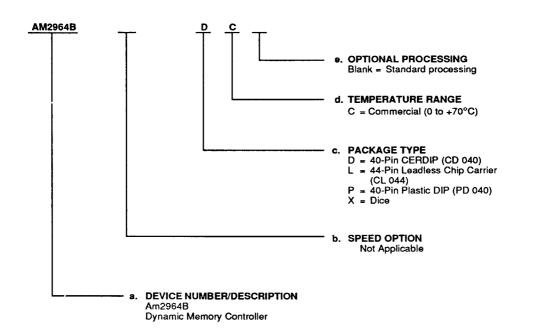

# ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

a. Device Number

b. Speed Option (If applicable)

- Package Type Temperature Range

- Optional Processing

| Valid Combinations |                |  |  |  |

|--------------------|----------------|--|--|--|

| AM2964B            | DC, LC, PC, XC |  |  |  |

# **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

Am2964B 6-68

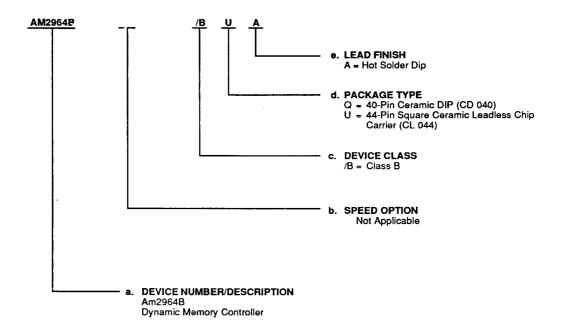

# **MILITARY ORDERING INFORMATION**

# **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of:

a. Device Number

- b. Speed Option (if applicable)

- c. d. Package Type Temperature Range

- Optional Processing

| Valid Combinations |            |  |  |  |

|--------------------|------------|--|--|--|

| AM2964B            | /BQA, /BUA |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations.

# PIN DESCRIPTION

| Pin No.         | Name                                                                               | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | A <sub>0</sub> – A <sub>7</sub>                                                    | ı   | The low order Address inputs are used to latch eight Row Address inputs for the RAM. These inputs drive the outputs $O_0 - O_7$ when MSEL is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | A <sub>8</sub> - A <sub>15</sub>                                                   | I   | The high order Address inputs are used to latch eight Column Address inputs for the RAM. These inputs drive the outputs $O_0 - O_7$ when MSEL is LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11              | A <sub>15</sub>                                                                    | +   | A <sub>15</sub> is a dual input. With normal TTL level inputs A <sub>15</sub> acts as address input A <sub>15</sub> for 64K RAMs. If A <sub>15</sub> is pulled up to $+$ 12V through a 1 K $\Omega$ resistor, the terminal count output. TC, will go LOW every 128 counts (for 16K RAMs) instead of every 256 counts.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | O <sub>0</sub> – O <sub>7</sub>                                                    | 0   | The RAM address outputs. The eight-bit width is designed for dynamic RAMs up to 64K.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16              | MSEL                                                                               | I   | The Multiplexer-SELect input determines whether low order or high order address inputs appear at the multiplexer outputs $O_0 - O_7$ . When MSEL is HIGH the low order address latches $(A_0 - A_7)$ are connected to the outputs. When MSEL is LOW the high order address latches are connected to the outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 25              | RESH                                                                               | 1   | The Refresh control input. When active LOW the RFSH input switches the address output multiplexer to output the inverted contents of the 8-bit refresh counter. RFSH LOW also inhibits the CĀS buffer and changes the mode of the RAS decoder from one-of-four to four-of-four so that all four RAS decoder outputs, RAS <sub>0</sub> , RAS <sub>1</sub> , RAS <sub>2</sub> and RAS <sub>3</sub> , go LOW in response to a LOW input at RASi. This action refreshes one row address in each of the four RAS decoded memory banks. The refresh counter is advanced at the end of each refresh cycle by the LOW-to-HIGH transition of RFSH or RASi (whichever occurs first). In burst mode refresh, RFSH may be held LOW and refresh accomplished by toggling RASI. |

| 9               | TC                                                                                 | 0   | The Terminal Count output. A LOW output at TC indicates that the refresh counter has been sequenced through either 128 or 256 refresh addresses depending on Al <sub>3</sub> . The TC output remains active LOW until the refresh counter is advanced by the rising edge of RASI or RESH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8               | CLR                                                                                | ı   | The refresh counter Clear input. An active LOW input at CLR resets the refresh counter to all LOW (refresh address output to all HIGH).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 36              | LE                                                                                 | 1   | The address latch enable input. An active HIGH input at LE causes the two 8-bit address latches and the 2-bit FAS Select input latch to go transparent, accepting new input data. A LOW input on LE latches the input data which meets set-up and hold time requirements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>4</b> , 5    | RSEL <sub>0</sub> and<br>RSEL <sub>1</sub>                                         | -   | The RAS decoder Select inputs. Data (latched) at these inputs (normally higher order addresses) is decoded by the RAS Decoder to "RAS Select" one of four banks of memory with RAS <sub>0</sub> , RAS <sub>1</sub> , RAS <sub>2</sub> or RAS <sub>3</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3               | RASI                                                                               | t   | The Row Address Strobe Input. During normal memory cycles the selected RAS Decoder output RAS <sub>0</sub> , RAS <sub>1</sub> , RAS <sub>2</sub> or RAS <sub>3</sub> will go active LOW in response to an active LOW input at RASi. During refresh (RFSH = LOW), all RAS outputs go LOW in response to RASI = LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 39, 40,<br>1, 2 | RAS <sub>0</sub> ,<br>RAS <sub>1</sub> ,<br>RAS <sub>2</sub> ,<br>RAS <sub>3</sub> | 0   | Row Address Strobe outputs (RAS). Each provides a Row Address Strobe for one of the four banks of memory. Each will go active LOW only when selected by RSEL0 and RSEL1 and only when RASI goes active LOW. All RAS0 - 3 outputs go active low in response RASI when RFSH goes LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7               | CASI                                                                               | I   | The Column Address Strobe. An active LOW input at CASI will result in an active LOW output at CASO, unless a refresh cycle is in progress (RFSH = LOW).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6               | CASO                                                                               | 0   | The Column Address Strobe output. The active LOW CASO output strobes the Column Address into the dynamic RAM. CASO is inhibited during refresh (RFSH = LOW).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# **RAS OUTPUT FUNCTION TABLE**

| RFSH | RASI | RSEL <sub>1</sub> | RSEL <sub>0</sub> | RAS <sub>0</sub> | RAS <sub>1</sub> | RAS <sub>2</sub> | RAS <sub>3</sub> |

|------|------|-------------------|-------------------|------------------|------------------|------------------|------------------|

| L    | Ι    | Х                 | Х                 | н                | Н                | Н                | H                |

| L    | L    | ×                 | Х                 | L                | L                | L                | L                |

| н    | H    | ×                 | Х                 | н                | Н                | Н                | Н                |

| Н    | L    | L                 | Ł                 | L                | Н                | Н                | Н                |

| Н    | L    | L                 | Н                 | Н                | L                | Н                | Н                |

| Н    | L    | Н                 | L                 | Н                | Н                | L                | Н                |

| Н    | L    | Н                 | Н                 | н                | н                | Н                | L                |

# **CASO** FUNCTION TABLE

| RFSH | CASI | CASO |

|------|------|------|

| Н    | L    | L    |

| Н    | Н    | Н    |

| L    | Х    | Н    |

## ADDRESS OUTPUT FUNCTION TABLE

| MSEL | RFSH | 00-07                           |

|------|------|---------------------------------|

| Ι    | н    | A <sub>0</sub> -A <sub>7</sub>  |

| L    | Н    | A <sub>8</sub> -A <sub>15</sub> |

| X    | L    | Refresh Address                 |

#### REFRESH ADDRESS COUNTER FUNCTION TABLE

| A <sub>15</sub> | CLR | RFSH     | RASI | TC         | REFRESH COUNT                       | FUNCTION                                                    |

|-----------------|-----|----------|------|------------|-------------------------------------|-------------------------------------------------------------|

| X               | L   | x        | X    | Х          | FFH                                 | Clear Counter                                               |

| x               | Н   | ٦        | ×    | ×          | NC                                  | Output Refresh Address<br>No Change for Counter             |

| x               | н   | <b>_</b> | L    | х          | Count - 1                           | Return to Memory Cycle<br>Mode and Decrement Counter        |

| x               | н   | L        | لم   | . <b>X</b> | NC                                  | Output all RAS <sub>i</sub> to RAM<br>No Change for Counter |

| ×               | н   | L        | 7    | ×          | Count - 1                           | Return RAS <sub>i</sub> to HIGH and<br>Decrement Counter    |

| L or H          | н   | X        | ×    | L          | 00 <sub>H</sub>                     | Terminal Count for 256 Line Refresh                         |

| + 12V*          | н   | ×        | ×    | L          | 00 <sub>H</sub> and 80 <sub>H</sub> | Terminal Count for 128 Line<br>Refresh                      |

<sup>\*</sup> Through 1K $\Omega$  resistor.

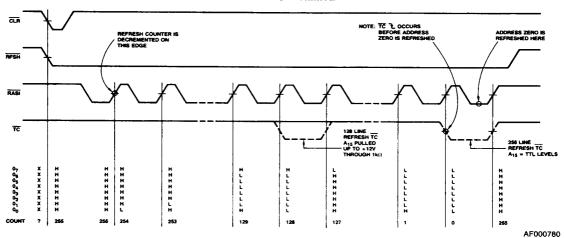

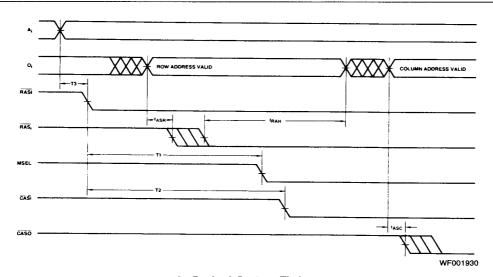

## **BURST REFRESH TIMING**

The timing shown assumes that burst mode applications may power-down the Am2964B with the RAM. Therefore the counter is cleared prior to executing the refresh sequence.

Am2964B

## **FUNCTIONAL DESCRIPTION**

#### **Architecture**

The Dynamic Memory Controller (DMC) provides address multiplexing, refresh address generation and RAS/CAS control for the MOS dynamic RAM memories of any data width. The eight bit address path is designed for 64K RAMs and can be used with 16K RAMs.

Sixteen address input latches and two RAS Select latches (for higher order addresses) allow the DMC to control up to 256K words of memory (with 64K RAMs) by using the internal RAS decoder to select from one-of-four banks of RAMs.

## Speed With Minimum Skew

The DMC provides Schottky speed in all of the critical paths. In addition, time skew between the Address, RAS and CAS paths is minimized (and specified) by placing these function on the same chip. The inclusion of the CAS buffer allows matching of its propagation delay, plus provides the CAS inhibit function during RAS – only refresh.

## Input Latches

The eighteen input latches are transparent when LE is HIGH and latch the input data meeting set-up and hold time requirements when LE goes LOW. In systems with separate address and data buses, LE may be permanently enabled HIGH

# **Refresh Counter**

The 8-bit refresh counter provides both 128 and 256 line refresh capability. Refresh control is external to allow maximum user flexibility. Transparent (hidden), burst, synchronous or asynchronous refresh modes are all possible.

The refresh counter is advanced at the LOW-to-HIGH transition of RFSH (or RASI). This assures a stable counter output for the next refresh cycle. The counter will continue to cycle through 256 addresses unless reset to zero by CLR. This actually causes all outputs to go HIGH since the output MUX is inverting. (Address inputs to outputs are non-inverting since both the input latches and output MUX are inverting).

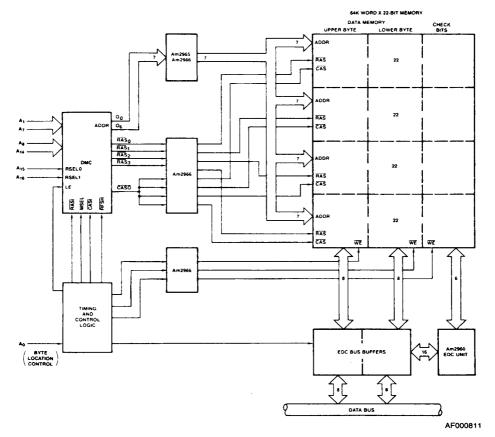

Address and RAS/CAS drivers each drive 22 RAM inputs at each output. Timing skew is minimized by using one device for address lines and one device for RAS/CAS, spreading the CAS loading over four drivers to equalize the capacitive load on each driver.

Figure 1. Dynamic Memory Control with Error Detection and Correction

Am2964B

#### Refresh Terminal Count

The refresh counter also provides a Terminal Count output for burst mode refresh applications.  $\overline{TC}$  normally occurs at count 255 (00 to 07 all LOW when  $\overline{RFSH}$  is LOW).  $\overline{TC}$  can be made to occur at count 127 for 128 line burst mode refresh by pulling A<sub>15</sub> up to +12V through a  $1K\Omega\pm10\%$  resistor. The counter actually cycles through 256 with  $\overline{TC}$  determined by A<sub>15</sub>. Otherwise, A<sub>15</sub> functions as an address input when driven at normal TTL levels.

# Three Input 8-Bit Address Multiplexer

The address MUX is 8-bits wide (for 64K RAMs) and has three data sources: the lower address input latch ( $A_0$  to  $A_7$ ), the upper address input latch ( $A_8$  to  $A_{15}$ ) and the internal refresh counter. The lower address latch is selected when MSEL is HIGH. This is normally the Row address. The upper address latch is selected when MSEL is LOW. This is normally the Column address. The third source, the refresh counter, is selected when RFSH is LOW and overrides MSEL.

When RFSH goes LOW, the MUX selects the refresh counter address and CASO is inhibited. Also, the RAS Decoder

function is changed from one-of-four to four-of-four so all RAS outputs RAS0-RAS3 go LOW to refresh all banks of memory when RAS1 goes LOW. When RFSH is HIGH only one RAS output goes low. This is determined by the RAS Select inputs, RSEL0 and RSEL1. In either case the RAS Decoder output timing is controlled by RAS1 to make sure the refresh count appears at 00-07 before RAS0-RAS3 go LOW. This assures meeting Row address Set-up time requirement of the RAM (tASR).

### **Maximum Performance System**

The typical organization of a maximum performance 16-bit system including Error Detection and Correction is shown in Figure 1. Delay lines provide the most accurate timing and are recommended for RAS/MSEL/CAS timing in this type of system.

# Controlling 16K RAMs or Smaller Systems

16K RAMs require seven address inputs and 128 line refresh. Also, A<sub>0</sub> is often used to designate upper or lower byte transactions in 16-bit systems. These modifications are shown in Figure 2.

\*A<sub>0</sub> Controls Byte Select Logic

Figure 2. Word Organized Memory Using 16K RAMs

# **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65°C to +150°C            |

|----------------------------------------------|

| Ambient Temperature under Bias55°C to +125°C |

| Supply Voltage to Ground Potential           |

| Continous0.5V to +7.0V                       |

| DC Voltage Applied to Outputs For            |

| High Output State0.5V to VCC Max             |

| DC Input Voltage0.5V to +5.5V                |

| Output Current, Into Outputs                 |

| DC Input Current30mA to ±5.0mA               |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

| Commercial (C) Devices |                    |

|------------------------|--------------------|

| Temperature            | 0°C to +70°C       |

| Supply Voltage         | + 4.75V to + 5.25V |

| Military (M) Devices   |                    |

| Temperature            | 55°C to +125°C     |

| Supply Voltage         | +4.5V to +5.5V     |

Operating ranges define those limits over which the functionality of the device is guaranteed.

## DC CHARACTERISTICS over operating ranges unless otherwise specified

| Parameters      | Descriptions                     |                                                                                                          | onditions<br>ote 1)                                               | <b>Min</b><br>2.5 | Typ<br>(Note 2) | Max   | Units |

|-----------------|----------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------|-----------------|-------|-------|

|                 |                                  | V <sub>CC</sub> = MIN                                                                                    | Τc                                                                |                   |                 |       | Volts |

| VOH             | Output HIGH Voltage              | VIN = VIH OrVIL<br>IOH = - 1mA                                                                           | Others                                                            | 3.0               |                 |       | Volts |

| V <sub>OH</sub> | Output HIGH Voltage              | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub><br>I <sub>OH</sub> = -15mA | All outputs except TC                                             | 2.0               |                 |       | Volts |

| Vol             | Output LOW Voltage               | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>H</sub>                             | All outputs except<br>TC, I <sub>OL</sub> = 16mA                  |                   |                 | 0.5   | Volts |

|                 |                                  | 111 9 1L                                                                                                 | TC, IOL = 8mA                                                     |                   |                 | 0.5   | Volts |

| VIH             | Input HIGH level                 | Guaranteed input log voltage for all inputs                                                              |                                                                   | 2.0               |                 |       | Volts |

| VIL             | Input LOW level                  | Guaranteed input log voltage for all inputs                                                              |                                                                   |                   | 0.8             | Volts |       |

| VI              | Input Clamp Voltage              | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18                                                             | 8mA                                                               |                   |                 | - 1.5 | Volts |

| l <sub>IL</sub> | Input LOW Current                | V <sub>CC</sub> = MAX<br>V <sub>IN</sub> = 0.4V                                                          | RASI                                                              |                   |                 | -3.2  | mA    |

|                 |                                  |                                                                                                          | CASI, MSEL, RFSH                                                  |                   |                 | -1.6  | mA    |

|                 |                                  |                                                                                                          | A <sub>0</sub> -A <sub>15</sub> , CLR<br>RSEL <sub>0.1</sub> , LE |                   |                 | -0.4  | mA    |

|                 |                                  | V <sub>CC</sub> = MAX<br>V <sub>IN</sub> = 2.7V                                                          | RASI                                                              |                   |                 | 100   | μА    |

| Iн              | Input HIGH Current               |                                                                                                          | CASI, MSEL, RFSH                                                  |                   |                 | 50    | μА    |

| יווי            | mpar man canon                   |                                                                                                          | A <sub>0</sub> -A <sub>15</sub> , CLR<br>RSEL <sub>0,1</sub> , LE |                   |                 | 20    | μА    |

|                 |                                  | V <sub>CC</sub> = MAX                                                                                    | RASI                                                              |                   |                 | 2.0   | mA    |

| 6               | Input HIGH Current               | V <sub>IN</sub> = 5.5V                                                                                   | CASI, MSEL, RFSH                                                  |                   |                 | 1.0   | mA    |

| l <sub>i</sub>  | input High Current               | V <sub>CC</sub> = MAX<br>V <sub>IN</sub> = 5.5V                                                          | A <sub>0</sub> -A <sub>15</sub> , CLR<br>RSEL <sub>0,1</sub> , LE |                   |                 | 0.1   | mA    |

| Isc             | Output Short Circuit Current     | V <sub>CC</sub> = MAX (Note 3)                                                                           |                                                                   | -40               |                 | - 100 | mA    |

|                 |                                  | 25°C, 5V                                                                                                 |                                                                   |                   | 122             |       | mA    |

|                 |                                  | 0°C to 70°C                                                                                              |                                                                   |                   |                 | 173   | mA    |

| lcc             | Power Supply Current<br>(Note 4) | 70°C                                                                                                     | COM'L                                                             |                   |                 |       | L     |

|                 | (100 4)                          | -55°C to + 125°C                                                                                         | J                                                                 |                   |                 | 164   | mA    |

|                 |                                  | + 125°C                                                                                                  | MIL                                                               |                   |                 | 150   | mA    |

| lT              | A <sub>15</sub> Enable Current   | $A_{15}$ connected to + $1K\Omega \pm 10\%$                                                              | 12V through                                                       |                   |                 | 5     | mA    |

Notes: 1. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Range for the applicable device type.

Typical limits are at  $V_{CC} = 5.0V$ , 25°C ambient and maximum loading.

Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

ICC is worst case when the Address inputs are latched HIGH, the refresh counter is at terminal count (255), RASI and CASI are HIGH and all other inputs are LOW.

# **SWITCHING CHARACTERISTICS** over operating range for $C_L = 50pF$ **Am2964B (Notes 5, 6)**

|      |                  |                                                         | Test                  |     | COMM | ERCIAL | MILI     | TARY |       |

|------|------------------|---------------------------------------------------------|-----------------------|-----|------|--------|----------|------|-------|

| Para | meter            | Description                                             | Conditions            | Тур | Min  | Max    | Min      | Max  | Units |

| 1    | tPD              | A <sub>i</sub> to O <sub>i</sub> Delay                  | 1                     | 14  |      | 19     |          | 23   | ns    |

| 2    | tpHL             | RASI to RAS; (RFSH = H)                                 |                       | 14  |      | 20     |          | 23   | ns    |

| 3    | tpHL             | RASI to RAS; (RFSH = L)                                 | <b>-</b>              | 14  |      | 20     | <u> </u> | 23   | ns    |

| 4    | teo              | MSEL to Oi                                              |                       | 17  | 9    |        | 9        |      | ns    |

| 5    | tPD              | MSEL to Oi                                              |                       | 17  |      | 21     |          | 25   | ns    |

| 6    | t <sub>PHL</sub> | CASI to CASO (RFSH = H)                                 |                       | 12  |      | 17     |          | 19   | ns    |

| 7    | tpHL             | RSEL; to RAS; (LE = H, RASI = L)                        |                       | 15  |      | 20     |          | 24   | ns    |

| 8    | tpLH             | RFSH to TC (RASI = L)                                   |                       | 30  |      | 40     |          | 50   | ns    |

| 9    | tPLH             | RASI to TC (RFSH = L)                                   |                       | 25  |      | 35     |          | 40   | ns    |

| 10   | tpw              | RASI = L (RFSH = L)                                     |                       | 10  | 50   |        | 50       |      | ns    |

| 11   | tpw              | RASI = H (RFSH = L)                                     |                       | 10  | 50   |        | 50       | l    | ns    |

| 12   | tPD              | RFSH to O <sub>i</sub> (RASI = X)                       |                       | 17  |      | 21     |          | 25   | ns    |

| 13   | tpHL             | RFSH to RASi (RASi = L)                                 |                       | 19  |      | 26     |          | 29   | ns    |

| 14   | tpw              | CLR = L                                                 |                       | 10  | 30   |        | 35       |      | ns    |

| 15   | tpLH             | RFSH to CASO<br>(RASI = L CASI = L, Note 7)             | C <sub>L</sub> = 50pF | 16  |      | 21     |          | 25   | ns    |

| 16   | tpD              | LE to Oi                                                |                       | 25  |      | 35     |          | 40   | ns    |

| 17   | tPHL             | LE to RAS <sub>i</sub>                                  |                       | 30  |      | 40     |          | 45   | ns    |

| 18   | tpLH             | CLR to TC                                               |                       | 35  |      | 45     |          | 56   | ns    |

| 19   | tpLH             | CLR to O <sub>i</sub> (RFSH = L)                        | 7                     | 31  |      | 44     |          | 54   | ns    |

| 20   | ts               | A <sub>i</sub> to LE Set-Up Time                        |                       | 0   | 5    |        | 5        |      | ns    |

| 21   | t <sub>H</sub>   | A <sub>i</sub> to LE Hold Time                          |                       | 5   | 12   |        | 15       |      | ns    |

| 22   | ts               | RSELi to LE Set-Up Time                                 |                       | 0   | 5    |        | 5        |      | ns    |

| 23   | t <sub>H</sub>   | RSELi to LE Hold Time                                   |                       | 10  | 17   |        | 25       |      | ns    |

| 24   | ts               | CLR Recovery Time                                       |                       | 10  | 16   | Ī      | 18       |      | ns    |

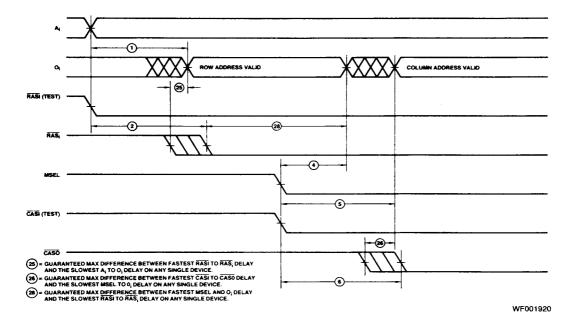

| 25   | tSKEW            | O <sub>i</sub> to RAS <sub>i</sub> (RFSH = H, Note 8)   |                       | 2   |      | 5      | Ī        | 6    | ns    |

| 26   | tSKEW            | O <sub>i</sub> to CASO (Note 8)                         |                       | 6   | 1    | 8      |          | 8    | ns    |

| 27   | tskew            | O <sub>i</sub> to RAS <sub>i</sub> (RFSH = L, Note 9)   |                       | 6   |      | 8      |          | 10   | ns    |

| 28   | tskew            | O <sub>i</sub> to RAS <sub>i</sub> (MSEL = 1_, Note 10) |                       | 1   |      | 5      |          | 5    | ns    |

Notes: 5. Minimum spec limits for t<sub>pw</sub>, t<sub>s</sub> and t<sub>H</sub> are minimum system operating requirements. Limits for t<sub>SKEW</sub> and t<sub>PD</sub> are guaranteed test limits for the device.

- 6. All AC parameters are specified at the 1.5V level.

- 7. RFSH inhibits CASO during refresh. Specification is for CASO inhibit time.

- 8. Oi to RASi (RFSH = HIGH) skew is guaranteed maximum difference between fastest RASi to RASi delay and slowest Ai to Oi delay within a single device. Oi to CASO skew is maximum difference between fastest CASi to CASO delay and slowest MSEL to Oi delay within a single device. See application section entitled Memory Cycle Timing for correlation to System Timing requirements.

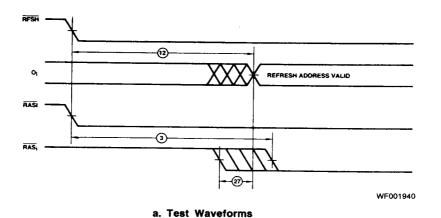

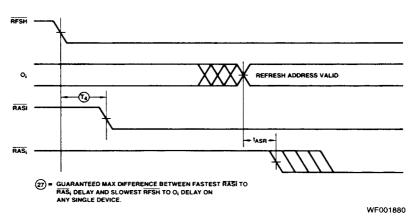

- O<sub>i</sub> to RAS<sub>i</sub> (RFSH = LOW) skew is guaranteed maximum difference between fastest RASi to RAS<sub>i</sub> delay and slowest RFSH to O<sub>i</sub> delay within a single device. See application section on Refresh Timing for correlation to system refresh timing requirements.

- 10. O<sub>i</sub> to RAS<sub>i</sub> (MSEL = 1 ) skew is guaranteed maximum difference between fastest MSEL 1 to O<sub>i</sub> delay and slowest RAS<sub>i</sub> to RAS<sub>i</sub> delay within a single device.

# **SWITCHING CHARACTERISTICS** over operating range for $C_L = 50pF$ **Am2964B (Notes 5, 6)**

|      |                  |                                                         | Test                   |     | сомм | ERCIAL | L MILITARY |     |       |

|------|------------------|---------------------------------------------------------|------------------------|-----|------|--------|------------|-----|-------|

| Para | meter            | Description                                             | Conditions             | Тур | Min  | Max    | Min        | Max | Units |

| 1    | tpD              | A <sub>i</sub> to O <sub>i</sub> Delay                  |                        | 20  |      | 25     |            | 30  | ns    |

| 2    | tPHL             | RASI to RAS; (RFSH = H)                                 | ]                      | 18  |      | 24     |            | 27  | ns    |

| 3    | tPHL             | RASi to RASi (RFSH = L)                                 |                        | 18  |      | 24     |            | 27  | ns    |

| 4    | t <sub>PD</sub>  | MSEL to Oi                                              |                        | 23  | 12   |        | 12         |     | ns    |

| 5    | tpD              | MSEL to Oi                                              |                        | 23  |      | 27     |            | 31  | ns    |

| 6    | tPHL             | CASI to CASO (RFSH = H)                                 | ]                      | 17  |      | 24     |            | 26  | ns    |

| 7    | tPHL             | RSELi to RASi (LE = H, RASI = L)                        |                        | 19  |      | 27     |            | 30  | ns    |

| 8    | tpLH             | RFSH to TC (RASI = L)                                   |                        | 34  |      | 45     |            | 55  | ns    |

| 9    | t <sub>PLH</sub> | RASI to TC (RFSH = L)                                   | ]                      | 32  |      | 45     |            | 55  | ns    |

| 10   | tpw              | RASI = L (RFSH = L)                                     | ]                      | 10  | 50   |        | 50         |     | ns    |

| 11   | tpw              | RASI = H (RFSH = L)                                     | 1                      | 10  | 50   |        | 50         |     | ns    |

| 12   | tPD              | RFSH to O <sub>i</sub> (RASI = X)                       | ]                      | 21  |      | 27     |            | 30  | ns    |

| 13   | tPHL             | RFSH to RAS; (RASI = L)                                 | ]                      | 25  |      | 33     |            | 36  | ns    |

| 14   | tpw              | CLR = L                                                 | ]                      | 10  | 30   |        | 35         |     | ns    |

| 15   | tPLH             | RFSH to CASO<br>(RASi = L CASI = L, Note 7)             | C <sub>L</sub> = 150pF | 21  |      | 27     |            | 31  | ns    |

| 16   | tPD              | LE to O <sub>i</sub>                                    |                        | 30  |      | 40     |            | 50  | ns    |

| 17   | tPHL             | LE to RAS                                               | ]                      | 34  |      | 45     |            | 54  | ns    |

| 18   | tPLH             | CLR to TC                                               |                        | 39  |      | 55     | I          | 60  | ns    |

| 19   | tPLH             | CLR to O <sub>i</sub> (RFSH = L)                        |                        | 38  |      | 50     |            | 62  | กร    |

| 20   | ts               | A <sub>i</sub> to LE Set-Up Time                        |                        | 0   | 5    |        | 5          |     | ns    |

| 21   | tH               | A <sub>i</sub> to LE Hold Time                          |                        | 5   | 12   |        | 12         |     | ns    |

| 22   | ts               | RSELi to LE Set-Up Time                                 |                        | 0   | 5    |        | 5          |     | ns    |

| 23   | tH               | RSELi to LE Hold Time                                   |                        | 10  | 17   |        | 25         |     | ns    |

| 24   | ts               | CLR Recovery Time                                       |                        | 10  | 16   |        | 18         |     | ns    |

| 25   | tSKEW            | O <sub>i</sub> to RAS <sub>i</sub> (RFSH = H, Note 8)   |                        | 3   | I    | 6      |            | 7   | ns    |

| 26   | tSKEW            | O <sub>i</sub> to CASO (Note 8)                         |                        | 6   |      | 8      |            | 8   | ns    |

| 27   | tSKEW            | O <sub>i</sub> to RAS <sub>i</sub> (RFSH = L, Note 9)   |                        | 6   | [    | 9      |            | 10  | ns    |

| 28   | tskew            | O <sub>i</sub> to RAS <sub>i</sub> (MSEL = L , Note 10) | ]                      | 1   |      | 5      |            | 5   | ns    |

# **Notes on Testing**

Incoming test procedures on this device should be carefully planned, taking into account the high complexity and power levels of the part. The following notes may be useful.

- Insure the part is adequately decoupled at the test head.

Large changes in V<sub>CC</sub> current as the device switches may cause erroneous function failures due to V<sub>CC</sub> changes.

- 2.Do not leave inputs floating during any tests, as they may start to oscillate at high frequency.

- 3.Do not attempt to perform threshold tests at high speed. Following an input transition, ground current may change by as much as 400mA in 5-8ns. Inductance in the ground cable

may allow the ground pin at the device to rise by 100s of millivolts momentarily.

- 4.Use extreme care in defining input levels for AC tests. Many inputs may be changed at once, so there will be significant noise at the device pins and they may not actually reach  $V_{IL}$  or  $V_{IH}$  until the noise has settled. AMD recommends using  $V_{IL} \leqslant 0.4 V$  and  $V_{IH} \geqslant 2.4 V$  for AC tests.

- 5.To simplify failure analysis, programs should be designed to perform DC, Function, and AC tests as three distinct groups of tests.

- To assist in testing, AMD offers complete documentation on our test procedures.

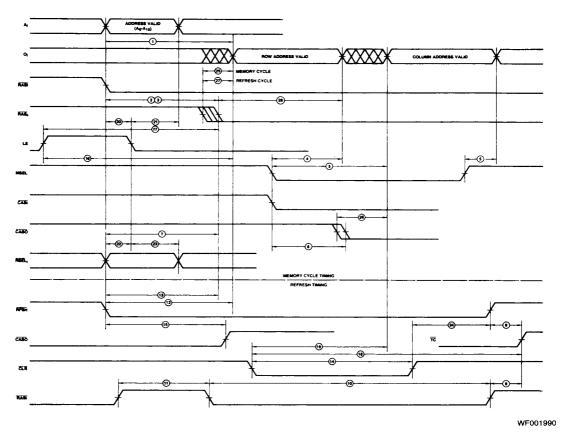

Am2964B Dynamic Memory Controller Timing

#### **MEMORY CYCLE TIMING**

The relationship between DMC specifications and system timing requirements are shown in Figure 3. T<sub>1</sub>, T<sub>2</sub> and T<sub>3</sub> represent the minimum timing requirements at the DMC inputs to guarantee that RAM timing requirements are met and that maximum system performance is achieved.

The minimum requirement for T<sub>1</sub>, T<sub>2</sub> and T<sub>3</sub> are as follows:

$$T_1MIN = t_{RAH} + t_{28}$$

$T_2MIN = T_1 + t_{26} + t_{ASC}$

$T_3MIN = t_{ASR} + t_{25}$

See RAM data sheet for applicable values for  $t_{\mbox{\scriptsize RAH}}$ ,  $t_{\mbox{\scriptsize ASC}}$  and  $t_{\mbox{\scriptsize ASR}}$ .

# a. Specifications Applicable to Memory Cycle Timing

b. Desired System Timing Figure 3. Memory Cycle Timing

6-78 Am2964B

# REFRESH CYCLE TIMING

The timing relationships for refresh are shown in Figure 4.  $T_4$  minimum is calculated as follows:  $T_4 = t_{ASR} + t_{27}$

b. Desired System Timing

Figure 4. Refresh Timing

Am2964B