#### February 2001 Copyright © 2000, 2001 by LSI Logic Corporation. All rights reserved.

ΡI

# TN FN

IDDTN -

Ζ

PO

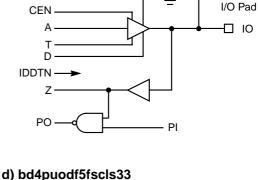

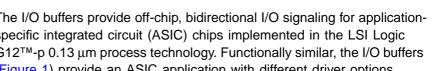

# b) bd4puf5fsls33

TN FN

# G12<sup>™</sup>-p 3.3 V, 4 mA, 5-Volt Tolerant, Fail-Safe, **General Purpose I/O Buffers**

# Datasheet

a) bd4f5fsls33

LSI Logic Corporation provides the following driver/receiver input/output (I/O) cells for use as general purpose I/O buffers:

- bd4f5fsls33

- bd4puodf5fsls33

- bd4puf5fsls33 bd4puodf5fscls33

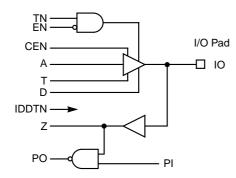

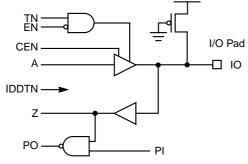

The I/O buffers provide off-chip, bidirectional I/O signaling for applicationspecific integrated circuit (ASIC) chips implemented in the LSI Logic G12<sup>™</sup>-p 0.13 µm process technology. Functionally similar, the I/O buffers (Figure 1) provide an ASIC application with different driver options.

#### **Buffer Block Diagrams** Figure 1

c) bd4puodf5fsls33

I/O Pad

- IIO

# LSI LOGIC

# **Features and Benefits**

- Up to 20 MHz,

3.3 V I/O operation

- 5-Volt tolerant

- Fail-safe at high voltages

- Feedthrough protection

- 20 μA maximum leakage current

- Minimum 4 mA current drive into a 40 pF load at 20 MHz

- 1.8 V internal signaling for reduced power consumption

- Uses one standard I/O slot

# **Signal Descriptions**

Table 1 describes signal connections for all four buffers.

| Signal           | Direction | Description                                                |

|------------------|-----------|------------------------------------------------------------|

| А                | IN        | Data input to I/O buffer driver from ASIC circuitry        |

| CEN <sup>1</sup> | IN        | Enables I/O buffer operation after power-on                |

| D <sup>2</sup>   | IN        | Configures driver operating mode                           |

| EN               | IN        | 0 = Normal mode<br>1 = Disable I/O buffer driver           |

| IDDTN            | IN        | 0 = Power down entire cell <sup>3</sup><br>1 = Normal mode |

| PI               | IN        | NAND-tree parametric test input                            |

| T <sup>2</sup>   | IN        | Configures driver operating mode                           |

| TN               | IN        | 0 = Disable I/O buffer driver<br>1 = Normal mode           |

| 10               | IN/OUT    | Input/output pad                                           |

| PO               | OUT       | NAND-tree parametric test output                           |

| Z                | OUT       | I/O buffer receiver output to ASIC circuitry               |

Table 1 I/O Buffer Connections

1. Not available in bd4puodf5fscls33

2. Available only in bd4f5fsls33 and bd4puf5fsls33. Refer to Table 4 for settings.

3. Used for production IDDQ leakage test

# **General Description**

The buffers include a receiver, driver, and NAND-tree circuitry to conform with standard LSI Logic test methodology. The buffers translate signals between the 1.8 V operating levels of the ASIC core circuitry and the 3.3 V operating levels at the I/O pad. They tolerate high DC and transient voltages at the I/O pad, are fail safe, and provide feedthrough protection.

# **Voltage Tolerance**

The I/O buffers are 5-volt tolerant. Although the off-chip I/O signaling normally operates at 3.3 volts, external circuitry may cause higher voltages, typically upwards of 5 volts, to appear at the chip I/O pad. Circuit and process techniques ensure that such DC or transient voltages do not damage the I/O buffer circuitry.

# **Failure and Feedthrough Protection**

In the absence of a V<sub>DD</sub> supply, the I/O buffers are fail-safe and protected against voltage feedthrough. With high voltage applied to the chip I/O pad, the I/O buffers can survive without degradation for up to ten years. Furthermore, with a low, maximum 20  $\mu$ A leakage current, the high voltage can not power up the ASIC through voltage feedthrough.

# **Functional Description of Receivers**

The buffers use the same receiver circuitry. The following truth table (Table 2) describes receiver behavior.

|       | Inputs         | Outputs |   |    |

|-------|----------------|---------|---|----|

| IDDTN | ю              | PI      | z | РО |

| 0 1   | High Impedance | 1       | 1 | 0  |

| 1     | 0              | 0       | 0 | 1  |

| 1     | 1              | 0       | 1 | 1  |

| 1     | 1              | 1       | 1 | 0  |

Table 2 Receiver Truth Table

1. Factory IDDQ test setting

# **Functional Description of Drivers**

The buffers use similar driver circuitry that produces a minimum of 4 mA of output drive. The buffers provide options for selecting the driver output configuration and power-up mode (Table 3). All the buffers except bd4f5fsls33 have internal pull-up resistor devices. Preset power-up modes avoid unpredictable output behavior.

#### Table 3 I/O Buffer Driver Characteristics

| I/O Buffer Cell  | Driver Mode                                                            | Pull-Up          | Power-Up Mode                    | Application    |

|------------------|------------------------------------------------------------------------|------------------|----------------------------------|----------------|

| bd4f5fsls33      | Dynamically programmable open-drain, open-source, or totem-pole output | None             | 3-State                          | General        |

| bd4puf5fsls33    | Dynamically programmable open-drain, open-source, or totem-pole output | Yes,<br>internal | 3-State                          | General        |

| bd4puodf5fsls33  | Open-drain output                                                      | Yes,<br>internal | Current sinking<br>logic level 0 | Power-on reset |

| bd4puodf5fscls33 | Open-drain output                                                      | Yes,<br>internal | 3-State                          | General        |

# **Driver Output Configuration**

With the bd4f5fsls33 (Figure 1a) or bd4puf5fsls33 (Figure 1b) buffer, the T and D inputs set a driver output to open-drain, open-source, or totem-pole mode (Table 4). An application can hardwire the T and D inputs, or, to dynamically configure a driver output, it can supply the T and D inputs from a register.

| т | D | Output      |

|---|---|-------------|

| 0 | 0 | Open drain  |

| 0 | 1 | Totem pole  |

| 1 | 0 | Totem pole  |

| 1 | 1 | Open source |

The bd4puodf5fsls33 (Figure 1c) and the bd4puodf5fscls33 (Figure 1d) buffers fix the output in the open-drain mode.

# **Pull-Up Resistor**

Except for bd4f5fsls33, the buffers include a pull-up resistor, which can provide from 100  $\mu$ A to 500  $\mu$ A of current across the specified process, voltage, and temperature ranges.

<u>Note:</u> Evaluate the buffer models before simulating a design. Models provided for some third-party design environments may not correctly represent or even include the pull-up resistor.

# **Power-Up Modes**

Each buffer has a defined power-up mode (Table 3) to avoid unpredictable output behavior. The bd4f5fsls33, bd4puf5fsls33, and bd4puodf5fsls33 buffers preset the driver output to 3-state or currentsinking mode upon power up. The bd4puodf5fscls33 buffer has no preset power-up mode.

#### Preset to 3-State (bd4f5fsls33 and bd4puf5fsls33)

At power up, circuitry in the bd4f5fsls33 and bd4puf5fsls33 buffers forces the IO signal at the I/O pad to the high-impedance state. To begin normal operation, the buffers require the ASIC application to assert CEN to HIGH.

#### Preset to Open-Drain (bd4puodf5fsls33)

At power up, circuitry in the bd4puodf5fs1s33 buffer forces the driver output to open-drain mode. As the driver sinks current, it drives the IO signal at the I/O pad to LOW. Designed primarily for power-on-reset applications, the buffer holds circuits connected to the I/O pad in the LOW reset state until the ASIC application asserts CEN to HIGH, thereby releasing the buffer to operate normally.

To drive the CEN signal HIGH directly from a source external to the ASIC, connect CEN to a DDRV type I/O pad for ESD protection and apply an activation signal. Although this activation signal may reach 3.3 V, a signal limited to 1.8 V better matches the normal internal signaling level, and is therefore preferable.

#### No Preset (bd4puodf5fscls33)

The bd4puodf5fsc1s33 buffer has no CEN signal to provide a separate power-up mode. However, power-up characteristics of the buffer circuitry prevent hard driving the IO signal at the I/O pad to HIGH, thereby avoiding unpredictable behavior. A relatively high-impedance pull-up device eventually drives IO to HIGH unless

- the buffer itself drives it LOW with A = EN = 0 and TN = 1, or

- another device external to the buffer drives it LOW.

# **Truth Tables**

Table 5 describes the driver behavior for the bd4f5fsls33 andbd4puf5fsls33 buffers.

| Table 5Truth Table for bd4f5fsls33 and bd4puf5fsls33 Drivers |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

| Inputs         |     |   |    |    |   | Output without | Output with                      |                                  |                           |

|----------------|-----|---|----|----|---|----------------|----------------------------------|----------------------------------|---------------------------|

| IDDTN          | CEN | Α | TN | EN | т | D              | Pull-up<br>Resistor <sup>1</sup> | Pull-up<br>Resistor <sup>2</sup> | Description               |

| Х <sup>3</sup> | 0   | Х | Х  | х  | Х | Х              | High Impedance                   | High Impedance                   | 3-State power-up mode     |

| 0              | 1   | Х | Х  | Х  | Х | Х              | High Impedance                   | High Impedance                   | Factory IDDQ test setting |

| 1              | 1   | Х | Х  | 1  | Х | Х              | High Impedance                   | High Impedance <sup>4</sup>      | Disabled with EN          |

| 1              | 1   | Х | 0  | Х  | Х | Х              | High Impedance                   | High Impedance <sup>4</sup>      | Disabled with TN          |

| 1              | 1   | 0 | 1  | 0  | 0 | 0              | 0                                | 0                                | Open-drain output         |

| 1              | 1   | 1 | 1  | 0  | 0 | 0              | High Impedance                   | High Impedance <sup>4</sup>      | Open-drain output         |

| 1              | 1   | 0 | 1  | 0  | 0 | 1              | 0                                | 0                                | Totem-pole output         |

| 1              | 1   | 1 | 1  | 0  | 0 | 1              | 1                                | 1                                | Totem-pole output         |

| 1              | 1   | 0 | 1  | 0  | 1 | 0              | 0                                | 0                                | Totem-pole output         |

| 1              | 1   | 1 | 1  | 0  | 1 | 0              | 1                                | 1                                | Totem-pole output         |

| 1              | 1   | 0 | 1  | 0  | 1 | 1              | High Impedance                   | High Impedance <sup>4</sup>      | Open-source output        |

| 1              | 1   | 1 | 1  | 0  | 1 | 1              | 1                                | 1                                | Open-source output        |

1. Using bd4f5fsls33 buffer

2. Using bd4puf5fsls33 buffer. Note: SPICE type simulation may produce different behavior.

3. Don't care state, X = 0 or 1

4. In silicon, the pull-up resistor actually pulls the output HIGH. However, third-party models do not correctly represent the pull-up resistor. Therefore, the truth table shows the output in the high-impedance state.

Table 6 describes the bd4puodf5fs1s33 driver behavior.

|                |     | Inputs |    |    | Output                      |                           |

|----------------|-----|--------|----|----|-----------------------------|---------------------------|

| IDDTN          | CEN | A      | TN | EN | ю                           | Description               |

| X <sup>1</sup> | 0   | Х      | Х  | Х  | 0                           | Open-drain power-up mode  |

| 0              | 1   | Х      | Х  | Х  | High Impedance              | Factory IDDQ test setting |

| 1              | 1   | Х      | Х  | 1  | High Impedance <sup>2</sup> | Disabled with EN          |

| 1              | 1   | Х      | 0  | Х  | High Impedance <sup>2</sup> | Disabled with TN          |

| 1              | 1   | 0      | 1  | 0  | 0                           | Open-drain output         |

| 1              | 1   | 1      | 1  | 0  | High Impedance <sup>2</sup> | Open-drain output         |

Table 6

Truth Table for bd4puodf5fsls33 Driver

1. Don't care state, X = 0 or 1

2. In silicon, the pull-up resistor actually pulls the output HIGH. However, third-party models do not correctly represent the pull-up resistor. Therefore, the truth table shows the output in the high-impedance state.

Table 7 describes the bd4puodf5fscls33 driver behavior.

#### Table 7Truth Table for bd4puodf5fscls33 Driver

|       | Inputs         |    |    | Output                      |                           |

|-------|----------------|----|----|-----------------------------|---------------------------|

| IDDTN | Α              | TN | EN | ю                           | Mode                      |

| 0     | X <sup>1</sup> | х  | х  | High Impedance              | Factory IDDQ test setting |

| 1     | Х              | х  | 1  | High Impedance <sup>2</sup> | Disabled with EN          |

| 1     | Х              | 0  | Х  | High Impedance <sup>2</sup> | Disabled with TN          |

| 1     | 0              | 1  | 0  | 0                           | Open-drain output         |

| 1     | 1              | 1  | 0  | High Impedance <sup>2</sup> | Open-drain output         |

1. Don't care state, X = 0 or 1

2. In silicon, the pull-up resistor actually pulls the output HIGH. However, thirdparty models do not correctly represent the pull-up resistor. Therefore, the truth table shows the output in the high-impedance state.

# **Driver Slew Rate**

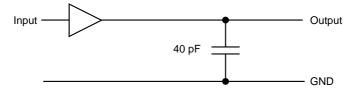

The following slew rate measurement applies to the bd4f5fsls33 and bd4puf5fsls33 buffers in totem-pole mode. In the rise/fall test, the driver drives a signal across a 40 pF load capacitor (Figure 2). Table 8 shows the observed slew rate across the load capacitor measured from 0.6 V to 2.2 V.

| Min. | Тур. | Max. | Unit  |  |

|------|------|------|-------|--|

| _    | 600  | _    | mV/ns |  |

# Testing

The buffers include test circuitry and signals compatible with standard LSI Logic test methodology. The PI and PO NAND-tree signals provide access for parametric testing. The global IDDTN signal powers down all circuitry for IDDQ leakage testing.

#### **IMPORTANT:**

The IDDQ leakage test requires the I/O buffers in the highimpedance state. Setting IDDTN to LOW usually accomplishes this condition. However, with the I/O buffers that use CEN to preset the power-up mode, IDDQ may fail due to high leakage current unless CEN is also driven HIGH.

# **Specifications**

The buffers adhere to the general specifications in Table 9. Table 10 describes the receiver DC characteristics. Table 11 describes the driver DC characteristics.

### Table 9 General Specifications

| Symbol          | Parameter                                              | Condition                                        | Min. | Тур. | Max. | Unit |

|-----------------|--------------------------------------------------------|--------------------------------------------------|------|------|------|------|

| V <sub>DD</sub> | Supply voltage                                         |                                                  | 2.97 | 3.30 | 3.63 | V    |

| Тј              | Junction temperature                                   |                                                  | 0    | -    | 125  | °C   |

| ESD             | Electrostatic discharge,<br>human body model (HBM)     | MIL-STD-883C,<br>Method 3015.7<br>100 pF @1.5 KΩ | 2000 | -    | _    | V    |

|                 | Electrostatic discharge,<br>charged device model (CDM) | ESD DS5.3.1-1996                                 | 500  | _    | -    | V    |

# Table 10 Receiver DC Characteristics<sup>1</sup>

| Symbol          | Parameter             | Test Condition                                                                                        | Min. | Тур. | Max. | Units |

|-----------------|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|-------|

| VIH             | Input HIGH voltage    |                                                                                                       | 1.5  | -    | 2.0  | V     |

| VIL             | Input LOW voltage     |                                                                                                       | 1.0  | _    | 1.5  | V     |

| V <sub>H</sub>  | Hysteresis            |                                                                                                       | 320  | -    | -    | mV    |

| IIL             | Input leakage current | $\begin{array}{l} 0 \leq V_{PAD} \leq 3.63 \text{ V}, \\ V_{DD} = 3.3 \text{ V} \pm 10\% \end{array}$ | _    | _    | 10   | μA    |

| I <sub>LU</sub> | Latchup current       | $-2 V < V_{PAD} < +8 V$                                                                               | _    | _    | ±100 | mA    |

1. Values apply over all voltage, temperature, and process conditions

| Symbol          | Parameter                | Test Condition                                                               | Min. | Тур. | Max. | Units |

|-----------------|--------------------------|------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>DD</sub> | Supply voltage           | V <sub>OL</sub> and high impedance output only                               | 2.97 | 3.30 | 3.63 | V     |

| V <sub>OL</sub> | Output, LOW              | I <sub>OL</sub> = 4 mA                                                       | -    | -    | 0.4  | V     |

| V <sub>OH</sub> | Output, HIGH             | I <sub>OH</sub> = -4 mA<br>V <sub>DD</sub> = 3.135 V                         | 2.4  | -    | -    | V     |

| I <sub>OL</sub> | Sink current             | V <sub>OL</sub> = 0.4 V maximum,<br>totem-pole and open-drain mode           | 4    | -    | -    | mA    |

| I <sub>OH</sub> | Source current           | V <sub>OH</sub> = 2.4 V minimum,<br>totem-pole and open-source mode          | _    | -    | -4   | mA    |

| I <sub>OZ</sub> | 3-Stated leakage current | $0 \leq V_{PAD} \leq 5.5$ V, resistors disabled, $V_{DD}$ = 3.3 V $\pm 10\%$ | -    | -    | 20   | μA    |

| I <sub>LU</sub> | Latchup current          | -2 V < V <sub>PAD</sub> < +8 V                                               | _    | -    | ±100 | mA    |

# Table 11 Driver DC Characteristics<sup>1</sup>

1. Values apply over all voltage, temperature, and process conditions.

# **System Design Guidelines**

To ensure good system-level operation, LSI Logic provides the following guidelines for placing these I/O cells in the ASIC and for supplying power.

# Placement

All these I/O cells have the same dimensions (Table 12) and require placement on the I/O ring using one I/O slot.

Table 12 Cell Dimensions on the I/O Ring

| Width Along the I/O Ring | Length into the Chip |

|--------------------------|----------------------|

| 45.36 μm                 | 397.53 μm            |

For correct placement of the I/O cells, adhere to the following guidelines:

- These I/O cells may adjoin each other. They may also adjoin a bd4f5fs601s33 cell.

- Separate these I/O cells from any other type of I/O function by at least one I/O slot to avoid N-channel to P-channel design rule violations. If possible, use a VDD or VSS pad for the separation.

- Because their lengths exceed the length of other standard I/O functions, these I/O cells may not use a corner I/O slot.

# Power

For best system-level performance, adhere to the following power guidelines:

- Use one power/ground pad pair for every four I/O cells.

- Place an I/O cell no more than four slots away from a power pad and no more than four slots away from a ground pad.

#### Sales Offices and Design Resource Centers

LSI Logic Corporation Corporate Headquarters Tel: 408.433.8000 Fax: 408.433.8989

#### NORTH AMERICA

California Irvine ♦ Tel: 949.809.4600 Fax: 949.809.4444

Pleasanton Design Center Tel: 925.730.8800 Fax: 925.730.8700

San Diego Tel: 858.467.6981 Fax: 858.496.0548

Silicon Valley ◆ Tel: 408.433.8000 Fax: 408.954.3353

Wireless Design Center Tel: 858.350.5560 Fax: 858.350.0171

Colorado Boulder ♦ Tel: 303.447.3800 Fax: 303.541.0641

Colorado Springs Tel: 719.533.7000 Fax: 719.533.7020

Fort Collins Tel: 970.223.5100 Fax: 970.206.5549

Florida Boca Raton

Tel: 561.989.3236 Fax: 561.989.3237

**Georgia** Alpharetta Tel: 770.753.6146 Fax: 770.753.6147 Illinois Oakbrook Terrace Tel: 630.954.2234 Fax: 630.954.2235

**Kentucky** Bowling Green Tel: 270.793.0010 Fax: 270.793.0040

Maryland Bethesda Tel: 301.897.5800 Fax: 301.897.8389

Massachusetts Waltham ► Tel: 781.890.0180 Fax: 781.890.6158

Burlington - Mint Technology Tel: 781.685.3800 Fax: 781.685.3801

Minneapolis ♦ Tel: 612.921.8300 Fax: 612.921.8399

New Jersey Red Bank Tel: 732.933.2656 Fax: 732.933.2643

Cherry Hill - Mint Technology Tel: 856.489.5530 Fax: 856.489.5531

New York Fairport Tel: 716.218.0020 Fax: 716.218.9010

North Carolina Raleigh Tel: 919.785.4520 Fax: 919.783.8909

Oregon Beaverton Tel: 503.645.0589 Fax: 503.645.6612 **Texas** Austin Tel: 512.388.7294 Fax: 512.388.4171

Plano ◆ Tel: 972.244.5000 Fax: 972.244.5001

> Houston Tel: 281.379.7800 Fax: 281.379.7818

Canada Ontario Ottawa ♦ Tel: 613.592.1263 Fax: 613.592.3253

#### INTERNATIONAL

France Paris LSI Logic S.A. Immeuble Europa ♦ Tel: 33.1.34.63.13.13

Fax: 33.1.34.63.13.19

Germany Munich LSI Logic GmbH ♦ Tel: 49.89.4.58.33.0

Fax: 49.89.4.58.33.10

Stuttgart ♦ Tel: 49.711.13.96.90 Fax: 49.711.86.61.428

Italy Milan LSI Logic S.P.A.

♦ Tel: 39.039.687371 Fax: 39.039.6057867

Japan Tokyo LSI Logic K.K. ♦ Tel: 81.3.5463.7821 Fax: 81.3.5463.7820

Osaka ♦ Tel: 81.6.947.5281 Fax: 81.6.947.5287 Korea Seoul LSI Logic Corporation of Korea Ltd Tel: 82.2.528.3400 Fax: 82.2.528.2250

The Netherlands Eindhoven LSI Logic Europe Ltd Tel: 31.40.265.3580 Fax: 31.40.296.2109

Singapore Singapore LSI Logic Pte Ltd Tel: 65.334.9061 Fax: 65.334.4749

Sweden Stockholm LSI Logic AB ♦ Tel: 46.8.444.15.00 Fax: 46.8.750.66.47

Taiwan Taipei LSI Logic Asia, Inc. Taiwan Branch Tel: 886.2.2718.7828 Fax: 886.2.2718.8869

United Kingdom Bracknell LSI Logic Europe Ltd ◆ Tel: 44.1344.426544

▼ Tel: 44.1344.426544 Fax: 44.1344.481039

Sales Offices with Design Resource Centers

To receive product literature, visit us at http://www.lsilogic.com

**ISO 9000 Certified**

The LSI Logic logo design is a registered trademark of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

LSI Logic Corporation reserves the right to make changes to any products and services herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase, lease, or use of a product or service from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or of third parties.

AC Printed in USA Order No. 115043 Doc. No. DB08-000158-00