# ID240E01 4MB Flash Memory Card

(Model No.: ID240E01)

Spec No.: EL105110

Issue Date: May 27, 1998

- Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.

- •When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.

- (1) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (2). even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).

- · Office electronics

- · Instrumentation and measuring equipment

- · Machine tools

- · Audiovisual equipment

- · Home appliances

- · Communication equipment other than for trunk lines

- (2) Those contemplating using the products covered herein for the following equipment which demands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- · Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- · Mainframe computers

- · Traffic control systems

- · Gas leak detectors and automatic cutoff devices

- · Rescue and security equipment

- · Other safety devices and safety equipment, etc.

- (3) Do not use the products covered herein for the following equipment which demands extremely high performance in terms of functionality, reliability, or accuracy.

- · Aerospace equipment

- · Communications equipment for trunk lines

- · Control equipment for the nuclear power industry

- · Medical equipment related to life support, etc.

- (4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

- •Please direct all queries regarding the products covered herein to a sales representative of the company.

1

## ID240E01

| Contents                                                                              |      |

|---------------------------------------------------------------------------------------|------|

| 1. General Descriptions · · · · · · · · · · · · · · · · · · ·                         | p. 2 |

| 2. Features • • • • • • • • • • • • • • • • • • •                                     |      |

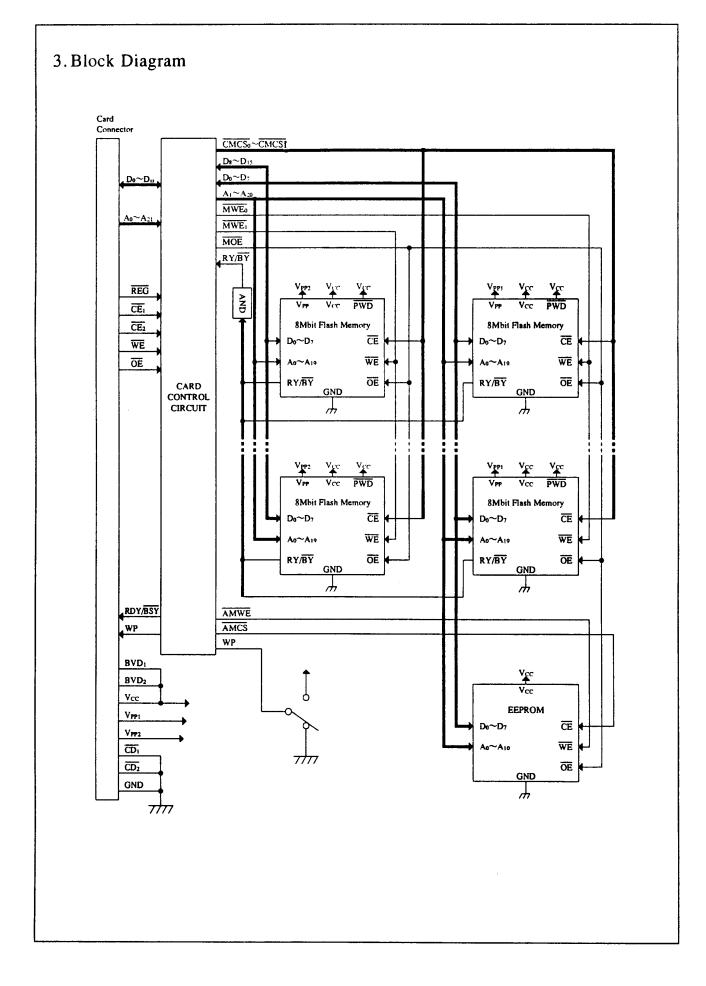

| 3. Block Diagram · · · · · · · · · · · · · · · · · · ·                                | p. 3 |

| 4. Pin Connections                                                                    | p. 4 |

| 5. Function Chart • • • • • • • • • • • • • • • • • • •                               | p. 5 |

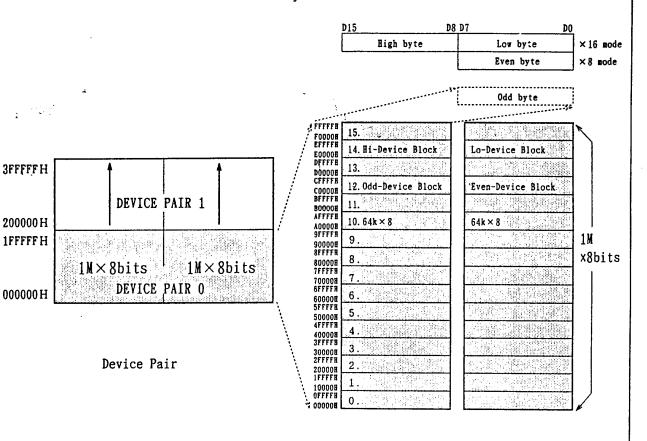

| 5.1 Memory Block · · · · · · · · · · · · · · · · · · ·                                | p. 5 |

| 5.1.1 Memory Configuration · · · · · · · · · · · · · · · · · · ·                      | p. 5 |

| 5.1.2 Memory Erase Unit • • • • • • • • • • • • • • • • • • •                         | p. 5 |

| 5.2 Function Table                                                                    | p. 6 |

| 5.3 Software Command                                                                  | 7, 8 |

| 5.4 Status Register • • • • • • • • • • • • • • • • • • •                             | p. 9 |

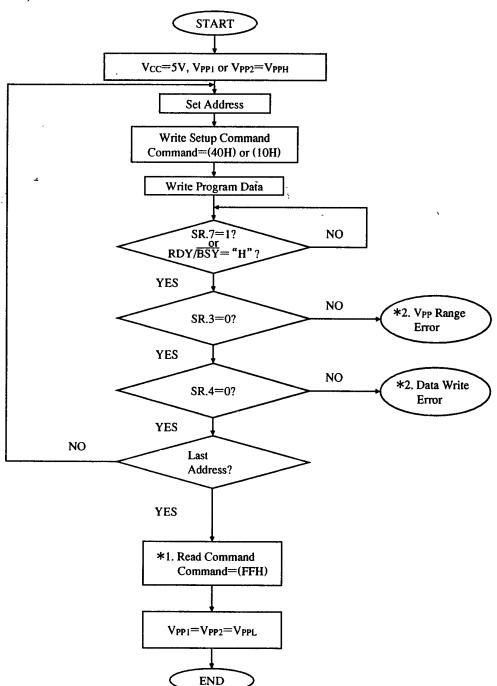

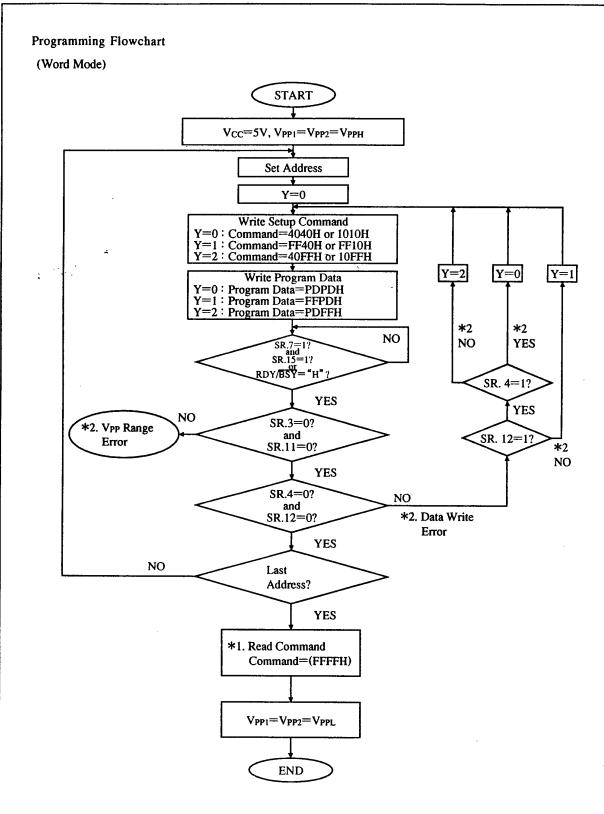

| 5.5 Programming Flowchart • • • • • • • • • • • • • • • • • • •                       | , 11 |

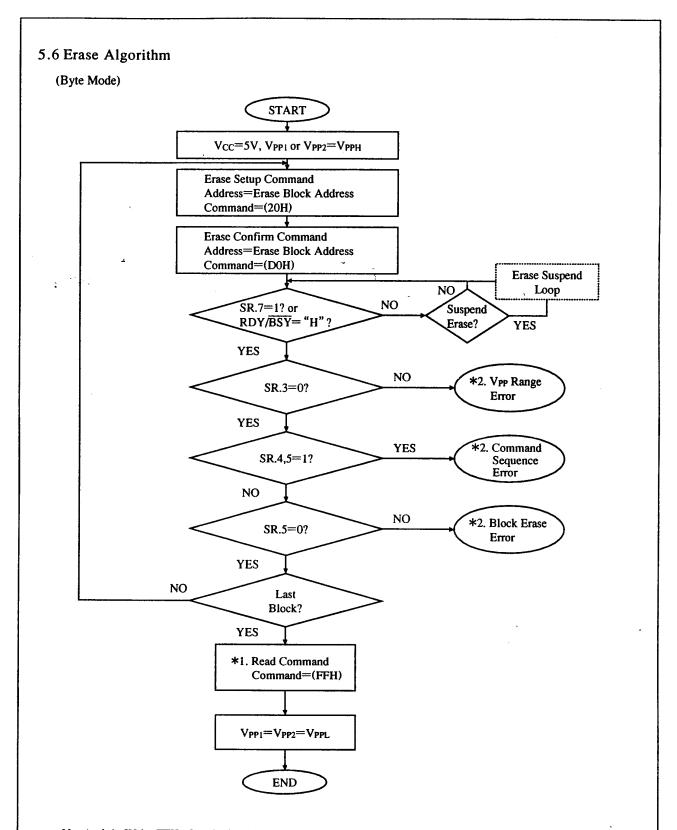

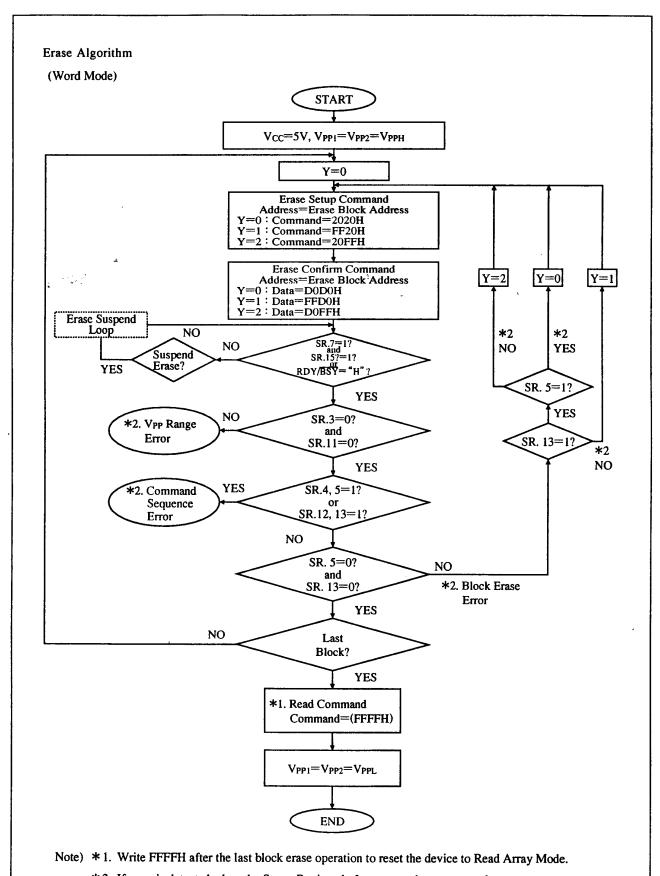

| 5.6 Erase Algorithm • • • • • • • • • • • • • • • • • • •                             | , 13 |

| 6. Absolute Maximum Ratings p                                                         | . 14 |

| 7. Recommended Operating Conditions · · · · · · · · · · · · · · · · · · p             | . 14 |

| 8. Capacitance · · · · · · · · · · · · · · · · p                                      | . 14 |

| 9. Read Operation • • • • • • • • • • • • • • • • • • •                               | . 15 |

| 9.1 DC Characteristics · · · · · · · · · · · · · · · · p                              | . 15 |

| 9.2 AC Characteristics • • • • • • • • • • • • • • • • • • •                          | , 17 |

| 10. Programming Operation • • • • • • • • • • • • • • • • • • •                       |      |

| 10.1 DC Characteristics · · · · · · · · · · · · · · · p.                              | . 17 |

| 10.2 AC Characteristics                                                               | , 20 |

| 11. Erase Operation · · · · · · · · · · · · · · · · · · ·                             |      |

| 11.1 DC Characteristics · · · · · · · · · · · · · · p                                 | . 21 |

| 11.2 AC Characteristics • • • • • • • • • • • • • • • • • • •                         | , 24 |

| 12. Block Erase and Data Write Characteristics • • • • • • • • • • • • • • • • • • •  | . 25 |

| •                                                                                     | . 25 |

| •                                                                                     | . 26 |

| 14.1 Attribute Memory Read/Write Function Chart • • • • • • • • • • • • • • • • • • • | . 26 |

| -                                                                                     | . 26 |

| •                                                                                     | . 27 |

| 14.4 Attribute Memory Write Cycle • • • • • • • • • • • • • • • • • • •               | , 29 |

| 15. Specification Changes · · · · · · · · · · · · · · · · · · ·                       | . 30 |

| •                                                                                     | . 30 |

| •                                                                                     | . 31 |

| -                                                                                     | . 32 |

| 19. External Appearances                                                              | . 33 |

ID240E01 2

#### 1. General Descriptions

SHARP

The SHARP ID240E01 is a 4MB Flash Memory PC Card conforms to PCMCIA Release 2.0 and is offered to customers giving aim to confirm an external shape or electrical performances of the card. Before mass production, we will create a new product name dedicated for a customer and also present a specification which implies customer's request including panel design.

#### 2. Features

4MB Flash Memory Card 2.1 Type -

(Conforms to PCMCIA Rel.2.0)

2.2 Memory Capacity

Common Memory 4M words × 8 bits or 2M words × 16 bits

EEPROM Model 2k words × 8 bits read/write Attribute Memory

Note) We have another type of attribute memory as follows,

No EEPROM Model. (5 words × 8 bits read only in card's control circuit.)

Sample card name: ID240E02. Customers can choose one model from two.

Supply Voltage 2.3

> Read Cycle  $V_{CC} = 5 \pm 0.5 \text{V}, V_{PP1}, V_{PP2} = 0 \sim 1.5 \text{V}$

Read/Program/Erase Cycle  $V_{CC} = 5 \pm 0.5 \text{V}, V_{PP1}, V_{PP2} = 12.0 \text{V} \pm 0.6 \text{V}$

Erase Unit Block

(64k bytes/byte access, 128k bytes/word access)

2.5 Program/Erase Cycles 100,000 cycles

2.6 Interface Parallel I/O Interface

2.7 **Function Table** See Function Table in page. 6

2.8 **External Dimensions**  $54 \times 85.6 \times 3.3$  mm

2.9 Pin Connections See Pin Connections in page. 4

2.10 Type of Connector Conforms to PCMCIA Re1.2.0 Card Use Connector

(Card connector: JC20-J68S-NB3 JAE or FCN-568J068-G/0 Fujitsu

or ICM-C68S-TS13-5035A JST)

2.11 Average Weight 30g

0 to 60℃ 2.12 Operating Temp Range

2.13 Storage Temp Range -20 to 65℃

2.14 External Appearance External appearance shall be free of any dirt, cratches and abnor-

malities that could adversely affect sales.

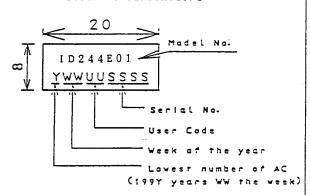

2.15 Manufacturer's Code The manufacturer's code shall be printed on the memory card di-

rectly or on the seal which is then attached to the memory card.

2.16 Brand Name The user's brand name will be used.

2.17 Not designed or rated radiation hardened.

#### 4. Pin Connections

| PIN | SIGNAL          | PIN | SIGNAL          | PIN | SIGNAL                     | PIN | SIGNAL                     |

|-----|-----------------|-----|-----------------|-----|----------------------------|-----|----------------------------|

| 1   | GND             | 18  | $V_{pp_1}$      | 35  | GND                        | 52  | $V_{PP2}$                  |

| 2   | $D_3$           | 19  | A <sub>16</sub> | 36  | $\overline{\text{CD}}_{1}$ | 53  | A <sub>22</sub> (NC)       |

| 3   | $D_4$           | 20  | A <sub>15</sub> | 37  | $D_{11}$                   | 54  | A <sub>23</sub> (NC)       |

| 4   | $D_5$           | 21  | A <sub>12</sub> | 38  | D <sub>12</sub>            | 55  | A <sub>24</sub> (NC)       |

| 5   | $D_6$           | 22  | A <sub>7</sub>  | 39  | D <sub>13</sub>            | 56  | A <sub>25</sub> (NC)       |

| 6   | $D_7$           | 23  | $A_6$           | 40  | $D_{14}$                   | 57  | NC                         |

| 7   | <del>CE</del> i | 24  | A <sub>5</sub>  | 41  | $D_{15}$                   | 58  | NC                         |

| 8   | A <sub>10</sub> | 25  | A <sub>4</sub>  | 42  | $\overline{\text{CE}}_2$   | 59  | NC                         |

| 9   | . ŌĒ            | 26  | A <sub>3</sub>  | 43  | NC                         | 60  | NC                         |

| 10  | A <sub>11</sub> | 27  | A <sub>2</sub>  | 44  | NC                         | 61  | REG                        |

| 11  | A <sub>9</sub>  | 28  | A <sub>1</sub>  | 45  | . NC                       | 62  | $BVD_2$                    |

| 12  | A <sub>8</sub>  | 29  | A <sub>0</sub>  | 46  | A <sub>17</sub>            | 63  | $BVD_1$                    |

| 13  | A <sub>13</sub> | 30  | $D_0$           | 47  | A <sub>18</sub>            | 64  | $D_8$                      |

| 14  | A <sub>14</sub> | 31  | D <sub>i</sub>  | 48  | A <sub>19</sub>            | 65  | D <sub>9</sub>             |

| 15  | WE/PGM          | 32  | $D_2$           | 49  | A <sub>20</sub>            | 66  | $D_{i0}$                   |

| 16  | RDY/BSY         | 33  | WP              | 50  | A <sub>21</sub>            | 67  | $\overline{\mathrm{CD_2}}$ |

| 17  | $V_{\rm cc}$    | 34  | GND             | 51  | $V_{cc}$                   | 68  | GND                        |

#### Pin Descriptions:

D<sub>0</sub>~D<sub>7</sub> Data Bus (Input/output)

D<sub>8</sub>~D<sub>15</sub> Data Bus (Input/output)

A<sub>0</sub>~A<sub>22</sub> Address Bus (Input)

$\overline{CE}_1$ ,  $\overline{CE}_2$  Card Enable (Input)

02[, 02]

OE Output Enable (Input)

WE/PGM Write Enable/Program (Input)

$\overline{\text{CD}}_1$ ,  $\overline{\text{CD}}_2$  Card Detect (Output) (Card Inserted Detection Signal)

WP Write Protect (Output) (in write protect mode, the WP output signal is "HIGH")

V<sub>PPI</sub> Program/Erase Power Supply (Even Byte)

V<sub>PP2</sub> Program/Erase Power Supply (Odd Byte)

REG Register Select (Input)

BVD<sub>1</sub>, BVD<sub>2</sub> Battery Voltage Detect (Always "HIGH")

RDY/BSY Ready/Busy (Output)

#### 5. Function

#### 5.1 Memory Block

5.1.1 Memory Configuration

8Mbits Flash Memory × 4 Devices.

5.1.2 Memory Erase Unit

**Block Erase**

Block:

Byte Mode

64k bytes

Word Mode

128k bytes

Block Pair

;

#### 5.2 Function Table

| $\overline{CE}_{i}$ | $\overline{\text{CE}}_2$ | A <sub>o</sub> | WE | ŌĒ | REG | $V_{PP1}$        | $V_{PP2}$ | $V_{cc}$ | Operation     | $D_0$ - $D_7$ | D <sub>8</sub> -D <sub>15</sub> | Status  |

|---------------------|--------------------------|----------------|----|----|-----|------------------|-----------|----------|---------------|---------------|---------------------------------|---------|

| Н                   | Н                        | ×              | ×  | ×  | Н   | $V_{PPL}$        | $V_{PPL}$ | $V_{cc}$ |               | Hi-Z          | Hi-Z                            | Standby |

| L                   | Н                        | L              | H  | L  | Н   | $V_{PPL}$        | $V_{PPL}$ | $V_{cc}$ | Read (×8)     | Do (Even)     | Hi-Z                            | Byte    |

| L                   | Н                        | Н              | Н  | L. | Н   | $V_{PPL}$        | $V_{PPL}$ | $V_{cc}$ | Read (×8)     | Do (Odd)      | Hi-Z                            | Byte    |

| L                   | L                        | ×              | Н  | L  | Н   | $V_{PPL}$        | $V_{PPL}$ | $V_{cc}$ | Read (×16)    | Do (Even)     | Do (Odd)                        | Word    |

| Н                   | L                        | ×              | Н  | L  | Н   | $V_{PPL}$        | $V_{PPL}$ | $V_{cc}$ | Read (×8)     | Hi-Z          | Do (Odd)                        | Byte    |

| L                   | ×                        | ×              | ×  | Н  | Н   | $V_{PPL}$        | $V_{PPL}$ | $V_{cc}$ | Outpu Disable | Hi-Z          | Hi-Z                            | Byte    |

| Н                   | L                        | ×              | ×  | Н  | H   | $V_{PPL}$        | $V_{PPL}$ | $V_{cc}$ | Outpu Disable | Hi-Z          | Hi-Z                            | Byte    |

| L                   | H                        | L              | L  | Н  | Н   | $V_{PPH}$        | $V_{PPX}$ | $V_{cc}$ | Program (×8)  | Di (Even)     | Don't care                      | Byte    |

| L                   | Н                        | ιH             | L  | H  | Н   | $V_{PPX}$        | $V_{PPH}$ | $V_{cc}$ | Program (×8)  | Di (Odd)      | Don't care                      | Byte    |

| L                   | L                        | ×              | L  | Н  | Н   | V <sub>PPH</sub> | $V_{PPH}$ | $V_{cc}$ | Program (×16) | Di (Even)     | Di (Odd)                        | Word    |

| . Н                 | L                        | ×              | L  | Н  | H   | $V_{PPX}$        | $V_{PPH}$ | $V_{cc}$ | Program (×8)  | Don't care    | Di (Odd)                        | Byte    |

| L                   | Н                        | L              | Н  | L  | Н   | $V_{PPH}$        | $V_{PPX}$ | $V_{cc}$ | Verify (×8)   | Do (Even)     | Hi-Z                            | Byte    |

| L                   | Н                        | H              | H  | L  | Н   | $V_{PPX}$        | $V_{PPH}$ | $V_{cc}$ | Verify (×8)   | Do (Odd)      | Hi-Z                            | Byte    |

| L                   | L                        | ×              | Н  | L  | Н   | $V_{PPH}$        | $V_{PPH}$ | $V_{cc}$ | Verify (×16)  | Do (Even)     | Do (Odd)                        | Word    |

| Н                   | L                        | ×              | H  | L  | Н   | $V_{PPX}$        | $V_{PPH}$ | $V_{cc}$ | Verify (×8)   | Hi-Z          | Do (Odd)                        | Byte    |

| L                   | Н                        | Н              | L  | L  | Н   | $V_{PPH}$        | $V_{PPX}$ | $V_{cc}$ | *1 Prohibited |               | _                               |         |

| L                   | H                        | L              | L  | L  | Н   | $V_{PPX}$        | $V_{PPH}$ | $V_{cc}$ | *1 Prohibited | _             |                                 | -       |

| L                   | L                        | ×              | L  | L  | Н   | $V_{PPH}$        | $V_{PPH}$ | $V_{cc}$ | *1 Prohibited |               |                                 | _       |

| Н                   | L                        | ×              | L  | L  | Н   | $V_{PPX}$        | $V_{PPH}$ | $V_{cc}$ | *1 Prohibited |               |                                 |         |

\*1. Do not use this mode as it will result in write errors.

Н : High L : Low × : Don't Care

: Input Data Di

Do : Output Data Hi-Z : High Impedance

: 4.5 ∼ 5.5V  $V_{cc}$

$V_{PPL}$  :  $0.0 \sim 1.5 V$

$V_{PPH}$  : 11.4  $\sim$  12.6 V

$V_{PPX} : V_{PPL} \text{ or } V_{PPH}$

Caution: When the write Protect switch is in protect-mode, the WP signal is "HIGH" and write operation are not allowed.

#### 5.3 Software Command (8/16 Bits Operation ( ):16 Bits Operation)

| Command                                | Bus Cycles | F         | irst Bus Cyc | le              |           | Second I | Bus Cycle       |             |

|----------------------------------------|------------|-----------|--------------|-----------------|-----------|----------|-----------------|-------------|

| Command                                | Dus Cycles | Operation | Address      | Data            | Operation | Address  | Data Input      | Data Output |

| Read<br>Array/Reset                    | 1          | Write     | RA           | FFH/<br>(FFFFH) |           | _        | <del></del>     |             |

| Read<br>Intelligent<br>Identifier      | 3          | Write     | DA           | 90H/<br>(9090H) | Read      | IA       | _               | IID         |

| Read Status<br>Register                | 2          | Write     | DA           | 70H/<br>(7070H) | Read      | DA       |                 | SRD         |

| Clear Status<br>Register               | 1          | Write     | DA           | 50H/<br>(5050H) |           |          | `               |             |

| Erase<br>Setup/Erase<br>Confirm        | 2          | Write     | BA           | 20H/<br>(2020H) | Write     | ВА       | D0H/<br>(D0D0H) |             |

| Erase<br>Suspend/Erase<br>Resume       | 2          | Write     | ВА           | B0H/<br>(B0B0H) | Write     | BA       | D0H/<br>(D0D0H) | _           |

| Byte Write<br>Setup/Write              | 2          | Write     | WA           | 40H/<br>(4040H) | Write     | WA       | WD              |             |

| Alternate<br>Byte Write<br>Setup/Write | 2          | Write     | WA           | 10H/<br>(1010H) | Write     | WA       | WD              |             |

Note) 1. This Table shows the basic from of Erase, Verify and Program Verify.

Refer Programming Flowchart, Erase Algorithm in detail.

2. Bus operations are defined in function table in page.

3. IA: Device Identifier Address IID

IID: Device Identifier Data

|                   |                 |                        | IA                    |         |                 |                  |  |

|-------------------|-----------------|------------------------|-----------------------|---------|-----------------|------------------|--|

|                   | DA              | 8Bits<br>(Even Device) | 8Bits<br>(Odd Device) | 16Bits  | Byte<br>(8Bits) | Word<br>(16Bits) |  |

| Manufacturer Code | 000000H∼1FFFFFH | 000000Н                | 000001H               | 000000Н | 89H             | 8989H            |  |

| Device Code       | 000000H∼1FFFFFH | 000002H                | 000003Н               | 000001H | A2H             | A2A2H            |  |

RA : Read Address

WA: Write Address

WD: Write Data

DA : Device Address (Any Address in device is acceptable.)

BA : Erase Block Address (Erase Size is 64k Bytes.)

SRD: Status Register Data

4. Either 40H (4040H) or 10H (1010H) are recognized by the WSM as the Byte Write Setup Command.

a) Read Array/Reset Command: (FFH/FFFFH)

By writing this command, device. Devices pair become read mode. The device remains enable for reads until the Command User Interface contents are altered.

b) Intelligent Identifier Command: (90H/9090H):

After writing this command into the Command User Interface, a read cycle retrieves the manufacturer Code and device Code. To terminate the Operation, it is necessary to write another valid command into the register.

c) Read Status Register Command: (70H/7070H):

By Writing this command, the Status Register may be read at any time to determine when a byte or block erase operation is complete, and whether that operation completed successfully.

Refer to Status Register definition in page. 9. After writing this command, all subsequent read operations output data from the Status Register, until another valid command is written to the Command User Interface.

d) Clear Status Register Command: (50H/5050H)

Status bits which show error, the Erase Status (SR. 5), Byte Write Status (SR. 4) bits and the  $V_{PP}$  Status bit (SR. 3) can be reset by the Clear Status Machine Register Command.

e) Erase Setup/Erase Command: (20H/2020H) (D0H/D0D0H): Erase is executed one block (64kB for 1 device, 128kB for 2 devices) at a time.

This command is functional when  $V_{PP} = V_{PPH}$  and an Erase Setup Command is first written to the Command User Interface, followed by the Erase Confirm Command. After that, the device automatically outputs Status Register data when read.

The CPU can detect the completion of the erase event by analyzing the output of the RDY/BSY pin, or the WSM Status bit of the Status Register. When erase is completed, the Erase Status bit should be checked. If erase error is detected, the Status Register should be cleared.

f) Erase Supend/Erase Resume Command: (B0H/B0B0H) / (D0H/D0D0H)

The Erase Suspend command allows block erase interruption in order to read data from another block of memory. The device continues to output Status Register data when read, after the Erase Suspend Command is written. Polling the WSM Status and Erase Suspend Status bits will determine when the erase operation has been suspended.  $RDY/\overline{BSY}$  pin will also transition to  $V_{OH}$ . At this point, a Read Array Command can be written to the Command User Interface to read data from blocks other than that which is suspended.  $V_{PP}$  must remain at  $V_{PPH}$  while device is in Erase Suspend.

Erase Resume Command, at which time the WSM will continue with the erase process. The Erase Suspend Status and WSM Status bits of the Status Register will be automatically cleared and RDY/ $\overline{BSY}$  pin will return to  $V_{OL}$ . After the Erase Resume is written, the device automatically output Status Register data when read.

g) Byte Write Setup/Write Command: (40H/4040H) or (10H/1010H)

This command is functional when  $V_{PP} = V_{PPH}$  and an Byte Write Setup Command is first written to the Command User Interface, followed by a second write specifying the address and data to be written. The WSM then take over, controlling the byte write and write verify algorithms internally. After the two command byte sequence is written to it, the device automatically outputs Status Register data when read. The CPU can detect the completion of the byte write event by analyzing the output of the RDY/ $\overline{BSY}$  pin, or the WSM Status bits of the Status Register.

## 5.4 Status Register

The memory devices in this card have Status Register which shows state of the device.

#### Byte Access × 8 Bits

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| SR.7 | SR.6 | SR.5 | SR.4 | SR.3 | SR.2 | SR.1 | SR.0 |

| WSMS | ESS  | ES   | BWS  | VPPS | RFU  | RFU  | RFU  |

| Register                                      | Contents                                                                        |

|-----------------------------------------------|---------------------------------------------------------------------------------|

| SR.7=Write State Machine Status               |                                                                                 |

| 1 = Ready                                     | When set "1" s, read, erase, data write is acceptable.                          |

| 0=Busy                                        |                                                                                 |

| · SR.6=Erase Suspend Status                   |                                                                                 |

| 1=Erase Suspend                               | Check whether Erase Suspend Command is executed or not.                         |

| 0=Erase In Progress/Completed                 | of not.                                                                         |

| SR.5=Erase Status                             | G . "1" 1 C !! . T                                                              |

| 1 = Error In Block Erase                      | Set "1" s when fail to Erase.  Reset by the Clear Status Register Command.      |

| 0=Successful Block Erase                      | Reset by the clear diatus Register Command.                                     |

| SR.4=Byte Write Status                        | Cas "1" - when fall as Posts With                                               |

| 1 = Error In Byte Write                       | Set "1" s when fail to Byte Write.  Reset by the Clear Status Register Command. |

| 0=Successful Byte Write                       | Reset by the clear status register command.                                     |

| $SR.3 = V_{PP}$ Status                        | Set "1" s when V <sub>PP</sub> , which is needed in Byte Write or               |

| 1=V <sub>PP</sub> Low Detect; Operation Abort | Erase operation, is below V <sub>PPH</sub> . Reset by the Clear                 |

| $0 = V_{PP} OK$                               | Status Register Command.                                                        |

| SR.2~SR.0=Reserved for Future Use             |                                                                                 |

#### Word Access × 16 bits

| bit15                                         | bit8      | bit7 |      |      |        |          |      |      | bit0 |

|-----------------------------------------------|-----------|------|------|------|--------|----------|------|------|------|

| SR.15   SR.14   SR.13   SR.12   SR.11   SR.10 | SR.9 SR.8 | SR.7 | SR.6 | SR.5 | SR.4   | SR.3     | SR.2 | SR.1 | SR.0 |

| Odd Byte device                               |           |      |      | E    | ven By | te devic | ·e   |      | •    |

#### 5.5 Programming Flowchart

(Byte Mode)

Note) \* 1. Write FFH after the last block write operation to reset the device to Read Array Mode.

Note) \* 1. Write FFFFH after the last block write operation to reset the device to Read Array Mode.

Note) \* 1. Write FFH after the last block erase operation to reset the device to Read Array Mode.

# 6. Absolute Maximum Ratings

| PARAMETER             | SYMBOL           | RATING                               | UNIT       |

|-----------------------|------------------|--------------------------------------|------------|

| Supply Voltage        | $V_{cc}$         | -0.3 to 7.0                          | V          |

| Input Voltage         | V <sub>IN</sub>  | $-0.3$ to $V_{cc}+0.3$ (Max: 7.0)    | V          |

| Output Voltage        | V <sub>out</sub> | $-0.3$ to $V_{cc} + 0.3$ (Max : 7.0) | V          |

| Operating Temperature | T <sub>OPR</sub> | 0 to +60                             | $^{\circ}$ |

| Storage Temperature   | T <sub>STG</sub> | -20 to+65                            | °C         |

# 7. Recommended Operating Conditions

| PARAMETER             | SYMBOL           | Min.  | Max.                 | UNIT       |

|-----------------------|------------------|-------|----------------------|------------|

| Operating Temperature | T <sub>OPR</sub> | 0     | +60                  | $^{\circ}$ |

| Supply Voltage        | V <sub>cc</sub>  | , 4.5 | 5.5                  | V          |

| Input Voltage High    | V <sub>IH</sub>  | 3.5   | V <sub>cc</sub> +0.3 | V          |

| Input Voltage Low     | V <sub>IL</sub>  | -0.3  | 1.5                  | V          |

# 8. Capacitance

| PARAMETER                | SYMBOL          | Min. | TYP | Max. | UNIT | CONDITION              |

|--------------------------|-----------------|------|-----|------|------|------------------------|

| Input Capacitance        | C <sub>IN</sub> | _    | 17  | _    | pF   | $V_{cc} = 5V \pm 10\%$ |

| Input/Output Capacitance | C <sub>io</sub> | _    | 17  |      | pF   | f=1MHz, Ta=25℃         |

## 9. Read Operation

#### 9.1 DC Characteristics

$(V_{CC}=4.5\sim5.5V, Ta=0\sim60°C)$

| PAR             | AMETER                                                                                       | SYMBOL          | Min.                 | TYP | Max.           | UNIT | CONDITION                                          |  |

|-----------------|----------------------------------------------------------------------------------------------|-----------------|----------------------|-----|----------------|------|----------------------------------------------------|--|

| Operating       | High Temperature                                                                             | V <sub>cc</sub> | 4.5                  |     | 5.5            | v    |                                                    |  |

| Voltage         | Low Temperature                                                                              | V CC            | 4.5                  |     | 5.5            | v    |                                                    |  |

| Current         | Static Operatin Current                                                                      | I <sub>sb</sub> | -                    |     | 2.0            | A    | X16, Address:                                      |  |

| Consumption * 1 | Dynamic Operating Current                                                                    | $I_{cc}$        |                      | _   | 80             | mA   | PingPong                                           |  |

| Input Voltage   | Input Voltage Level High                                                                     | V <sub>IH</sub> | 3.5                  |     | $V_{cc} + 0.3$ | v    | V <sub>cc</sub> =4.5~5.5V                          |  |

| input voltage.  | Input Voltage Level Low                                                                      | $V_{IL}$        | -0.3                 | _   | 1.5            | V    |                                                    |  |

| Input Current   | $A_0 \sim A_{20}, D_0 \sim D_{15}$                                                           | T               | -10                  |     | 70             | A    |                                                    |  |

| Input Current   | $\overline{CE}_1$ , $\overline{CE}_2$ , $\overline{OE}$ , $\overline{WE}$ , $\overline{REG}$ | $I_{l,1}$       | <b>-70</b>           | -   | 10             | μΑ   | $V_i = V_{cc}, 0V$                                 |  |

| Output Voltage  | High                                                                                         | V <sub>oн</sub> | V <sub>cc</sub> ~0.5 | . — | _              | v    | $I_{OH} = -2mA (*^2)$<br>$I_{OH} = -4 \mu A (*^3)$ |  |

|                 | Low                                                                                          | V <sub>oL</sub> |                      |     | 0.4            | `    | I <sub>OL</sub> =4mA                               |  |

PingPong: Scan the target address, with accessing the target and another address alternately.

- \*1 (1) Static Operating Current: With the memory card's voltage at 5.5V and the  $\overline{CE}_1$ ,  $\overline{CE}_2$   $\overline{OE}$ ,  $\overline{WE}$  and  $\overline{REG}$  signals "HIGH" ( $V_{IH} = V_{CC} = 0.2V$ ),  $A_0$  signal "LOW" ( $V_{IL} \le 0.2V$ ) the current consumption is measured with the output open.

- (2) Dynamic Operating Current: With the memory card's V<sub>CC</sub> at 5.5V and V<sub>PP1</sub> = V<sub>PP2</sub> at 12.6V, current consumption during access is measured with the output open.

(Access time: 200ns) The current depends on addressing.

- \*2 D<sub>0</sub>~D<sub>15</sub>

- \*3 BVD<sub>1</sub>, BVD<sub>2</sub>, RDY/BSY, WP

#### 9.2 AC Characteristics ( $V_{CC}=4.5\sim5.5V$ , $V_{PP}=0.0\sim1.5V$ , $Ta=0\sim60^{\circ}C$ )

Testing Conditions:

Input Pulse Level : 0.8~3.5V

Input Rise/Fall Time : 10ns

Input/Output Timing Reference Level : 1.5V

4) Output Load : 1TTL+C<sub>L</sub> (100pF) (including scope and jig capacitance)

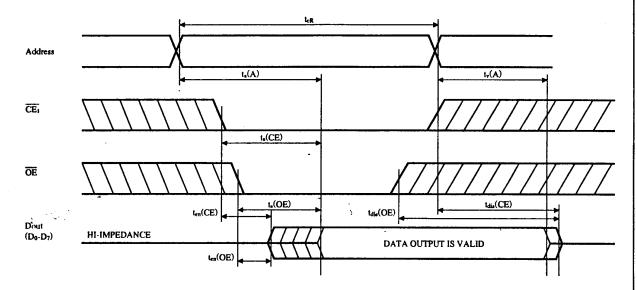

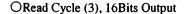

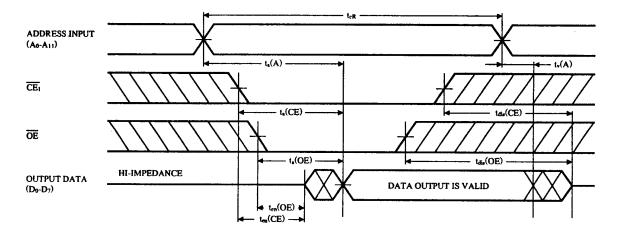

9.2.1 Read Cycle

$(V_{CC}=4.5\sim5.5V, V_{PP}=0.0\sim1.5V, Ta=0\sim60^{\circ}C)$

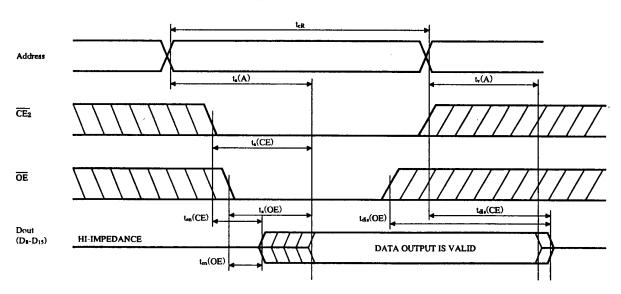

| PARAMETER                    | SYMBOL            | SYMBOL (PCMCIA)       | Min. | Max. | UNIT |

|------------------------------|-------------------|-----------------------|------|------|------|

| Read Cycle Time              | t <sub>AVAV</sub> | t <sub>eR</sub>       | 200  | _    |      |

| Address Access Time          | t <sub>AVQV</sub> | t <sub>a</sub> (A)    |      | 200  | 1    |

| Card Enable Access Time      | t <sub>ELQV</sub> | t <sub>a</sub> (CE)   |      | 200  | 1    |

| Output Enable Access Time    | $t_{GLQV}$        | t <sub>a</sub> (OE)   |      | 100  | 1    |

| Output Disable Time from CE∗ | t <sub>EHQV</sub> | t <sub>dis</sub> (CE) | _    | 90   | ns   |

| Output Disable Time from OE* | t <sub>GHQZ</sub> | t <sub>dis</sub> (OE) | _    | 90   | 1    |

| Output Enable Time from CE   | t <sub>ELQX</sub> | t <sub>en</sub> (CE)  | 5    | _    | 1    |

| Output Enable Time form OE   | $t_{GLQX}$        | t <sub>en</sub> (OE)  | 5    |      | 1    |

| Data Valid from Add Change   |                   | t <sub>v</sub> (A)    | 0    |      | 1    |

<sup>\*</sup> Time until output becomes floating. (The output voltage is not defined.)

ORead CYCLE (1) ( $\overline{CE}_2 = V_{IH}$  Fixed), 8bits Output

- Note) 1. WE="HIGH", during a read cycle.

- 2. Either "HIGH" or "LOW" in diagonal areas.

- 3. The output data becomes valid when last interval,  $t_a$  (A),  $t_a$  (CE) or  $t_a$  (CE) have concluded.

ORead Cycle (2) ( $\overline{CE}_1 = V_{IH}$  Fixed), 8Bits Output

- Note) 1. WE="HIGH", during a read cycle.

- 2. Either "HIGH" or "LOW" in diagonal areas.

- 3. The output data becomes valid when last interval,  $t_a$  (A),  $t_a$  (CE) or  $t_a$  (CE) have concluded.

- Note) 1. WE="HIGH", during a read cycle.

- 2. Either "HIGH" or "LOW" in diagonal areas.

- 3. Change  $\overline{CE_1}$  and  $\overline{CE_2}$  at the same time.

- 4. The output data becomes valid when last interval, t, (A), t, (CE) or t, (CE) have concluded.

## 10. Programming Operation

#### 10.1 DC Characteristics

| 1 | $V_{\alpha\alpha}=4$ | 5~55 | VV.     | =11   | 4~12  | 6V  | $T_9 = 0$ | ~60°C) |

|---|----------------------|------|---------|-------|-------|-----|-----------|--------|

| 1 | V CC 7               |      | V . V t | D II. | 7 12. | υν. | 1 a – \   | , -000 |

| PARAMET                                                  | ER      | SYMBOL           | Min.          | Max.             | UNIT | CONDITION            |

|----------------------------------------------------------|---------|------------------|---------------|------------------|------|----------------------|

| 37 37                                                    | Read    | $V_{PPL}$        | 0             | 1.5              |      |                      |

| V <sub>PP1</sub> , V <sub>PP2</sub> operating<br>Voltage | Program | $V_{pph}$        | 11.4          | 12.6             | v    |                      |

| V <sub>PP1</sub> , V <sub>PP2</sub> operating            | Read    | l <sub>SB2</sub> |               | 1.6              |      | Input open           |

| Current<br>(×16 Mode)                                    | Program | $I_{pp}$         | —             | 20               | mA   | RMS                  |

| V <sub>cc</sub> operating                                | Standby | I <sub>sbi</sub> | _             | 2                | ]    | Input open           |

| Current                                                  | Program | $I_{cc}$         |               | 75               |      | RMS                  |

| Input Voltage                                            |         | $V_{iL}$         | -0.3          | 1.5              |      |                      |

| input voitage                                            |         | $V_{IH}$         | 3.5           | $V_{\infty}+0.3$ | v    |                      |

| Output Voltage<br>During Verify                          |         | V <sub>oL</sub>  | _             | 0.4              | ]    | I <sub>oL</sub> =4mA |

|                                                          |         | $V_{OH}$         | $V_{cc}$ -0.5 |                  |      | $I_{OH} = -2mA$      |

- Note) 1. Power on  $V_{cc}$  before power on  $V_{cc}$ , power off  $V_{cc}$  after power off  $V_{pp}$ .

- 2. Keep  $V_{PP}$  including its overshoot, below 13V.

- 3. Card insertion or removal while applying  $V_{PP}=12V$  may cause a loss of integrity.

- 4. Do not turn on or turn off during  $\overline{CE}$ ="LOW".

- 5. If  $V_{IH}$  goes above  $V_{CC}+0.3V$ , normal operation is not assured.

#### 10.2 AC Characteristics ( $V_{CC}=4.5\sim5.5V$ , $V_{PP}=11.4\sim12.6V$ , $T_a=0\sim60^{\circ}C$ )

Testing Conditions:

1) Input Pulse Level

: 0.8~3.5V

2) Input Rise/Fall Time

: 10ns

3) Input/Output Timing Reference Level

: 1.5V

4) Output Load

: 1TTL+C<sub>L</sub> (100pF) (including scope and jig capacitance)

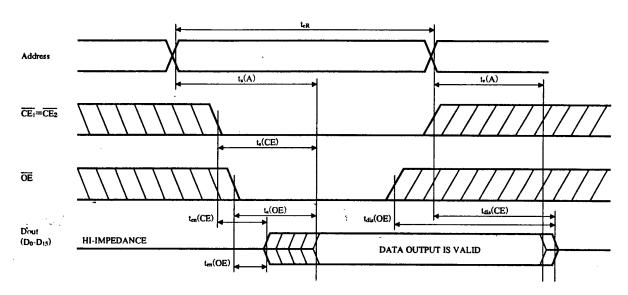

#### 10.2.1 Program Cycle

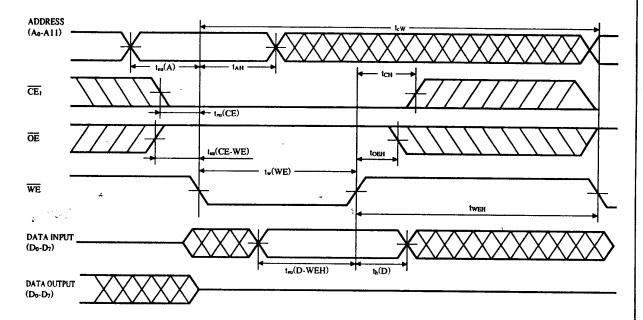

WE Controlled

$(V_{cc}=4.5\sim5.5V, V_{PP}=11.4\sim12.6V, Ta=0\sim60^{\circ}C)$

|                                                   |                    | ( , ()                   | · FF | ,    |      |

|---------------------------------------------------|--------------------|--------------------------|------|------|------|

| PARAMETER                                         | SYMBOL             | SYMBOL (PCMCIA)          | Min. | Max. | UNIT |

| Write Cycle Time                                  | t <sub>AVAV</sub>  | t <sub>eW</sub>          | 200  |      |      |

| Address Setup Time                                | tavwl              | t,u (A)                  | 20   |      |      |

| Write Recovery Time                               | twhax              | t <sub>rea</sub> (WE)    | 30   | _    |      |

| Data Setup Time for WE                            | t <sub>DVWH</sub>  | t,u (D-WEH)              | 60   |      |      |

| Data Hold Time                                    | t <sub>whDX</sub>  | t <sub>h</sub> (D)       | 30   |      |      |

| Write Recovery Before Read                        | t <sub>wHGL</sub>  |                          | 10   | _    |      |

| Card Enable Setup time for WE                     | t <sub>ELWH</sub>  | t <sub>su</sub> (CE-WEH) | 140  |      | ns   |

| Address Setup for WE                              | t <sub>AVWH</sub>  | t <sub>su</sub> (A-WEH)  | 140  |      |      |

| Card Enable Hold Time                             | t <sub>when</sub>  |                          | 15   | _    |      |

| Write Pulse Width                                 | twlwh              | t <sub>w</sub> (WE)      | 120  |      |      |

| Write Pulse Width High                            | twhwL              | tw (WEH)                 | 30   | _    |      |

| WE High to RDY/BSY Going Low                      | twirl              |                          |      | 150  |      |

| Duration of write                                 |                    |                          |      |      |      |

| operation                                         | t <sub>WHQV1</sub> |                          | 4.8  |      | μς   |

| V <sub>PP</sub> Setup to WE Going High            | t <sub>vpwH</sub>  |                          | 100  | _    |      |

| V <sub>PP</sub> Hold from Valid SRD, RDY/BSY High | t <sub>QVVL</sub>  |                          | 0    | _    | ns   |

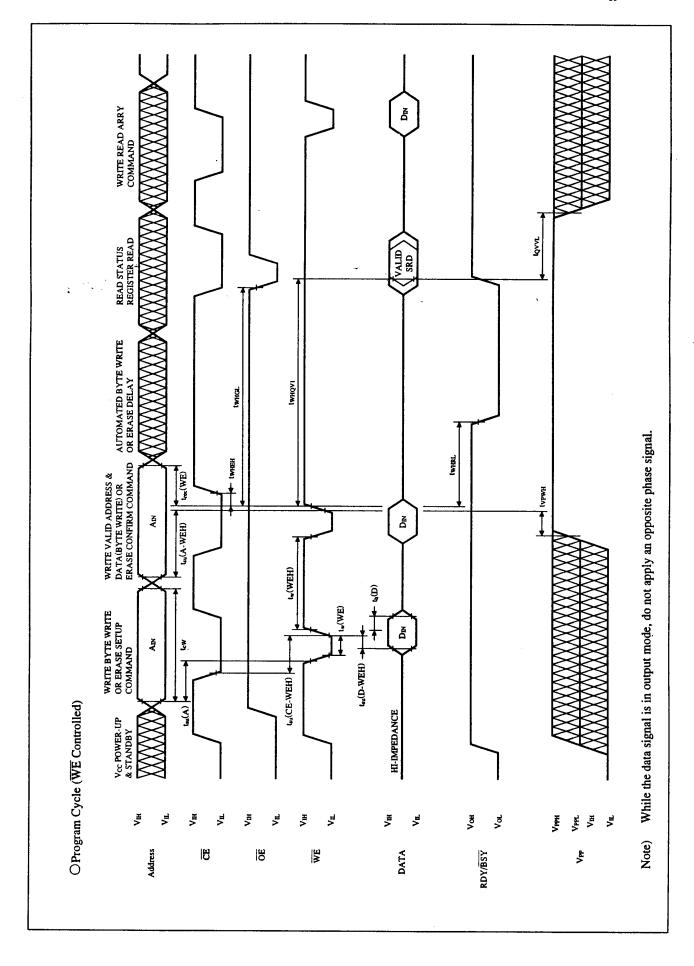

CE Controlled

$(V_{cc}=4.5\sim5.5V, V_{pp}=11.4\sim12.6V, Ta=0\sim60^{\circ}C)$

| CL Condoned                                       |                    | ( 700 7.5 5.5 7, 1       | v pp 11.— | 12.0 V, 1a | 0 · 00 C, |

|---------------------------------------------------|--------------------|--------------------------|-----------|------------|-----------|

| PARAMETER                                         | SYMBOL             | SYMBOL (PCMCIA)          | Min.      | Max.       | UNIT      |

| Write Cycle Time                                  | t <sub>AVAV</sub>  | t <sub>eW</sub>          | 200       |            |           |

| Address Setup Time                                | t <sub>AVEL</sub>  | t <sub>su</sub> (A)      | 20        | <b>—</b> . | 1         |

| Write Recovery Time                               | t <sub>ehax</sub>  | t <sub>rec</sub> (CE)    | 30        | -          | 1         |

| Data Setup Time for CE                            | t <sub>DVEH</sub>  | t <sub>su</sub> (D-CEH)  | 60        |            | 1         |

| Data Hold Time                                    | t <sub>EHDX</sub>  | t <sub>h</sub> (D)       | 30        | _          | ] .       |

| Write Recovery Before Read                        | t <sub>EHGL</sub>  |                          | 10        |            | 1         |

| Write Enable Setup time for CE                    | t <sub>wleh</sub>  | t <sub>su</sub> (WE-CEH) | 140       |            | ns        |

| Address Setup for CE                              | t <sub>aveh</sub>  | t <sub>su</sub> (A-CEH)  | 140       |            |           |

| Write Enable Hold Time                            | t <sub>EHWH</sub>  |                          | 0         |            |           |

| Write Pulse Width                                 | t <sub>ELEH</sub>  | t <sub>w</sub> (CE)      | 120       | _          |           |

| Write Pulse Width High                            | t <sub>EHEL</sub>  | tw (CEH)                 | 30        | <u> </u>   |           |

| WE High to RDY/BSY Going Low                      | t <sub>EHRL</sub>  |                          | _         | 150        |           |

| Duration of write operation                       | t <sub>EHQV1</sub> |                          | 4.8       | _          | μs        |

| V <sub>PP</sub> Setup to WE Going High            | t <sub>VPEH</sub>  |                          | 100       |            |           |

| V <sub>PP</sub> Hold from Valid SRD, RDY/BSY High | t <sub>QVVL</sub>  |                          | 0         |            | ns        |

1. Set  $\overline{CE}_1$ ,  $\overline{CE}_2$ ,  $\overline{OE}$  and  $\overline{WE}$  "HIGH", when  $V_{PP}$  changes from  $V_{PPL}$  to  $V_{PPH}$  or vice versa.

#### 11. Erase Operation

#### 11.1 DC Charactristics

$(V_{cc}=4.5\sim5.5V, V_{pp}=11.4\sim12.6V, Ta=0\sim60^{\circ}C)$

$(V_{cc}=4.5\sim5.5V, V_{PP}=11.4\sim12.6V, Ta=0\sim60°C)$

0

|                                                                        |               |                          | (100 7.5     | 3.3 V, V       | pp 11.4 12.0 v, 1a 0 -00 C |                                                      |

|------------------------------------------------------------------------|---------------|--------------------------|--------------|----------------|----------------------------|------------------------------------------------------|

| PARAME                                                                 | TER           | SYMBOL                   | Min.         | Max.           | UNIT                       | CONDITION                                            |

| v v                                                                    | Read          | $V_{PPL}$                | 0            | 1.5            |                            |                                                      |

| V <sub>PP1</sub> , V <sub>PP2</sub><br>Operating Voltage               | Program       | $V_{\tiny 	exttt{PPHE}}$ | 11.4         | 12.6           | v                          |                                                      |

| V V                                                                    | Standby       | I <sub>SB2</sub>         |              | 1.6            |                            | I/O open                                             |

| V <sub>PP1</sub> , V <sub>PP2</sub><br>Operating Current<br>(×16 Mode) | Erase         | $I_{pp}$                 | _            | 20             | mA                         | RMS                                                  |

|                                                                        | Erase Suspend | I <sub>PPS</sub>         |              | 1.6            | 1                          | $\overline{CE_1}$ , $\overline{CE_2} = V_{IH}$ , RMS |

| V <sub>cc</sub> Operating                                              | Standby       | I <sub>SB1</sub>         |              | 2.0            |                            | I/O open                                             |

| Current                                                                | Erase         | I <sub>CCE</sub>         |              | 75             |                            | RMS                                                  |

| (×16 Mode)                                                             | Erase Suspend | I <sub>CCES</sub>        | -0.3         | 22 -           | 1 1                        | $\overline{CE_1}$ , $\overline{CE_2} = V_{IH}$ , RMS |

| Input Voltage                                                          |               | V <sub>IL</sub>          | 3.5          | 1.5            | l <sub>v</sub> l           |                                                      |

|                                                                        |               | V <sub>IH</sub>          | _            | $V_{cc} + 0.3$ | ]                          |                                                      |

| Output Voltage                                                         |               | VoL                      | $V_{cc}-0.5$ | 0.4            | ] [                        | I <sub>oL</sub> =4mA                                 |

| During Verify                                                          |               | V <sub>OH</sub>          |              |                |                            | $I_{OH} = -2mA$                                      |

Note) Power on  $V_{cc}$  before power on  $V_{pp}$ , power off  $V_{cc}$  after power off  $V_{pp}$ . Keep  $V_{pp}$  including its overshoot, below 13V. Card insertion or removal while applying  $V_{pp} = 12V$  may cause a loss of integrity. Do not turn on or turn off during  $\overline{CE} = \text{`LOW''}$ .

If  $V_{IH}$  goes above  $V_{CC}+0.3V$ , normal operation is not assured.

## 11.2 AC Characteristics ( $V_{CC}=4.5\sim5.5V$ , $V_{PP}=11.4\sim12.6V$ , $Ta=0\sim60^{\circ}C$ )

Testing Conditions:

Input Pulse Level : 0.8~3.5V

Input Rise/Fall Time : 10ns

Input/Output Timing Reference Level : 1.5V

4) Output Load : 1TTL+C<sub>L</sub> (100pF) (including scope and jig capacitance)

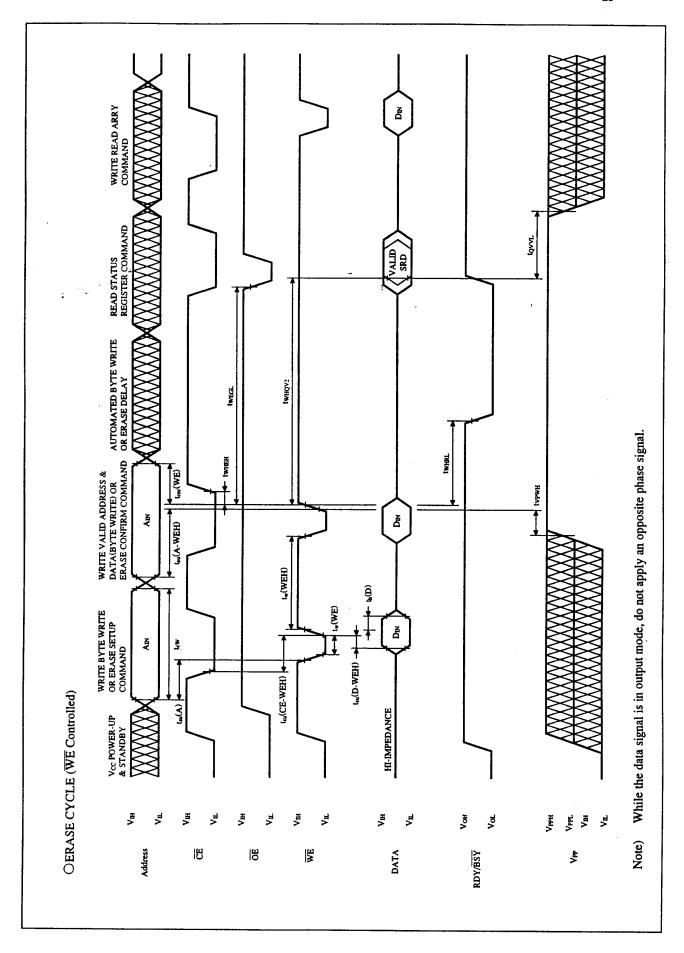

#### 11.2.1 Erase Cycle

V<sub>PP</sub> Hold from Valid SRD, RDY/BSY High

WE Controlled

**PARAMETER** SYMBOL SYMBOL (PCMCIA) Min. Max. UNIT Write Cycle Time 200 t<sub>AVAV</sub>  $t_{cW}$ Address Setup Time t<sub>su</sub> (A) 20  $t_{AVWL}$ Write Recovery Time t<sub>rec</sub> (WE) 30 twhax Data Setup Time for WE t<sub>su</sub> (D-WEH) t<sub>DVWH</sub> 60 Data Hold Time  $t_h(D)$ 30 t<sub>whDX</sub> Write Recovery Before Read 10 twHGL กร Card Enable Setup time for WE t<sub>ru</sub> (CE-WEH) 140 telwh Address Setup for WE t<sub>su</sub> (A-WEH) 140 tAVWH Card Enable Hold Time 15 twhen Write Pulse Width tw (WE) twlwh 120 Write Pulse Width High tw (WEH) 30 t<sub>whwl</sub> WE High to RDY/BSY Going Low twhrl. 150 Duration of Erase twHQV2 operation 0.3 V<sub>PP</sub> Setup to WE Going High 100 tvPWH

tovvl

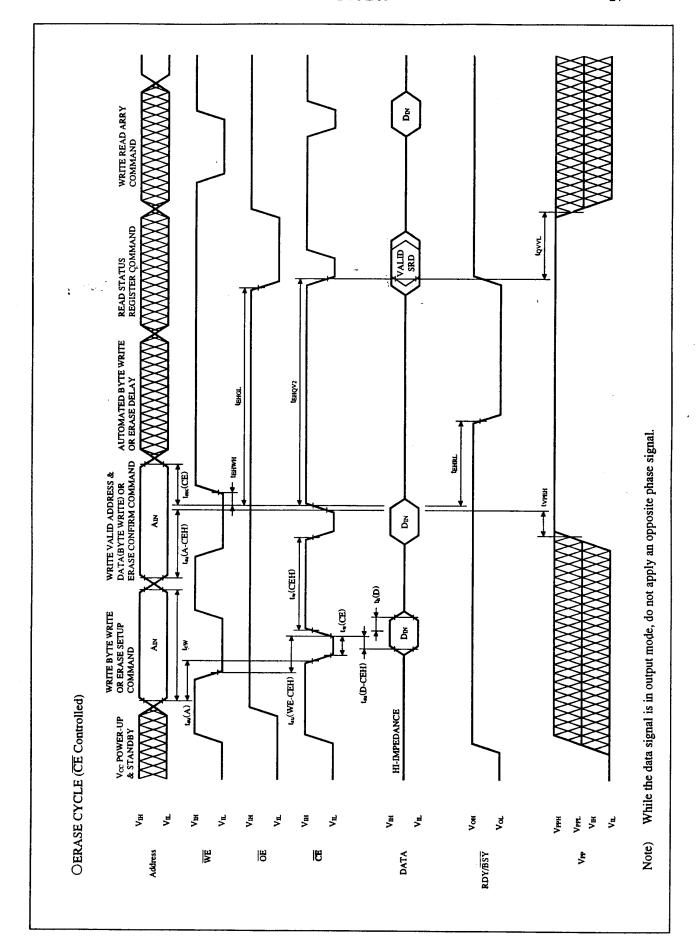

| ᅋ | Con | torol | hai |

|---|-----|-------|-----|

|   |     |       |     |

$(V_{cc}=4.5\sim5.5V, V_{PP}=11.4\sim12.6V, Ta=0\sim60^{\circ}C)$

| PARAMETER                                         | SYMBOL             | SYMBOL (JEIDA)           | T    | Mari |      |

|---------------------------------------------------|--------------------|--------------------------|------|------|------|

|                                                   | STMBOL             | 31 MBOL (JEIDA)          | Min. | Max. | UNIT |

| Write Cycle Time                                  | t <sub>AVAV</sub>  | t <sub>cW</sub>          | 200  |      |      |

| Address Setup Time                                | t <sub>avel</sub>  | t <sub>su</sub> (A)      | 20   | _    |      |

| Write Recovery Time                               | t <sub>EHAX</sub>  | t <sub>rec</sub> (CE)    | 30   | _    |      |

| Data Setup Time for CE                            | t <sub>DVEH</sub>  | t <sub>su</sub> (D-CEH)  | 60   | _    |      |

| Data Hold Time                                    | t <sub>EHDX</sub>  | t <sub>h</sub> (D)       | 30   |      |      |

| Write Recovery Before Read                        | t <sub>EHGL</sub>  |                          | 10   |      |      |

| Write Enable Setup time for CE                    | t <sub>WLEH</sub>  | t <sub>su</sub> (WE-CEH) | 140  | _    | ns   |

| Address Setup for CE                              | t <sub>aveh</sub>  | t <sub>su</sub> (A-CEH)  | 140  |      |      |

| Write Enable Hold Time                            | t <sub>EHWH</sub>  |                          | 0    |      |      |

| Write Pulse Width                                 | t <sub>ELEH</sub>  | t <sub>w</sub> (CE)      | 120  |      |      |

| Write Pulse Width High                            | t <sub>ehel</sub>  | t <sub>w</sub> (CEH)     | 30   |      |      |

| WE High to RDY/BSY Going Low                      | t <sub>EHRL</sub>  |                          |      | 150  |      |

| Duration of Erase operation                       | t <sub>EHQV2</sub> | -                        | 0.3  |      | s    |

| V <sub>PP</sub> Setup to WE Going High            | t <sub>vpeh</sub>  |                          | 100  | _    |      |

| V <sub>PP</sub> Hold from Valid SRD, RDY/BSY High | t <sub>QVVL</sub>  |                          | 0    |      | ns   |

<sup>1.</sup> Set  $\overline{CE}_1$ ,  $\overline{CE}_2$ ,  $\overline{OE}$  and  $\overline{WE}$  "HIGH", when  $V_{PP}$  changes from  $V_{PPL}$  to  $V_{PPH}$  or vice versa.

#### 12. Block Erase and Data Write Characteristics

| $(V_{CC}=4.5\sim5.5V_{c}$ | $V_{PP}=11.4\sim12.6$ | 6V, Ta=0~60°C)        |

|---------------------------|-----------------------|-----------------------|

| , ,,                      | · FF ·                | ··, · · · · · · · · · |

| PARAMETER                | Min. | Тур. | Max. | UNIT |

|--------------------------|------|------|------|------|

| Block Pair<br>Erase Time | _    | 1.0  | 10   |      |

| Block Pair               |      |      |      | s    |

| Write Time               |      | 0.4  | 2.1  |      |

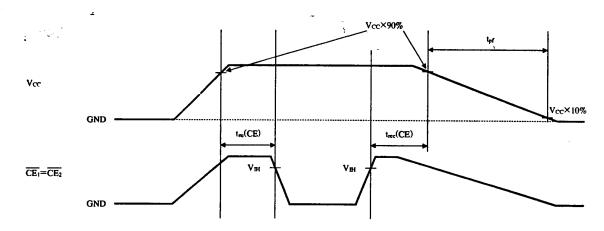

## 13. Voltage Timing (Ta=25℃)

3.5V < VIH < Vcc+0.3

| PARAMETER                    | SYMBOL                | Min. | Max. | UNIT |

|------------------------------|-----------------------|------|------|------|

| CE Setup Time                | t <sub>su</sub> (CE)  | 4.0  | -    | ms   |

| CE Recovery Time             | t <sub>ree</sub> (CE) | 1.0  | _    | μs   |

| V <sub>CC</sub> Falling Time | tpf                   | 3.0  | 300  | ms   |

Note) 1. When  $V_{CC}$  (4.5~5.5V) is applied to the memory card and you are inserting or removing the card,  $\overline{CE}_1$ ,  $\overline{CE}_2$  should both be high-impedance. At such a time, other signal line should also be hi-impedance. After inserting the memory card, do not access it during the  $\overline{CE}$  setup time (minimum of 4ms).

(During this time, neither  $\overline{CE_1}$  nor  $\overline{CE_2}$ = "LOW".)

2. When V<sub>CC</sub> is turn on, if the condition (for example, V<sub>CC</sub> rising time. etc) is not sufficient to as specified, it is possible that device's Status Register is not cleared or device not becomes to Read Array Mode. To prevent these, it is recommended that using software command, reset the Status Register or set the device to Read Array Mode.

ex.

Reset the Status Register 50H (5050H)

Set to Read Array Mode FFH (FFFFH)

#### 14. Attribute Memory

The attribute memory holds the attribute information of the card such as the type of card, bit configuration, speed and so on.

#### **EEPROM Model**

Card has 2k bytes of EEPROM attribute memory. To read the attribute memory, set REG = "LOW" and perform a read with the same access timming as common memory read.

For this operation, access time is 300ns maximum. To allow 2k bytes of attribute memory, even addresses from 0 to 4096 are reserved. Since only the even-numbered bytes are used, reading odd-numbered bytes will result in invalid data.

Note) We have another type of attribute memory as follows,

No EEPROM Model. (Model no ID240E02:5 bytes device informations in even address 0 to 8, read only in card's control circuit, with the same access timming as common memory read.)

#### 14.1 Attribute Memory Read/Write Function Chart

| $\overline{CE_i}$ | CE <sub>2</sub> | A <sub>0</sub> | WE | ŌĒ | REG | MODE                         | D <sub>0</sub> ~D <sub>7</sub> | D <sub>8</sub> ~D <sub>15</sub> | STAATUS     |

|-------------------|-----------------|----------------|----|----|-----|------------------------------|--------------------------------|---------------------------------|-------------|

| Н                 | Н               | X              | X  | X  | X   |                              | High-Z                         | High-Z                          | Standby     |

| L                 | . H             | L              | Н  | L  | L   | Read (×8)                    | D <sub>0</sub> (even byte)     | High-Z                          | Byte Access |

| L                 | Н               | Н              | H  | L  | L   |                              | High-Z                         | High-Z                          | Standby     |

| L                 | L               | X              | Н  | L  | L   | Read (×8)                    | D <sub>0</sub> (even byte)     | High-Z                          | Byte Access |

| Н                 | L               | X              | Н  | L  | L   |                              | High-Z                         | High-Z                          | Standby     |

| L                 | Н               | L              | L  | Н  | L   | Write (×8)                   | D <sub>1</sub> (even byte)     | ×××                             | Byte Access |

| L                 | Н               | Н              | L  | Н  | L   |                              | ×××                            | ×××                             | Standby     |

| L                 | L               | X              | L  | Н  | L   | Write (×8)                   | D <sub>1</sub> (even byte)     | ×××                             | Byte Access |

| H                 | L               | X              | L  | Н  | L   |                              | ×××                            | ×××                             | Standby     |

| L                 | х               | X              | Н  | L  | L   | Attribute Memory Address 0~8 | D <sub>0</sub>                 | High-Z                          | Byte Access |

H: High

L : Low

X: High/Low not applicable

Di: Input Data

Do: Output Data

Hi-Z: High Impedance

×××: Don't Care

Notes: 1) When the write protect switch is in protect-mode, the WP output signal is "HIGH" and write operations (including attribute memory) are not allowed.

2) A<sub>0</sub>-A<sub>11</sub> are attribute memory address. Addresses after A<sub>12</sub> are not decoded, so care should be taken.

#### 14.2 AC Characteristics ( $V_{CC}=4.5V\sim5.5V$ , $Ta=0\sim60^{\circ}C$ )

**Testing Conditions**

1) Input Pulse Level

: 0.8~3.5V

2) Input Rise/Fall Time

: 10ns

3) Input/Output Timing Reference Level

: 1.5V

4) Output Load Capacitance

$: 1TTL + C_{L} (100pF)$

(including scope and jig capacitance)

#### 14.3 Attribute Memory Read Cycle

| $(V_{cc}=4.5\sim5.5V,$       | To-On-KORC)  |

|------------------------------|--------------|

| $(v_{CC} + J_{CC} + J_{CC})$ | , 1a-0 ~00C) |

| PARAMETER                   | SYMBOL           | SYMBOL (PCMCIA)       | Min. | Max. | UNIT |

|-----------------------------|------------------|-----------------------|------|------|------|

| Read Cycle Time             | t <sub>CR</sub>  | t <sub>cR</sub>       | 300  |      |      |

| Address Access Time         | t <sub>ACC</sub> | t <sub>a</sub> (A)    | -    | 300  | 1    |

| Card Enable Access Time     | t <sub>CE</sub>  | t <sub>a</sub> (CE)   |      | 300  | 1    |

| Output Enable Access Time   | t <sub>OE</sub>  | t <sub>a</sub> (OE)   |      | 150  | 1    |

| Output Disable Time from CE |                  | t <sub>dis</sub> (CE) |      | 100  | ns   |

| Output Disable Time from OE | t <sub>DF</sub>  | t <sub>dis</sub> (OE) | _    | 100  | 1    |

| Output Enable Time from CE  |                  | t <sub>en</sub> (CE)  | 5    | _    | Ì    |

| Output Enable Time from OE  |                  | t <sub>en</sub> (OE)  | 5    | _    | 1    |

| Data Valid from Add Change  | t <sub>oh</sub>  | t <sub>v</sub> (A)    | 0    |      |      |

#### OAttribute Memory Read Cycle

- Note: 1. To read attribute memory,  $\overline{REG}$ ="LOW",  $\overline{WE}$ ="HIGH" and either  $\overline{CE}_2$ ="LOW" or else  $\overline{CE}_2$ ="HIGH" and  $A_0$ ="LOW".

- 2. The output data becomes valid when last interval,  $t_a$  (A),  $t_a$  (CE)or  $t_a$  (OE)have concluded.

# 14.4 Attribute Memory Write Cycle

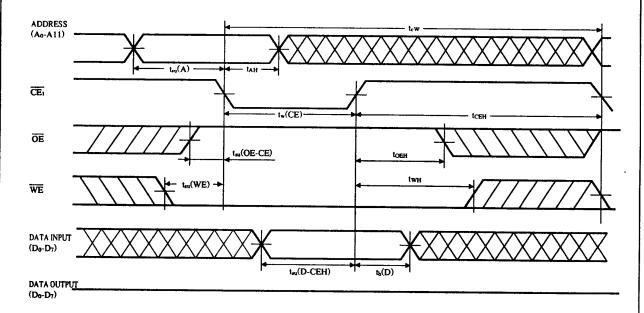

WE Controlled

$(V_{cc}=4.5V\sim5.5V, Ta=0\sim60^{\circ}C)$

| PARAMETER                | SYMBOL           | SYMBOL (PCMCIA)         | Min. | Max. | UNIT |

|--------------------------|------------------|-------------------------|------|------|------|

| Write Cycle Time         | t <sub>wc</sub>  | t <sub>cW</sub>         | 10   |      | ms   |

| Write Pulse Width        | t <sub>wp</sub>  | t <sub>w</sub> (WE)     | 180  |      |      |

| Address Setup Time       | t <sub>AS</sub>  | t <sub>su</sub> (A)     | 10   |      | 1    |

| Data Setup Time for WE   | t <sub>DS</sub>  | t <sub>su</sub> (D-WEH) | 100  |      | 1    |

| Card Enable Setup Time   | t <sub>CES</sub> | t <sub>su</sub> (CE)    | 0    |      | 1    |

| Output Enable Setup Time | t <sub>OES</sub> | t <sub>su</sub> (OE-WE) | 45   |      | ns   |

| Address Hold Time        | t <sub>AH</sub>  |                         | 260  |      | 1    |

| Write Hold Time          | t <sub>CH</sub>  |                         | 0    |      |      |

| Output Enable Hold Time  | t <sub>OEH</sub> |                         | 70   |      |      |

| WE HIGH Hold Time        | t <sub>weh</sub> | 3                       | 9.9  |      | ms   |

| Data Hold Time           | t <sub>DH</sub>  | t <sub>h</sub> (D)      | 80 . |      | ns   |

CE Controlled

$(V_{CC}=4.5V\sim5.5V, Ta=0\sim60^{\circ}C)$

| PARAMETER                | SYMBOL           | SYMBOL (PCMCIA)         | Min. | Max. | UNIT |

|--------------------------|------------------|-------------------------|------|------|------|

| Write Cycle Time         | t <sub>wc</sub>  | t <sub>cw</sub>         | 10   |      | ms   |

| Write Pulse Width        | t <sub>wp</sub>  | t <sub>w</sub> (CE)     | 210  |      |      |

| Address Setup Time       | t <sub>AS</sub>  | t <sub>su</sub> (A)     | 10   |      | 1    |

| Data Setup Time for CE   | t <sub>DS</sub>  | t <sub>su</sub> (D-CEH) | 100  |      | 1    |

| Write Enable Setup Time  | t <sub>wes</sub> | t <sub>su</sub> (WE)    | 0    |      | 1    |

| Output Enable Setup Time | t <sub>OES</sub> | t <sub>su</sub> (OE-CE) | 45   |      | ns   |

| Address Hold Time        | t <sub>AH</sub>  |                         | 260  |      | Ì    |

| Write Hold Time          | t <sub>wH</sub>  |                         | 0    | T —  | İ    |

| Output Enable Hold Time  | t <sub>OEH</sub> |                         | 70   |      |      |

| CE HIGH Hold Time        | t <sub>CEH</sub> |                         | 9.9  |      | ms   |

| Data Hold Time           | t <sub>DH</sub>  | t <sub>h</sub> (D)      | 80   | _    | ns   |

#### OAttribute Memory Write Cycle (WE Controlled)

#### OAttribute Memory Write Cycle (CE Controlled)

Note: 1. To write attribute memory,  $\overline{REG}$ ="LOW" and either  $\overline{CE}_2$ ="LOW" or else  $\overline{CE}_2$ ="HIGH" and  $A_0$ = "LOW"

## 15. Specification Changes

Specifications may be changed upon discussion and agreement between both parties.

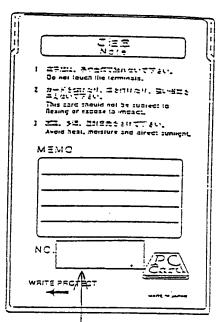

#### 16. Othes Precautions

| 0 | Permanent damage occures if the memory card is stressed beyond Absolute Maximum Ratings. Operation beyond |

|---|-----------------------------------------------------------------------------------------------------------|

|   | the Recommended Operating Conditions is not recommended and extended exposure beyond the Recommended      |

|   | Operating Conditions may affect device reliability.                                                       |

- O Writing to the memory card can be prevented by switching on the write protect switch on the end of the memory card.

- O Avoid allowing the memory card connectors to come in contact with metals and avoid touching the connectors, as the internal circuits can be damaged by static electricity.

- O Avoid storing in direct sunlight, high temperatures (do not place near heaters or radiators), high humidity and dusty areas.

- O Avoid subjecting the memory card to strong physical abuse. Dropping, bending, smashing or throwing the card can result in loss of function.

- O When the memory card is not being used, return it to its protective case.

- O Do not allow the memory card to come in contact with fire.

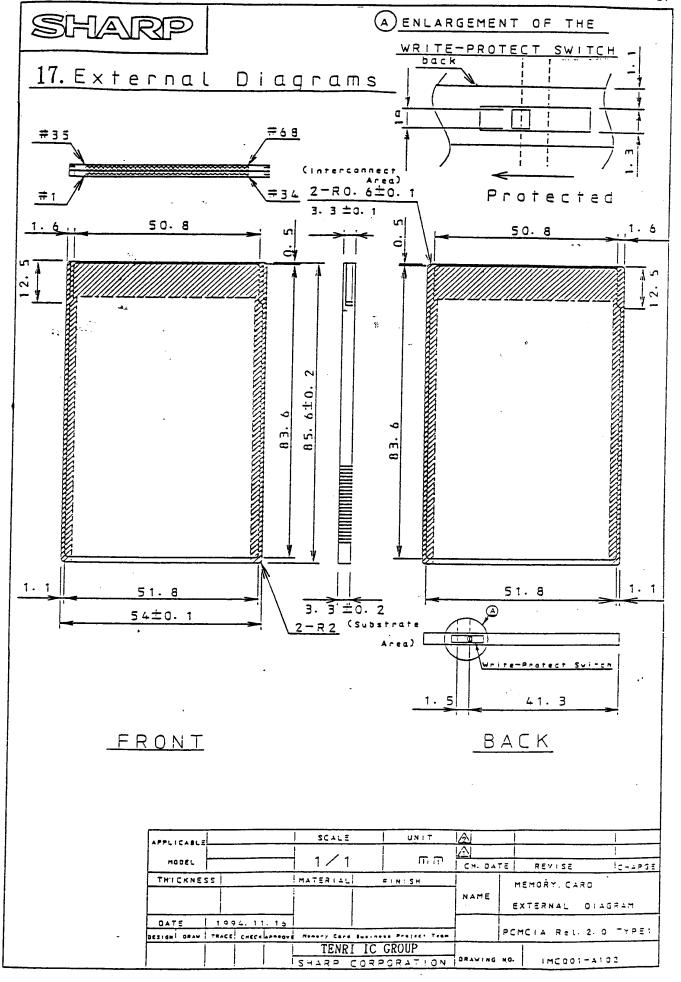

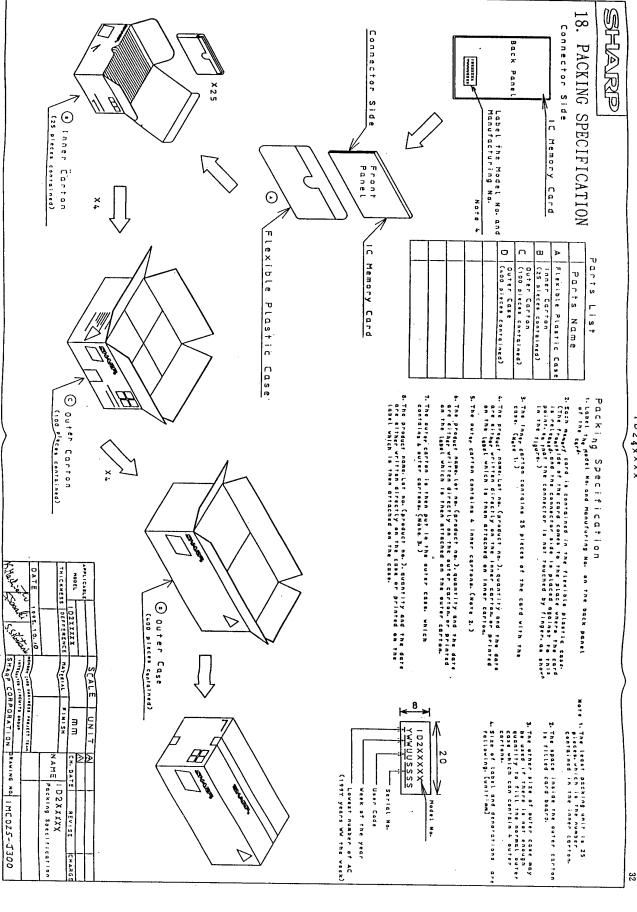

# 19. EXTERNAL APPEARANCES

CONNECTOR SIDE

FRONT PANEL

LABELING POSITION BACK PANEL

LABEL SIZE AND DENOTATIONS

| APPLICABLE | ID244E01                                 | SCALE            | UNIT              | 12          |        |             |

|------------|------------------------------------------|------------------|-------------------|-------------|--------|-------------|

| HODEL      |                                          |                  | mm                | CH. DATE    | REVISE | <br> CHARGE |

| THICKNESS  | DEFFERENCE                               | MATERIAL         | FINISH            | NAME        |        |             |

| DATE       | 1995. 10. 10                             |                  |                   |             |        |             |

|            | asabi S.Shritariu                        | HEMORY CARD BUSI | HESS PROJECT TEAM |             |        |             |

| Phone K    | S. S | SHARP COR        | PORATION          | PRAWING NOT |        |             |

4 MB, PCMCIA, Flash Card, ID240E01

#### SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE.

Suggested applications (if any) are for standard use; See Important Restrictions for limitations on special applications. See Limited Warranty for SHARP's product warranty. The Limited Warranty is in lieu, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY EXCLUDED. In no event will SHARP be liable, or in any way responsible, for any incidental or consequential economic or property damage.

#### NORTH AMERICA

SHARP Microelectronics of the Americas 5700 NW Pacific Rim Blvd. Camas, WA 98607, U.S.A. Phone: (360) 834-2500 Fax: (360) 834-8903 http://www.sharpsma.com

#### EUROPE

SHARP Microelectronics Europe Sonninstraße 3 20097 Hamburg, Germany Phone: (49) 40 2376-2286 Fax: (49) 40 2376-2232 http://www.sharpsme.com

#### ASIA

SHARP Corporation Integrated Circuits Group 2613-1 Ichinomoto-Cho Tenri-City, Nara, 632, Japan Phone: +81-743-65-1321 Fax: +81-743-65-1532 http://www.sharp.co.jp