## HUGHES

SOLID STATE PRODUCTS

# C MOS Decade Counter/ Latch/Decoder/Driver

HCTR 0200D/ HCTR 0200P

#### **DESCRIPTION**

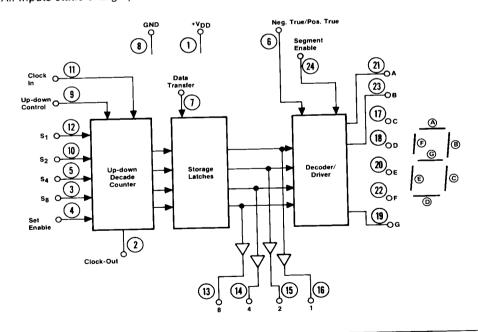

The Hughes HCTR 0200 Decade Counter/Latch/Decoder/Driver is a TTL compatible, Positive True Logic circuit for driving 7 segment light emitting diode displays, liquid crystal displays, incandescent displays and bipolar transistor base currents. A modified version for driving electroluminescent tubes is also available by special order.

The HCTR 0200 is an up-down, presettable, decade counter with storage latches which hold the BCD state of the counter on command. The stored information appears in numeric form at the seven segment driver outputs.

#### **FEATURES**

- 7 Segment outputs drive LED's directly without Bipolar interface

- Up-down presettable BCD Counter

- Count Independent Storage Latches

- All inputs TTL compatible

- Low Power Dissipation

- Units may be cascaded

- BCD and Clock Outputs will drive one worst case TTL load

- All inputs static charge protected.

## TERMINAL CONNECTIONS

159

# ELECTRICAL CHARACTERISTICS OVER FULL TEMPERATURE VARIATIONS

| CHARACTERISTICS                                                                                                                                | CONDITIONS                                                                                          | TYPICAL VALUES           |                              |          |                 |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------|------------------------------|----------|-----------------|

|                                                                                                                                                |                                                                                                     | MIN                      | ТҮР                          | MAX      | UNITS           |

| Operating Voltage, V <sub>DD</sub>                                                                                                             |                                                                                                     | 2                        | 5                            | 10       | v               |

| All Inputs<br>Logic "High", V <sub>INH</sub><br>Logic "Low", V <sub>INL</sub>                                                                  | (All following at<br>+V <sub>DD</sub> = 5V unless<br>otherwise stated)                              | 2.4<br>GND               |                              | 5<br>1.0 | v<br>v          |

| Capacitance<br>Input Leakage, I <sub>I</sub><br>Set Enable Pulse, T <sub>SEH</sub>                                                             | v <sub>in</sub> = 0, F <sub>in</sub> = MHz                                                          | 200                      | 3                            | 1.0      | PF<br>A<br>nS   |

| Width Data Transfer Pulse, T <sub>DXH</sub> Width                                                                                              |                                                                                                     | 250                      |                              |          | nS              |

| Set Input Valid Time, TSIH Necessary Delay from Count Control change to Positive Clock                                                         |                                                                                                     | 200                      |                              | nS       | nS              |

| Transition  Clock Input Clock Frequency, FMAX Rise, Fall Times, T <sub>r,f</sub> Pulse Width in "High", T <sub>CLPW</sub> State or "Low" State |                                                                                                     | 2<br>250                 |                              | 200      | MHz<br>nS<br>nS |

| Clock Output<br>Logic "High", VOCH<br>Logic "Low", VOCL                                                                                        | I <sub>L</sub> = 200 μA<br>I <sub>L</sub> = 1.6 mA                                                  | 4<br>GND                 |                              | 5<br>0.4 | v<br>v          |

| BCD Outputs<br>Logic "High", VOH<br>Logic "Low", VOL                                                                                           | L = -200 μA<br>  L = 1.6 mA                                                                         | 4<br>GND                 |                              | 5<br>0.4 | v<br>v          |

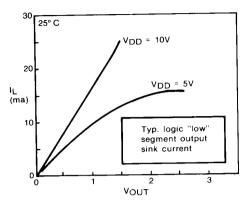

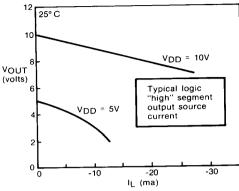

| Display Outputs Logic "High" (Source), VODH Logic "Low" (Sink), VODL Logic "High" (Source), VODH Logic "Low" (Sink), VODL                      | I <sub>L</sub> = -1 mA<br>I <sub>L</sub> = 2 mA<br>I <sub>L</sub> = -1.5 mA<br>I <sub>L</sub> = 3mA | 4.5<br>0.5<br>9.5<br>0.5 | 4.8*<br>0.2*<br>9.8*<br>0.2* |          | V<br>V<br>V     |

\*At 25° C

For driving electroluminescent displays a special mask option is available which will modify the circuit to provide single ended segment output drivers for interfacing with high-voltage electroluminescent tubes.

An option for a 16 Pin package is available. The 16 Pin version is similar to the 24 Pin version except that the BCD OUTPUTS and SET INPUTS are not bonded out. In this version, the SET ENABLE input becomes a RESET input. Other bonding options, with even fewer pins are feasible.

The chip contains an additional power input pad which is not bonded out in the Standard 24 Pin version. The additional power input permits TTL compatible BCD OUTPUTS while operating the segment outputs at voltages higher than the standard TTL 5V supply voltage. Bonding out the additional power input pads can be done by eliminating (i.e. not bonding out) one of the standard pin functions and bonding out the additional power input instead. (Note: This may require a different pin — out for the other pins.)

#### MAXIMUM RATINGS

+5.3 to -10.0V Voltage, any pin (+VDD = 5V)

350 mw Power Dissipation

0°C to +70°C Operating Temperature -65° C to +125° C

Storage Temperature

NOTE: These ratings are limiting values above which the serviceability of the device may be impaired.

#### **PACKAGES**

24 Pin Ceramic DIP (HCTR 0200D) 24 Pin Plastic DIP (HCTR 0200P)

#### **OPERATING NOTES**

#### PRESETTING

When the Set Enable is a "high" the clock input is disabled and the flip-flops in the counter are set by the Set Inputs (S1, S2, S4, S8). When the Set Input is "low", the Set Inputs are disabled and the counter is enabled to respond to pulses on the Clock In input.

#### DATA TRANSFER:

When the Data Transfer is a "high", the storage flip-flops and all outputs follow the count. When a "low" input is applied, the storage flip-flops lock up at the last count without interrupting the counter. The outputs will not change until this goes in a "high".

#### CLOCK IN:

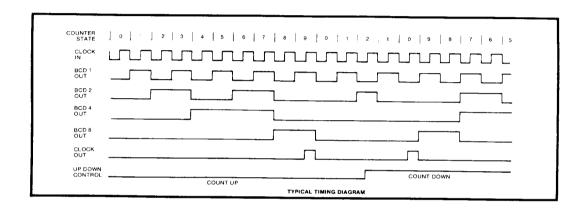

The flip-flops toggle on the falling (High to Low) edge of CLOCK IN.

#### **CLOCK OUT:**

When counting up and the count of "9" is reached, the next clock pulse in generates a CLOCK OUT pulse having the same width as the input pulse. When counting down, and the count of "0" is reached, the next clock pulse in generates a CLOCK OUT pulse. When cascading counters, connect the CLOCK OUT terminal to the CLOCK IN terminal of the following counter.

#### SET INPUTS:

The Set Inputs are positive true logic. Refer to presetting note.

#### UP-DOWN CONTROL:

The Up-Down Count Control determines the operating mode.

= Logic "low" = Logic "high" DOWN

For cascaded counters, the Up-Down Count Control should not be changed when the CLOCK-NOTE: IN is "high".

162

#### **BCD OUTPUTS:**

The BCD outputs are positive true logic. Each BCD output can drive one standard power TTL load.

#### 7-SEGMENT OUTPUTS:

The 7-Segment Outputs form numbers by connecting the outputs to the appropriate decoder driver outputs. The "true" state of the segment outputs is controlled by the NEGATIVE TRUE/POSITIVE TRUE input as follows:

| NEGATIVE TRUE/<br>POSITIVE TRUE Input | 7-Segment<br>Output "True" State            |  |  |

|---------------------------------------|---------------------------------------------|--|--|

| "low"                                 | "high" (Low impedance to +V <sub>DD</sub> ) |  |  |

| "high"                                | "low" (Low impedance to GROUND)             |  |  |

A logic "low" on the SEGMENT ENABLE input will cause the SEGMENT OUTPUTS to "float" i.e. all segment outputs will have a high impedance to VDD and to GROUND. The high impedance "float" state is independent of the NEGATIVE TRUE/POSITIVE TRUE input. A logic "high" on the SEGMENT ENABLE will allow the decoder segment driver outputs to operate in the low impedance driver mode.

For Liquid Crystal Displays, requiring AC drive signals, the NEGATIVE TRUE/POSITIVE TRUE input can be driven with the back plane signal.

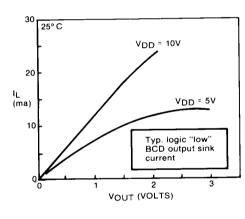

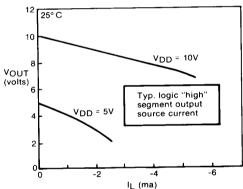

## HCTR 0200 TYPICAL BCD OUTPUT CHARACTERISTICS

Information furnished by Hughes is believed to be accurate and reliable. However, no responsibility is assumed by Hughes for its use; nor for any infringements or patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Hughes.

## **HUGHES**

Represented By

#### Solid State Products

esa Superior Avenue, Newport Beach, CA 92663 Timetra nei: 8001 854 -3515 br (714 - 759-2942 - TWX, 910-596-1374

## Europe Hughes Microelectronics Ltd.

performer 12 18 Oberns Road Weybridge Surrey KT 139XD England opning 932 47262 Telex 929727