|                                                                                                |    |                                   |     |                 |                  |                                                  |        |         | REVIS    | SIONS     |                      |        |                                        |                 |              |                |               |       |                                                  |        |

|------------------------------------------------------------------------------------------------|----|-----------------------------------|-----|-----------------|------------------|--------------------------------------------------|--------|---------|----------|-----------|----------------------|--------|----------------------------------------|-----------------|--------------|----------------|---------------|-------|--------------------------------------------------|--------|

| LTR                                                                                            |    |                                   |     |                 |                  | DESC                                             | RIPTIC | ON      |          |           |                      |        | D                                      | ATE (           | YR-MO        | -DA)           |               | APP   | ROVE                                             | D      |

|                                                                                                |    |                                   |     |                 |                  |                                                  |        |         |          |           |                      |        |                                        |                 |              |                |               |       |                                                  |        |

| REV<br>SHEET<br>REV                                                                            |    |                                   |     |                 |                  |                                                  |        |         |          |           |                      |        | ************************************** |                 |              |                |               |       |                                                  |        |

| SHEET                                                                                          | 15 | 16                                | 17  | 18              | 19               | <del>                                     </del> | -      |         |          |           |                      |        |                                        |                 |              |                |               |       |                                                  |        |

| REV STATUS                                                                                     |    |                                   | L   | RE              | <u> </u>         | <u> </u>                                         |        |         |          |           |                      |        |                                        |                 | <del> </del> |                |               |       | <del>                                     </del> |        |

| OF SHEETS                                                                                      |    |                                   |     | SHI             | EET              |                                                  | 1      | 2       | 3        | 4         | 5                    | 6      | 7                                      | 8               | 9            | 10             | 11            | 12    | 13                                               | 14     |

| PMIC N/A                                                                                       |    |                                   |     |                 | PAREI<br>arry T. | D BY<br>Gaude                                    | er     |         | <u> </u> |           | DI                   | EFENS  |                                        |                 |              | S SUP<br>O 454 |               | CENTE | R                                                |        |

| STANDARD<br>MICROCIRCUIT<br>DRAWING                                                            |    |                                   | Т   |                 | CKED<br>omas N   | BY<br>1. Hess                                    | S      |         |          | <b>-</b>  |                      | ID 6:: |                                        |                 |              |                |               |       |                                                  |        |

| THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE |    | BLE                               |     | ROVE<br>nica L. | D BY<br>Poelki   | ing                                              |        |         | MU       | LTIC      | IRCU<br>HANN<br>THIC | EL R   | ECEI                                   | L, CIV<br>VER/I | IOS, A       | ARIN(<br>SMIT  | C 429<br>TER, | ,     |                                                  |        |

|                                                                                                |    | DRAWING APPROVAL DATE<br>95-10-04 |     |                 |                  | <del>-</del>                                     |        | GE CODE |          | 5962-9551 |                      | 518    | -                                      |                 |              |                |               |       |                                                  |        |

| AMSC N/A                                                                                       |    |                                   | REV | ISION           | LEVE             | L                                                |        |         |          | 4         | 6                    | 726    | 8                                      | 1               |              |                |               |       |                                                  |        |

|                                                                                                |    |                                   |     |                 |                  |                                                  |        |         |          | SHE       | ET                   | 1      |                                        | OF              | 1            | 9              |               |       |                                                  |        |

| DESC FORM 19:<br>JUL 94                                                                        | 3  |                                   |     | -               |                  | -                                                |        |         |          | 1         |                      |        |                                        |                 |              |                |               |       | 5063                                             | E020 0 |

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

■ 9004708 0014143 345 ■

# 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). Two product assurance classes consisting of military high reliability (device classes Q and M) and space application (device class V), and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). Device class M microcircuits represent non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

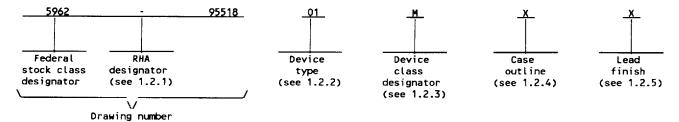

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>RHA designator</u>. Device class M RHA marked devices shall meet the MIL-I-38535 appendix A specified RHA levels and shall be marked with the appropriate RHA designator. Device classes Q and V RHA marked devices shall meet the MIL-I-38535 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

Device type Generic number Circuit function

01 68C429A CMOS Arinc 429 multichannel receiver/transmitter

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

Device class

# Device requirements documentation

M

Vendor self-certification to the requirements for non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883

0 or V

Certification and qualification to MIL-I-38535

1.2.4 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u> Terminals</u> | Package style              |

|----------------|------------------------|-------------------|----------------------------|

| X              | CMGA15-P84             | 84                | pin grid array             |

| Y              | CQCC1-G132             | 132               | gullwing lead chip carrier |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-STD-883 (see 3.1 herein) for class M or MIL-I-38535 for classes Q and V. Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

| SIZE<br><b>A</b> |                | 5962-95518 |

|------------------|----------------|------------|

|                  | REVISION LEVEL | SHEET 2    |

DESC FORM 193A JUL 94

■ 9004708 0014144 281 **■**

1.3 Absolute maximum ratings. 1/ Maximum power dissipation (PD) - - - - - - - - - - 400 mW Lead temperature (soldering, 10 seconds) - - - - - -Maximum operating junction temperature (T<sub>J</sub>) - -Thermal resistance, junction-to-case  $(\theta_{JC})$ : 2°C/W 3°C/W Thermal resistance, junction-to-ambient ( $\Theta_{JA}$ ): Case X - - - - - -`----- 28°C/W 1.4 <u>Recommended operating conditions</u>. Supply voltage range ( $V_{CC}$ ) - - - -4.5 V dc minimum to 5.5 V dc maximum High level input voltage range (V  $_{1\,\rm H}$ ) - - - - - - - - - - Low level input voltage range (V  $_{1\,\rm L}$ ) 2.25 V to 5.8 V -0.3 V dc to 0.8 V dc Case operating temperature range  $(I_C)$  - - --55°C to +125°C 1.5 <u>Digital logic testing for device classes Q and V</u>. Fault coverage measurement of manufacturing logic tests (MIL-STD-883, test method 5012) . . . . . XX percent 2/ 2. APPLICABLE DOCUMENTS 2.1 Government specification, standards, bulletin, and handbook. Unless otherwise specified, the following specification, standards, bulletin, and handbook of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein. SPECIFICATION MILITARY MIL-1-38535 - Integrated Circuits, Manufacturing, General Specification for. STANDARDS MILITARY - Test Methods and Procedures for Microelectronics. MIL-STD-883 MIL-STD-973 - Configuration Management. MIL-STD-1835 - Microcircuit Case Outlines. BULLETIN MILITARY MIL-BUL-103 - List of Standardized Military Drawings (SMD's). HANDROOK **MILITARY** MIL-HDBK-780 - Standardized Military Drawings. (Copies of the specification, standards, bulletin, and handbook required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.) Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability. Values will be added when they become available. SIZE **STANDARD** 5962-95518 Α MICROCIRCUIT DRAWING **DEFENSE ELECTRONICS SUPPLY CENTER** REVISION LEVEL SHEET DAYTON, OHIO 45444 3 DESC FORM 193A **JUL 94** 9004708 0014145 118 🖿

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device class M shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. The individual item requirements for device classes Q and V shall be in accordance with MIL-I-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not effect the form, fit, or function as described herein.

- 3.2 <u>Design. construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-STD-883 (see 3.1 herein) for device class M and MIL-I-38535 for device classes Q and V and herein.

- 3.2.1 <u>Case outline(s)</u>. The case outline(s) shall be in accordance with 1.2.4 herein.

- 3.2.2 <u>Ierminal connections</u>. The terminal connections shall be as specified on figure 1.

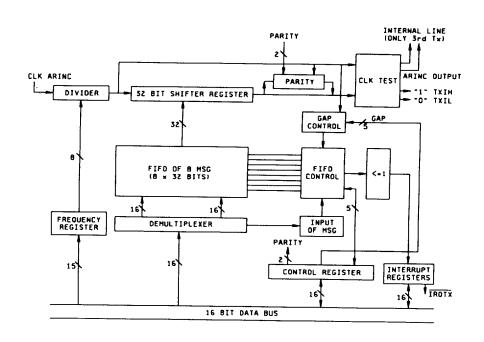

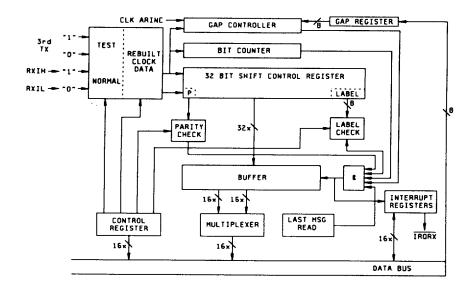

- 3.2.3 Block diagram(s). The block diagram(s) shall be as specified on figure 2.

- 3.2.4 Radiation exposure circuit. The radiation exposure circuit shall be as specified when available.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes Q and V shall be in accordance with MIL-I-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-I-38535.

- 3.6 <u>Certificate of compliance</u>. For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7.2 herein). For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.7.1 herein). The certificate of compliance submitted to DESC-EC prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device class M, the requirements of MIL-STD-883 (see 3.1 herein), or for device classes Q and V, the requirements of MIL-I-38535 and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device class M in MIL-STD-883 (see 3.1 herein) or for device classes Q and V in MIL-I-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change for device class M. For device class M, notification to DESC-EC of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-973.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 100 (see MIL-I-38535, appendix A).

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. For device class M, sampling and inspection procedures shall be in accordance with MIL-STD-883 (see 3.1 herein). For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-I-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not effect the form, fit, or function as described herein.

STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 SIZE 5962-95518

REVISION LEVEL SHEET 4

DESC FORM 193A

JUL 94

9004708 0014146 054 🗪

| Test                                                                            | Symbol               | Conditions <u>1</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C   | +125°C subgroups |          | lı   | Limits                  | Unit       |

|---------------------------------------------------------------------------------|----------------------|------------------------------------------------------------|------------------|----------|------|-------------------------|------------|

|                                                                                 |                      | V <sub>CC</sub> = 5.0 V ±10%<br>unless otherwise specified | 1                | type     | Min  | Max                     | _          |

| Input high voltage                                                              | VIH                  |                                                            | 1, 2, 3          | ALL      | 2.25 | V <sub>CC</sub><br>+0.3 | ٧          |

| Input low voltage                                                               | VIL                  |                                                            | 1, 2, 3          | ALL      | -0.5 | 0.8                     | v          |

| Output high voltage                                                             | v <sub>OH</sub>      | (except IRQRX, IRQTX: open drain outputs)                  | 1, 2, 3          | ALL      | 2.7  |                         | v          |

| Output low voltage                                                              | v <sub>OL</sub>      |                                                            | 1, 2, 3          | All      |      | 0.5                     | V          |

| Output sou <u>rce current</u><br>(except IRQRX, IRQTX:<br>open drain outputs)   | ТОН                  | V <sub>OUT</sub> = 2.7 V                                   | 1, 2, 3          | All      |      | -8                      | mA         |

| Output sink current                                                             | IOL                  | V <sub>OUT</sub> = 0.5 V                                   | 1, 2, 3          | All      |      | 8                       | mA         |

| Input leakage current                                                           | ILI                  | V <sub>IN</sub> = 0 to V <sub>CC</sub>                     | 1, 2, 3          | All      |      | ±20                     | μΑ         |

| Dynamic current                                                                 | I <sub>DD</sub>      | TCASE = Tmin, 2/<br>VDD = Vmax                             | 1, 2, 3          | All      |      | 65                      | m <b>A</b> |

| Input capacitance                                                               | CIN                  | See 4.4.1c                                                 | 4                | All      |      | 10                      | pF         |

| fi-Z output capacitance                                                         | C <sub>OUT</sub>     | See 4.4.1c                                                 | 4                | All      |      | 20                      | pF         |

| functional test                                                                 |                      | See 4.4.1b<br>V <sub>CC</sub> = 4.5 V, 5.5 V               | 7, 8             |          |      |                         |            |

| lock period                                                                     | tcYCS                | V <sub>CC</sub> = 4.5 V and 5.5 V                          | 9, 10, 11        | All      | 50   | 2000                    | ns         |

| lock pulse width                                                                | t <sub>CLS</sub>     | V <sub>CC</sub> = 4.5 V and 5.5 V                          | 9, 10, 11        | ALL      | 20   |                         | ns         |

| ise and fall times                                                              | t <sub>CFS</sub>     | V <sub>CC</sub> = 4.5 V and 5.5 V                          | 9, 10, 11        | All      |      | 5                       | ns .       |

| See footnotes at end of ta                                                      | ble.                 |                                                            |                  |          |      | 1                       | 1          |

|                                                                                 | NDARD<br>CUIT DRAWIN |                                                            | ZE A             |          |      | 59                      | 62-95518   |

| MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |                      |                                                            | REV              | ISION LE | VEI  | SHE                     | <br>FT     |

■ 9004708 0014147 T90 **■**

| Test                                                                      | Symbol Condition |                                                     |                  | Group A<br>subgroups | Device<br>type | L   | imits | Unit               |

|---------------------------------------------------------------------------|------------------|-----------------------------------------------------|------------------|----------------------|----------------|-----|-------|--------------------|

|                                                                           |                  | V <sub>CC</sub> = 5.0 V ±10<br>unless otherwise spe | 0%               | Land: only           | (7pc           | Min | Max   | -                  |

| Cycle time                                                                | tCYCA            | V <sub>CC</sub> = 4.5 V and 5.5 V                   |                  | 9, 10, 11            | ALL            | 200 | 8000  | ns                 |

| Clock pulse width                                                         | t <sub>CLS</sub> | V <sub>CC</sub> = 4.5 V and 5.5 V                   |                  | 9, 10, 11            | ALL            | 240 |       | ns                 |

|                                                                           | <sup>t</sup> CHA |                                                     |                  | , 10, 11             |                | 240 |       | 115                |

| Rise and fall times                                                       | tCRA             | V <sub>CC</sub> = 4.5 V and 5.5 V                   | ′ ,              | 9, 10, 11            | All            |     | 5     |                    |

|                                                                           | <sup>t</sup> CFA |                                                     | '                | , 10, 11             | 1              |     |       | ns                 |

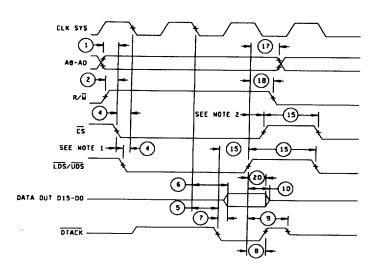

| Address valid to CS low                                                   | 1                | See figure 3                                        | Ş                | 9, 10, 11            | ALL            | 0   |       | ns                 |

| R/W valid to CS low                                                       | 2                | See figure 3                                        | ç                | , 10, 11             | All            | 0   |       | ns                 |

| Data in valid to LDS/UDS<br>low                                           | 3                | See figure 3                                        | 9                | 9, 10, 11            | ALL            | 0   |       | ns                 |

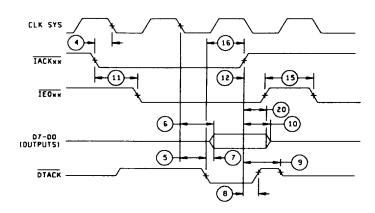

| CS, LDS/UDS, TACKXX valid<br>to CLK-SYS low                               | 4                | See figure 3                                        | 9                | , 10, 11             | ALL            | 5   |       | ns                 |

| CLK-SYS low to DTACK low                                                  | 5                | See figure 3                                        | 9                | , 10, 11             | ALL            |     | 45    | ns                 |

| CLK-SYS low to data out valid                                             | 6                | See figure 3                                        | 9                | , 10, 11             | All            |     | 50    | ns                 |

| DTACK low to data out valid                                               | 7                | 3/<br>See figure 3                                  | 9                | , 10, 11             | All            |     | 10    | ns                 |

| CS or LDS/ <u>UDS o</u> r IACKxx<br>high to DTACK high                    | 8                | 3/<br>See figure 3                                  | 9                | , 10, 11             | ALL            |     | 35    | ns                 |

| CS or LDS/ <u>UDS o</u> r IACKxx<br>high to DTACK hi-z                    | 9                | 3/<br>See figure 3                                  | 9                | , 10, 11             | ALL            |     | 50    | ns                 |

| CS or LDS/UDS or IACKxx<br>high to data out hi-z                          | 10               | 3/<br>See figure 3                                  | 9                | , 10, 11             | ALL'           |     | 25    | ns                 |

| IEIxx or IACKxx low to IEOxx                                              | 11               | See figure 3                                        | 9                | , 10, 11             | All            |     | 35    | ns                 |

| IACKxx high to IEOxx high                                                 | 12               | See figure 3                                        | 9                | , 10, 11             | All            |     | 40    | ns                 |

| See footnotes at the end of t                                             | able.            |                                                     | <u>-</u>         |                      | <b>.</b>       |     |       |                    |

|                                                                           | IT DRAWII        |                                                     | SIZE<br><b>A</b> |                      |                | -   | 59    | 62-9551            |

| MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  |                                                     |                  | REV                  | ISION LE       | VEL | SHEI  | <br>≣T<br><b>6</b> |

**9**004708 0014148 927 **=**

| Symbol | Conditions 1/<br>-55°C ≤ T <sub>C</sub> ≤ +125°C<br>V <sub>CC</sub> = 5.0 V ±10% | Group A                                                                                                                              | Device                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                         |

|--------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | V = E O V +109                                                                   | Group A<br>subgroups                                                                                                                 | type                                                                                                                                                                                                                                    | Limits                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                  | Unit                                                                                                                                                                                                                                                                                                                                                    |

|        | unless otherwise specified                                                       |                                                                                                                                      | !                                                                                                                                                                                                                                       | Min                                                                                                                                                                                                                                                                                                                | Max                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                         |

| 13     | See figure 3                                                                     | 9, 10, 11                                                                                                                            | ALL                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                    | 40                                                                                                                                                                                                                                                                                                                               | ns                                                                                                                                                                                                                                                                                                                                                      |

| 14     | See figure 3                                                                     | 9, 10, 11                                                                                                                            | All                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                    | 45                                                                                                                                                                                                                                                                                                                               | ns                                                                                                                                                                                                                                                                                                                                                      |

| 15     | See figure 3                                                                     | 9, 10, 11                                                                                                                            | ALL                                                                                                                                                                                                                                     | 15                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                  | ns                                                                                                                                                                                                                                                                                                                                                      |

| 16     | 3/<br>See figure 3                                                               | 9, 10, 11                                                                                                                            | ALL                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  | ns                                                                                                                                                                                                                                                                                                                                                      |

| 17     | 3/<br>See figure 3                                                               | 9, 10, 11                                                                                                                            | Att                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  | ns                                                                                                                                                                                                                                                                                                                                                      |

| 18     | 3/<br>See figure 3                                                               | 9, 10, 11                                                                                                                            | ALL                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  | ns                                                                                                                                                                                                                                                                                                                                                      |

| 19     | 3/<br>See figure 3                                                               | 9, 10, 11                                                                                                                            | ALL                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                | ns                                                                                                                                                                                                                                                                                                                                                      |

| 20     | 3/ See figure 3                                                                  | 9, 10, 11                                                                                                                            | All                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  | ns                                                                                                                                                                                                                                                                                                                                                      |

|        | 14<br>15<br>16<br>17<br>18                                                       | See figure 3  14  See figure 3  15  See figure 3  16  3/ See figure 3  17  3/ See figure 3  18  3/ See figure 3  19  3/ See figure 3 | See figure 3  14  See figure 3  9, 10, 11  15  See figure 3  9, 10, 11  16  3/ See figure 3  9, 10, 11  9, 10, 11  17  3/ See figure 3  9, 10, 11  18  3/ See figure 3  9, 10, 11  19  3/ See figure 3  9, 10, 11  9, 10, 11  9, 10, 11 | See figure 3  14  See figure 3  9, 10, 11  All  9, 10, 11  All  15  See figure 3  9, 10, 11  All  16  3/  See figure 3  9, 10, 11  All  9, 10, 11  All  17  3/  See figure 3  9, 10, 11  All  9, 10, 11  All  18  3/  See figure 3  9, 10, 11  All  9, 10, 11  All  9, 10, 11  All  9, 10, 11  All  9, 10, 11  All | See figure 3  14  See figure 3  9, 10, 11  All  15  See figure 3  9, 10, 11  All  15  16  3/ See figure 3  9, 10, 11  All  0  17  3/ See figure 3  9, 10, 11  All  0  18  3/ See figure 3  9, 10, 11  All  0  19  3/ See figure 3  9, 10, 11  All  0  9, 10, 11  All  0 | See figure 3  14  See figure 3  9, 10, 11  All  45  15  See figure 3  9, 10, 11  All  15  16  3/ See figure 3  9, 10, 11  All  0  17  3/ See figure 3  9, 10, 11  All  0  18  3/ See figure 3  9, 10, 11  All  0  19  3/ See figure 3  9, 10, 11  All  0  9, 10, 11  All  0 |

<sup>1/</sup> All testing performed using worst-case test conditions unless otherwise specified.

| STANDARD MICROCIRCUIT DRAWING                        | SIZE<br><b>A</b> |                | 5962-95518 |

|------------------------------------------------------|------------------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | SHEET<br>7 |

JUL 94

9004708 0014149 863 📟

<sup>2/</sup> IDD is measured with all I/O pins at 0 V, all input pins at 0 V except CLK-SYS and CLK-ARINC which run at

t<sub>CYC</sub> minimum.

3/ Guaranteed, but not tested.

| Ca | s | e | X |

|----|---|---|---|

|    |   |   |   |

|                    | ·                  | Ca                 | se X               |                    |                    |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |

| A1                 | GND                | C11                | RX6H               | J5                 | <b>A</b> 5         |

| A2                 | v <sub>DD</sub>    | D1                 | D4                 | J6                 | A6                 |

| A3                 | тх1н               | D2                 | D3                 | J7                 | LDS                |

| A4                 | TX2H               | D10                | RX6L               | J10                | TACKTX             |

| A5                 | TX3L               | D11                | RX7H               | J11                | IACKRX             |

| A6                 | TX2L               | E1                 | D7                 | К1                 | D15                |

| A7                 | RX1L               | E2                 | D6                 | K2                 | V <sub>DD</sub>    |

| A8                 | RX3H               | E3                 | V <sub>DD</sub>    | K3                 | CLK-SYS            |

| A9                 | RX4H               | E9                 | GND                | K4                 | AO                 |

| A10                | RX4L               | E10                | RX8H               | K5                 | A3                 |

| A11                | V <sub>DD</sub>    | E11                | RX8L               | K6                 | A2                 |

| B1                 | D1                 | F1                 | D8                 | K7                 | UDS                |

| B2                 | V <sub>DD</sub>    | F2                 | D5                 | K8                 | <del>c s</del>     |

| В3                 | GND                | F3                 | GND                | к9                 | CLK-ARINC          |

| B4                 | TX1L               | F9                 | DTACK              | K10                | IEITX              |

| B5                 | тхзн               | F10                | V <sub>DD</sub>    | K11                | IEIRX              |

| В6                 | RX1H               | F11                | RX7L               | L1                 | GND                |

| B7                 | RX2H               | G1                 | D9                 | L2                 | GND                |

| B8                 | RX3L               | G2                 | D10                | L3                 | V <sub>DD</sub>    |

| B9                 | GND                | G3                 | D11                | L4                 | A1                 |

| B10                | GND                | G9                 | IRQTX              | L5                 | A4                 |

| B11                | RX5L               | G10                | IEOTX              | L6                 | A7                 |

| <u>c1</u>          | D2                 | G11                | GND                | L7                 | 8A                 |

| C2                 | DO                 | Н1                 | D12                | L8                 | R/W                |

| C5                 | V <sub>DD</sub>    | H2                 | D13                | L9                 | RESET              |

| C6                 | GND                | н10                | IRQRX              | L10                | v <sub>DD</sub>    |

| C7                 | RX2L               | Н11                | IEORX              | L11                | GND                |

| C9                 | NC                 | J1                 | D14_               | ',                 |                    |

| C10                | RX5H               | 12                 | v <sub>DD</sub>    |                    |                    |

FIGURE 1. <u>Terminal connections</u>.

| STANDARD MICROCIRCUIT DRAWING                        | SIZE<br><b>A</b> |                | 5962-95518 |

|------------------------------------------------------|------------------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | SHEET<br>8 |

JUL 94

9004708 0014150 585

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| 1                  | NC NC              | 34                 | NC                 | 67                 | NC                 | 100                | NC                 |

| 2                  | NC                 | 35                 | NC                 | 68                 | NC                 | 101                | NC                 |

| 3                  | NC                 | 36                 | NC                 | 69                 | NC                 | 102                | NC                 |

| 4                  | V <sub>DD</sub>    | 37                 | v <sub>DD</sub>    | 70                 | V <sub>DD</sub>    | 103                | V <sub>DD</sub>    |

| 5                  | GND                | 38                 | GND                | 71                 | GND                | 104                | GND                |

| 6                  | D0                 | 39                 | CLK-SYS            | 72                 | IEITX              | 105                | GND                |

| 7                  | D1                 | 40                 | GND                | 73                 | TACKTX             | 106                | RX4L               |

| 8                  | NC                 | 41                 | NC                 | 74                 | IEIRX              | 107                | RX4H               |

| 9                  | D2                 | 42                 | V <sub>DD</sub>    | 75                 | TACKRX             | 108                | RX3L               |

| 10                 | D3                 | 43                 | AO                 | 76                 | IRQRX              | 109                | RX3H               |

| 11                 | D4                 | 44                 | A1                 | 77                 | IEORX              | 110                | RX1H               |

| 12                 | V <sub>DD</sub>    | 45                 | V <sub>DD</sub>    | 78                 | V <sub>DD</sub>    | 111                | V <sub>DD</sub>    |

| 13                 | GND                | 46                 | GND                | 79                 | GND                | 112                | NC NC              |

| 14                 | D6                 | 47                 | A5                 | 80                 | IEOIX              | 113                | RX2H               |

| 15                 | D7                 | 48                 | A3                 | 81                 | GND                | 114                | RX1L               |

| 16                 | D5                 | 49                 | A4                 | 82                 | NC                 | 115                | RX2L               |

| 17                 | GND                | 50                 | A2                 | 83                 | IRQIX              | 116                | GND                |

| 18                 | D11                | 51                 | A6                 | 84                 | DTACK              | 117                | TX2L               |

| 19                 | D9                 | 52                 | LDS                | 85                 | RX7L               | 118                | TX3L               |

| 20                 | V <sub>DD</sub>    | 53                 | v <sub>DD</sub>    | 86                 | NC                 | 119                | V <sub>DD</sub>    |

| 21                 | GND                | 54                 | GND                | 87                 | GND                | 120                | GND                |

| 22                 | D10                | 55                 | A8                 | 88                 | RX8L               | 121                | тхзн               |

| 23                 | D8                 | 56                 | UDS                | 89                 | RX8H               | 122                | V <sub>DD</sub>    |

| 24                 | D12                | 57                 | A7                 | 90                 | GND                | 123                | TX2H               |

| 25                 | D13                | 58                 | R/₩                | 91                 | RX7H               | 124                | TX1L               |

| 26                 | D14                | 59                 | <del>CS</del>      | 92                 | RX6L               | 125                | ТХ1Н               |

| 27                 | D15                | 60                 | RESET              | 93                 | RX6H               | 126                | NC NC              |

| 28                 | V <sub>DD</sub>    | 61                 | V <sub>DD</sub>    | 94                 | V <sub>DD</sub>    | 127                | V <sub>DD</sub>    |

| 29                 | GND                | 62                 | GND                | 95                 | GND                | 128                | GND                |

| 30                 | NC                 | 63                 | CLK-ARINC          | 96                 | RX5L               | 129                | GND                |

| 31                 | NC                 | 64                 | GND                | 97                 | RX5H               | 130                | NC NC              |

| 32                 | NC                 | 65                 | NC NC              | 98                 | V <sub>DD</sub>    | 131                | NC NC              |

| 33                 | NC                 | 66                 | NC                 | 99                 | NC NC              | 132                | NC NC              |

| · .                |                    | FIGURE             |                    | ·                  | continued          |                    | 1                  |

|                    | STAND              |                    |                    | SIZE<br><b>A</b>   |                    |                    | 5962-9551          |

9004708 0014151 411 🖿

Transmitter channel block diagram

FIGURE 2. Block diagram.

| STANDARD MICROCIRCUIT DRAWING                        | SIZE<br><b>A</b> |                | 5962-95518 |

|------------------------------------------------------|------------------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | SHEET 10   |

DESC FORM 193A

JUL 94

9004708 0014152 358

Receiver channel block diagram

FIGURE 2. Block diagram. - continued

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br><b>A</b> |                | 5962-95518  |

|---------------------------------------------------------------------------------------------|------------------|----------------|-------------|

|                                                                                             |                  | REVISION LEVEL | SHEET<br>11 |

DESC FORM 193A JUL 94

9004708 0014153 294

Read cycle

NOTE 1.  $\overline{\text{LDS/UDS}}$  can be asserted on the next CLK-SYS period after  $\overline{\text{CS}}$  goes low bit (4) must be met for the next period.

NOTE 2. The cycle ends when the first of CS, LDS/UDS goes high.

Write cycle

NOTE 3. LDS/UDS can be asserted on the same CLK-SYS priod as CS but (4) must be met.

FIGURE 3. <u>liming waveforms</u>.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br><b>A</b> |                | 5962-95518  |

|------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | SHEET<br>12 |

DESC FORM 193A JUL 94

9004708 0014154 120 📟

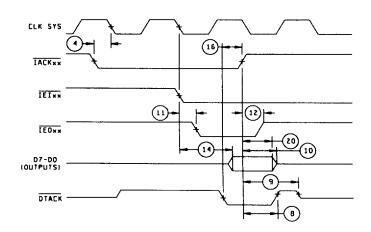

Interrupt cycle ( $\overline{IEIxx} = 0$ ).

NOTE:

- If  $\overline{\text{UDS}}$  = 1, D15-D8 stay hi-z else D15-D8 drive the bus with a stable unknown value.

- If IEOxx goes low, nor vector neither DTACK are generated, else IEOxx stays inactive and a vector is generated (D7-D0 and DTACK).

Interrupt cycle ( $\overline{IEIxx} = 1$ )

FIGURE 3. Timing waveforms. - continued

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br><b>A</b> |                | 5962-95518      |

|------------------------------------------------------|------------------|----------------|-----------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | SHEET <b>13</b> |

DESC FORM 193A JUL 94

9004708 0014155 067

- 4.2 <u>Screening</u>. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. For device classes Q and V, screening shall be in accordance with MIL-I-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection.

- 4.2.1 Additional criteria for device class M.

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, or C. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

- 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-I-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in appendix B of MIL-I-38535.

- 4.3 <u>Qualification inspection for device classes Q and V</u>. Qualification inspection for device classes Q and V shall be in accordance with MIL-I-38535. Inspections to be performed shall be those specified in MIL-I-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

- 4.4 <u>Conformance inspection</u>. Quality conformance inspection for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein) and as specified herein. Inspections to be performed for device class M shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4). Technology conformance inspection for classes Q and V shall be in accordance with MIL-I-38535 including groups A, B, C, D, and E inspections and as specified herein except where option 2 of MIL-I-38535 permits alternate in-line control testing.

- 4.4.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. For device class M, subgroups 7 and 8 tests shall be sufficient to verify the functionallity of the device. For device classes Q and V, subgroups 7 and 8 shall include verifying the functionality of the device; these tests shall have been fault graded in accordance with MIL-STD-883, test method 5012 (see 1.5 herein).

- c. Subgroup 4 ( $C_{1N}$  measurment) shall be measured only for the initial test and after process or design changes which may affect input capacitance.

- 4.4.2 <u>Group C inspection</u>. The group C inspection end-point electrical parameters shall be as specified in table II herein.

- 4.4.2.1 Additional criteria for device class M. Steady-state life test conditions, method 1005 of MIL-STD-883:

- a. Test condition A, B, or C. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005.

- b.  $T_A = +125$ °C, minimum.

- c. Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br><b>A</b> |                | 5962-95518         |

|---------------------------------------------------------------------------------------------|------------------|----------------|--------------------|

|                                                                                             |                  | REVISION LEVEL | SHEET<br><b>14</b> |

JUL 94

9004708 0014156 TT3

TABLE II. <u>Electrical test requirements</u>.

| Test requirements                                 | Subgroups<br>(in accordance with<br>MIL-STD-883,<br>TM 5005, table I) | Subgroups<br>(in accordance<br>MIL-I-38535, tab | with                          |

|---------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------|-------------------------------|

|                                                   | Device<br>class M                                                     | Device<br>class Q                               | Device<br>class V             |

| Interim electrical parameters (see 4.2)           | 1                                                                     | 1                                               | 1                             |

| Final electrical parameters (see 4.2)             | 1/1,2,3,7,8,9,10,11                                                   | <u>1</u> /1,2,3,7,8,9,<br>10,11                 | 2/1,2,3,7,8,<br>9,10,11       |

| Group A test<br>requirements (see 4.4)            | 1, 2, 3, 4, 7, 8,9,<br>10, 11                                         | 1, 2, 3, 4, 7,<br>8, 9, 10, 11                  | 1, 2, 3, 4, 7<br>8, 9, 10, 11 |

| Group C end-point electrical parameters (see 4.4) | 1, 2, 3                                                               | 1, 2, 3                                         | 1, 2, 3                       |

| Group D end-point electrical parameters (see 4.4) | 1, 2, 3                                                               | 1, 2, 3,                                        | 1, 2, 3                       |

| Group E end-point electrical parameters (see 4.4) | 1, 7, 9                                                               | 1, 7, 9                                         | 1, 7, 9                       |

- 1/ PDA applies to subgroup 1.

- 2/ PDA applies to subgroups 1 and 7.

- 4.4.2.2 <u>Additional criteria for device classes Q and V</u>. The steady-state life test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The test circuit shall be maintained under document revision level control by the device manufacturer's TRB, in accordance with MIL-I-38535, and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005.

- 4.4.3 <u>Group D inspection</u>. The group D inspection end-point electrical parameters shall be as specified in table II herein.

- 4.4.4 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein). RHA levels for device classes Q and V shall be M, D, L, R, F, G, and H and for device class M shall be M and D.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. For device class M, the devices shall be subjected to radiation hardness assured tests as specified in MIL-I-38535, appendix A, for the RHA level being tested. For device classes Q and V, the devices or test vehicle shall be subjected to radiation hardness assured tests as specified in MIL-I-38535 for the RHA level being tested. All device classes must meet the postirradiation end-point electrical parameter limits as defined in table I at  $T_A$  = +25°C ±5°C, after exposure, to the subgroups specified in table II herein.

- c. When specified in the purchase order or contract, a copy of the RHA delta limits shall be supplied.

| STANDARD<br>MICROCIRCUIT DRAWING                        | SIZE<br><b>A</b> |                | 5962-95518      |

|---------------------------------------------------------|------------------|----------------|-----------------|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |                  | REVISION LEVEL | SHEET <b>15</b> |

■ 9004708 0014157 93T **■**

# 5. PACKAGING

5.1 <u>Packaging requirements</u>. The requirements for packaging shall be in accordance with MIL-STD-883 (see 3.1 herein) for device class M and MIL-I-38535 for device classes Q and V.

#### NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.1.1 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.1.2 <u>Substitutability</u>. Device class Q devices will replace device class M devices.

- 6.2 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-973 using DD Form 1692, Engineering Change Proposal.

- 6.3 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and which SMD's are applicable to that system. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DESC-EC, telephone (513) 296-6047.

- 6.4 <u>Comments</u>. Comments on this drawing should be directed to DESC-EC, Dayton, Ohio 45444-5765, or telephone (513) 296-8525.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE **5962-95518**REVISION LEVEL SHEET 16

DESC FORM 193A

9004708 0014158 876

6.5 <u>Abbreviations, symbols, and definitions</u>. The abbreviations, symbols, and definitions used herein are defined in MIL-I-38535 and MIL-STD-1331.

| Bit                     | Function                                                                          | Comments                                                                                                                                                                                                  |

|-------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 15                  | Channel enable                                                                    | O: channel is out of service 1: channel is in service                                                                                                                                                     |

| Bit 14                  | Test mode                                                                         | O: external ARINC lines as input (normal operation) 1: third transmitter lines as input (test mode)                                                                                                       |

| Bit 13                  | Label control                                                                     | O: no control, all the labels are accepted 1: automatic check of the label according to the label control matrix                                                                                          |

| Bit 12                  | LCMWE label control matrix write enable                                           | 0: receiving mode (write to the matrix are disabled) 1: programmation mode for labels control matrix                                                                                                      |

| Bit 11                  | Parity control                                                                    | 0: even parity check<br>1: odd parity check                                                                                                                                                               |

| Bit 10                  | Paraity control                                                                   | 0: parity ckeck is disable<br>1: parity check is enable                                                                                                                                                   |

| Bit 9<br>Bit 8          | Not used<br>Not used                                                              |                                                                                                                                                                                                           |

| Bit 7                   | Wrong parity: this feature is enable only if self test register bit 0 is set to 1 | O: received message parity is correct if read, reset wrong , wrong parity flag if written 1: an incorrect received message parity has been detected (the corresponding message is lost) (set by hardware) |

| Bit 6<br>Bit 5<br>Bit 4 | Not used<br>Not used<br>Not used                                                  |                                                                                                                                                                                                           |

| Bit 0 to 3              | Channel priority: order                                                           | The lowest value will give the highest priority. Each channel must have a unique channel priority order. If several messages are pending, the interrupt vector will account for highest priority channel  |

This read/write register controls the function of the related receiver channel.

The lowest value will give the highest priority. If two channels have the same priority, one of them will never be able to send its interrupt vector to the microprocessor. Each channel must have a unique channel priority order.

Receiver control register.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-95518

REVISION LEVEL

SHEET

17

DESC FORM 193A JUL 94

**--** 9004708 0014159 702 **--**

| Bit          | Function                | Comments                                                                                                                                                                                                                                       |

|--------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 15       | Enable transmission     | 0: channel out of service (stops on going transmission) 1: channel in service 1 to 0: transition is not allowed at the same time as an 1 to 0 transition of the bit 4                                                                          |

| Bit 14       | Test (only 3rd channel) | O: normal operating     1: test, output are only driven on internal lines for input testing                                                                                                                                                    |

| Bit 13 to 12 | Not used                |                                                                                                                                                                                                                                                |

| Bit 11       | Parity control          | 0: even parity calculation 1: odd parity calculation                                                                                                                                                                                           |

| Bit 10       | Parity control          | O: parity disable. Bit 32 of the message stays unchanged 1: parity enable. Bit 32 of the message will be forced by parity control                                                                                                              |

| Bit 9 to 5   | Transmission gap        | "transmission gap" which is the delay between two 32 bit ARINC messages (in ARINC bit)                                                                                                                                                         |

| Bit 4        | Reset FIFO              | <ul> <li>write a 0 in this bit, reset the FIFO counter</li> <li>this bit must be set to 1 before any write in the transmit buffer</li> <li>1 to 0: transition is not allowed at the same time as an 1 to 0 transition of the bit 15</li> </ul> |

| Bit 3 to 0   | Number of msg           | these four bits contain the number of messages within the FIFO                                                                                                                                                                                 |

Transmitter control register