# **FEATURES**

- Provides simultaneous hardwareassist for bit-mapped graphics operations on four independent memory planes. Includes two 32-bit barrel shifters in each Raster Op section.

- Performance increase over software implementations: 4 x (Planes) x Software

- Supports any type of raster image manipulation, including CRT displays and laser printers

- Implements 256 possible raster operations on source, destination, and pattern data

- 100-lead plastic quad flat pack (PJQFP) package; 5 V supply

- Low power CMOS technology

### DESCRIPTION

The VL82C164 Quad Raster Op ALU (QRO) provides hardware-assisted performance enhancement for bit manipulation operations in bit-mapped

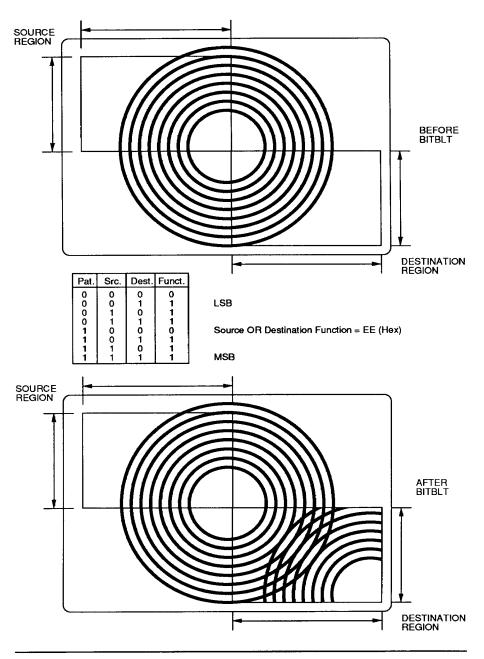

graphics displays. These operations, called bit block translation (BITBLT), allow bit-mapped images to be combined and manipulated by logical operations. These operations include AND, OR, and XOR, as well as a wide range of others which can be arbitrarily defined by the user. The QRO also contains Mask Registers which provide automatic clipping capability at the boundaries of the image section being manipulated.

The BITBLT operation is applicable to a wide variety of graphics operations, including proportionally spaced text display using arbitrary fonts, attributes, and enhancements. Successive applications of BITBLT can perform such operations as scaling, filling, and texturing.

In a typical application, the QRO operates on display data in 16-bit words that are latched into input buffers by external hardware. Source, Destination, Pattern, and Output Registers have

# QUAD RASTER OP ALU

dedicated strobe signals, which eliminate the delays associated with address decode. Each of the four independent Raster Op sections has a dedicated chip select to allow maximum speed as well as allowing the same data to be loaded into multiple sections simultaneously. Each section can also be selected via a pair of address lines, allowing a linear address map for host access. For each cycle of operation, the Source and Destination Registers are loaded and the source is aligned according to a previously loaded shift count and combined with the destination and pattern data. The result is written back to the display memory via the dedicated strobe. The QRO can scan forward or backward through the display memory. For cases where only part of the memory word is to be modified, the QRO automatically applies the appropriate mask at each end of the scan.

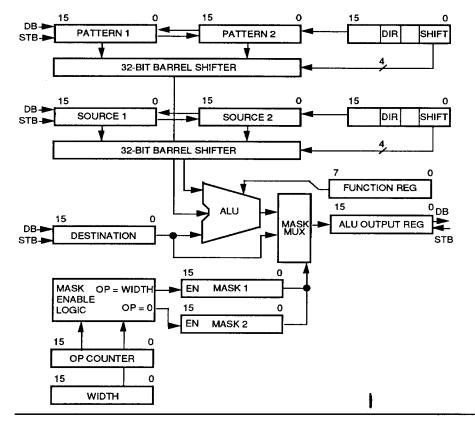

# **BLOCK DIAGRAM** (Three other Raster Op ALU's are identical.)

# ORDER INFORMATION

| Part<br>Number | Package                |

|----------------|------------------------|

| VL82C164-FC    | Plastic Quad Flat Pack |

**Note:** Operating temperature range is 0°C to +70°C.

March 1990

VLSI Technology, Inc. • 8375 South River Parkway • Tempe, AZ 85284 • 602-752-8574

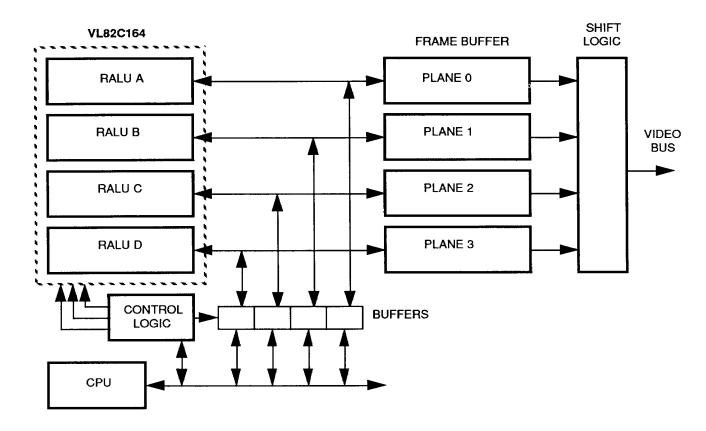

# SYSTEM BLOCK DIAGRAM

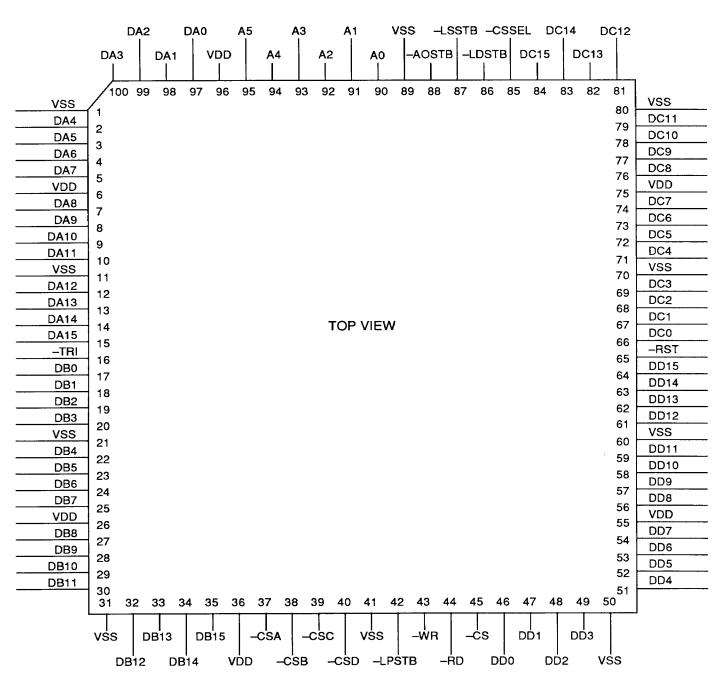

# PIN DIAGRAM PLASTIC QUAD FLAT PACK (PJQFP)

### VL82C164

# SIGNAL DESCRIPTIONS

| Signal<br>Name | Pin<br>Number                    | Signal<br>Type | Signal  Description                                                                                                                                                                                                                                                                           |

|----------------|----------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DA0-DA15       | 97-100,<br>2-5, 7-10,<br>12-15   | I/O            | Bidirectional data lines for Raster Op Section A enabled by -CSA or A0-A5 and -CS.                                                                                                                                                                                                            |

| -TRI           | 16                               | I              | Test Pin - Disables output drivers on all I/O lines when low. This pin has an internal pull up resistor.                                                                                                                                                                                      |

| DB0-DB15       | 17-20,<br>22-25, 27-30,<br>32-35 | I/O            | Bidirectional data lines for Raster Op Section B enabled by -CSB or A0-A5 and -CS.                                                                                                                                                                                                            |

| -CSA           | 37                               | 1              | Chip Select A - Enables register I/O to Raster Op Section A.                                                                                                                                                                                                                                  |

| -CSB           | 38                               | 1              | Chip Select B - Enables register I/O to Raster Op Section B.                                                                                                                                                                                                                                  |

| -CSC           | 39                               | 1              | Chip Select D - Enables register I/O to Raster Op Section D.                                                                                                                                                                                                                                  |

| -CSD           | 40                               | 1              | Chip Select C - Enables register I/O to Raster Op Section C.                                                                                                                                                                                                                                  |

| -LPSTB         | 42                               | I              | Load Pattern Strobe - Loads all four Pattern Registers from their associated data busses according to the Direction Bit in the Pattern Shift Register. The other Pattern Register in the Raster Op section is loaded with the previous contents of the register currently being loaded.       |

| –WR            | 43                               | 1              | Write - Used in conjunction with A0-A5 and -CS to write data into any of the internal registers.                                                                                                                                                                                              |

| -RD            | 44                               | I              | Read - Used in conjunction with A0-A5 and -CS to read data from any of the internal registers.                                                                                                                                                                                                |

| -CS            | 45                               | 1              | Chip Select - This is a General Chip Select signal used in conjunction with A0-A5 and -RD or -WR to access the internal registers.                                                                                                                                                            |

| DD0-DD15       | 46-49,<br>51-54, 56-59,<br>61-64 | 1/O            | Bidirectional data lines for Raster Op Section D enabled by -CSD or A0-A5 and -CS.                                                                                                                                                                                                            |

| -RST           | 65                               | ı              | Reset - This signal, when low, resets the Shift Count and Direction Bit to zero.                                                                                                                                                                                                              |

| DC0-DC15       | 66-69,<br>71-74, 76-79,<br>81-84 | I/O            | Bidirectional data lines for Raster Op Section C enabled by -CSC or A0-A5 and -CS.                                                                                                                                                                                                            |

| -CSSEL         | 85                               | 1              | CS Select - When low, the Direct Chip Selects (-CSA, -CSB, -CSC, -CSD) are used. When high, the Address Lines (A4,A5) and General Chip Select (-CS) are used.                                                                                                                                 |

| -LDSTB         | 86                               | I              | Load Destination Strobe - Loads all four Destination Registers from their associated data busses. The Op Counter is also decremented each time this signal is pulsed.                                                                                                                         |

| -LSSTB         | 87                               | I              | Load Source Strobe - Loads all four Source Registers from their associated data busses according to the Direction Bit in the Shift Count Register. The other source register within the Raster Op section is loaded with the previous contents of the source register currently being loaded. |

| -AOSTB         | 88                               | 1              | ALU Output Strobe - When low, enables the output of the function decoder (ALU) onto the data bus pins of all four Raster Op sections. This signal should not be active when -CS and -RD or -WR are active.                                                                                    |

# SIGNAL DESCRIPTIONS (Cont.)

| Signal<br>Name | Pin<br>Number                               | Signal<br>Type | Signal<br>Description                                                                                                                                                                                                  |

|----------------|---------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A5          | 90-95                                       | i .            | Register Address - Address inputs which specify which internal register to access for read or write operations. A0-A3 select individual registers within a section, A4 and A5 select which of four sections to access. |

| VDD            | 6, 26, 36,<br>55, 75, 96                    |                | Power - The power supply requirement is 5 V $\pm$ 5%.                                                                                                                                                                  |

| VSS            | 1, 11, 21,<br>31, 41, 50,<br>60, 70, 80, 89 |                | Ground                                                                                                                                                                                                                 |

## **FUNCTIONAL DESCRIPTION**

The VL82C164 contains four complete identical Raster Op sections. Each section consists of five basic components: Source Shifter, Pattern Shifter, Function Decoder, Op Counter, and Mask Registers. The internal data path is 16-bits wide, enabling all internal registers to be accessed easily for context saving and restoring. In normal operation, the Source and Pattern Shifters align the 32-bit source and pattern data from which 16-bit values are extracted and combined with the data in the Destination Register by the Function Decoder. The Op Counter is decremented and, whenever its value equals zero or a user defined width. one of the Mask Registers is activated to clip the resulting value at the BITBLT region boundary, if necessary. The Internal Block Diagram shows how the functional blocks relate to each other and the internal data bus. The System Block Diagram shows how the VL82C164 might be configured with a 16-bit CPU and 256K x 4 VRAMs to implement a high performance 16-color (4-plane) graphics subsystem capable of resolutions up to 2360 x 1770. The following paragraphs describe how each of the major functional subsections work.

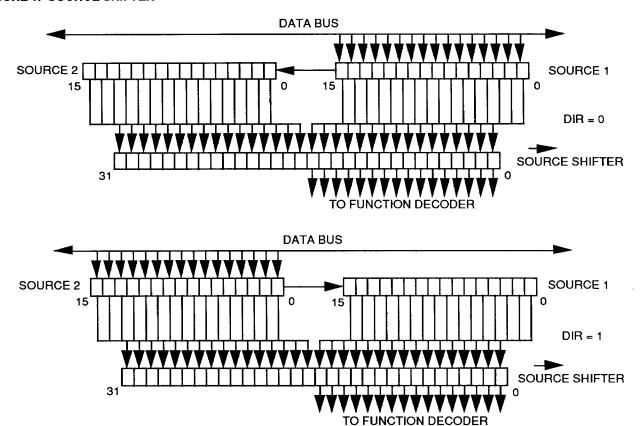

# **SOURCE SHIFTER**

The Source Shifter performs bit alignment on the concatenated data in the Source 1 and Source 2 Registers. The number of bits the data is shifted depends on the value in the Source Shift Register. When –LSSTB is strobed, the Source Shifter extracts 16 bits of contiguous data from the

concatenated and shifted Source 1 and Source 2 Registers as follows:

- If the Direction Bit in the Source Shift Register is zero, each new data word is written to the Source 1 Register, and the previous data from the Source 1 Register is transferred to the Source 2 Register.

- If the Direction Bit in the Source Shift Register is one, each new data word is written to the Source 2 Register, and the previous data from the Source 2 Register is transferred to the Source 1 Register.

- 3. Source Shift bits 0 through 3 form a 4-bit shift count. The shift count determines the amount of right shift applied to the 32-bit data in the concatenated Source Registers. The 16-bit result is always extracted from bits 0-15 of the shifter, which correspond to bits 0-15 of the Source 1 Register. The net effect is that if the Direction Bit is one and the shift count is zero, the data from Source 2 is shifted right 16 bits to the extraction point and ends up being passed through unchanged. If the Direction Bit is zero and the shift count is zero, the data from Source 1 is passed through unchanged. If the shift count is other than zero, the data is shifted right by the number of bits specified, regardless of the state of the Direction Bit. (See Figure 1.)

## **PATTERN SHIFTER**

The Pattern Shifter performs bit alignment on the concatenated data in the Pattern 1 and Pattern 2 Registers. The number of bits the data is shifted

- depends on the value in the Pattern Shift Register. When –LSSTB is strobed, the Pattern Shifter extracts 16 bits of contiguous data from the concatenated and shifted Pattern 1 and Pattern 2 Registers as follows:

- If the Direction Bit in the Pattern Shift Register is zero, each new data word is written to the Pattern 1 Register, and the previous data from the Pattern 1 Register is transferred to the Pattern 2 Register.

- If the Direction Bit in the Pattern Shift Register is one, each new data word is written to the Pattern 2 Register and the previous data from the Pattern 2 Register is transferred to the Pattern 1 Register.

- 3. Pattern Shift bits 0 through 3 form a 4-bit shift count. The shift count determines the amount of right shift applied to the 32-bit data in the concatenated Pattern Registers. The 16-bit result is always extracted from bits 0-15 of the shifter, which corresponds to bits 0-15 of the Pattern 1 Register. The net effect is that if the Direction Bit is one and the shift count is zero, the data from Pattern 2 is shifted right 16 bits to the extraction point and ends up being passed through unchanged. If the Direction Bit is zero and the shift count is zero, the data from Pattern 1 is passed through unchanged. If the shift count is other than zero, the data is shifted right by the number of bits specified, regardless of the state of the Direction Bit. The Pattern Shift Register works essentially the

#### FIGURE 1. SOURCE SHIFTER

same way as the Source Shift Register. The only difference is that when the –RST input is low, the Pattern Shift Count is reset to zero.

### **FUNCTION DECODER**

The Function Decoder performs a Boolean operation on the contents of the Destination Register, the output of the Pattern Shifter, and the output of the Source Shifter. The Boolean operation is specified by the Function Register. With the three operands, 256 different Boolean operations are possible. The result of the operation is available on the I/O bus when the -AOSTB control signal is active. The -AOSTB signal must not be active at the same time that -CS and -RD or -WR are active. The result of the Boolean operation is also available by reading the ALU Output Register.

To understand how the Function Decoder performs the desired Boolean operation, note again that with three operands (data in the Source, Pattern and Destination Registers) a total of 256 different Boolean operations are possible. The 8-bit Function Register defines which of the 256 possible functions to use as follows: each bit of the final result is formed as a Boolean combination of the corresponding bits from each of the three operands (Source, Pattern, and Destination). These three bits combine to form a value from 0 to 7 which is used to select a bit from the 8-bit Function Register. In this way, a three-input Boolean function of arbitrary complexity can be formed simply by storing an 8-bit value in the Function Register.

For example (see Figure 2), to "paint" a new image over an existing image requires the source data (image) to be ORed with the destination data (image). This means "Source Register OR the Destination Register". For each bit, there are four possible results of this operation between these two registers.

However, since the Pattern Register is always included, even when it is a "don't care," a total of eight different possible results of this one Boolean operation is possible. These eight combinations define the "function code" for the overlay operation. Thus, the function code is really defined as the result (and the only result possible) of a Boolean combination of the Source, Destination, and Pattern Registers. In using the VL82C164, the application defines which of the 256 possible Boolean combinations of the Source, **Destination and Pattern Registers** define those "functions" required of the application. When that "function" is required, the corresponding function code is loaded into the Function Regis-

The function codes required of an application are normally determined ahead of time by the user and stored in memory to be used as needed. The determination of the correct function

#### FIGURE 2. RASTER OPERATION EXAMPLE

code is a matter of simply applying the definitions stated above (see Block Diagram), in a simple method. The truth table for Pattern, Source, and Destination Bits is written, with the desired output for each combination. This is read as the desired value of the Function Register, with the least significant bit as shown in the Block Diagram. Using this method, the software

engineer can easily define a pattern to suit each specific need.

#### **OP COUNTER**

The Op Counter, in conjunction with the Width and Mask Registers, provides for masking of selected bits in the Destination Register. This masking prevents the VL16164 from modifying selected areas of display memory when performing BITBLT's. For example, clipping

may be required at the edges of a window. The function of the Op Counter is to keep track of the beginning and end of each row, so that the Mask Registers can handle this clipping automatically, without additional processor intervention.

The Op Counter should be initialized to the same value as the Width Register prior to the beginning of a raster operation, and is internally clocked by the –LDSTB signal. Masking is enabled by the first –LDSTB pulse after loading the Op Counter. If context switching is utilized, reinitialization (including loading the Op Counter) is necessary upon re-entering a context in the middle of a BITBLT.

#### **EXAMPLE**

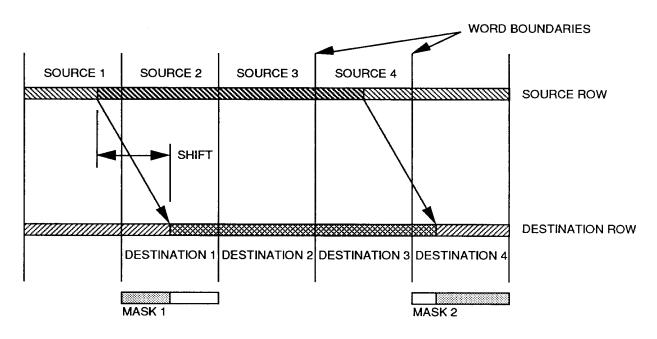

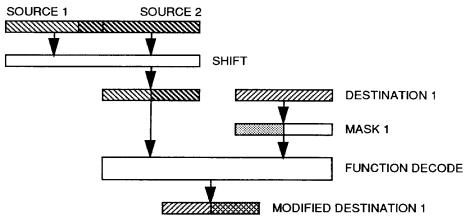

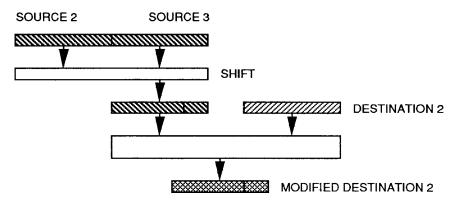

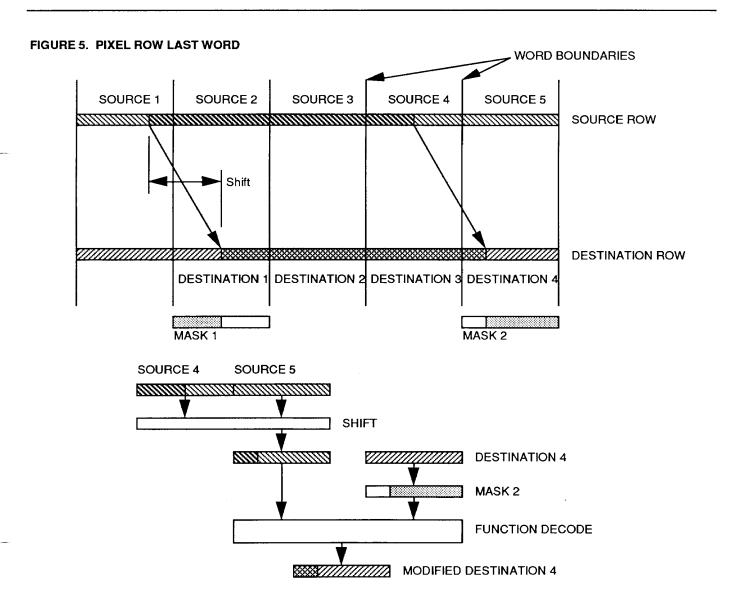

Figures 3, 4 and 5 illustrate how a single row from a block of pixels might be processed. Neither the source nor the destination regions are aligned on word boundaries, to show how the shift and mask logic works. There are three cases illustrated: the first and last word in the row, which are masked, and the remaining words, which are not masked. Figure 3 shows how the source and destination region boundaries relate to the memory word boundaries, how the Mask Registers relate to the destination boundaries, and how the shift value corresponds to the relative source and destination boundary positions. In this case, the shift value accounts for the entire horizontal displacement of the image, but this need not be the case. The true meaning of the shift value is relative to the destination word boundary, which may be anywhere in memory. Figure 3 also shows how the first word of the destination region is derived: source words 1 and 2 are concatenated and shifted to align the source region boundary with the destination region boundary, the existing destination word is combined with the resulting source word under Mask 1 and according the programmed function, and the modified destination word is written back into memory. Figure 4 shows how destination words 2 and 3 would be processed. This is exactly the same as for word 1 except that no masking is done, since no boundaries are involved. Figure 5 shows how the last word of the destination region is derived: source words 4

# FIGURE 3. PIXEL ROW FIRST WORD

### FIGURE 4. PIXEL ROW SECOND WORD

and 5 are concatenated and shifted to align the source region boundary with the destination region boundary, the existing destination word is combined with the resulting source word under Mask 2 and according the programmed function, and the modified destination word is written back into memory. This whole process would then be repeated for every row in the block of pixels to be transferred.

### REGISTER DESCRIPTIONS

As shown in the Block Diagram, each Raster Op segment consists of a number of registers, each connected to the internal 16-bit data path. Of these registers, four are used very often and are directly accessible from the data bus by the assertion of strobe signals.

## SOURCE

The Source Register holds a 16-bit word of data to be modified by a raster operation. It is loaded from the data bus by the assertion of the –LSSTB signal.

#### **PATTERN**

The Pattern Register holds a 16-bit word of data to be combined with source and destination data. It is loaded from the data bus by the assertion of the –LPSTB signal.

### **DESTINATION**

The Destination Register holds a word of data from the bit-mapped display that

is modified by the source data and raster operation. It is loaded from the data bus when –LDSTB is asserted.

#### **ALU OUTPUT**

The ALU Output Register holds the result of the raster operation to be written back to memory. The contents may be put onto the data bus by the assertion of the –AOSTB signal.

The remainder of the registers are typically set up for a series of operations and are not changed until the end of a scan line.

### **SOURCE DIR / SHIFT**

This register controls the direction of the raster operation (left-to-right or right-to-left). In addition, it specifies the number of bits to shift to align the source with the destination fields.

#### **PATTERN DIR / SHIFT**

This register controls the direction of the raster operation (left-to-right or right-to-left). In addition, it specifies the number of bits to shift to align the pattern with the destination fields.

### MASK 1 AND 2

These registers are used to define the left and right boundaries of the area on the screen that is manipulated. (The Direction Bit affects which register corresponds to left versus right.) A bit set in these registers allows the corresponding bit in the Destination Register to pass through unaltered.

When the Op Counter is equal to the Width Register (usually for the first raster operation on each scan line), the Mask 1 Register selects bits to be included in the operation. Masking is disabled until the Op Counter is zero (usually for the last operation on a scan line); at that time, the Mask 2 Register is used.

#### **FUNCTION**

This register contains the operator that is used to combine the source, destination, and pattern data.

## **OP COUNTER**

The Op Counter Register specifies the current count of the operation in progress. The Op Counter is decremented each time –LDSTB is brought active. After the Op Counter goes to zero, the next –LDSTB causes the Op Counter to be reloaded with the value of the Width Register prior to the next operation.

#### WIDTH

The Width Register specifies the width of the line (in 16-bit words) on which raster operations will take place, minus one.

### **FLAG REGISTER**

The Flag Register is uncommitted and can be used to temporarily store context information for multi-tasking implementations.

**TABLE 1. REGISTER MAP**

|    | Register | Register |    |               |

|----|----------|----------|----|---------------|

| А3 | A2       | A1       | A0 | Name          |

| 0  | 0        | 0        | 0  | Destination   |

| 0  | 0        | 0        | 1  | Source 1      |

| 0  | 0        | 1        | 0  | Source 2      |

| 0  | 0        | 1        | 11 | Pattern 1     |

| 0  | 1        | 0        | 0  | Mask 1        |

| 0  | 1        | 0        | 1  | Mask 2        |

| 0  | 11       | 1        | 0  | Source Shift  |

| 0  | 1        | 1        | 1  | Function      |

| 1  | 0        | 0        | 0  | Width         |

| 1  | 0        | 0        | 1  | Op Count      |

| 1  | 0        | 11       | o  | ALU Output    |

| 1  | 0        | 1        | 1  | Pattern 2     |

| 1  | 1        | 0        | 0  | Pattern Shift |

| 1  | 1        | 0        | 1  | Reserved      |

| 1  | 1        | 1        | 0  | Reserved      |

| 1  | 1        | 1        | 1  | Flag          |

**TABLE 2. SECTION MAP**

| Section A  | Raster Op |             |  |

|------------|-----------|-------------|--|

| <b>A</b> 5 | A4        | Section     |  |

| 0          | 0         | Raster Op A |  |

| 0          | 1         | Raster Op B |  |

| 1          | 0         | Raster Op C |  |

| 1          | 1         | Raster Op D |  |

# AC CHARACTERISTICS: TA = 0°C to +70°C, VDD = 5 V ± 5%, VSS = 0 V, Capacitive Load = 50 pF

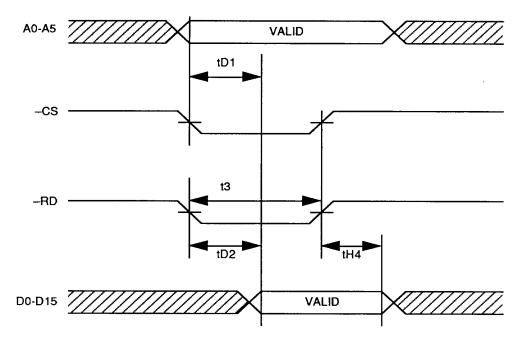

# **REGISTER READ TIMING (SEE FIGURE 6.)**

| Symbol | Parameter                                   | Min. | Max. | Units | Condition    |

|--------|---------------------------------------------|------|------|-------|--------------|

| tD1    | Data Valid after -CS Active and A0-A5 Valid | _    | 52   | ns    | (-RD Active) |

| tD2    | Data Valid after –RD Active                 | _    | 45   | ns    | (–CS Active) |

| t3     | –RD Signal Pulse Width                      | 45   |      | ns    |              |

| tH4    | Data Hold after -RD, -CS Inactive           | 5    | _    | ns    |              |

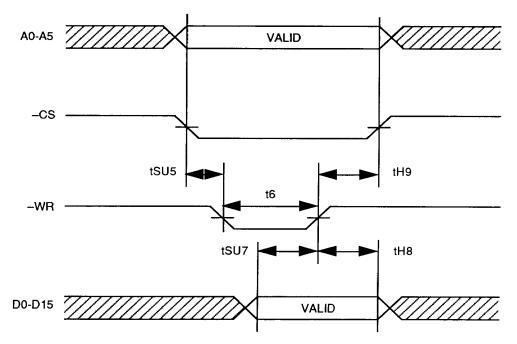

# **REGISTER WRITE TIMING (SEE FIGURE 7.)**

| Symbol | Parameter                          | Min. | Max. | Units | Condition |

|--------|------------------------------------|------|------|-------|-----------|

| tSU5   | -CS, A0-A5 Setup to -WR Active     | 5    |      | ns    |           |

| t6     | –WR Signal Pulse Width             | 30   | _    | ns    |           |

| tSU7   | Data Setup to -WR Inactive         | 9    |      | ns    |           |

| tH8    | Data Hold after -WR Inactive       | 19   | -    | ns    |           |

| tH9    | -CS, A0-A5 Hold after -WR Inactive | 8    | _    | ns    |           |

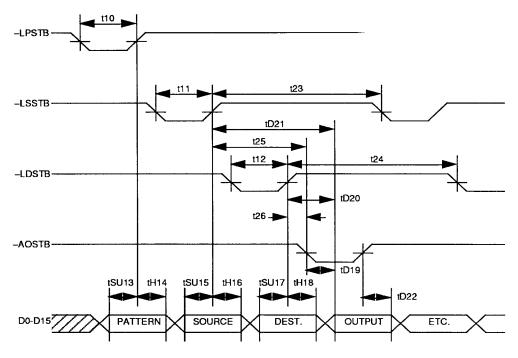

# DIRECT STROBE CONTROL SIGNAL TIMING (SEE FIGURE 8.)

| Symbol | Parameter                                | Min. | Max. | Units | Condition |

|--------|------------------------------------------|------|------|-------|-----------|

| t10    | -LPSTB Pulse Width                       | 10   | _    | ns    |           |

| t11    | -LSSTB Pulse Width                       | 9    |      | ns    |           |

| t12    | –LDSTB Pulse Width                       | 10   | _    | ns    |           |

| tSU13  | Data Setup to -LPSTB Inactive            | 10   | _    | ns    |           |

| tH14   | Data Hold after -LPSTB Inactive          | 9    | _    | ns    |           |

| tSU15  | Data Setup to -LSSTB Inactive            | 10   | _    | ns    |           |

| tH16   | Data Hold after -LSSTB Inactive          | 9    | _    | ns    |           |

| tSU17  | Data Setup to -LDSTB Inactive            | 10   | _    | ns    |           |

| tH18   | Data Hold after -LDSTB Inactive          | 9    | _    | ns    |           |

| tD19   | Output Valid after -AOSTB Active         | +    | 44   | ns    |           |

| tD20   | Output Valid after –LDSTB Inactive       | -    | 71   | ns    |           |

| tD21   | Output Valid after –LSSTB Inactive       | -    | 80   | ns    |           |

| tD22   | Bus High Impedence after -AOSTB Inactive | -    | 25   | ns    | (Note 1)  |

| t23    | Time Between -LSSTB Pulses               | 89   | _    | ns    |           |

| t24    | Time Between –LDSTB Pulses               | 89   | -    | ns    |           |

| t25    | -LSSTB Inactive to -AOSTB Active         | 36   | _    | ns    |           |

| t26    | -LDSTB Inactive to -AOSTB Active         | 17   | _    | ns    |           |

Note 1: As measured from ±0.5 V from worst case static VOH/VOL levels.

# FIGURE 6. REGISTER READ TIMING

# FIGURE 7. REGISTER WRITE TIMING

#### FIGURE 8. DIRECT STROBE CONTROL SIGNAL TIMING

# **ABSOLUTE MAXIMUM RATINGS**

**Ambient Operating**

Temperature 0°C to +70°C

Storage Temperature -40°C to +125°C

Supply Voltage to

Ground Potential -0.5 V to VDD +6.0 V

**Applied Input**

Voltage -0.5 V to VDD +0.5 V

DC Input Current ±20 mA

Lead Temperature

300°C

Stresses above those listed may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these

or any other conditions above those

indicated in this data sheet is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# DC CHARACTERISTICS: TA = 0°C to +70°C, VDD = 5 V $\pm$ 5%, VSS = 0 V, Capacitive Load = 50 pF

| Symbol | Parameter                       | Min.   | Туре     | Max.        | Units                    | Condition              |

|--------|---------------------------------|--------|----------|-------------|--------------------------|------------------------|

| VIH    | Input High Voltage              | 2.0    | _        | VDD         | ٧                        | VDD = 5.25 V           |

| VIL    | Input Low Voltage               | -0.5   | _        | 0.8         | ٧                        | VDD = 5.25 V           |

| VOH    | Output High Voltage             | 2.4    | _        |             | V                        | IOH = -8 mA            |

| VOL    | Output Low Voltage              | -      | _        | 0.4         | V                        | IOL = 8 mA             |

| IIN    | Input Leakage Current           | -10    | _        | +10         | μА                       | VIN = VDD/VSS (Note 2) |

| IINTRI | Tri-Input Leakage Current       | _<br>_ | <u>-</u> | +10<br>-300 | μ <b>Α</b><br>μ <b>Α</b> | VIN = VDD<br>VIN = VSS |

| IOZ    | High Impedence Output Leakage   | -10    | _        | +10         | μА                       | VOUT = VDD/VSS         |

| IDD    | Dynamic Current Drain @ 1.0 MHz | _<br>_ | 9.0      | 15<br>-     | mA<br>mA/MHz             | VDD = 5.25 V           |

Note 2: Does not apply to pin 16, -TRI input.

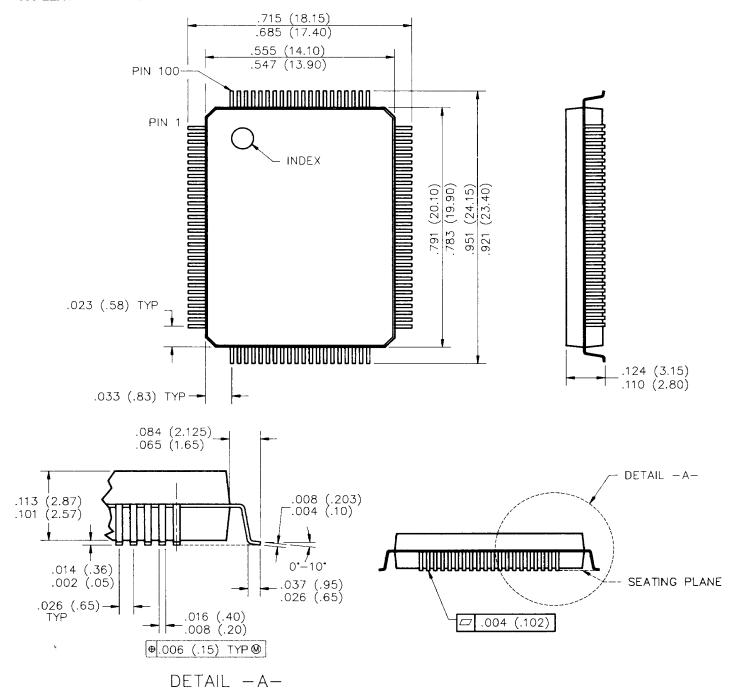

# PACKAGE OUTLINE 100-LEAD PLASTIC QUAD FLAT PACK

NOTES:

1. CONTROLLING DIMENSION IS MM.

#### VLSI CORPORATE OFFICES

CORPORATE HEADQUARTERS - ASIC AND MEMORY PRODUCTS - VLSI Technology, Inc. • 1109 McKay Drive • San Jose, CA 95131 • 408-434-3100 LOGIC AND GOVERNMENT PRODUCTS • VLSI Technology, Inc. • 8375 South River Parkway • Tempe, AZ 85284 • 602-752-8574

#### VLSI SALES OFFICES AND TECH CENTERS

#### ARIZONA

8375 South River Parkway Tempe, AZ 85284 602-752-6450 FAX 602-752-6001

#### CALIFORNIA

2235 Qume Dr San Jose, CA 95131 408-922-5200 FAX 408-943-9792 TELEX 278807 MAIL 1109 McKay Drive San Jose, CA 95131

6345 Balboa Blvd., Ste. 100 Encino, CA 91316 818-609-9981 FAX 818-609-0535

30 Corporate Park, Stes. 100-102 Irvine, CA 92714 714-250-4900 FAX 714-250-9041

FLORIDA 2200 Park Central N., Ste. 600 Pompano Beach, FL 33064 305-971-0404 FAX 305-971-2086

#### GEORGIA

2400 Pleasant Hill Rd., Ste 200 Duluth, GA 30136 404-476-8574 FAX 404-476-3790

### ILLINOIS

3100 Higgins Rd., Ste. 155 Hoffman Estates, IL 60195 708-884-0500 FAX 708-884-9394

# MARYLAND

124 Maryland Rte 3 N. Millersville, MD 21108 301-987-8777 FAX 301-987-8779

# MASSACHUSETTS

261 Bailardvale St. Wilmington, MA 01887 508-658-9501 FAX 508-658-0423

NEW JERSEY 311C Enterprise Dr. Plainsboro, NJ 08536 609-799-5700 FAX 609-799-5720

# TEXAS

850 E. Arapaho Rd., Ste. 270 Richardson, TX 75081 214-231-6716 FAX 214-669-1413

#### WASHINGTON

405 114th Ave. SE, Ste. 300 Bellevue, WA 98004 206-453-5414 FAX 206-453-5229

#### FRANCE

2, Allee des Garays F-91124 Palaiseau Cedex France 1-6447.04.79 TELEX visifr 600 759 F FAX 1-6447.04.80

# GERMANY

Rosenkavalierplatz 10 D-8000 Muenchen 81 West Germany 89-9269050 TELEX 521 4279 vlsid FAX 89-92690545

#### HONG KONG

Shui On Centre 28/12 8 Harbor Road Hong Kong 852-5-865-3755 FAX 852-5-865-3159

#### JAPAN

Shuwa-Kioicho TBR Bidg., Room 101 5-7 Kojimachi, Chiyoda-Ku Tokyo, Japan 102 81-3-239-5211 FAX 81-3-239-5215

#### UNITED KINGDOM

486-488 Midsummer Blvd. Saxon Gate West, Central Milton Keyes, MK9 2EQ United Kingdom 09 08/66 75 95 TELEX visiuk 825 135 FAX 09 08/67 00 27

#### **VLSI SALES OFFICES**

#### ALABAMA

2614 Artie St., Ste. 36 Huntsville, AL 35805 205-539-5513 FAX 205-536-8622

#### CONNECTICUT

60 Church St., Ste. 16 Yalesville, CT 06492 203-265-6698 FAX 203-265-3653

#### FLORIDA

5955 T. G. Lee Blvd., Ste. 170 Orlando, FL 32822 407-240-9603 FAX 407-240-9605

MINNESOTA 5871 Cedar Lake Rd., Ste. 9 St. Louis Park, MN 55416 612-545-1490 FAX 612-545-3489

# NORTH CAROLINA

1000 Park Forty Plaza, Ste. 300 Durham, NC 27713 919-544-1891/92 FAX 919-544-6667

### оню

4 Commerce Park Sq. 23200 Chagrin Blvd., Ste.600 Cleveland, OH 44122 216-292-8235 FAX 216-464-7609

#### OREGON

10300 S.W. Greenburg Rd., Ste. 365 Portland, OR 97223 503-244-9882 FAX 503-245-0375

#### TEXAS

9600 Great Hills Trail, Ste. 150W Austin, TX 78759 512-343-8191 FAX 512-343-2759

#### VLSI AUTHORIZED **DESIGN CENTERS**

COLORADO SIS MICROELECTRONICS, INC. Longmont, 303-776-1667

#### MAINE

QUADIC SYSTEMS, INC. South Portland, 207-871-8244

PENNSYLVANIA INTEGRATED CIRCUIT SYSTEMS, INC. King of Prussia, 215-265-8690

# EIRE AND U.K. Herts, 76-3-61222

#### FRANCE CETIA

Toulon Cedex, 9-42-12005 SOREP

#### Chateaubourg, 99-623955 NORWAY

NORKRETS AS Oslo, 47-2360677/8

# SWEDEN

NORDISK ARRAYTEKNIK AB Solna, 8-734 99 35

#### **VLSI SALES** REPRESENTATIVES

# CALIFORNIA

CENTAUR CORP Irvine, 714-261-2123 CENTAUR CORP Calabasas, 818-704-1655 CENTAUR CORP San Diego, 619-278-4950 EMERGING TECHNOLOGY San Jose, 408-263-9366

#### Orangevale, 916-988-4387 COLORADO

LUSCOMBE ENGINEERING Longmont, 303-772-3342

EMERGING TECHNOLOGY

IOWA SELTEC SALES Cedar Rapids, 319-364-7660

### MARYLAND

DELTA III Columbia, 301-730-4700

# NEW YORK bbd ELECTRONICS

Rochester, 716-425-4101

#### OREGON

MICRO SALES Beaverton, 503-645-2841

UTAH LUSCOMBE ENGINEERING Salt Lake City, 801-565-9885

# WASHINGTON

MICRO SALES Bellevue, 206-451-0568

# ISBAFI

RDT ELECTRONICS Tel Aviv, 3-483211-9

#### SINGAPORE

LIFE SUPPORT APPLICATIONS

DYNAMIC SYSTEMS PTE, LTD Singapore, 011-65-742-1986

#### **VLSI DISTRIBUTORS**

United States represented by SCHWEBER ELECTRONICS except

#### ALABAMA

Huntsville, 205-895-0480

# ARIZONA

Tempe, 602-431-0030

**CALIFORNIA**Calabasas, 818-880-9686

Irvine, 714-863-0200 Sacramento, 916-364-0222 San Diego, 619-495-0015 San Jose, 408-432-7171

#### COLORADO

Englewood, 303-799-0258

#### CONNECTICUT Oxford, 203-264-4700

#### FLORIDA

Altamonte Springs, 407-331-7555 Pompano Beach, 305-977-7511 Tampa, 813-541-5100

#### GEORGIA

Norcross, 404-449-9170 ILLINOIS

Elk Grove Village, 312-569-3650

# IOWA

Cedar Rapids, 319-373-1417

#### KANSAS Overland Park. 913-492-2921

MARYLAND

Gaithersburg, 301-596-7800 MASSACHUSETTS

#### Bedford, 617-275-5100 MICHIGAN

Livonia, 313-525-8100

#### MINNESOTA Eden Praire, 612-941-5280

MISSOURI

#### Earth City, 314-739-0526

NEW HAMPSHIRE Manchester, 603-625-2250

# **NEW JERSEY**

Fairfield, 201-227-7880

#### **NEW YORK**

Rochester, 716-424-2222 Westbury, 516-334-7474

### NORTH CAROLINA

Raleigh, 919-876-0000

#### OHIO

Beachwood, 216-464-2970 Dayton, 513-439-1800

# OKLAHOMA

Tulsa, 918-622-8003

## OREGON

ALMAC ELECTRONICS CORP. Beaverton, 503-629-8090

**PENNSYLVANIA** Horsham, 215-441-0600 Pittsburgh, 412-963-6804

#### TEXAS

Austin, 512-339-0088 Dallas, 214-247-6300 Houston, 713-784-3600

# WASHINGTON

ALMAC ELECTRONICS CORP. Bellevue, 206-643-9992 Spokane, 509-924-9500 WISCONSIN

New Berlin, 414-784-9020

#### AUSTRALIA

ENERGY CONTROL Brisbane, 61-7-376-2955

#### AUSTRIA

TRANSISTOR GmbH Vienna. 222-8294010

#### **BELGIUM AND LUXEMBURG**

Angleur, 41-674208

### DENMARK

INTERELKO Karlslunde, 3-140700

EIRE AND U.K. HAWKE COMPONENTS Sunbury-on-Thames, 1-9797799 QUARNDON ELECTRONICS

#### Derby, 332-3265 FINLAND

OY COMDAX Helsinki, 0-670277

# FRANCE

ASAP s.a. Montigny-le-Bretonneux, 1-3043-82.33

#### GERMANY

DATA MODUL GmbH Munich, 89-4180070 SPEZIAL-ELECTRONIC KG

#### Bueckeburg, 5722-2030 HONG KONG

LESTINA INTERNATIONAL, LTD Tsımshatsui, 852-3-7351736

#### ITALY

INTER-REP S.P.A Torino, 11-2165901

#### JAPAN

ASAHI GLASS CO. LTD Tokyo. 81-3-218-5854 TEKSEL COMPANY LTD Tokyo. 81-3-461-5311 TOKYO ELECTRON, LTD Tokyo, 81-423-33-8009

# KOREA

ANAM VLSI DESIGN CENTER Seoul. 82-2-553-2106 EASTERN ELECTRONICS

#### Seoul. 82-2-464-0399 NETHERLANDS

# DIODE Houten, 3403-91234

SWEDEN AND NORWAY TRACO AB

# Farsta, 8-930000

SOUTH AMERICA - BRAZIL INTERNATIONAL TRADE DEVELOPMENT

### Palo Alto, 415-856-6686

SPAIN AND PORTUGAL SEMICONDUCTORES s.a Barcelona, 3-217-23 40

# SWITZERLAND FABRIMEX AG Zurich, 1-2 5129 29

TAIWAN PRINCETON TECH CORP. Taipei, 886-2-717-1439

11/89

The information contained in this document has been carefully checked and is believed to be reliable. However, VLSI Technology, Inc., (VLSI) makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon, it. VLSI does not guarantee that the use of any information contained herein will not infringe upon the patent or other rights of third parties, and no patent or other license is implied hereby

This document does not in any way extend VLSI's warranty on any product beyond that set forth in its standard terms and conditions of sale. VLSI Technology, Inc., reserves the right to make changes in the products or specifications, or both, presented in this publication at any time and without

VLSI Technology, Inc., products are not intended for use as critical components in life support appliances, devices, or

16

systems in which the failure of a VLSI Technology product to perform could reasonably be expected to result in Please contact VLSI for the latest information concerning

@ 1990 VLSI Technology, Inc. Printed in U.S.A. 8350-195164-001 15M

VLSI Technology, Inc. • 8375 South River Parkway • Tempe, AZ 85284 • 602-752-8574