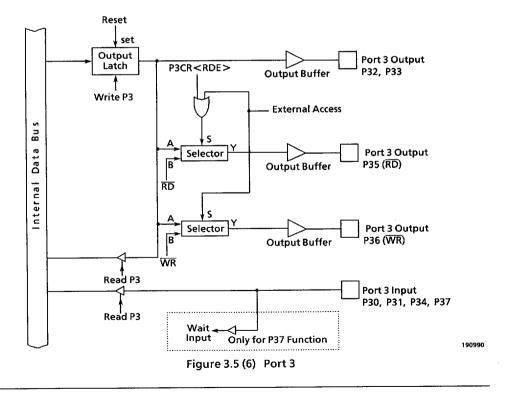

## 3.5.4 Port 3 (P30~P37)

Port 3 is an 8-bit general-purpose I/O port P3 with fixed I/O function. All bits of the output latch are initialized to "1" by resetting, and "High level" is generated to the output port.

In addition to the I/O port function, P30~P34 have the I/O function for the internal serial interface, while P35~P37 have the external memory control function. The additional functions can be selected by the control register P3CR. All bits of the control register are initialized to "0" by resetting, and the port turns to the general-purpose I/O Ports mode.

However, access of an external memory makes P35~P36 automatically function as the memory control pins ( $\overline{RD}$  and  $\overline{WR}$ ), and access of an internal memory makes them function as general-purpose I/O ports.

When an external memory is accessed, therefore, the output latch registers P35 ( $\overline{\text{RD}}$ ) and P36 ( $\overline{\text{WR}}$ ) should be kept at "1" which is the initial value after the reset.

The P3CR <RDE > of the control register is intended for a pseudostatic RAM. When set to "1", it always functions as an  $\overline{RD}$  pin. Therefore the  $\overline{RD}$  pin outputs "0" (Enable) when it is an internal memory read and internal I/O read cycle.

MCU90-40 9097249 0028997 292 **■**

|        |                    |                                                                        |        | ı                                                                                                                                                                                                                                 | Port 3 Regist   | ter                                                          |       |                                                 |                               |

|--------|--------------------|------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------|-------|-------------------------------------------------|-------------------------------|

|        |                    | 7                                                                      | 6      | 5                                                                                                                                                                                                                                 | 4               | 3                                                            | 2     | 1                                               | 0                             |

|        | oit Symbol         | P37                                                                    | P36    | P35                                                                                                                                                                                                                               | P34             | P33                                                          | P32   | P31                                             | P30                           |

| FFC6H) | Read/Write         | R                                                                      | R/W    | R/W                                                                                                                                                                                                                               | R               | R/W                                                          | R/W   | R                                               | R                             |

| P.     | Resetting<br>Value | Input                                                                  | 1      | 1                                                                                                                                                                                                                                 | Input           | 1                                                            | 1     | Input                                           | Input                         |

|        |                    |                                                                        |        | Port                                                                                                                                                                                                                              | 3 Control R     | egister                                                      |       |                                                 |                               |

|        |                    | 7                                                                      | 6      | 5                                                                                                                                                                                                                                 | 4               | 3                                                            | 2     | 1                                               | 0                             |

|        | bit Symbol         | WAITC1                                                                 | WAITC0 | RDE                                                                                                                                                                                                                               | ODE             | TXDC1                                                        | TXDC0 | RXDC1                                           | RXDC0                         |

| FC7H)  | Read/Write         | R/W                                                                    |        | R/W                                                                                                                                                                                                                               | R/W             | R/W                                                          |       | R/W                                             |                               |

| Ĩ      | Resetting<br>Value | 0                                                                      | 0      | 0                                                                                                                                                                                                                                 | 0               | 0                                                            | 0     | 0                                               | 0                             |

|        | Function           | Wait Control 00: 2state wait 01: normal wait 10: non wait 11: Not used |        | RD Control 0: RD for only external access 1: Always RD                                                                                                                                                                            | Control 0: CMOS | P33 P32 00: Out Out 01: Out TxD 10: TxD Out 11: TxD RTS/SCLK |       | P31<br>00: In<br>01: In<br>10: RxD<br>11: Not u | P30<br>In<br>RxD<br>In<br>sed |

|        |                    |                                                                        |        | See "3.8 Serial Ch  Set port P33 to open drain  O CMOS output  1 Open drain output  Set port P35 to fixed RD m  O General-purpose I/O  1 Fixed as RD Pin  WAIT control  OO 2-state wait  O1 Normal wait  10 No wait (used as an I |                 |                                                              |       | drain outpu<br>put<br>RD mode<br>e I/O port     |                               |

Figure 3.5 (7) Register for Ports 3

MCU90-41 ■ 9097249 0028998 129 ■

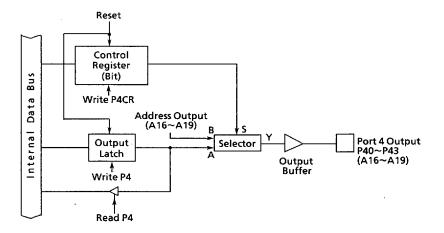

## 3.5.5 Port 4 (P40~P43)

Port 4 is a 4-bit port P4 intended only for the output. All bits of the output latch are initialized to "0" by resetting, and "0" is generated to the port.

In addition to the output port function, it works as an address bus (A16~A19). The selection of the address bus function is made by the control register P4CR. The output port or address bus function can be selected for each bit. All bits of the control register are initialized to "0" by resetting, and the port turns to the output mode.

200990

Figure 3.5 (8) Port 4