- >> 32 bit bus transceiver/register. non-inverting or inverting.

- >> High density .070 center spaced ZIP leads for maximum I/O in minimum area.

- >> Space saving vertical mounting orientation.

- >> Convenient \*in one side, out the other" broadside pin-out.

- >> TTL compatible

- >> Uses single +5V power supply

## 32 LINE TRANSCEIVER REGISTER MODULE

#### **DESCRIPTION:**

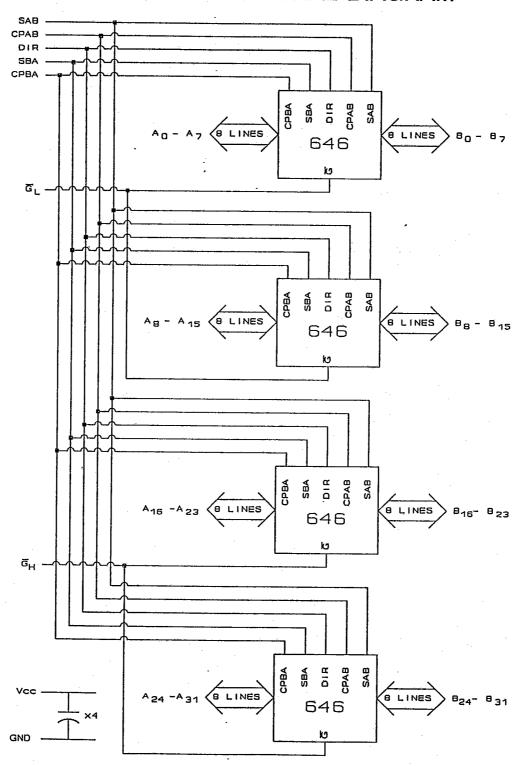

The AEPT/RZ32 is a high speed, high density 32-line transceiver/register module ideal for use with 16 or 32-bit wide address/data paths or buses. It combines the advantages of the 646 (non-inverting) or 648 (inverting) type octal transceiver/register ICs with very large data widths and a space saving configuration.

Use of the 646 type ICs provides independent registers for A and B buses, multiplexed real-time and stored data, 3state outputs, and a choice of true or inverted data paths. The vertical mounting orientation and compact I/O pin footprint of the module make it superb for projects with tight space constraints.

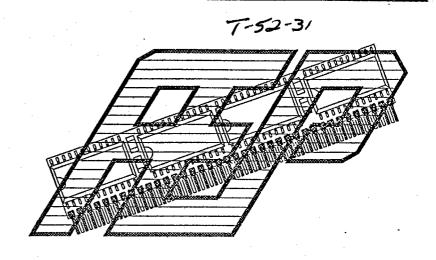

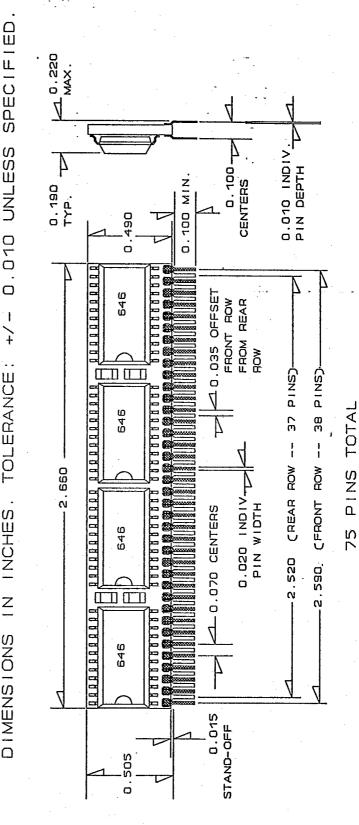

Physically the module consists of an FR4 PC material substrate mounted with four 646 or 648 type transceiver/register ICs, four 0.10 microfarad decoupling capacitors, and 75 I/O pins in a staggered ZIP package format. It can be ordered with any 646 or 648 type register made by any manufacturer producing them in a 24 pin SOP package. The module features all the 646 control lines connected in common to all four ICs except the Output Enable which is split into Glow and G-high controlling 16 lines each. Both G-low and G-high are active LOW.

Performance specifications and electrical characteristics are determined by the IC devices used. These items can vary according to the type and manufacturer of the components. The necessary information is obtained from the IC vendors' data sheets, like those attached, or from their data books.

Mechanical dimensions are 0.505 inch high by 2.66 inches long by 0.22 inch wide. The I/O pins are in two rows which are 0.1 inch apart and offset longitudinally 0.035 inch. In each row the pins are on 0.070 inch center spacing. See included specification drawing.

T-52-31

#### PART NUMBERING CHART

| T/RZ32 with non-inverting     |                  |

|-------------------------------|------------------|

| 74F646 transceiver/register   | AEPT/RZ32-F646   |

| 74FCT646 transceiver/register | AEPT/RZ32-FCT646 |

| 74LS646 transceiver/register  | AEPT/RZ32-LS646  |

| T/RZ32 with inverting         |                  |

| 74F648 transceiver/register   | AEPT/RZ32-F648   |

| 74FCT648 transceiver/register | AEPT/RZ32-FCT648 |

| 74LS648 transceiver/register  | AEPT/RZ32-LS648  |

Transceiver/Register notes:

The standard transceiver/register used is the 74FCT646A or 74PCT646A. Please contact AEP if a type that is not listed above is desired. If the pin out configuration is the same as the 74FCT646 or 74FCT648 and the desired type is available in a standard 24 pin SOP, there should be no problem using it on the module.

The "A" at the end of the standard IC number is a "High Performance" speed indicator. AEP may use the "A" version of a device even if it is not explicitly specified unless requested not to. An exact specification (type and manufacturer) of the IC device desired is recommended. Please contact AEP for assistance if needed.

#### Vendor notes:

The IC device specification information included is typical and does not limit AEP to that vendor. The actual devices used will be equivalent depending on price, availability, and customer requirements. AEP will gladly use or exclude particular manufacturers upon request. However, this might affect module price.

#### Disclaimers:

The information in this document has been carefully checked and is believed to be reliable. However, Advanced Electronic Packaging Inc. assumes no responsibility for inaccuracies. AEP also reserves the right to change products or specifications without notice.

(714) 969-1150

FAX: (714) 536-0936

O S S S S

(M) TOLERANCE - NOTEN DIMENSIONS

3

## T-52-31

# 32 LINE TRANSCEIVER/REGISTER MODULE PIN CONFIGURATION (TOP VIEW)

|                       | •                                            |                      |

|-----------------------|----------------------------------------------|----------------------|

|                       | PIN #s                                       |                      |

| A INDUTE /P OUTDUTE   | $A_1 - 1$                                    |                      |

| A INPUTS /B OUTPUTS   | 2 - B <sub>1</sub>                           | B INPUTS /A OUTPUTS  |

|                       | $A_2 - 3$ $4 - B_2$                          | - ·                  |

|                       | $A_2 - 5$                                    |                      |

|                       | $A_4 - 7 \qquad \qquad 6 - B_3$              |                      |

| _                     | ` 8 B₄                                       |                      |

| • .                   | $A_5 - 9 $ $10 - B_5$                        |                      |

|                       | Aa 11                                        | •                    |

|                       | A <sub>7</sub> - 13                          |                      |

|                       | 14 B <sub>7</sub>                            |                      |

|                       | A <sub>8</sub> - 15<br>16 - B <sub>8</sub>   |                      |

| OUTPUT ENABLELOW      | G <sub>L</sub> - 17 18 - SAB                 | TRANSMIT/RECEIVE A-B |

| CLOCK PULSE A-B       | CPAB 19                                      |                      |

| A INPUTS /B OUTPUTS   | 20 - GND<br>A <sub>9</sub> - 21              | GROUND               |

| 2.0,2 33 3.3          | 22 B₀                                        | B INPUTS /A OUTPUTS  |

|                       | A <sub>10</sub> - 23 24 - B <sub>10</sub>    |                      |

|                       | A <sub>11</sub> 25<br>26 B <sub>11</sub>     |                      |

|                       | A.a. = 27                                    |                      |

|                       | A <sub>13</sub> 29 28 B <sub>12</sub>        |                      |

|                       | 30 ↔ 8₄₀                                     |                      |

| ÷.                    | $A_{14} - 31$ $32 - B_{14}$                  |                      |

|                       | A 33                                         |                      |

|                       | A <sub>16</sub> 35 34 B <sub>15</sub>        |                      |

| POWER                 | Vcc - 37                                     |                      |

|                       | 38 – Vcc                                     | POWER                |

| A INPUTS /B OUTPUTS   | A <sub>17</sub> - 39<br>40 - B <sub>17</sub> | B INPUTS /A OUTPUTS  |

|                       | A.a - 41                                     |                      |

|                       | A <sub>19</sub> 43                           |                      |

|                       | 44 B <sub>10</sub>                           |                      |

|                       | A <sub>20</sub> 45<br>46 B <sub>20</sub>     |                      |

|                       | A <sub>21</sub> - 47<br>48 - B <sub>21</sub> |                      |

|                       | Ann = 49                                     |                      |

|                       | 50 - B <sub>22</sub><br>A <sub>22</sub> - 51 |                      |

|                       | 52 Baa                                       |                      |

|                       | A <sub>24</sub> - 53 54 - B <sub>24</sub>    |                      |

| GROUND                | GND 55                                       | CLOCK BUILDE B A     |

| OUTPUT ENABLEHIGH     | 56 - CPBA<br>G <sub>H</sub> - 57             | CLOCK PULSE B-A      |

| A INPUTS /B OUTPUTS   | 58 - SBA<br>A <sub>25</sub> - 59             | TRANSMIT/RECEIVE B-A |

| X 114 010 /B 0011 010 | 60 B <sub>25</sub>                           | B INPUTS /A OUTPUTS  |

|                       | A <sub>26</sub> 61 62 B <sub>26</sub>        |                      |

|                       | A 63                                         |                      |

| •                     | A <sub>28</sub> - 65 64 - B <sub>27</sub>    |                      |

| <del>-</del>          | A <sub>29</sub> - 67                         |                      |

|                       | 68 ⊶ B <sub>20</sub>                         |                      |

|                       | A <sub>30</sub> 69 70 B <sub>30</sub>        |                      |

|                       | Aa. = 71                                     |                      |

|                       | A <sub></sub> 73                             | •                    |

| OLITOLIT DIDECTION    | 74 - R.                                      |                      |

| OUTPUT DIRECTION      | DIR 75                                       |                      |

Note: OUTPUT ENABLEs are active LOW.

### August 1, 1990

## 32 LINE TRANSCEIVER/REGISTER MODULE FUNCTIONAL DIAGRAM