# **PI74ALVCH16269**

with 3-State Outputs

### **Product Features**

- PI74ALVCH16269 is designed for low voltage operation

- $V_{CC} = 2.3 \text{V to } 3.6 \text{V}$

- Hysteresis on all inputs

- Typical V<sub>OLP</sub> (Output Ground Bounce) < 0.8V at  $V_{CC} = 3.3V$ ,  $T_A = 25$ °C

- Typical V<sub>OHV</sub> (Output V<sub>OH</sub> Undershoot) < 2.0 V at  $V_{CC} = 3.3 \text{V}$ ,  $T_A = 25 ^{\circ}\text{C}$

- Bus Hold retains last active bus state during 3-State, eliminating the need for external pullup resistors

- Industrial operation at -40°C to +85°C

- Packages available:

- -56-pin 240 mil wide plastic TSSOP (A)

- -56-pin 300 mil wide plastic SSOP (V)

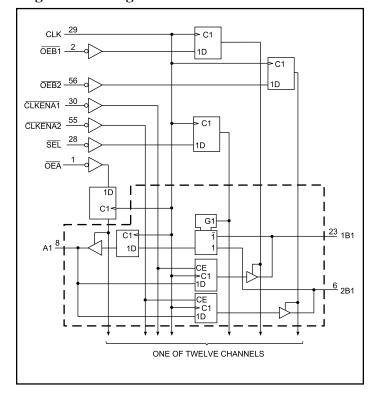

# Logic Block Diagram

## **Product Description**

Pericom Semiconductor's PI74ALVCH series of logic circuits are produced using the Company's advanced 0.5 micron CMOS technology, achieving industry leading speed.

12-Bit to 24-Bit Registered Bus Exchanger

The PI7ALVCH16269 is used in applications in which two separate ports must be multiplexed onto, or demultiplexed from, a single port. It is particularly suitable as an interface between synchronous DRAM's and high-speed microprocessors.

Data is stored on the internal B-port registers on the low-to-high transition of the clock (CLK) input when the appropriate clock-enable (CLKENA) inputs are low. Proper control of these inputs allows two sequential 12-bit words to be presented as a 24-bit word on the B-port. For data transfer in the B-to-A direction, a single storage register is provided. The select (SEL) line selects 1B or 2B data for the A outputs. The register on the A output permits the fastest possible data transfer, thus extending the period during which the data is valid on the bus. The control terminals are registered so that all transactions are synchronous with CLK. Data flow is controlled by the active-low output enables  $(\overline{OEA}, \overline{OEB1}, \text{ and } \overline{OEB2}).$

To ensure the high-impedance state during power up or power down, a clock pulse should be applied as soon as possible and  $\overline{OE}$ should be tied to V<sub>CC</sub> through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver. Because OE is being routed through a register, the active state of the outputs cannot be determined prior to the arrival of the first clock pulse.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

PS8379 04/16/99

1

### **Product Pin Description**

| Pin Name | Description                      |

|----------|----------------------------------|

| ŌĒ       | Output Enable Input (Active LOW) |

| CLK      | Clock                            |

| SEL      | Select (Active Low)              |

| CLKEN    | Clock Enable (Active Low)        |

| A,1B,2B  | 3-State Outputs                  |

| GND      | Ground                           |

| VCC      | Power                            |

### **Truth Tables**<sup>(1)</sup>

|            | Inputs | Out | puts   |        |

|------------|--------|-----|--------|--------|

| CLK        | ŌĒĀ    | ŌEB | A      | 1B,2B  |

| 1          | Н      | Н   | Z      | Z      |

| $\uparrow$ | Н      | L   | Z      | Active |

| $\uparrow$ | L      | Н   | Active | Z      |

| 1          | L      | L   | Active | Active |

# **Product Pin Configuration**

| ŌĒĀ  | 1    |               | 56 | OEB2    |

|------|------|---------------|----|---------|

| OEB1 | 2    |               | 55 | CLKENA2 |

| 2B3  | □ 3  |               | 54 | 2B4     |

| GND  | □ 4  |               | 53 | GND     |

| 2B2  | □ 5  |               | 52 | 2B5     |

| 2B1  | □ 6  |               | 51 | 2B6     |

| Vcc  | 7    |               | 50 | VCC     |

| A1   | 8 🛚  |               | 49 | 2B7     |

| A2   | □ 9  |               | 48 | 2B8     |

| A3   | □ 10 |               | 47 | 2B9     |

| GND  | □ 11 |               | 46 | GND     |

| A4   | [ 12 | <b>56-PIN</b> | 45 | 2B10    |

| A5   | □ 13 | A56           | 44 | 2B11    |

| A6   | □ 14 | V56           | 43 | 2B12    |

| A7   | □ 15 |               | 42 | 1B12    |

| A8   | □ 16 |               | 41 | 1B11    |

| A9   | 17   |               | 40 | 1B10    |

| GND  | □ 18 |               | 39 | GND     |

| A10  | 19   |               | 38 | 1B9     |

| A11  | □ 20 |               | 37 | 1B8     |

| A12  | 21   |               | 36 | 1B7     |

| Vcc  | 22   |               | 35 | VCC     |

| 1B1  | □ 23 |               | 34 | 1B6     |

| 1B2  | 24   |               | 33 | 1B5     |

| GND  | □ 25 |               | 32 | GND     |

| 1B3  | □ 26 |               | 31 | 1B4     |

| NC   | □ 27 |               | 30 | CLKENA1 |

| SEL  | □ 28 |               | 29 | CLK     |

|      |      |               |    |         |

|      |      |               |    |         |

# A to B STORAGE $\overline{(OEB} = L)$

|         | OUT     | PUTS     |   |              |              |

|---------|---------|----------|---|--------------|--------------|

| CLKENA1 | CLKENA2 | CLK      | A | 1B           | 2B           |

| Н       | Н       | X        | X | $1B_0^{(2)}$ | $2B_0^{(2)}$ |

| L       | X       | <b>↑</b> | L | L            | X            |

| L       | X       | 1        | Н | Н            | X            |

| X       | L       | 1        | L | X            | L            |

| X       | L       | 1        | Н | X            | Н            |

# B to A STORAGE ( $\overline{OEA} = L$ )

|          | Outputs |    |    |                   |

|----------|---------|----|----|-------------------|

| CLK      | SEL     | 1B | 2B | A                 |

| X        | Н       | X  | X  | A0 <sup>(2)</sup> |

| X        | L       | X  | X  | A0 <sup>(2)</sup> |

| 1        | Н       | L  | X  | L                 |

| 1        | Н       | Н  | X  | Н                 |

| 1        | L       | X  | L  | L                 |

| <b>↑</b> | L       | X  | Н  | Н                 |

#### Notes:

2

- 1. H = High Signal Level

- L = Low Signal Level

- X = Irrelevant

- Z = High Impedance

- $\uparrow$  = Transition, Low to High

- 2. Output level before indicated steady state input conditions established.

PS8379 04/16/99

### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| <u> </u>                                                     |

|--------------------------------------------------------------|

| Storage Temperature65°C to +150°C                            |

| Supply Voltage Range, V <sub>CC</sub> 0.5V to 4.6V           |

| Input Voltage Range, V <sub>I</sub> : Except                 |

| I/O ports <sup>(1)</sup> 0.5V to 4.6V                        |

| I/O ports <sup>(1,2)</sup> 0.5V to V <sub>CC</sub> + 0.5V    |

| Output Voltage Range, $V_0^{(1,2)}$ 0.5V to $V_{CC}$ + 0.5V  |

| Input Clamp current, $I_{IK}$ ( $V_I < 0$ )                  |

| Output Clamp current, $I_{OK}(V_O < 0)$                      |

| Continous Output Current, I <sub>O</sub> ±50mA               |

| Continuos Current through each V <sub>CC</sub> or GND ±100mA |

| Maximum Power Dissipation:                                   |

| A package1W                                                  |

| V package                                                    |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Notes:**

- 1. The input and output negative-voltage ratings maybe exceeded if the input and outputclamp-current ratings are observed.

- 2. This value is limited to 4.6V maximum.

# **DC Electrical Characteristics** (Over the Operating Range, TA = -40°C to +85°C, $VCC = 3.3V \pm 10$ %)

| Parameters              | Description                  | Test Conditions                          | Min. | Тур. | Max.            | Units |  |

|-------------------------|------------------------------|------------------------------------------|------|------|-----------------|-------|--|

| $V_{CC}$                | Supply Voltage               |                                          | 2.3  |      | 3.6             |       |  |

| <b>V</b> . (1)          | Innut IIICII Voltoco         | $V_{CC} = 2.3 \text{V to } 2.7 \text{V}$ | 1.7  |      |                 |       |  |

| $V_{IH}^{(1)}$          | Input HIGH Voltage           | $V_{CC} = 2.7V \text{ to } 3.6V$         | 2.0  |      |                 |       |  |

| <b>V</b> . (1)          | Innut I OW Voltogo           | $V_{CC} = 2.3 V \text{ to } 2.7 V$       |      |      | 0.7             | V     |  |

| $V_{\mathrm{IL}}^{(1)}$ | Input LOW Voltage            | $V_{CC} = 2.7V \text{ to } 3.6V$         |      |      | 0.8             |       |  |

| $V_{IN}^{(1)}$          | Input Voltage                |                                          | 0    |      | V <sub>CC</sub> |       |  |

| V <sub>OUT</sub> (1)    | Output Voltage               |                                          | 0    |      | V <sub>CC</sub> |       |  |

|                         |                              | $V_{CC} = 2.3V$                          |      |      | -12             |       |  |

| $I_{OH}^{(1)}$          | HIGH-level<br>Output Current | $V_{\rm CC} = 2.7 V$                     |      |      | -12             |       |  |

|                         |                              | $V_{CC} = 3.0V$                          |      |      | -24             |       |  |

|                         |                              | $V_{CC} = 2.3V$                          |      |      | 12              | mA    |  |

| $I_{\rm OL}^{(1)}$      | LOW-level<br>Output Current  | $V_{\rm CC} = 2.7 V$                     |      |      | 12              |       |  |

|                         |                              | $V_{CC} = 3.0V$                          |      |      | 24              |       |  |

| $T_{A}$                 | Operating Fre                | Operating Free-Air Temperature           |      |      | 85              | °C    |  |

| $At/\Delta_{ m V}$      | Input Transitio              | n Rise or Fall Rate                      |      |      | 10              | ns/V  |  |

3

### Note:

1. Unused control inputs must be held HIGH or LOW to prevent them from floating.

### **DC Electrical Characteristics-Continued** (Over the Operating Range, $T_A = -40$ °C to +85°C, $V_{CC} = 3.3 \text{V} \pm 10\%$

| Parameters                           | Test Conditions                                               | V <sub>CC</sub> <sup>(1)</sup> | Min.                 | Typ.(2) | Max. | Units |

|--------------------------------------|---------------------------------------------------------------|--------------------------------|----------------------|---------|------|-------|

|                                      | $I_{OH} = -100 \mu A$                                         | Min. to Max.                   | V <sub>CC</sub> -0.2 |         |      |       |

|                                      | $I_{OH} = -6 \text{mA}$                                       | 2.3V                           | 2.0                  |         |      |       |

| $ m V_{OH}$                          |                                                               | 2.3V                           | 1.7                  |         |      |       |

| V OH                                 | $I_{OH} = -12mA$                                              | 2.7V                           | 2.2                  |         |      |       |

|                                      |                                                               | 3.0V                           | 2.4                  |         |      |       |

|                                      | $I_{OH} = -24 \text{mA}$                                      | 3.0V                           | 2.0                  |         |      | V     |

|                                      | $I_{OL} = 100 \mu A$                                          | Min. to Max.                   |                      |         | 0.2  |       |

|                                      | $I_{OL} = 6mA$                                                | 2.3V                           |                      |         | 0.4  |       |

| $V_{OL}$                             | I = 12mA                                                      | 2.3V                           |                      |         | 0.7  |       |

|                                      | $I_{OL} = 12$ mA                                              | 2.7V                           |                      |         | 0.4  |       |

|                                      | $I_{OL} = 24 \text{mA}$                                       | 3.0V                           |                      |         | 0.55 |       |

| $I_{\rm I}$                          | $V_I = V_{CC}$ or GND                                         | 3.6V                           |                      |         | ±5   |       |

|                                      | $V_I = 0.7V$                                                  | 2.27/                          | 45                   |         |      |       |

|                                      | $V_I = 1.7V$                                                  | 2.3V                           | -45                  |         |      |       |

| I <sub>I</sub> (Hold) <sup>(3)</sup> | $V_I = 0.8V$                                                  | 2.01/                          | 75                   |         |      |       |

|                                      | $V_I = 2.0V$                                                  | 3.0V                           | -75                  |         |      | ]     |

|                                      | $V_I = 0$ to 3.6V                                             | 3.6V                           |                      |         | ±500 | μΑ    |

| $I_{OZ}^{(4)}$                       | $V_O = V_{CC}$ or GND                                         | 3.6V                           |                      |         | ±10  |       |

| $I_{CC}$                             | $V_I = V_{CC}$ or GND, $I_O = 0$                              | 3.6V                           |                      |         | 40   | 1     |

| $\Delta I_{CC}$                      | One input at $V_{CC}$ - 0.6V, Other inputs at $V_{CC}$ or GND | 3V to 3.6V                     |                      |         | 750  |       |

| C <sub>I</sub> Control Inputs        | $V_I = V_{CC}$ or GND                                         | 3.3V                           |                      | 3.5     |      | "E    |

| C <sub>IO</sub> A or B Ports         | $V_O = V_{CC}$ or GND                                         | 3.3V                           |                      | 8.5     |      | pF    |

### **Notes:**

1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type.

4

- 2. Typical values are at  $V_{CC} = 3.3V$ , +25°C ambient and maximum loading.

- 3. Bus hold maximum dynamic current required to switch the input from one state to another

- 4. For I/O ports, the I<sub>OZ</sub> includes the input leakage current.

# **Timing Requirements over Operating Range**

|                  |                                    |                                 |      | $V_{\rm CC} = 2.5 \text{V} \pm 0.2 \text{V}$ |      | 2.7V | $V_{\rm CC} = 3.3 \mathrm{V} \pm 0.3 \mathrm{V}$ |      |       |  |

|------------------|------------------------------------|---------------------------------|------|----------------------------------------------|------|------|--------------------------------------------------|------|-------|--|

| Parameters       |                                    | Description                     | Min. | Max.                                         | Min. | Max. | Min.                                             | Max. | Units |  |

| $f_{CLOCK}$      | Clock frequency                    |                                 |      | 135                                          |      | 135  |                                                  | 135  | MHz   |  |

| $t_{\mathrm{W}}$ | Pulse duration, CLK<br>High or Low |                                 | 3.3  |                                              | 3.3  |      | 3.3                                              |      |       |  |

|                  |                                    | A data before CLK↑              | 2.0  |                                              | 2.0  |      | 1.7                                              |      |       |  |

|                  |                                    | B data before CLK↑              | 2.2  |                                              | 2.1  |      | 1.8                                              |      |       |  |

| $t_{ m SU}$      | Setup time                         | SEL before CLK↑                 | 1.6  |                                              | 1.6  |      | 1.3                                              |      |       |  |

| *50              | Stup time                          | CLKENA1 or CLKENA2 before CLK ↑ | 1.0  |                                              | 1.2  |      | 0.9                                              |      |       |  |

|                  |                                    | OE data before CLK ↑            | 1.5  |                                              | 1.6  |      | 1.3                                              |      | ns    |  |

|                  |                                    | A data after CLK↑               | 0.7  |                                              | 0.6  |      | 0.6                                              |      |       |  |

|                  |                                    | B data after CLK↑               | 0.7  |                                              | 0.6  |      | 1.6                                              |      |       |  |

| t <sub>H</sub>   | Hold time                          | SEL after CLK↑                  | 1.1  |                                              | 0.7  |      | 0.7                                              |      |       |  |

| vn               | Tiold talle                        | CLKENA1 or CLKENA2 after CLK ↑  | 1.0  |                                              | 0.8  |      | 1.1                                              |      |       |  |

|                  |                                    | OE after CLK↑                   | 0.8  |                                              | 0.8  |      | 0.8                                              |      |       |  |

# Switching Characteristics over Operating Range $^{(1)}$

| Parameters       |         |          |                     | $V_{CC} = 2.5V \pm 0.2V$ |         | $V_{\rm CC} = 2.7 V$ |                     | $V_{CC} = 3.3V \pm 0.3V$ |    | Units |

|------------------|---------|----------|---------------------|--------------------------|---------|----------------------|---------------------|--------------------------|----|-------|

|                  | (INPUT) | (OUTPUT) | Min. <sup>(2)</sup> | Max.                     | Min.(2) | Max.                 | Min. <sup>(2)</sup> | Max.                     |    |       |

| $f_{MAX}$        |         |          | 135                 |                          | 135     |                      | 135                 |                          |    |       |

| <b>t</b>         |         | В        | 1.0                 | 8.2                      |         | 7.3                  | 1.0                 | 6.2                      |    |       |

| $t_{ m PD}$      |         | A        | 1.0                 | 6.4                      |         | 5.8                  | 1.0                 | 5.0                      |    |       |

| t                | CLK     | В        | 1.0                 | 7.9                      |         | 6.7                  | 1.0                 | 6.1                      | ns |       |

| $t_{\rm EN}$     | CLK     | A        | 1.0                 | 7.6                      |         | 6.2                  | 1.0                 | 5.9                      |    |       |

| t <sub>DIS</sub> |         | В        | 1.0                 | 8.1                      |         | 6.9                  | 1.0                 | 6.1                      |    |       |

|                  |         | A        | 1.0                 | 7.5                      |         | 6.8                  | 1.0                 | 5.6                      |    |       |

#### **Notes:**

- 1. Unused control inputs must be held HIGH or LOW to prevent them from floating.

- 2. Minimum limits are guaranteed but not tested on Propagation Delays.

# Operating Characteristics, $T_A = 25^{\circ}C$

|                                                      |                  | Test        | $V_{CC} = 2.5V \pm 0.2V$ | $V_{CC} = 3.3V \pm 0.3V$ |       |

|------------------------------------------------------|------------------|-------------|--------------------------|--------------------------|-------|

| Parameter                                            |                  | Conditions  | Тур                      | oical                    | Units |

| C <sub>PD</sub> Power Dissipation<br>Capacitance per | Outputs Enabled  | $C_L=0pF$ , | 87                       | 120                      | nE    |

| Exchanger                                            | Outputs Disabled | F = 10  MHz | 80.5                     | 118                      | pF    |

### **Pericom Semiconductor Corporation**

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com