## APRIL 1986 PRELIMINARY

# CA82C12

### 8-BIT INPUT/OUTPUT PORT

- High performance pin and function compatible replacement for the industry standard 8212

- TTL compatible input/output voltages

- Low power consumption

- 8-bit parallel data register and buffer

- Interrupt generation logic using a service request flipflop

- Tri-state outputs

- · Asynchronous register clear

- Ideal for reducing parts count in microcomputer system applications

- Manufactured using proven CMOS process technology

The CA82C12 Input/Output Port combines an 8-bit data latch and tri-state output buffers, with device selection and control logic. In addition, interrupt generation and control logic is provided for applications which require interfacing to microprocessor systems.

The CA82C12 is manufactured using proven CMOS process technology to produce a solid, reliable product. It is supplied in a selection of packages that are pin compatible with the industry standard 8212.

Overall, the CA82C12 is versatile component which can be used to implement many of the peripheral and input/output functions within high speed microcomputer systems, including latches, bus drivers, gated buffers and multiplexors. Featuring TTL compatibility and particularly low power consumption, this chip is ideally suited to portable or standby type applications.

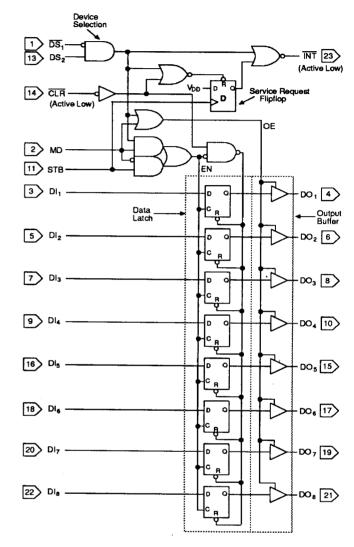

Figure 1: CA82C12 LOGIC DIAGRAM

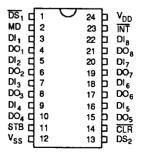

Figure 2: PIN CONFIGURATION

#### **FUNCTIONAL DESCRIPTION**

The elements of the CA82C12 are shown in the logic diagram of Figure 1, with pin configuration and pin descriptions given in Figure 2 and Table 1 respectively. Note that three major functional areas comprise the chip: the data latch, data output buffer and control and interrupt logic.

#### **Data Latch**

Eight "D"-type latches, controlled by the "EN" signal, comprise the data latch. When EN is high, the output of each latch follows the corresponding data input ( $DI_{1-8}$ ). The data at  $DO_{1-8}$  is latched when EN goes low.

The latched data is cleared by the active low  $\overline{\text{CLR}}$  signal, if EN is low. If EN is high,  $\overline{\text{CLR}}$  will be ignored since the data must be in a latched state before the data latches

Table 1: PIN DESCRIPTIONS

| Symbol                            | Pin(s)<br>DIP Package          | Туре | Name and Function                                                                                                                                                                                                                                                                   |

|-----------------------------------|--------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLR                               | 14                             | 1    | Clear: This active low signal is used to reset the data latch and reset the D flipflop. It has NO effect on the output buffer. CLR overrides STB when generating an interrupt (INT).                                                                                                |

| DI <sub>1</sub> - DI <sub>8</sub> | 3, 5, 7, 9, 16,<br>18, 20, 22  | ı    | Data In: An 8-bit data field into the CA82C12. It can be connected directly to the system bus.                                                                                                                                                                                      |

| DO <sub>1</sub> - DO <sub>8</sub> | 4, 6, 8, 10, 15,<br>17, 19, 21 | 0    | Data Out: Tri-state output lines which either display the contents of the data buffer, or are disabled by OE set low, (high impedance state)                                                                                                                                        |

| DS₁•DS₂                           | 1,13                           | 1    | <b>Device Select:</b> The AND function of these two inputs is used for device selection. When $(\overline{DS_1} \cdot DS_2)$ is high, the CA82C12 is selected, the output buffer is enabled, and the D flipflop is asynchronously reset. Note that $\overline{DS_1}$ is active low. |

| INT                               | 23                             | 0    | Interrupt: This active low signal is generated by either a device select, or by a strobe signal if CLR is high.                                                                                                                                                                     |

| MD                                | 2                              | ı    | Mode: This signal is used to determine both the state of the output buffer and the source of the data latch enable clock (EN). The CA82C12 is in input mode when MD is low, and in output mode when MD is high.                                                                     |

| STB                               | 11                             | I    | Strobe: This input is used as the data latch enable clock when the CA82C12 is in input mode (MD is low), and to synchronously set the D flipflop.                                                                                                                                   |

| V <sub>DD</sub>                   | 24                             | -    | Power: 5.0v ± 10% VDC Supply                                                                                                                                                                                                                                                        |

| V <sub>SS</sub>                   | 12                             | -    | Ground: 0v                                                                                                                                                                                                                                                                          |

can be cleared (reset). If the data is not latched (EN is high) when CLR goes low, then the outputs of the data latch (Q) will continue to follow their corresponding data inputs, overriding the reset signal.

#### **Data Output Buffer**

The output of each data latch (Q) is connected to a tristate, non-inverting output buffer. Each of these buffers is controlled through a common control line, "output enable" (OE). When OE is high, the data output buffer is enabled, and data can be transferred from the data latch outputs (Q). When OE is low, the data output buffers are disabled, forcing the buffer outputs into a high impedance state. Thus, the CA82C12 can be connected directly onto a microprocessor bi-directional data bus.

Table 2 shows the data output buffer states under different control signal conditions.

Table 2: CONTROL LOGIC

| STB | MD | DS <sub>1</sub> • DS <sub>2</sub> | Data Out Equals           |

|-----|----|-----------------------------------|---------------------------|

| 0   | 0  | 0                                 | Disabled (high impedance) |

| 1   | 0  | 0                                 | Disabled (high impedance) |

| 0   | 1  | 0                                 | Data Latch                |

| . 1 | 1  | 0                                 | Data Latch                |

| 0   | 0  | 1                                 | Data Latch                |

| 1   | 0  | 1                                 | Data In                   |

| 0   | 1  | 1                                 | Data In                   |

| 1   | 1  | 1                                 | Data In                   |

Note that  $\overline{CLR}$  resets both the data latch and the D flipflop, without affecting the output buffer.

#### Control and Interrupt Logic

The CA82C12 has four control signal inputs  $(\overline{DS}_1, DS_2, MD)$  and STB), and an interrupt output (INT). The inputs are used to control device selection, data latching, output buffer state and to generate interrupts.

**Device Select** ( $\overline{DS_1}$ ,  $DS_2$ ): The AND function of these  $\underline{two}$  signals is used to select the device. That is, when  $\overline{DS_1} \cdot DS_2$  is high, the device is selected. When selected, the output buffer is enabled (OE is high), and the service request flipflop "D" is cleared (reset) asynchronously.

**Mode (MD):** This input is used to generate the data buffer output enable signal (OE), and to determine the source of the data latch enable signal (EN).

When MD is high, the device is in "output mode," the data output buffers are enabled (OE is high), and the data latch enable signal (EN) is generated by the device select (DS<sub>1</sub> • DS<sub>2</sub>).

Table 3: INTERRUPT SIGNAL LOGIC

| CLR | DS <sub>1</sub> • DS <sub>2</sub> | STB  | Q1 | ĪNT |

|-----|-----------------------------------|------|----|-----|

| 0   | 0                                 | 0    | 0  | 1   |

| 0   | 0                                 | H->L | 0  | 1   |

| 0   | 1                                 | 0    | 0  | 0   |

| 1   | 0                                 | 0    | 0  | 1   |

| 1   | 0                                 | H>L  | 1  | 0   |

| 1   | 1                                 | 0    | 0  | 0   |

| 1   | 1                                 | H->L | 0  | 0   |

Note: 1. Internal D flipflop signal

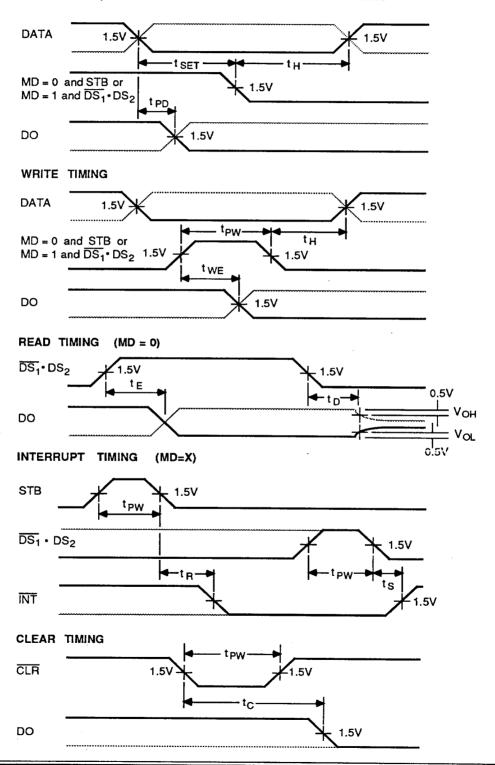

Figure 3: TIMING DIAGRAMS

DATA SETUP, HOLD and PROPORTIONAL DELAY TIMING

Table 4: AC CHARACTERISTICS

$T_A = 0$  °C to +70 °C,  $V_{DD} = +5v \pm 10\%$ ,  $C_L = 50$  pF,  $R_L = 10$ K

| 0 1              | Parameter                    | Limits |     |       |

|------------------|------------------------------|--------|-----|-------|

| Symbol           |                              | Min    | Max | Units |

| tc               | Clear to Output Delay        | -      | 45  | ns    |

| t <sub>D</sub>   | Output Disable Time          | -      | 45  | ns    |

| t⊨               | Output Enable Time           | -      | 30  | ns    |

| t <sub>H</sub>   | Data Hold Time               | 10     | -   | ns    |

| t <sub>PD</sub>  | Data to Output Delay         | -      | 30  | ns    |

| tpW              | Pulse Width                  | 25     | -   | ns    |

| t <sub>R</sub>   | Reset to Output Delay        | -      | 40  | ns    |

| t <sub>S</sub>   | Set to Output Delay          | -      | 30  | ns    |

| <sup>t</sup> seT | Data Set Up Time             | 15     | -   | ns    |

| tWE              | Write Enable to Output Delay | -      | 40  | ns    |

#### Table 5: DC CHARACTERISTICS

$T_A$  = -40 °C to +85 °C,  $V_{DD}$  = +5v  $\pm$  10%

| Symbol          | Parameter                    | Test Conditions                             | Limits |      |       |

|-----------------|------------------------------|---------------------------------------------|--------|------|-------|

|                 |                              |                                             | Min    | Max  | Units |

| l <sub>DD</sub> | Power Supply Current         | Active                                      |        | 1    | mA    |

| I <sub>IL</sub> | Input Leakage Current        | 0V ≤ V <sub>IN</sub> ≤ V <sub>DD</sub>      | -10    | 10   | μА    |

| I <sub>SC</sub> | Short Circuit Output Current | V <sub>OUT</sub> = 0v, V <sub>DD</sub> = 5v | -15    | -75  | mA    |

| VIL             | Input Low Voltage            |                                             |        | 0.85 | V     |

| V <sub>IH</sub> | Input High Voltage           |                                             | 2.0    |      | V     |

| V <sub>OL</sub> | Output Low Voltage           | I <sub>OL</sub> = 4mA                       |        | 0.4  | V     |

| $V_{OH}$        | Output High Voltage          | I <sub>OH</sub> = -4mA                      | 3.7    |      | ٧     |

Table 6: ABSOLUTE MAXIMUM RATINGS

| Temperature Under Bias Plastic  | 0 °C to +70 °C     |

|---------------------------------|--------------------|

| Storage Temperature             | -65 °C to +160 °C  |

| All Input Voltages              | -1.0 to +5.5 Volts |

| All Output or Supply Voltages . | -0.5 to +7 Volts   |

| Output Currents                 | 100mA              |

Stresses beyond those listed above may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.