# **COM 9004**

# IBM 3274/3276 Compatible COAX Receiver/Transmitter

# **FEATURES**

- Conforms to the IBM 3270 Interface Display System Standard

- ☐ Transmits and Receives Manchester II Code

- ☐ Detects and Generates Line Quiesce, Code Violation, Sync, Parity, and Ending Sequence (Mini Code Violation)

- ☐ Multi Byte or Single Byte Transfers

- ☐ Double Buffer Receiver and Transmitter

- ☐ Separate Data and Stratus Select

- ☐ Operates at 2.3587 /IHz

- TTL Compatible Inputs and Outputs

- COPLAMOS® n-Channel Silicon Gate Technology

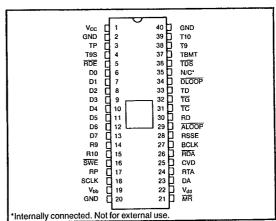

### PIN CONFIGURATION

### **GENERAL DESCRIPTION**

The COM 9004 is an MOS/LSI circuit which may be used to facilitate high speed data transmission. The COM 9004 is fabricated using SMC's patented COPLAMOS® technology and may be used to implement an interface between IBM 3274/3276 compatible control units and 3278/3287/ 3289 compatible terminal units. The receiver and transmitter sections of the COM 9004 are separate and may be used independently of each other.

The COM 9004 generates and detects the line quiesce, code violation, parity, and mini code violation bit patterns.

The on-chip parity logic is capable of generating and checking either even or odd parity for the entire 10 bit data word. In addition, parity may be generated for the least sig-nificant 8 bits of the data word (this parity bit would replace the ninth data bit).

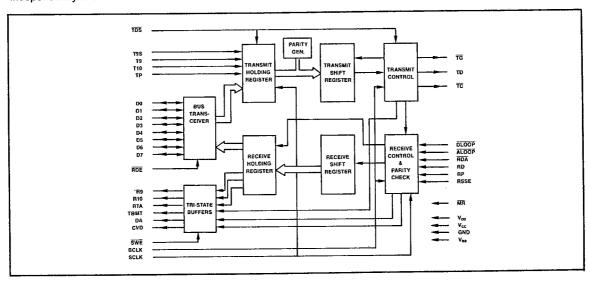

### **ORGANIZATION**

transmit circuitry. It also generates the Line Quiesce, Code Violation, sync bits and Mini Code Violation patterns.

The COM 9004 is organized into 9 major sections. Communication between each section is achieved via internal data and control busses.

### **Transmitter Holding Register**

The transmit holding register is a 12 bit latch. This latch is loaded with the transmit data and parity generation information from the system bus.

#### **Tri-State Buffers**

These buffers allow gating of the COM 9004's status word onto the system data bus.

### **Bus Transceiver**

The bus transceiver allows bi-directional data transfer between the system data bus and the transmit and receive holding registers.

### **Parity Generator**

This logic determines and generates the correct parity for the data in the transmitter holding register.

### **Transmitter Control**

This logic generates signals required to enable external

# Transmitter Shift Register

The transmitter shift register is an 11 bit parallel to serial shift register. It accepts data from the transmitter holding register and the parity generation logic and converts it into serial form for transmission.

### Receive Control/Parity Check

This logic checks the received character for the specified parity and ensures that no Transmit Check conditions occurred. It also handles the self test mode and generates a strobe when the complete data word is received.

### Receiver Shift Register

This logic is a serial to parallel shift register that converts the received information into a 10 bit data word and RTA status bit.

### **Receiver Holding Register**

This register holds the assembled data word until it is read by the processor.

# DESCRIPTION OF PIN FUNCTIONS Processor Related Signals

|        |                                   |        | Flocessor riciated digitals                                                                                                                                                                                                                                    |

|--------|-----------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN NO. | NAME                              | SYMBOL | FUNCTION                                                                                                                                                                                                                                                       |

| 6-13   | Transmit/<br>Receive Data<br>Bits | D0-D7  | Bidirectional: 8 bit, three state data port used to transfer data between the COM 9004 and the processor.  D0 is the first bit transmitted.                                                                                                                    |

| 4      | Transmit Bit 9<br>Select          | T9S    | Input: A low level on this pin enables T9 to be transmitted as bit 9. A high level on this pin causes T9 to determine the type of parity bit generated for bits D0-D7.                                                                                         |

| 38     | Transmit Bit 9                    | Т9     | Input: If T9S is low, this supplies transmit bit 9. If T9S is high, then T9 low forces odd parity and T9 high forces even parity to be generated for D0-D7. In this case the parity bit generated is transmit bit 9.                                           |

| 39     | Transmit Bit 10                   | T10    | Input: This pin supplies transmit bit 10.                                                                                                                                                                                                                      |

| 3      | Transmit Parity                   | TP*    | Input: This input controls the parity bit for transmit bits 1-10. A low level on this picauses odd parity and a high level on this pin causes even parity to be generated for bits 1-10. The parity bit generated is transmit bit 11.                          |

| 18     | System Clock                      | SCLK   | Input: This signal is used to synchronize the COM 9004. The transmitter is loade and started on the low to high transition of SCLK if TDS is low. DA is reset on the low to high transition of SCLK if RDA is low.                                             |

| 36     | Transmitter<br>Data Strobe        | TDS    | Input: This input and SCLK are used to load the transmitter holding register and start the transmit sequence. Code Violation Detect (CVD) is reset at this time.                                                                                               |

| 26     | Reset Data<br>Available           | RDA    | Input: This input and SCLK are used to reset DA.                                                                                                                                                                                                               |

| 16     | Status Word<br>Enable             | SWE    | Input: A low level at this pin enables the status word buffer outputs (DA, CVD, TBMT, R9, R10, and RTA). A high level on SWE places the status word buffer outputs in a high impedance state.                                                                  |

| 23     | Receive Data<br>Available         | DA     | This three-state output signal is at a high level when an entire word has been received and transferred into the receiver buffer register. It is only set if a Transm Check Condition did not occur.                                                           |

| 25     | Code Violation<br>Detected        | CVD    | This three-state output signal is at a high level if a valid Code Violation was detected at the receiver since the last time the transmitter was loaded. It is reset when the transmitter is loaded.                                                           |

| 37     | Transmit Buffer<br>Empty          | TBMT   | This three-state output signal is at a high level when the transmit holding registe may be loaded with new data.                                                                                                                                               |

| 14     | Receive Bit 9                     | R9     | This three-state output signal is receiver data bit 9.                                                                                                                                                                                                         |

| 15     | Receive Bit 10                    | R10    | This three-state output signal is receiver data bit 10.                                                                                                                                                                                                        |

| 24     | Receiver Turn-<br>around          | RTA    | This three-state output signal is set to a high level when a valid Mini Code Violation is detected. It is only set if a Transmit Check did not occur. It is reset when the transmitter is loaded.                                                              |

| 5      | Receive Data<br>Enable            | RDE    | Input: A low level enables the outputs of the receive data register D0-D7.                                                                                                                                                                                     |

| 17     | Receiver<br>Parity                | RP*    | Input: This input determines whether the entire received word will be checked for even or odd parity. A low at this pin will cause a check for odd parity and a high this pin will cause a check for even parity. This input has an internal pull-up resistor. |

\*The SYNC bit is included in parity checking.

# DESCRIPTION OF PIN FUNCTIONS (cont.)

| T- | K   | - | 4 | 5 | -07 |

|----|-----|---|---|---|-----|

|    | ••• |   |   |   | - , |

| PIN NO.   | NAME                | SYMBOL          | FUNCTION                                                                                                                                                                                                                                                                                                                      |

|-----------|---------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29        | Analog<br>Loopback  | ALOOP           | Input: A low level on this pin disables the receiver except when the transmitter is active. A high level on this pin and DLOOP will cause the receiver to be disabled while the transmitter is active.  ALOOP is used to allow loop-back through the line drivers and receivers. This input has an internal pull-up resistor. |

| 34        | Digital<br>Loopback | DLOOP           | Input: A low level on this pin disables the receiver except when the transmitter is active. TG is forced to a high level to disable the external coax driver. Data input to the receiver is internally wrapped from the transmitter data output. This input has an internal pull-up resistor.                                 |

| 21        | Master Reset        | MR              | Input: This input should be pulsed low after power-on. This signal resets DA to a low level and sets TG and TBMT to a high level. This input has an internal pull-up.                                                                                                                                                         |

| 1         | Supply Voltage      | V <sub>cc</sub> | +5 volt supply                                                                                                                                                                                                                                                                                                                |

| 22        | Supply Voltage      | V <sub>sd</sub> | + 12 volt supply                                                                                                                                                                                                                                                                                                              |

| 19        | Supply Voltage      | V <sub>bb</sub> | -12 volt supply                                                                                                                                                                                                                                                                                                               |

| 2, 20, 40 | Ground              | GND             | GROUND                                                                                                                                                                                                                                                                                                                        |

### **Device Related Signals**

| PIN NO. | NAME                             | SYMBOL | FUNCTION                                                                                                                                                                                                                                                                                          |

|---------|----------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27      | Baud Rate<br>Clock               | BCLK   | This input is a clock whose frequency is 8 times the desired transmitter and receiver baud rate (typically 18.8696 MHz for 3274/3276 operation). This input is not TTL compatible.                                                                                                                |

| 33      | Transmit Data                    | TD     | Output: Serial data from the transmitter. This signal is a biphase Manchester II encoded bit stream. This output is high when no data is being transmitted.                                                                                                                                       |

| 31      | Transmit Clock                   | TC     | The Transmit Clock output is ½ the frequency of BCLK. It is synchronized with TD and used to provide external pre-distortion timing.                                                                                                                                                              |

| 30      | Receive Data                     | RD     | Input: Accepts the serial biphase Manchester II encoded bit stream.                                                                                                                                                                                                                               |

| 32      | Transmit Gate                    | TG     | Output: This signal is low during the time that the transmit data is valid. TG is used to turn on the external transmit circuitry.                                                                                                                                                                |

| 28      | Receive<br>Single Shot<br>Enable | RSSE   | Input: A high level on this pin enables an internal digital single shot on RD. This limits a high level on RD to 3 clock times. Also when high it will cause the receiver not to detect a valid Code Violation. A low level disables the single shot causing no reshaping of the RD input signal. |

### **COM 9004 OPERATION**

The COM 9004 consists of a receiver section that converts Manchester II phase encoded serial data to parallel data and a transmitter section that converts parallel data to Manchester II phase encoded serial data.

#### Receiver

Message transfers must conform to the IBM 3270 protocol in order for the COM 9004 to acknowledge them.

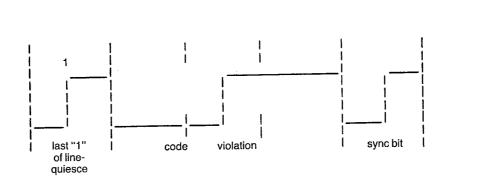

The received message is checked for the Code Violation sequence (start sequence) bit pattern, preceding the first data word, and Mini Code Violation (end sequence) following the last data word.

The data word consists of 10 data bits, a sync bit and a parity bit. Receiving data in multiple byte format is functional only when even parity is selected.

The data word along with the first bit of the next word or ending zero (bit 13) is shifted into a shift register. Once it is assembled it is transferred and held in the holding register until another data word is assembled. The 13th bit is inverted and presented to the bus or RTA (receiver turn-around). Therefore RTA is set high on the last word of a message and is reset when the transmitter is loaded with the

Once the data word is in the holding register and parity is correct the data available (DA) status signal is set high.

The Code Violation Detect signal (CVD) goes active high

after a line Quiesce, Code Violation and sync bit have been detected by the receiver. It is reset when the transmitter of the COM 9004 is asserted. By examining this signal, the processor can determine whether a timeout or Transmit Check condition caused a receiver error.

The receive input is sampled at 8 times the data rate. The receiver logic is brought into bit synchronization during the Line Quiesce pattern. Once the Code Violation following the Line Quiesce is detected, the receiver is brought into bit and word synchronization. The internal receiver clock is adjusted after each transition to compensate for jitter and distortion in the received data signal.

## **Transmitter**

The transmitter section basically consists of a 12-bit holding register, parallel to serial shift register and a parity generator. The firmware initiates a transmit sequence by strobing TDS low. The data is loaded into the holding register on the rising edge of SCLK while TDS is low. Nine bits of data (D0-D7 and T10) are transferred without change to the transmit shift register. The logic level of T9S determines whether T9 will be transmitted as parity on the preceding eight bits, or as data.

After the processor loads the transmit holding register with data, status signal TBMT is driven inactive low until the COM 9004 transfers the data from the transmit holding register to the transmit shift register. After the transfer, TBMT is driven

Diagnostic Modes T-75-45-07

NORMAL OPERATION (ALOOP AND DLOOP HIGH)

Internal read data signal follows the RD input as long as the COM 9004's transmitter is off. The receiver will be disabled while the transmitter is active.

ANALOG LOOPBACK (ALOOP LOW AND DLOOP HIGH) The internal read data signal follows the RD input as long as the COM 9004's transmitter is active.

DIGITAL LOOPBACK ALOOP HIGH AND DLOOP LOW) The internal read data signal follows an internally generated and latched valid transmit signal (only when the transmitter is active.) The output  $\overline{\text{TG}}$  is disabled in digital loopback mode.

DISABLE RECEIVER (ALOOP AND DLOOP LOW) The internal read data signal is held low and output TG is disabled.

### 9004 while TBMT is low. When initiating a data transmission, the COM 9004 automatically transmits a Line Quiesce pattern and a Code Violation. The data is then shifted out of the shift register with a sync bit (1) inserted before the data word, and a parity bit appended after the data word. If a new word is loaded into the COM 9004 before the parity

high. The processor should not try to load data into the COM

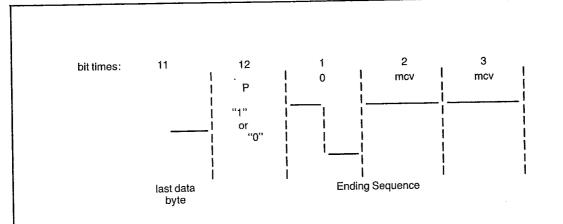

bit of the previous word has been transmitted, a sync bit (1) followed by the new data bits is transmitted. If not, after the COM 9004 transmits the last data word (no more transmit sequences are started), a sync bit (0) and a Mini Code Violation is appended to the end of the message.

Output  $\overline{\text{TG}}$  goes active low one-half bit cell time before the first Line Quiesce character is output. It is made inactive (high) during the transmission of the Mini Code Violation.

### **MESSAGE FORMATS**

| Single Byte Transmission | on   |             | _                 |               |                    |              |

|--------------------------|------|-------------|-------------------|---------------|--------------------|--------------|

| COAX LINE                | CODE | SYNC<br>BIT | DATA<br>(10 BITS) | PARITY<br>BIT | ENDING<br>SEQUENCE | COAX<br>IDLE |

**Multiple Byte Transmission**

| COAX  | LINE | CODE<br>VIOLATION | SYNC<br>BIT | DATA 1<br>(10 BITS) | PARITY<br>BIT | SYNC<br>BIT        | DATA 2<br>(10 BITS) |

|-------|------|-------------------|-------------|---------------------|---------------|--------------------|---------------------|

| PARIT | Υ    | SYNC              | DATA N      |                     | RITY          | ENDING<br>SEQUENCE | COAX<br>IDLE        |

Bits on the coax appear as positive and negative going pulses. A positive pulse to negative pulse transition in the middle of the bit cell is interpreted as a logical '0'. A negative pulse to positive pulse transition in the middle of a bit cell is

interpreted as a logical '1'. A predistortion pulse is generated for every pulse transition from an up to down level or a down to up level.

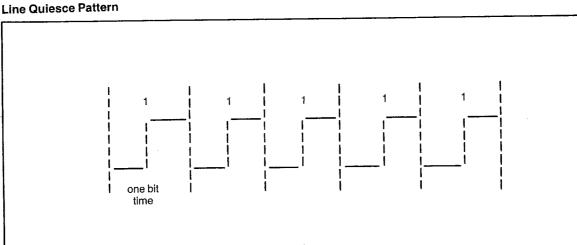

The Line Quiesce pattern consists of five contiguous logical ones. It establishes an equilibrium condition on the coax following line turnaround.

### **Code Violation Pattern**

The Code Violation pattern is a bit sequence containing no mid-bit time level transition in two of its three bit cells. It is a unique pattern that violates the encoding rules and indicates the start of valid data.

# Mini Code Violation Pattern

The Mini Code Violation (MCV) pattern is a bit sequence containing no mid-bit time level transition in either of its bit cells. It is a unique code that violates the encoding rules and indicates the end of valid transmit data.

### **Transmit Check**

A Transmit Check is defined as follows:

- A logical zero sync bit in the ending sequence not followed by a Mini Code Violation.

- 2) Loss of a level transition at the mid-bit time during other than a normal ending sequence.

- 3) A transmission parity error.

### MAXIMUM GUARANTEED RATINGS

| Operating Temperature Range                             | 0°C to | o +70°C |

|---------------------------------------------------------|--------|---------|

| Storage Temperature Range –                             | 55° to | + 150°C |

| Lead Temperature (soldering, 10 sec.)                   |        | + 300°C |

| Positive Voltage on any I/O Pin, with respect to ground |        | + 18.0V |

| Negative Voltage on any I/O Pin, with respect to ground |        | 0.3V    |

<sup>\*</sup>Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

NOTE: When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes or "glitches" on their outputs when the AC power is switched on and off. In addition, voltage transients on the AC power line may appear on the DC output. For example, the bench power supply programmed to deliver + 12 volts may have large voltage transients when the AC power is switched on and off. If this possibility exists it is suggested that a clamp circuit be used.

DC ELECTRICAL CHARACTERISTICS ( $T_a$ = 0°C to 70°C,  $V_{cc}$  =  $\pm 5V$   $\pm 5\%$ ,  $V_{pb}$  =  $\pm 12V$   $\pm 5\%$ ,  $V_{eb}$  =  $\pm 12V$   $\pm 5\%$ )

| PARAMETER                                  | MIN  | TYP | MAX                  | UNIT | COMMENTS                      |

|--------------------------------------------|------|-----|----------------------|------|-------------------------------|

| DC CHARACTERISTICS<br>INPUT VOLTAGE LEVELS |      |     |                      |      |                               |

| V <sub>II</sub> Low                        | -0.3 |     | .8                   | V    |                               |

| V <sub>H</sub> High                        | 2.0  |     | V <sub>cc</sub>      | Ý    | (Except BCLK, MR)             |

| V <sub>™</sub> High                        | 4.3  |     | V <sub>cc</sub> + .3 | v    | (BCLK only)                   |

| V <sub>n</sub> High                        | 3.0  |     | V <sub>cc</sub> + .3 | Ÿ    | MR only                       |

| OUTPUT VOLTAGE LEVELS                      |      |     |                      |      |                               |

| V <sub>ol.</sub> Low                       |      |     | .4                   |      | $I_{OL} = 2.0 \text{ mA}$     |

| V <sub>он</sub> High                       | 2.4  |     | . <u>]</u>           |      | $I_{OH} =25  \text{mA}$       |

| POWER SUPPLY CURRENT                       |      |     |                      |      |                               |

| Icc                                        | 1    | 70  | [ ]                  | mA   | All outputs = V <sub>OH</sub> |

| l <sub>pp</sub>                            |      | 16  |                      | mA   | ]                             |

| l <sub>BB</sub>                            |      | 5   |                      | mA   | l                             |

| NPUT LEAKAGE CURRENT                       |      |     |                      |      |                               |

| All input pins                             |      |     | .01                  | mA   | $V_{IN} = 0$ to $V_{CC}$      |

| CAPACITANCE                                |      |     |                      |      |                               |

| C <sub>IN</sub>                            |      |     | 10                   | pf   | (Except BCLK)                 |

| C'M                                        |      |     | 35                   | pf   | (BCLK only)                   |

AC ELECTRICAL CHARACTERISTICS (T\_A = 0°C to 70°C,  $V_{cc}$  = +5V  $\pm5\%$ ,  $V_{dd}$  = +12V  $\pm5\%$ ,  $V_{BB}$  = -12V  $\pm5\%$ )

| PARAMETER                                            | MIN       | TYP      | MAX  | UNIT | CONDITIONS |

|------------------------------------------------------|-----------|----------|------|------|------------|

| Clock Frequency                                      |           |          |      |      |            |

| Bar                                                  | 7         | 18.8696  | 18.9 | MHz  |            |

| S <sub>CLK</sub>                                     | DC        | 4.7474   | 5    | MHz  |            |

| Clock Width                                          |           |          |      |      |            |

| t <sub>skH</sub> SCLK High                           | 80        | ľ        |      | ns   |            |

| t <sub>skL</sub> SCLK Low                            | 80        |          |      | ns   |            |

| t <sub>BKH</sub> BCLK High                           | 20        |          |      | ns   |            |

| t <sub>skr</sub> BCLK Low                            | 20        |          |      | ns   |            |

| t, BCLK rise time                                    |           |          | 6    | ns   |            |

| t <sub>F</sub> BCLK fall time                        |           |          | 6    | ns   |            |

| t <sub>app</sub> RDE to Data Valid Delay             |           |          | 50   | ns   |            |

| t <sub>spp</sub> SWE to Data Valid Delay             |           | ŀ        | 50   | ns   |            |

| top Data Read to Bus Float                           |           |          | 50   | ns   |            |

| t <sub>ps</sub> Data Setup Time                      | 100       |          |      | ns   |            |

| t <sub>он</sub> Data Hold Time                       | 10        |          |      | ns   |            |

| t <sub>oav</sub> DA to receive data                  | -100      |          | 100  | ns   |            |

| valid delay                                          |           | <u> </u> |      | l    | Í          |

| t <sub>τc</sub> TC clock period                      |           | 106      |      | ns   |            |

| troup TC to TG low delay                             | -53       |          | 30   | ns   |            |

| t <sub>TGHD</sub> TC to TG high delay                |           |          | 30   | ns   |            |

| t <sub>ros</sub> Transmit data to TG                 | 10        |          |      | ns   |            |

| setup time                                           |           |          |      |      | 1          |

| t <sub>TDH</sub> Transmit data to TC                 | 20        |          |      | ns   |            |

| hold time<br>t <sub>n</sub> TBMT active to de-active |           | 200      |      | l    |            |

|                                                      |           | 200      |      | ns   | -          |

| t <sub>ppc</sub> TBMT cycle                          |           |          | 3,2  | μS   |            |

| t <sub>DD</sub> TBMT de-activated                    | 1 1       |          | 2    | μs   |            |

| toss TDS set up                                      | 100       |          | 200  | ns   |            |

| t <sub>DSH</sub> TDS hold                            | 10<br>300 |          | 100  | ns   |            |

| t <sub>MR</sub> MR pulse width                       | 300       | <u> </u> |      | ns   | <u> </u>   |

COLUMN ACCOUNT

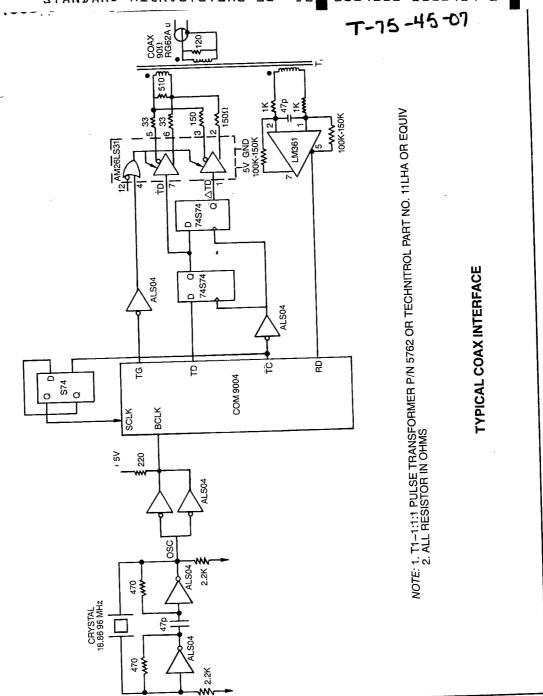

Circuit diagrams utilizing SMC products are included as a means of illustrating typical semiconductor applications, consequently complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of SMC or others. SMC reserves the right to make changes at any time in order to improve design and supply the best product possible.