### **CMOS DUAL-PORT RAM** 8K (1K x 8-BIT)

PRELIMINARY IDT7030SA/LA IDT7040SA/LA

#### **FEATURES:**

· High-speed access

-Military: 25/35/45ns (max.) -Commercial: 20/25/35ns (max.)

· Low-power operation

-IDT7030/40SA

Active: 400mW (typ.) Standby: 7mW (typ.)

-IDT7030/40LA

Active: 400mW (typ.) Standby: 2mW (tvp.)

· MASTER IDT7030 easily expands data bus width to 16or-more-bits using SLAVE IDT7040

On-chip port arbitration logic (IDT7030 only)

BUSY output flag on IDT7030; BUSY input on IDT7040

INT flag for port-to-port communication

· Fully asynchronous operation from either port

· Battery backup operation-2V data retention

TTL-compatible, single 5V ±10% power supply · Military product compliant to MIL-STD-883, Class B

Industrial temperature range (-40°C to +85°C) is avail-

able, tested to military electrical specifications

#### **DESCRIPTION:**

The IDT7030/IDT7040 are high speed 1K x 8 dual-port static RAMs. The IDT7030 is designed to be used as a stand-alone 8-bit dual-port RAM or as a "MASTER" dualport RAM together with the IDT7040 "SLAVE" dual-port in 16-bit-or-more word width systems. Using the IDT MASTER/ SLAVE dual-port RAM approach in 16-or-more-bit memory system applications results in full-speed, error-free operation without the need for additional discrete logic.

Both devices provide two independent ports with separate control, address, and I/O pins that permit independent asynchronous access for reads or writes to any location in memory. An automatic power down feature, controlled by CE, permits the on chip circuitry of each port to enter a very low standby power mode.

Fabricated using IDT's CEMOS™ high-performance technology, these devices typically operate on only 400mW of power at maximum access times as fast as 20ns. Lowpower (LA) versions offer battery backup data retention capability, with each dual-port typically consuming 200µW from a 2V battery.

The IDT7030/IDT7040 devices are packaged in 48-pin sidebraze or plastic DIPs. Military grade product is manufactured in compliance with the latest revision of MIL-STD-883, Class B.

2690 drw 01

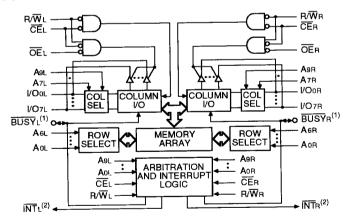

### **FUNCTIONAL BLOCK DIAGRAM**

NOTES:

IDT7030 (MASTER): BUSY is open drain output and requires pullup resistor. IDT7040 (SLAVE): BUSY is input.

Open drain output: requires pullup resistor.

CEMOS is a trademark of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

**APRIL 1992**

DSC-1078/2

@1992 Integrated Device Technology, Inc.

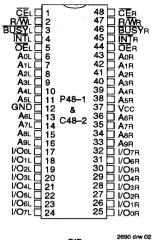

#### PIN CONFIGURATIONS

#### DIP TOP VIEW

#### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol               | Rating                               | Commercial   | Military     | Unit |

|----------------------|--------------------------------------|--------------|--------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage with Respect to GND | -0.5 to +7.0 | -0.5 to +7.0 | >    |

| TA                   | Operating<br>Temperature             | 0 to +70     | -55 to +125  | ç    |

| TBIAS                | Temperature<br>Under Bias            | -55 to +125  | -65 to +135  | ပ္   |

| Тѕтс                 | Storage<br>Temperature               | -55 to +125  | -65 to +150  | ç    |

| Іоит                 | DC Output<br>Current                 | 50           | 50           | mA   |

#### NOTE:

2690 tbi 0

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS

may cause permanent damage to the device. This is a stress rating only

and functional operation of the device at these or any other conditions

above those indicated in the operational sections of the specification is not

implied. Exposure to absolute maximum rating conditions for extended

periods may affect reliability.

- 2. VTERM must not exceed Vcc + 0.5V.

#### CAPACITANCE (TA = +25°C, f = 1.0MHz)

| Symbol | Parameter (1)      | Parameter <sup>(1)</sup> Conditions |    |    |  |  |

|--------|--------------------|-------------------------------------|----|----|--|--|

| Cin    | Input Capacitance  | VIN = 0V                            | 11 | рF |  |  |

| Соит   | Output Capacitance | VIN = 0V                            | 11 | pF |  |  |

#### NOTE:

## RECOMMENDED DC OPERATING CONDITIONS

| Symbol | Parameter          | Min.                | Тур. | Max.   | Unit |  |

|--------|--------------------|---------------------|------|--------|------|--|

| Vcc    | Supply Voltage     | 4.5                 | 5.0  | 5.5    | ٧    |  |

| GND    | Supply Voltage     | 0                   | 0    | 0      | ٧    |  |

| ViH    | Input High Voltage | 2.2                 |      | 6.0(2) | ٧    |  |

| VIL    | Input Low Voltage  | -0.5 <sup>(1)</sup> | _    | 0.8    | ٧    |  |

2690 tbl 02

- NOTE:

1. Vil. (min.) = -3.0V for pulse width less than 20ns.

- 2. VTERM must not exceed Vcc + 0.5V.

## RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| Grade      | Amblent<br>Temperature | GND | Vcc        |

|------------|------------------------|-----|------------|

| Military   | -55°C to +125°C        | ov  | 5.0V ± 10% |

| Commercial | 0°C to +70°C           | ٥٧  | 5.0V ± 10% |

2690 tbl 03

This parameter is determined by device characterization but is not production tested.

### DC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE (Vcc = 5.0V ±10%)

|             |                                              |                             | IDT70 |      | IDT<br>IDT |      |      |

|-------------|----------------------------------------------|-----------------------------|-------|------|------------|------|------|

| Symbol      | Parameter                                    | Test Conditions             | Min.  | Max. | Max.       | Max. | Unit |

| lu          | Input Leakage<br>Current <sup>(7)</sup>      | Vcc = 5.5V, VIN = 0V to Vcc | _     | 10   |            | 5    | μΑ   |

| lto         | Output Leakage<br>Current                    | CE = ViH, VOUT = 0V to VCC  |       | 10   | _          | 5    | μА   |

| Vol         | Output Low Voltage                           | IOL = 4.0mA                 | _     | 0.4  |            | 0.4  | V    |

| Vol         | Open Drain Output<br>Low Voltage (BUSY, INT) | IOL = 16mA                  |       | 0.5  |            | 0.5  | V    |

| <b>V</b> он | Output High Voltage                          | IOH = -4mA                  | 2.4   |      | 2.4        |      | V    |

2690 tbl 05

## DC ELECTRICAL CHARACTERISTICS OVER THE **OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE** (Vcc = $5.0V \pm 10\%$ )

|        |                                           |                                                                                 |         |                |               | x 20 <sup>(2)</sup><br>x 20 <sup>(2)</sup> |                   | 0 x 25<br>0 x 25  |                   | ) x 35<br>) x 35  | 7030 x<br>7040 x |            |             |

|--------|-------------------------------------------|---------------------------------------------------------------------------------|---------|----------------|---------------|--------------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------|-------------|

| Symbol | Parameter                                 | Test Condition                                                                  | Version | on             | Тур.          | Max.                                       | Тур.              | Max.              | Тур.              | Max.              | Тур.             | Max.       | Unit        |

| lcc    | Dynamic Operating<br>Current (Both Ports  | CE = VIL<br>Outputs Open                                                        | Mil.    | SA<br>LA<br>SA | _<br>_<br>125 |                                            | 125<br>125<br>125 | 300<br>240<br>260 | 125<br>125<br>125 | 290<br>230<br>250 | 125<br>125       | 285<br>225 | mA          |

|        | Active)                                   | f = fMAX <sup>(4)</sup>                                                         | Com'l.  | LA             | 125           | 215                                        | 125               | 210               | 125               | 200               | <u> </u>         |            |             |

| ISB1   | Standby Current<br>(Both Ports — TTL      | CEL and CER ≥ VIH f = fMAX <sup>(4)</sup>                                       | Mil.    | SA<br>LA       | <u> </u>      | _                                          | 30<br>30          | 80<br>60          | 30<br>30          | 80<br>60          | 30<br>30         | 80<br>60   | mA          |

|        | Level Inputs)                             | T = IWAX                                                                        | Com'l.  | SA<br>LA       | 30<br>30      | 65<br>45                                   | 30<br>30          | 65<br>45          | 30<br>30          | 65<br>45          | =                |            |             |

| ISB2   | Standby Current<br>(One Port — TTL        | CEL or CER ≥ VIH<br>Active Port Outputs                                         | Mil.    | SA<br>LA       |               |                                            | 80<br>80          | 195<br>160        | 80<br>80          | 185<br>150        | 80<br>80         | 180<br>145 | mA          |

|        | Level Inputs)                             | Open, f = fMAX <sup>(4)</sup>                                                   | Com'l.  | SA<br>LA       | - 70000       | 180<br>145                                 | 80<br>80          | 175<br>140        | 80<br>80          | 165<br>130        | <u> </u>         |            |             |

| ISB3   | Full Standby Current<br>(Both Ports — All | Both Ports CEL and<br>CER > Vcc - 0.2V                                          | Mil.    | SA<br>LA       |               | <i>-</i>                                   | 1.0<br>0.2        | 30<br>10          | 1.0<br>0.2        | 30<br>10          | 1.0<br>0.2       | 30<br>10   | mA          |

|        | CMOS Level Inputs)                        | $VIN \ge VCC - 0.2V \text{ or } VIN \le 0.2V, f = 0^{(5)}$                      | Com'l.  | SA<br>LA       | 1.0<br>0.2    | 15<br>5                                    | 1.0<br>0.2        | 15<br>5           | 1.0<br>0.2        | 15<br>5           |                  |            |             |

| ISB4   | Full Standby Current<br>(One Port — All   | One Port CEL or<br>CER ≥ Vcc - 0.2V                                             | Mil.    | SA<br>LA       | 4             |                                            | 70<br>70          | 185<br>150        | 70<br>70          | 175<br>140        | 70<br>70         | 170<br>135 | mA          |

|        | CMOS Level Inputs)                        | $Vin \ge Vcc - 0.2V$ or $Vin \le 0.2V$ Active Port Outputs Open, $f=fmax^{(4)}$ | Com'l   | . SA<br>LA     | 70<br>70      | 175<br>140                                 | 70<br>70          | 170<br>135        | 70<br>70          | 160<br>125        | =                |            | 2690 tbl 06 |

- 1. x in part numbers indicates power rating (SA or LA).

- 2. 0°C to +70°C temperature range only.

- 3. -55°C to +125°C temperature range only.

- 4. At f = fMAX, address and control lines (except Output Enable) are cycling at the maximum frequency read cycle of 1/tnc, and using "AC TEST CONDITIONS" of input levels of GND to 3V.

- 5. f = 0 means no address or control lines change. Applies only to inputs at CMOS level standby.

- Vcc=5V, Ta=+25°C for Typ.

- At Vcc≤2.0V input leakages are undefined.

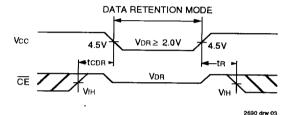

### DATA RETENTION CHARACTERISTICS (LA Version Only)

|                     |                                         |                                        |          | ID1703              | OLA/IDDT7 | 040LA |    |

|---------------------|-----------------------------------------|----------------------------------------|----------|---------------------|-----------|-------|----|

| Symbol              | Parameter                               | Test Conditions                        | Min.     | Typ. <sup>(1)</sup> | Max.      | Unit  |    |

| <b>V</b> DR         | Vcc for Data Retention                  | Vcc = 2.0V, <del>CE</del> ≥ Vcc - 0.2V |          | 2.0                 |           | 0     | V  |

| ICCDR               | Data Retention Current                  | VIN ≥ VCC - 0.2V or VIN ≤ 0.2V         | Mit.     |                     | 100       | 4000  | μА |

|                     |                                         |                                        | Com'l.   | _                   | 100       | 1500  |    |

| tcon <sup>(3)</sup> | Chip Deselect to Data<br>Retention Time |                                        | <u> </u> | 0                   | _         | _     | ns |

| tR <sup>(3)</sup>   | Operation Recovery<br>Time              | 1                                      |          | trc(2)              | _         |       | ns |

#### NOTES:

- 1. Vcc = 2V, TA = +25°C

- 2. tRc = Read Cycle Time

- 3. This parameter is guaranteed but not tested.

#### **DATA RETENTION WAVEFORM**

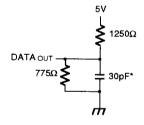

### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V          |

|-------------------------------|----------------------|

| Input Rise/Fall Times         | 5ns                  |

| Input Timing Reference Levels | 1.5V                 |

| Output Reference Levels       | 1.5V                 |

| Output Load                   | See Figures 1, 2 & 3 |

2690 tbl 08

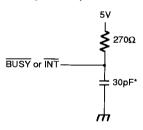

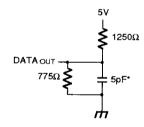

Figure 1. Output Load

Figure 3. BUSY and INT Output Load

Figure 2. Output Load (for thz, tLz, twz, and tow)

2690 drw 04

<sup>\*</sup> Including scope and jig

# AC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE<sup>(5)</sup>

|             |                                             | 7030 x 20 <sup>(2)</sup><br>7040 x 20 <sup>(2)</sup> | 7030 x 25<br>7040 x 25 |      | 7030 x 35<br>7040 x 35 |      | 7030 x 45 <sup>(3)</sup><br>7040 x 45 <sup>(3)</sup> |      |      |

|-------------|---------------------------------------------|------------------------------------------------------|------------------------|------|------------------------|------|------------------------------------------------------|------|------|

| Symbol      | Parameter                                   | Min. Max.                                            | Min. M                 | lax. | Min.                   | Max. | Min.                                                 | Max. | Unit |

| Read Cyc    | cle                                         |                                                      |                        |      |                        |      |                                                      | 15   |      |

| trc         | Read Cycle Time                             | 20 —                                                 | 25                     | _    | 35                     | _    | 45                                                   |      | ns   |

| taa         | Address Access Time                         | <b>— 20</b>                                          | _                      | 25   |                        | 35   |                                                      | 45   | ns   |

| tACE        | Chip Enable Access Time                     | - 20                                                 |                        | 25   |                        | 35   |                                                      | 45   | ns   |

| tage        | Output Enable Access Time                   | — 10                                                 |                        | 12   |                        | 25   |                                                      | 30   | ns   |

| <b>t</b> OH | Output Hold From Address Change             | 0                                                    | 0                      | _    | 0                      | _    | 0                                                    | _    | ns   |

| 1LZ         | Output Low Z Time(1,4)                      | 0 —                                                  | 0                      | _    | 0                      | _    | 0                                                    |      | ns   |

| tHZ         | Output High Z Time(1,4)                     | 8                                                    |                        | 10   |                        | 15   | _                                                    | 20   | ns   |

| tpu         | Chip Enable to Power Up Time <sup>(4)</sup> | 0 —                                                  | 0                      | _    | 0                      | _    | 0                                                    | _    | ns   |

| tPD         | Chip Disable to Power Down Time(4)          | _ 50                                                 | Ī —                    | 50   | _                      | 50   | _                                                    | 50   | ns   |

NOTES:

2690 tbl 09

- 1. Transition is measured ±500mV from low or high impedance voltage with load (Figures 1, 2 and 3).

- 2. 0°C to +70°C temperature range only.

- 3. -55°C to +125°C temperature range only.

- 4. This parameter guaranteed but not tested.

- "x" in part numbers indicates power rating (SA or LA).

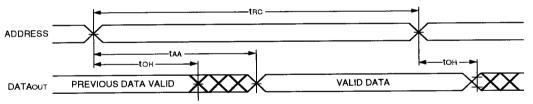

## TIMING WAVEFORM OF READ CYCLE NO. 1, EITHER SIDE(1,2,4)

2690 drw 05

#### NOTES:

- R/W is high for Read Cycles.

- 2. Device is continuously enabled,  $\overline{CE} = VIL$ .

- 3. Addresses valid prior to or coincident with CE transition low.

- 4. OE = VIL.

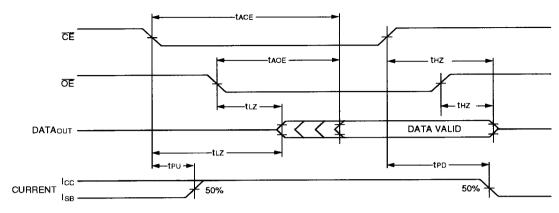

## TIMING WAVEFORM OF READ CYCLE NO. 2, EITHER SIDE(1,3)

2690 drw 06

#### NOTES:

- 1. R/W is high for Read Cycles.

- 2. Device is continuously enabled,  $\overline{CE} = VIL.$

- 3. Addresses valid prior to or coincident with CE transition low.

- 4. OE = VIL.

## AC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE<sup>(7)</sup>

| Sumbal    | Parameter                                          | 7030 x 20 <sup>(2)</sup><br>7040 x 20 <sup>(2)</sup><br>Min. Max. | 7040 | x 25<br>x 25<br>Max. | 7030<br>7040<br>Min |         | 7030 :<br>7040 :<br>Min |     | Unit |

|-----------|----------------------------------------------------|-------------------------------------------------------------------|------|----------------------|---------------------|---------|-------------------------|-----|------|

| Symbol    |                                                    | I WILLIA                                                          |      | MUA.                 | 141111              | · · · · |                         | ex: |      |

| Write Cyc | cie                                                |                                                                   |      |                      |                     |         |                         |     |      |

| twc       | Write Cycle Time <sup>(5)</sup>                    | 20 >                                                              | 25   | _                    | 35                  |         | 45                      | _   | ns   |

| tEW       | Chip Enable to End of Write                        | 15 —                                                              | 20   | _                    | 30                  | _       | 35                      |     | ns   |

| taw       | Address Valid to End of Write                      | 15 —                                                              | 20   | -                    | 30                  |         | 35                      | _   | ns   |

| tas       | Address Set-up Time                                | 0 —                                                               | 0    | -                    | 0                   | _       | 0                       | _   | ns   |

| twp       | Write Pulse Width <sup>(6)</sup>                   | 15 —                                                              | 20   |                      | 30                  | _       | 35                      |     | ns   |

| twn       | Write Recovery Time                                | 0                                                                 | 0    | _                    | 0                   |         | 0                       |     | ns   |

| tow       | Data Valid to End of Write                         | 10 —                                                              | 12   | _                    | 20                  | _       | 20                      |     | ns   |

| tHZ       | Output High Z Time <sup>(1,4)</sup>                | — 8                                                               | _    | 10                   |                     | 15      |                         | 20  | ns   |

| ton       | Data Hold Time                                     | 0 —                                                               | 0    |                      | 0                   | _       | 0                       |     | ns   |

| twz       | Write Enabled to Output in High Z <sup>(1,4)</sup> | → 8                                                               | _    | 10                   |                     | 15      | _                       | 20  | ns   |

| tow       | Output Active From End of Write(1,4)               | 0 —                                                               | 0    | _                    | 0                   | _       | 0                       | _   | ns   |

#### NOTES:

- 1. Transition is measured ±500mV from low or high impedance voltage with load (Figures 1, 2 and 3).

- 2. 0°C to +70°C temperature range only.

- 3. -55°C to +125°C temperature range only

- 4. This parameter guaranteed but not tested.

- 5. For MASTER/SLAVE combination, two = tBAA + twp.

- 6. Specified for OE at high (refer to "Timing Waveform of Write Cycle", Note 7).

- 7. "x" in part numbers indicates power rating (SA or LA).

2690 tbl 10

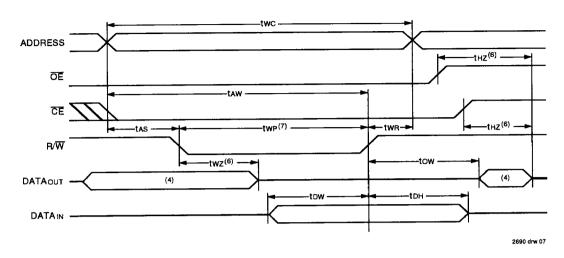

## TIMING WAVEFORM OF WRITE CYCLE NO. 1, (R/W CONTROLLED TIMING)(1,2,3,7)

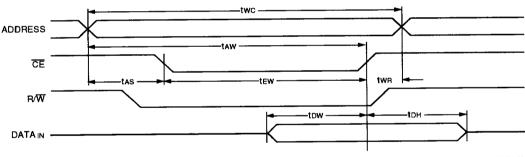

## TIMING WAVEFORM OF WRITE CYCLE NO. 2, $(\overline{\text{CE}} \text{ CONTROLLED TIMING})^{(1,2,3,5)}$

2690 drw 08

6

#### NOTES:

- 1. R/W must be high during all address transitions.

- 2. A write occurs during the overlap (tew or twp) of a low CE and a low R/W.

3. twn is measured from the earlier of CE or R/W going high to the end of the write cycle.

- During this period, the I/O pins are in the output state and input signals must not be applied.

If the CE low transition occurs simultaneously with or after the R/W low transition, the outputs remain in the high impedance state.

- Transition is measured ±500mV from steady state with a 5pF load (including scope and jig).

- 7. If OE is low during a R/W controlled write cycle, the write pulse width must be larger of two or (twz + tow) to allow the I/O drivers to turn off and data to be placed on the bus for the required tow. If OE is high during a R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified twp.

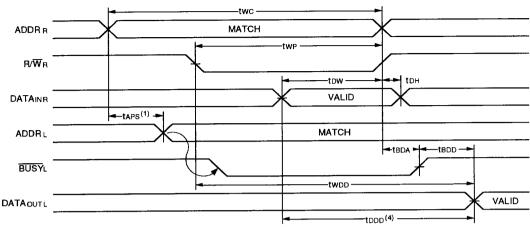

## AC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE<sup>(8)</sup>

|          |                                                 | 7030 x 20 <sup>(1)</sup><br>7040 x 20 <sup>(1)</sup> |      | 0 x 25<br>0 x 25 |      | 0 x 35<br>0 x 35 |      | x 45 <sup>(2)</sup><br>x 45 <sup>(2)</sup> |      |

|----------|-------------------------------------------------|------------------------------------------------------|------|------------------|------|------------------|------|--------------------------------------------|------|

| Symbol   | Parameter                                       | Min. Max.                                            | Min. | Max.             | Min. | Max.             | Min. | Max.                                       | Unit |

| Busy Tim | ing (For Master IDT7030 Only)                   |                                                      |      |                  |      |                  |      |                                            |      |

| tBAA     | BUSY Access Time to Address                     | — 20                                                 | _    | 25               |      | 35               | _    | 35                                         | ns   |

| tBDA     | BUSY Disable Time to Address                    | — <u> </u>                                           |      | 20               |      | 30               | _    | 35                                         | ns   |

| tBAC     | BUSY Access Time to Chip Enable                 | 20                                                   | _    | 20               | _    | 30               | _    | 30                                         | ns   |

| tBDC     | BUSY Disable Time to Chip Enable                | <u> </u>                                             | _    | 20               | -    | 25               | _    | 25                                         | ns   |

| twdd     | Write Pulse to Data Delay <sup>(3)</sup>        | _ 50                                                 | _    | 50               | -    | 60               | _    | 70                                         | ns   |

| todo     | Write Data Valid to Read Data Delay(3)          | <b>— 35</b>                                          | _    | 35               | _    | 45               |      | 55                                         | ns   |

| taps     | Arbitration Priority Set-up Time <sup>(4)</sup> | 5                                                    | 5    | _                | 5    | _                | 5    |                                            | ns   |

| tBDD     | BUSY Disable to Valid Data <sup>(5)</sup>       | Note 5                                               |      | Note 5           | _    | Note 5           |      | Note 5                                     | ns   |

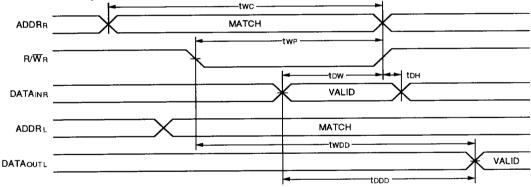

| Busy In  | out Timing (For Slave IDT7040 Only)             |                                                      |      |                  |      |                  |      |                                            |      |

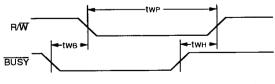

| twB      | Write to BUSY Input <sup>(6)</sup>              | 0 —                                                  | 0    | _                | 0    |                  | 0    |                                            | ns   |

| twн      | Write Hold After BUSY <sup>(7)</sup>            | 12 —                                                 | 15   | _                | 20   |                  | 20   | _                                          | ns   |

| twdd     | Write Pulse to Data Delay <sup>(9)</sup>        | <b>—</b> 50                                          | _    | 50               | _    | 60               | _    | 70                                         | ns   |

| topo     | Write Data Valid to Read Data Delay(9)          | 35                                                   | -    | 35               | –    | 45               | _    | 55                                         | ns   |

#### NOTES:

0°C to +70°C temperature range only.

-55°C to +125°C temperature range only.

3. Port-to-port delay through RAM cells from writing port to reading port, refer to "Timing Waveform of Read With BUSY (For Master IDT7030 only)".

4. To ensure that the earlier of the two ports wins.

5. tabb is a calculated parameter and is the greater of 0, twoo-two (actual) or topo-tow (actual).

To ensure that the write cycle is inhibited during contention.

To ensure that a write cycle is completed after contention.

8. "x" in part numbers indicates power rating (SA or LA).

9. Port-to-port delay through RAM cells from writing port to reading port, refer to "Timing Waveform of Read With Port-to-Port Delay (for Slave IDT7040 Only)".

2690 tbl 11

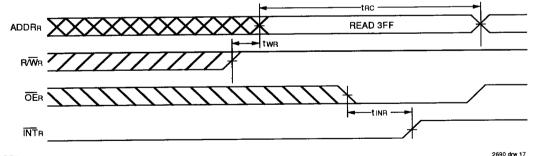

## TIMING WAVEFORM OF READ WITH $\overline{\text{BUSY}}^{(1,2,3)}$ (FOR MASTER IDT7030 ONLY)

NOTES:

2690 drw 09

- 1. To ensure that the earlier of the two ports wins.

- 2. Write Cycle parameters should be adhered to in order to ensure proper writing.

- 3. Device is continuously enabled for both ports.

- 4. OE at LO for the reading port.

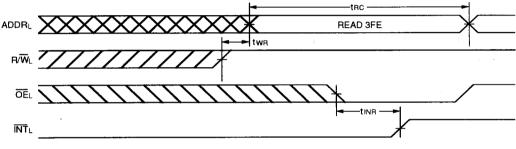

## TIMING WAVEFORM OF READ WITH PORT-TO-PORT DELAY(1,2,3) (FOR SLAVE IDT7040 ONLY)

#### NOTES:

- 1. Assume BUSY input at HI for the writing port, and OE at LO for the reading port.

- 2. Write Cycle parameters should be adhered to in order to ensure proper writing.

- 3. Device is continuously enabled for both ports.

### TIMING WAVEFORM OF WRITE WITH BUSY INPUT (FOR SLAVE IDT7040 ONLY)

2690 drw 11

9

2690 drw 10

6-2-9

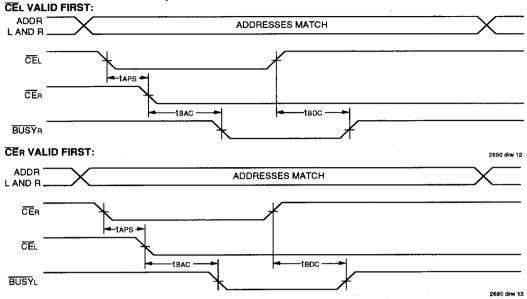

## TIMING WAVEFORM OF CONTENTION CYCLE NO. 1, CE ARBITRATION (FOR MASTER IDT7030 ONLY)

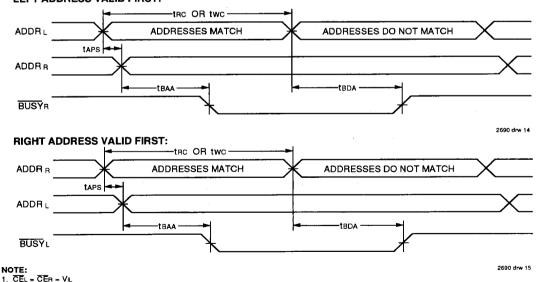

# TIMING WAVEFORM OF CONTENTION CYCLE NO. 2, ADDRESS VALID ARBITRATION $^{(1)}$ (FOR MASTER IDT7030 ONLY)

#### **LEFT ADDRESS VALID FIRST:**

## 6

## AC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE<sup>(3)</sup>

|           |                      | 7030 x 20 <sup>(1)</sup><br>7040 x 20 <sup>(1)</sup> | 7030 x 25<br>7040 x 25 |      |      |      |          |      | 7030 x 45 <sup>(2)</sup><br>7040 x 45 <sup>(2)</sup> |  | 1 |  |  |

|-----------|----------------------|------------------------------------------------------|------------------------|------|------|------|----------|------|------------------------------------------------------|--|---|--|--|

| Symbol    | Parameter            | Min. Max.                                            | Min.                   | Max. | Min. | Max. | Min.     | Max. | Unit                                                 |  |   |  |  |

| Interrupt | Timing               |                                                      |                        |      |      |      |          |      |                                                      |  |   |  |  |

| tas       | Address Set-up Time  | 0 —                                                  | 0                      |      | 0    | _    | 0        |      | ns                                                   |  |   |  |  |

| twn       | Write Recovery Time  | o 🤲 —                                                | 0                      |      | 0    |      | 0        |      | ns                                                   |  |   |  |  |

| tins      | Interrupt Set Time   | <b>—</b> 20                                          | _                      | 25   |      | 35   | <u> </u> | 40   | ns                                                   |  |   |  |  |

| tinr      | Interrupt Reset Time | <u> </u>                                             | _                      | 25   |      | 35   | —        | 40   | ns                                                   |  |   |  |  |

NOTES:

- 1. 0°C to +70°C temperature range only.

- 2. -55°C to +125°C temperature range only.

- 3. "x" in part numbers indicates power rating (SA or LA).

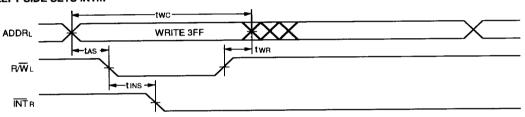

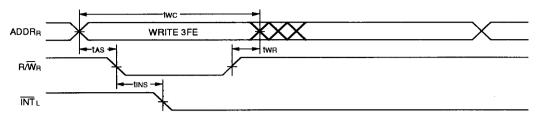

## TIMING WAVEFORM OF INTERRUPT MODE<sup>(1,2)</sup>

#### LEFT SIDE SETS INTR:

2690 drw 16

2690 tbl 12

#### RIGHT SIDE CLEARS INTR:

NOTES:

- 1. CEL = CER = VIL

- 2. INTL and INTR are reset (high) during power up.

### TIMING WAVEFORM OF INTERRUPT MODE(1,2)

#### RIGHT SIDE SETS INTL:

2690 drw 18

#### LEFT SIDE CLEARS INTL:

2690 drw 19

#### NOTES:

1. CEL = CER = VIL

2. INTh and INTL are reset (high) during power up.

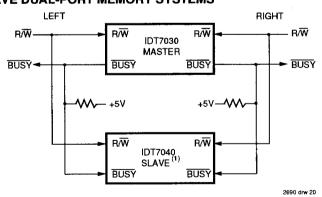

### 16-BIT MASTER/SLAVE DUAL-PORT MEMORY SYSTEMS

NOTE:

1. No arbitration in IDT7040 (SLAVE). BUSY-IN inhibits write in IDT7040 (SLAVE).

## 6

#### **FUNCTIONAL DESCRIPTION**

The IDT7030/IDT7040 provides two ports with separate control, address, and I/O pins that permit independent access for reads or writes to any locations in memory. The IDT7030/IDT7040 has an automatic power down feature controlled by CE. The CE controls on-chip power down circuitry that permits the respective port to go into a standby mode when not selected (CE high). When a port is enabled, access to the entire memory array is permitted. Each port has its own Output Enable control (OE). In the read mode, the port's OE turns on the output drivers when set LOW. Noncontention READ/WRITE conditions are illustrated in Table

The interrupt flag (INT) permits communication between ports or systems. If the user chooses to use the interrupt function, a memory location (mail box or message center) is assigned to each port. The left port interrupt flag (INTL) is set when the right port writes to memory location 3FE (HEX). The left port clears the interrupt by reading address location 3FE (HEX). Likewise, the right port interrupt flag (INTR) is set when the left port writes to memory location 3FF (HEX) and to clear the interrupt flag (INTR) the right port must read the memory location 3FF. The message (8-bits) at 3FE or 3FF is user defined. If the interrupt function is not used, address locations 3FE or 3FF are not used as mailboxes, but as part of the random access memory. Refer to Table II for the interrupt operation.

## ARBITRATION LOGIC FUNCTIONAL DESCRIPTION

The arbitration togic will resolve an address match or a chip enable match down to 5ns minimum and determine which port has access. In all cases, an active BUSY flag will be set for the delayed port.

The BUSY flags are provided for the situation when both ports simultaneously access the same memory location. When this situation occurs, on-chip arbitration logic will determine which port has access and sets the delayed port's BUSY flag. BUSY is set at speeds that permit the processor to hold the operation and its respective address data. It is important to note that the write operation is invalid for the port that has BUSY set LOW. The delayed port will have access when BUSY goes inactive.

Contention occurs when both left and right ports are active and both addresses match. When this situation occurs, the on-chip arbitration logic determines access. Two modes of arbitration are provided: (1) if the addresses match and are valid before  $\overline{\text{CE}}$ , on-chip control logic arbitrates between  $\overline{\text{CE}}$  and  $\overline{\text{CE}}$ n for access; or (2) if the  $\overline{\text{CE}}$ s are low before an address match, on-chip control logic arbitrates between the left and right addresses for access (refer to Table II). In either mode of arbitration, the delayed port's  $\overline{\text{BUSY}}$  flag is set and will reset when the port granted access completes its operation.

## DATA BUS WIDTH EXPANSION MASTER/SLAVE DESCRIPTION

Expanding the data bus width to sixteen-or-more-bits in a dual-port RAM system implies that several chips will be active at the same time. If each chip includes a hardware arbitrator, and the addresses for each chip arrive at the same time, it is possible that one will activate its BUSYL while another activates its BUSYR signal. Both sides are now busy and the CPUs will wait indefinitely for their port to become free.

To avoid the "Busy Lock-Out" problem, IDT has developed a MASTER/SLAVE approach where only one arbitrator, in the MASTER, is used. The SLAVE has BUSY inputs which allow an interface to the MASTER with no external components and with a speed advantage over other systems.

When expanding dual-port RAMS in width, the writing of the SLAVE RAMS must be delayed, until after the BUSY input has settled. Otherwise, the SLAVE chip may begin a write cycle during a contention situation. Conversely, the write pulse must extend a hold time past BUSY to ensure that a write cycle takes place after the contention is resolved. This timing is inherent in all dual-port memory systems where more than on chip is active at the same time.

The write pulse to the SLAVE should be delayed by the maximum arbitration time of the MASTER. If, then, a contention occurs, the write to the SLAVE will be inhibited due to BUSY from the MASTER.

#### **TRUTH TABLES**

### **TABLE I - NON-CONTENTION** READ/WRITE CONTROL<sup>(4)</sup>

| Le  | ft or | Right | Port <sup>(1)</sup> |                                                      |

|-----|-------|-------|---------------------|------------------------------------------------------|

| R/W | CE    | ΟĒ    | D0-7                | Function                                             |

| Х   | Н     | X     | Z                   | Port Disabled and in Power<br>Down Mode IsB2 or IsB4 |

| Х   | Н     | Х     | Z                   | CER = CEL = H, Power Down<br>Mode, ISB1 or ISB3      |

| L   | L     | Х     | DATAIN              | Data on Port Written into Memory (2                  |

| Н   | L     | L     | DATAOUT             | Data in Memory Output on Port (3)                    |

| H   | لىا   | Н     | z                   | High Impedance Outputs                               |

NOTES: 1. AoL - AoL ≠ AoR - AoR 2690 tbl 13

- 2. If BUSY = L, data is not written.

- 3. If BUSY = L, data may not be valid, see twoo and tood timing.

- 4. H = HIGH, L = LOW, X = DON'T CARE, Z = HIGH IMPEDANCE

### TABLE II – INTERRUPT FLAG<sup>(1,4)</sup>

| Left Port |     |     |         |                  |      |     |     |         |                  |                       |

|-----------|-----|-----|---------|------------------|------|-----|-----|---------|------------------|-----------------------|

| R/WL      | CEL | OEL | AoL-AgL | INΥL             | R/WR | CER | OER | Aor-Aor | ΪÑΤR             | Function              |

| L         | L   | х   | 3FF     | Х                | х    | Х   | Х   | Х       | L <sup>(2)</sup> | Set Right INTR Flag   |

| Х         | х   | ×   | х       | Х                | Х    | L   | L   | 3FF     | H <sup>(3)</sup> | Reset Right INTR Flag |

| X         | х   | ×   | х       | L <sup>(3)</sup> | L    | L   | х   | 3FE     | Х                | Set Left INTL Flag    |

| ×         | L.  | L   | 3FE     | H <sup>(2)</sup> | Х    | Х   | Х   | X       | X                | Reset Left INTL Flag  |

NOTES:

1. Assume BUSYL = BUSYR = H.

2. If BUSYL = L, then NC.

3. If  $\overline{BUSY}R = L$ , then NC.

2690 tbl 14

4. H = HIGH, L = LOW, X = DON'T CARE, NC = NO CHANGE.

### TABLE II - ARBITRATION(1,2)

| Left Port      |                                             | Righ          | t Port     | Fla   | ags <sup>(1)</sup> |                      |  |  |

|----------------|---------------------------------------------|---------------|------------|-------|--------------------|----------------------|--|--|

| CEL            | AoL-A9L                                     | CER           | Aor-Agr    | BUSYL | BUSYR              | Function             |  |  |

| Н              | Х                                           | Н             | Х          | Н     | Н                  | No Contention        |  |  |

| L              | Any                                         | Н             | Х          | Н     | Н                  | No Contention        |  |  |

| Н              | х                                           | L             | Any        | Н     | Н                  | No Contention        |  |  |

| L              | ≠A0R-A9R                                    | L .           | ≠A0L-A9L   | Н     | Н                  | No Contention        |  |  |

| Address Arb    | itration With CE L                          | ow Before Add | ress Match |       |                    |                      |  |  |

| L              | LV5R                                        | L             | LV5R       | Н     | L                  | L-Port Wins          |  |  |

| L              | RV5L                                        | L             | RV5L       | L     | Н                  | R-Port Wins          |  |  |

| L              | Same                                        | L.            | Same       | Н     | L                  | Arbitration Resolved |  |  |

| L              | Same                                        | L             | Same       | L     | Н                  | Arbitration Resolved |  |  |

| CE Arbitration | CE Arbitration With Address Match Before CE |               |            |       |                    |                      |  |  |

| LL5R           | =A0R-A9R                                    | LL5R          | =A0L-A9L   | H     | L                  | L-Port Wins          |  |  |

| RL5L           | =A0R-A9R                                    | RL5L          | =A0L-A9L   | L     | Н                  | R-Port Wins          |  |  |

| LW5R           | =A0R-A9R                                    | LW5R          | =A0L-A9L   | Н     | L                  | Arbitration Resolved |  |  |

| LW5R           | =A0R-A9R                                    | LW5R          | =A0L-A9L   | L     | Н                  | Arbitration Resolved |  |  |

NOTES:

2690 tbl 15

1. INT Flags Don't Care.

X = DON'T CARE, L = LOW, H = HIGH. LV5R = Left Address Valid ≥ 5ns before right address. RV5L = Right Address Valid ≥ 5ns before left address.

Same = Left and Right Addresses match within 5ns of each other. LL5R = Left CE = LOW ≥ 5ns before Right CE. RL5L = Right CE = LOW ≥ 5ns before Left CE. LW5R = Left and Right CE = LOW within 5ns of each other.

6-2-14