# 240 Channel Segment Driver for Dot matrix STN Liquid Crystal Display with Low Voltage Drive

## EM65H134

### Contents

| 1. General description            | 2  |

|-----------------------------------|----|

| 2. Feature                        | 2  |

| 3. Applications                   | 2  |

| 4. Pin configurations (package)   | 3  |

| 5. Functional block diagram       | 4  |

| 6. Pin descriptions               | 5  |

| 7. Function description           | 7  |

| 8. Absolute maximum rating        | 16 |

| 9. DC electrical characteristics  | 18 |

| 10. AC electrical characteristics | 20 |

| 11. Timing diagrams               | 21 |

| 12. Application circuit           | 22 |

### **GeneralDescription**

The EM65H134 is a 240-channel segment LCD driver LSI, Which drives a dot matrix STN liquid crystal display at low power. The EM65H134 operates with a low 5V LCD drive voltage and a low 3V logic voltage. The EM65H134 includes shadowing correction circuit in order to improve image quality. The EM65H134 is packaged in a fine pitch slim TCP( slim type carrier package) technology, it is deal for substantially decreasing the size of LCD module frame.

### Feature

- Duty cycle: Up to 1/300

- LCD drive voltage: 3.5 to 5.5 V

- 240 LCD drive circuits

Operating voltage: 2.7 to 5.5 V

- Eight data bits

Shift clock speed

-25 MHz max/3 V

-40 MHz max/5 V

Shadowing correction circuit

- Display-off function

- Slim-TCP

—Output lead pitch: 70 µ m

-User area: 5.5mm

- Automatic generation of the chip enable signal

- Standby function

### **Applications**

- PDA

- Dictionary

- Message display product

### **PinConfiguration**

EM65H134 Top View

Note: The pin configuration is LSI chip, not TCP.

Figure 1. Pin configuration

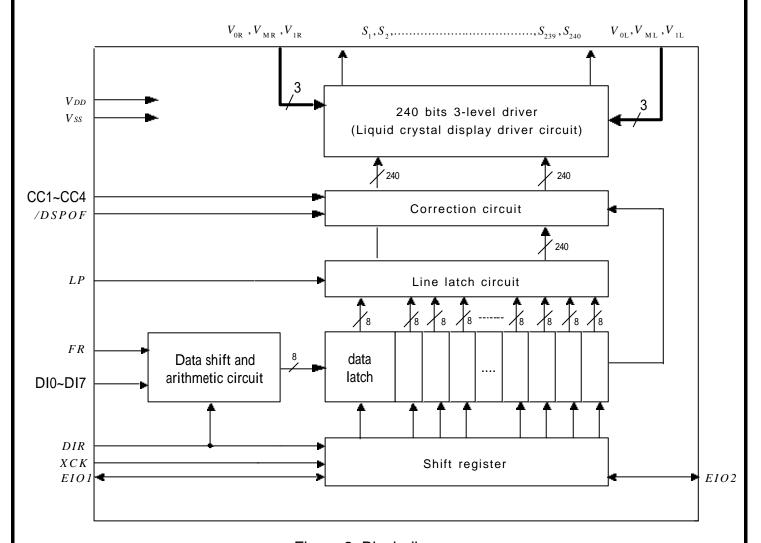

### Functional Block Diagram

Figure 2. Block diagram

### **PinDescriptions**

Table1 pin description

| Symbol                              | Pin No. | I/O | Connected to        |                                                                |  |  |  |  |

|-------------------------------------|---------|-----|---------------------|----------------------------------------------------------------|--|--|--|--|

| $V_{DD}$                            | 264     |     | Power Supply        | Power supply for internal logic connects to                    |  |  |  |  |

|                                     |         |     |                     | +2.7 to +5.5V                                                  |  |  |  |  |

| $V_{SS}$                            | 244     | ı   | GND                 | Connect to Ground                                              |  |  |  |  |

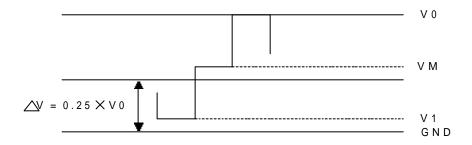

| $V_{0R}$ , $V_{0L}$                 | 266,242 | I   | Power Supply        | Power supply for LCD driver level                              |  |  |  |  |

| $V_{MR}, V_{ML}$                    | 267,241 |     |                     | Ensure that the voltage are set such that                      |  |  |  |  |

| $V_{1R}, V_{1L}$                    | 256,243 |     |                     | $V_1 < V_M < V_0$ , $V_M = 0.5(V_0 - V_1)$                     |  |  |  |  |

| $DI_0 - DI_7$                       | 260 t0  | I   | Controller          | Input for display data                                         |  |  |  |  |

|                                     | 253     |     |                     | input data into 8 pins Dl₀ – Dl <sub>7</sub>                   |  |  |  |  |

| XCK                                 | 252     | I   | Controller          | Clock signal for taking display data                           |  |  |  |  |

|                                     |         |     |                     | Data is read on the falling of the clock                       |  |  |  |  |

|                                     |         |     |                     | pulse                                                          |  |  |  |  |

| LP                                  | 251     |     | Controller          | Latch signal for display data                                  |  |  |  |  |

|                                     |         |     |                     | Data is latched on the falling edge of the                     |  |  |  |  |

|                                     |         |     |                     | clock pulse                                                    |  |  |  |  |

| FR                                  | 250     | l   | Controller          | AC signal for LCD driver                                       |  |  |  |  |

|                                     |         | _   |                     | Input a frame inversion signal                                 |  |  |  |  |

| DIR                                 | 263     |     | Controller          | Directional selection for reading display                      |  |  |  |  |

|                                     |         |     |                     | data                                                           |  |  |  |  |

|                                     |         |     |                     | DIR Data read direction                                        |  |  |  |  |

|                                     |         |     |                     | H S <sub>240</sub> to S <sub>1</sub>                           |  |  |  |  |

| /DCDOE                              | 004     |     | Cantrallar          | L S <sub>1</sub> to S <sub>240</sub>                           |  |  |  |  |

| /DSPOF                              | 261     | I   | Controller          | When the signal is low, the output $(S_1 - S_1)$               |  |  |  |  |

| FIO FIO                             | 000 040 | 1/0 | O a va tiva II a vi | S <sub>240</sub> ) of LCD drive be set to level V <sub>M</sub> |  |  |  |  |

| EIO <sub>1</sub> , EIO <sub>2</sub> | 262,249 | I/O | Controller          | Input/output for chip selection                                |  |  |  |  |

|                                     |         |     |                     | In output state , the output pin must                          |  |  |  |  |

|                                     |         |     |                     | connect to input pin of next EM65H134                          |  |  |  |  |

|                                     |         |     |                     | In input state , the input pin of the fist                     |  |  |  |  |

|                                     |         |     |                     | EM65H134 must connect to Vss , the other                       |  |  |  |  |

|                                     |         |     |                     | input pin must connect to the output pin of                    |  |  |  |  |

|                                     |         |     |                     | previous EM65H134.  DIR EIO <sub>1</sub> EIO <sub>2</sub>      |  |  |  |  |

|                                     |         |     |                     | H output input                                                 |  |  |  |  |

|                                     |         |     |                     | L input output                                                 |  |  |  |  |

|                                     |         |     |                     |                                                                |  |  |  |  |

Table1 pin description (continous)

| · abio · piii at                 | (        | • • • • • • • • • • • • • • • • • • • • |                                                                                                                                                                                           |

|----------------------------------|----------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CC1                              | 248      | I                                       | Rising crosstalk correction signal. The V1 level output is reset to VM level when CC1 is high.                                                                                            |

| CC2                              | 247      | I                                       | Falling crosstalk correction signal. The V0 level output is reset to VM level when CC2 is high.                                                                                           |

| CC3                              | 246      | I                                       | Waveform distortion non-selected (black) data correction signal. The present output pin (non-selected) and the next output pin (non-selected) are reset to the VM level when CC3 is high. |

| CC4                              | 245      | I                                       | Waveform distortion selected (white) data correction signal. The present output pin (selected) and the next output pin (selected) are reset to the VM level when CC4 is high.             |

| S <sub>1</sub> -S <sub>240</sub> | 1 to 240 | 0                                       | LCD driver output.  One of two levels is output according to the combination of the FR signal and display data, when /DSPOF is in V <sub>DD</sub>                                         |

### **FUNCTIONDESCRIPTIONS**

#### - Shift Register

The 30-bit shift register generate latch signal for data latch circuit at the falling edge of XCK signal. The shift direction is selected by DIR signal.

#### - Data Latch

It latches the data on the 8 bits data bus(DI0 to DI7) and output the data to line latch. It is controlled by shift register.

#### - Line Latch

All 240 bits, which have been read into the data latch are simultaneously latched at the falling edge of the LP signal then output to the correction circuit and 3-level driver.

#### - 3-level Driver

Drive LCD panel from driver output pins, selecting one of three levels  $(V_0, V_M, V_1)$  based on the line latch data, correction circuit(CC1 to CC4) and /DSPOF.

#### -Correction Circuit

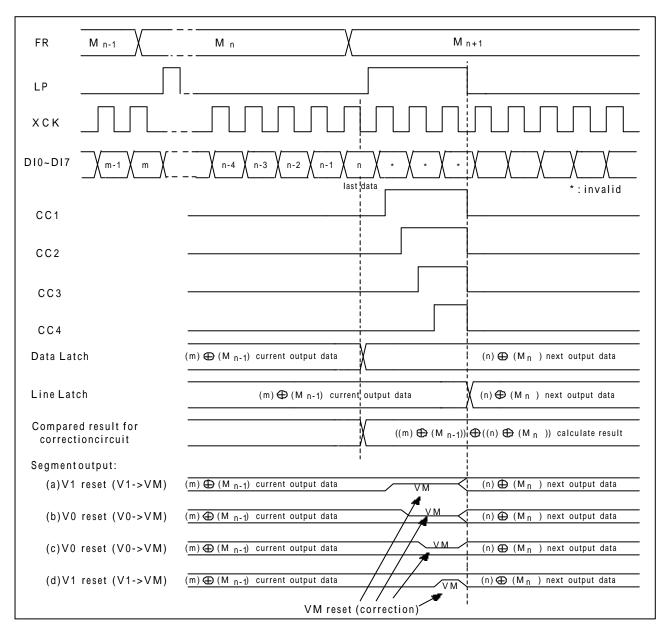

This circuit corrects the shadowing volume.

- 1. The circuit compares the crosstalk correction signals (CC1 and CC2) from the external circuits and present output, and determines whether the effective value is increased due to crosstalk. If the effective value is increased, the output level is reset to the VM level.

- 2. The circuit compares the output data to the next output data. If there are no data changes due to the waveform distortion correction signal (CC3 and CC4), the output level is reset to VM level.

The reset period can be adjusted by using CC1 to CC4. The correction needed depends on each output pin.

#### -Data Shift and Arithmetic Circuit

The data shifter shifts the destinations of data output when necessary. The arithmetic circuit performs operations for the data and FR signal.

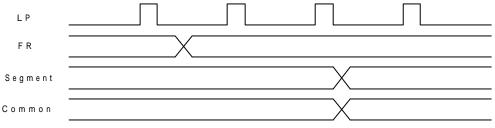

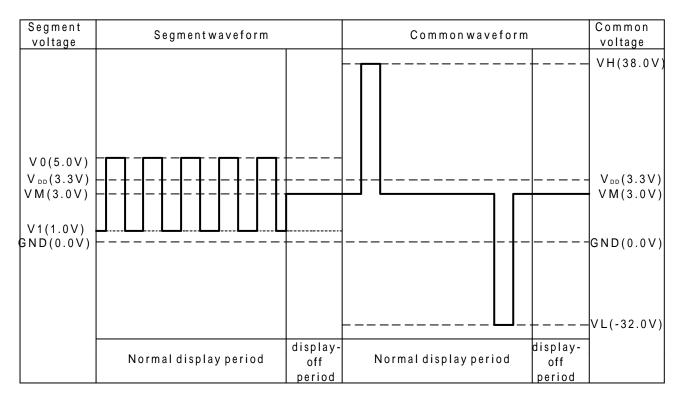

Figure 3. FR, LP, output timing

Relation between FR、latch data、/DSPOF and output level

Table 2 LCD driver output voltage level

| FR | Latch data | /DSPOF | Driver output voltage level |

|----|------------|--------|-----------------------------|

| Н  | Н          | Н      | V <sub>0</sub>              |

| Н  | L          | Н      | $V_1$                       |

| L  | Н          | Н      | $V_1$                       |

| L  | L          | Н      | $V_0$                       |

| Х  | Х          | L      | $V_{M}$                     |

$V_{SS}$   $V_1 < V_M < V_0$   $H:V_{DD}$   $L:V_{SS}$  X:Don'tcare

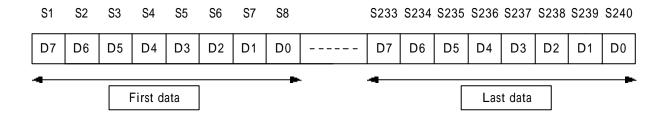

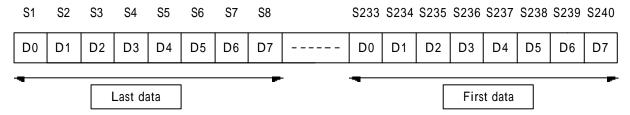

Relationship between the display data and driver output and data output destination

Table 3 Relationship between the display data and driver output

| DIR | EIO1   | EIO2   | Data   |                  |                  | Figu             | ire of c | lock             |                  |                  |

|-----|--------|--------|--------|------------------|------------------|------------------|----------|------------------|------------------|------------------|

|     |        |        | Input  | 1 <sub>st</sub>  | 2 <sub>nd</sub>  | 3 <sub>rd</sub>  |          | 28 <sub>th</sub> | 29 <sub>th</sub> | 30 <sub>th</sub> |

| L   | Input  | Output | $DI_0$ | S <sub>8</sub>   | S <sub>16</sub>  | S <sub>24</sub>  |          | S <sub>224</sub> | S <sub>232</sub> | S <sub>240</sub> |

|     |        |        | $DI_1$ | S <sub>7</sub>   | S <sub>15</sub>  | $S_{23}$         |          | S <sub>223</sub> | S <sub>231</sub> | S <sub>239</sub> |

|     |        |        | $DI_2$ | $S_6$            | S <sub>14</sub>  | S <sub>22</sub>  |          | S <sub>222</sub> | $S_{230}$        | $S_{238}$        |

|     |        |        | $DI_3$ | $S_5$            | S <sub>13</sub>  | S <sub>21</sub>  |          | S <sub>221</sub> | S <sub>229</sub> | S <sub>237</sub> |

|     |        |        | $DI_4$ | $S_4$            | S <sub>12</sub>  | S <sub>20</sub>  |          | $S_{220}$        | $S_{228}$        | $S_{236}$        |

|     |        |        | $DI_5$ | $S_3$            | S <sub>11</sub>  | S <sub>19</sub>  |          | $S_{229}$        | S <sub>227</sub> | S <sub>235</sub> |

|     |        |        | $DI_6$ | $S_2$            | S <sub>10</sub>  | S <sub>18</sub>  |          | S <sub>228</sub> | S <sub>226</sub> | S <sub>234</sub> |

|     |        |        | $DI_7$ | $S_1$            | $S_9$            | S <sub>17</sub>  |          | S <sub>227</sub> | S <sub>225</sub> | $S_{233}$        |

| Н   | Output | Input  | $DI_0$ | $S_{233}$        | S <sub>225</sub> | S <sub>217</sub> |          | S <sub>17</sub>  | $S_9$            | $S_1$            |

|     |        |        | $DI_1$ | S <sub>234</sub> | S <sub>226</sub> | S <sub>218</sub> |          | S <sub>18</sub>  | S <sub>10</sub>  | $S_2$            |

|     |        |        | $DI_2$ | $S_{235}$        | S <sub>227</sub> | S <sub>219</sub> |          | S <sub>19</sub>  | S <sub>11</sub>  | $S_3$            |

|     |        |        | $DI_3$ | S <sub>236</sub> | S <sub>228</sub> | S <sub>220</sub> |          | $S_{20}$         | S <sub>12</sub>  | $S_4$            |

|     |        |        | $DI_4$ | S <sub>237</sub> | S <sub>229</sub> | S <sub>221</sub> |          | S <sub>21</sub>  | S <sub>13</sub>  | $S_5$            |

|     |        |        | $DI_5$ | $S_{238}$        | S <sub>230</sub> | S <sub>222</sub> |          | $S_{22}$         | S <sub>14</sub>  | $S_6$            |

|     |        |        | $DI_6$ | S <sub>239</sub> | S <sub>231</sub> | $S_{223}$        |          | $S_{23}$         | S <sub>15</sub>  | S <sub>7</sub>   |

|     |        |        | $DI_7$ | S <sub>240</sub> | $S_{232}$        | S <sub>224</sub> |          | S <sub>24</sub>  | S <sub>16</sub>  | S <sub>8</sub>   |

### Data output destination

The direction of data latch and the chip enable input/output pin can be select by DIR signal.

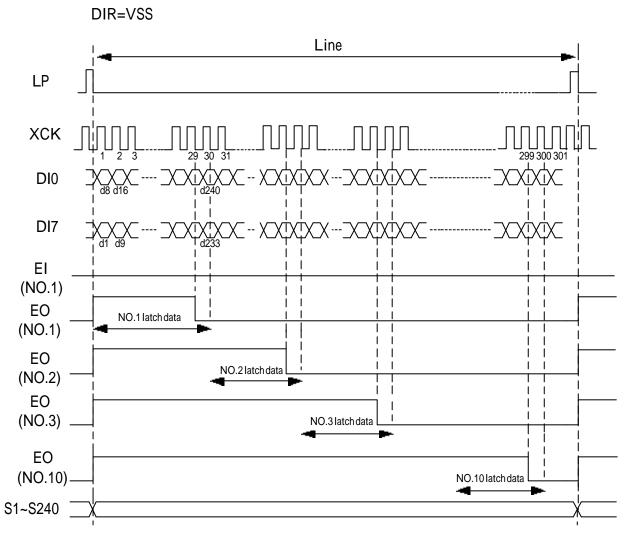

DIR=VSS ,Enable input: EIO1 ,Enable output: EIO2

DIR=VDD ,Enable input: EIO2 ,Enable output: EIO1

Figure 4. Data output destination

### Operating timing

Figure 4 shows the 8-bit data-latch timing when DIR=GND; that is, when the EIO1 pin is a chip-enable input and the EIO2 pin is a chip-enable output. When SHL=V<sub>cc</sub>, the EIO1 pin is a chip-enable output and the EIO2 pin is a chip-enable input.

When a low chip-enable signal is input via the EIO1 pin, the EM65H134 is first released from the data-standby state, then, at the falling edge of the following XCK pulse, it is released entirely from the standby state and starts latching data.

It simultaneously latches eight bits of data at the falling edge of each XCK pulse. When it has latched 232 bits of data, it sets the EIO2 signal to low. When it has latched 240 bits of data, it automatically stops and enters the standby state, initiating the next EM65H134, provided its EIO2 pin is connected to the EIO1 pin of the next EM65H134.

The EM65H134 output one line of data from the S1 to S240 pins at the falling edge of each LP pulse. Data d1 is output from S1, and d240 from S240 when SHL=GND, and d1 is output from S240, and d240 from S1 when DIR=  $V_{cc.}$

Figure 5. Data latch timing

#### Correction circuit

The EM65H134 include shadowing correction circuits. There are two types of shadowing: one caused by crosstalk, and the other by waveform distortion. In both types, image quality can be improved by correction circuits CC1, CC2, CC3, and CC4.

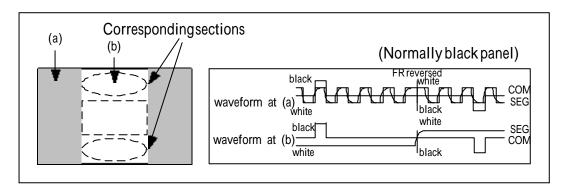

(1) CC1 and CC2(Shadowing caused by crosstalk)

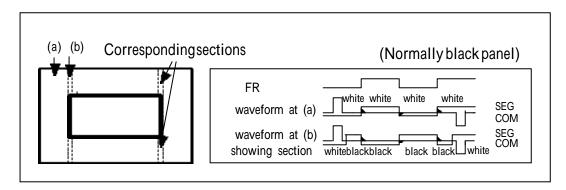

Figure 6. Shadowing caused by crosstalk

When a ruled line is displayed, noise occurs in the common VM level in the LCD panel due to the segment change of a solid background in FR reverse. This is because many segments display the solid background and are simultaneously changed, affecting the common VM level (creating crosstalk). The effective voltage for section (a) in the solid background becomes low. On the other hand, the effective voltage for section (b) becomes high. Shadowing occurs in the corresponding sections due to the different voltages.

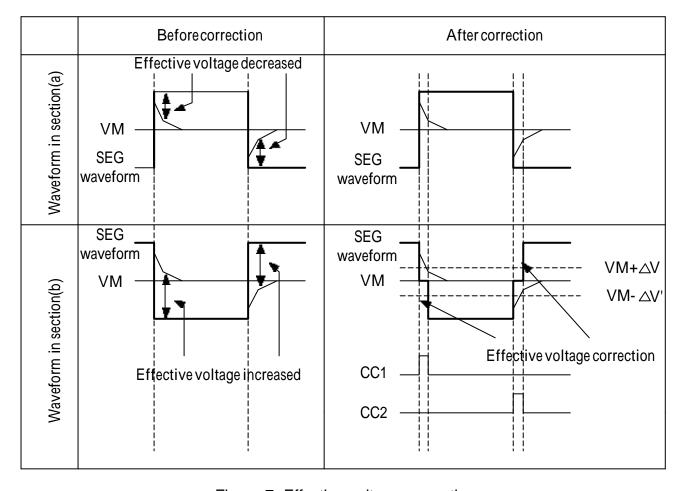

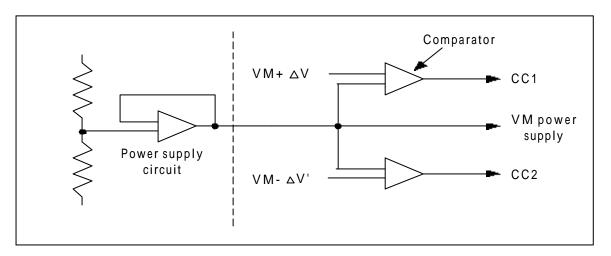

The EM65H134s compare the crosstalk correction signals CC1 and CC2 and the present output, and determine whether the effective value is increased by the crosstalk. If increased, the output level is reset to the VM, which corrects the effective voltages in (a) and (b) and suppresses the shadowing. Figure 8 shows an example of the crosstalk-correction-signal external circuit. The basic potentials of a comparator (VM+ V and VM - V') are corrected according to the shadowing level for output correction while CC1 and CC2 are high. CC1 corrects the rising crosstalk, and CC2 corrects the falling crosstalk.

Figure 7. Effective voltage correction

Figure 8. CC1 and CC2 external circuit

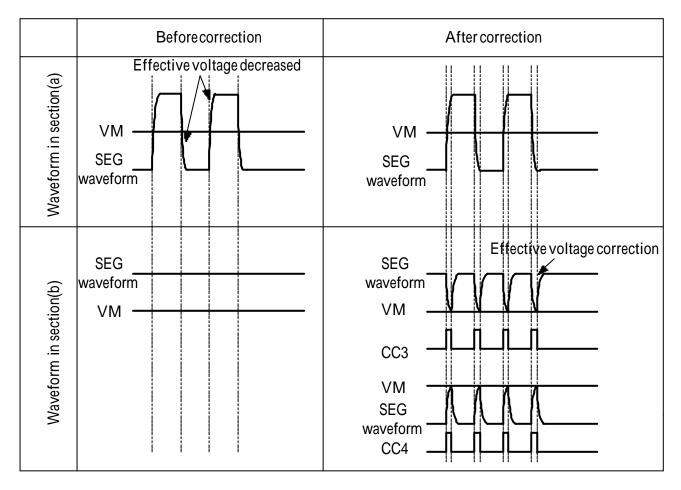

(2) CC3 and CC4(shadowing caused by waveform distortion)

Figure 9. Shadowing caused by waveform distortion

When the background is displayed in grayscale (for example, in a checker pattern), many segment levels are changed in section (a) but not in section (b). The effective voltage for section (a) becomes low because distortion occurs in the segment output waveform due to driver or panel impedance. On the other hand, the effective voltage for section (b) becomes high because the waveform is changed only slightly. Shadowing occurs in the corresponding sections due to the different voltages.

The EM65H134 compare the present output data and the next output data. If the data is not changed, the output level is reset to the VM, which corrects the effective voltages in (a) and (b). The high width is corrected according to the shadowing level for output correction while CC3 and CC4 are high. CC3 corrects the ron-selected output pin (black background), and CC4 corrects the selected output pin (white background).

Figure 10. Effective voltage correction by waveform distortion

Figure 11. Compared result for correction circuit

The correction circuit compares the present output data (line latch) and the next output data (data latch). Depending on the compared result, the circuit resets the high width of CC3 to the VM for the output without a data change if the data is the non-selected output ((c) in figure 12). The circuit resets the high width of CC4 to the VM if the data is the selected output ((d) in figure 12). CC3 and CC4 are input after the last valid data is transferred. CC1 forcibly resets the V1 output to for the high width ((a) in the figure 12). CC2 forcibly resets the V0 output to VM for the high width ((b) in figure 12). Therefore, shadowing caused by waveform distortion is corrected with CC3 or CC4 (non-selected or selected), and shadowing caused by crosstalk is corrected with CC1 or CC2 (in the V0 or V1 direction).

Note: The high period from CC1 to CC4 should be matched with the shadowing level.

### **AbsoluteMaximumratings**

Table 4 absolute maximum ratings

| Parameter             | Symbol            | Conditions   | Applicable pins                                | Ratings                | Unit |

|-----------------------|-------------------|--------------|------------------------------------------------|------------------------|------|

| Supply voltage (1)    | $V_{\mathrm{DD}}$ | Referenced   | V <sub>DD</sub> *1,*2                          | -0.3  to  +7.0         | V    |

| Supply voltage (2)    | $V_0$             | to           | $V_{0L}, V_{0R}$ *1,*2                         | -0.3 to +7.0           | V    |

| Input voltage(1)      | $V_{I1}$          | $V_{SS}(0V)$ | XCK, LP,DIR,FR, EIO <sub>1</sub>               | $-0.3$ to $V_{DD}+0.3$ | V    |

|                       |                   |              | EIO <sub>2</sub> , DI <sub>0-7</sub> ,/DSPOF,  |                        |      |

|                       |                   |              | CC1 to CC4 *:                                  |                        |      |

| Input voltage(2)      | $V_{I2}$          |              | $V_{ML}$ , $V_{MR}$ , $V_{1L}$ , $V_{1R}$ *1,* | 2 -0.3 to $V_0+0.3$    | V    |

| Operating temperature | $T_{opr}$         |              |                                                | -30to +75              |      |

| Storage temperature   | $T_{stg}$         |              |                                                | -55 to +110            |      |

- Note: 1. if the LSI is used beyond the above maximum ratings, it may be permanently damaged. It should always be used within it's specified operating range for normal operation to prevent malfunctions or degraded reliability.

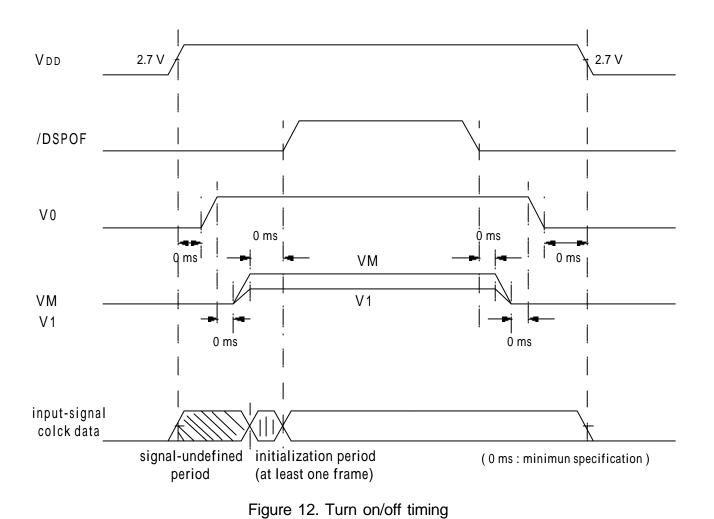

- 2. As show in figure 11, user should conform to the following turn on/off sequence for the power and signal. Otherwise, the LSI will malfunction or will be permanently damaged. In addition, the LSI reliability will be affected.

- 3. Turn on the power:

- (1) Turn on the power in the order of GND-VDD, GND-V0, and VM/V1. THEN ground the /DSPOF pin.

- (2) The LCD forcibly outputs the VM level by the DISPLAYOFF function.

- (3) Even an input signal disturbed immediately after VDD is applied, the DISPLAYOFF function has priority.

- (4) Input the specific signal to initialize the registers in the driver. The initialization period must be at lease one frame.

- (5) The preparation for the normal display is completed. Apply the VDD level to the /DSPOF pin to cancel the DISPLAYOFF function. At this time, the level of pin V0, VM and V1 must rise to the specific potential.

- 4. Turn off the power:

The procedure is basically the reverse of that used to turn on the power.

- (1) Ground the /DSPOF pin.

- (2) Turn off the LCD power in the order of VM/V1 and GND-V0.

- (3) Ground VDD and an input signal.

At this time, the level of pin V0, VM and V1 must fall to 0V. Since the DISPLAYOFF function stops when VDD fall to 0V, the LCD may output a level other than VM. Therefore, a display failure may occur when the power is turn off or on.

### **DCCHARACTERISTICS**

Table 5 DC characteristics 1

$(V_{SS} = GND=0V, V_{DD} = +2.7 \text{ to } +4.5V, V_0 - Vss = 3.5 \text{ to } 5.5V, T_a = -30 \sim +75 °C)$

| Poromotor     | Symbol           | Car                     | ditions                               | Applicable pine                             | Min          | Type | Mov         | Hnit |

|---------------|------------------|-------------------------|---------------------------------------|---------------------------------------------|--------------|------|-------------|------|

| Parameter     | Symbol           | Col                     | nditions                              | Applicable pins                             | Min          | Type | Max         | Unit |

| Input voltage | $V_{IH}$         |                         |                                       | $DI_0$ - $DI_7$ , XCK,                      | $0.7V_{DD}$  |      | $V_{DD}$    | V    |

|               | $V_{IL}$         |                         |                                       | LP,DIR,FR,EIO <sub>1</sub> ,                | 0            |      | $0.3V_{DD}$ | ٧    |

|               |                  |                         |                                       | EIO <sub>2</sub> , /DSPOF,                  |              |      |             |      |

|               |                  |                         |                                       | CC1 to CC4                                  |              |      |             |      |

| Output        | \/ .             | I <sub>OH</sub> =-0.4m  | Λ                                     | EIO <sub>1</sub> , EIO <sub>2</sub>         | V 0          |      |             | V    |

| •             | $V_{OH}$         | IOH=-0.411              | A                                     | $\square \square_1, \square \square_2$      | $V_{DD}$ -0. |      |             | V    |

| voltage       |                  |                         |                                       |                                             | 4            |      |             |      |

|               | $V_{OL}$         | $I_{OL}=+0.4n$          | 1A                                    |                                             |              |      | +0.4        | V    |

| Input leakage | $I_{IL1}$        | $V_I = V_{DD} - V_{DD}$ | / <sub>SS</sub>                       | DI <sub>0</sub> -DI <sub>7</sub> , XCK, LP, | -5           |      | +5          | uA   |

| current (1)   |                  |                         |                                       | DIR, FR, MD, EIO <sub>1</sub> ,             |              |      |             |      |

| ( )           |                  |                         |                                       | EIO <sub>2</sub> , /DSPOF                   |              |      |             |      |

| Input leakage | I <sub>IL2</sub> | $V_1 = V_0 - V_S$       | _                                     | $V_{ML}, V_{MR}, V_{1L}, V_{1R}$            | -100         |      | +100        | uA   |

|               | 1112             | v  - v0                 | S                                     | VML, VMR, V1L, V1R                          | 100          |      | 1 100       | uA   |

| current (2)   |                  |                         | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \       |              | 0.5  | 4.0         |      |

| Output        | R <sub>ON</sub>  | I <sub>ON</sub> =       | $V_{0R}, V_{OL}$                      | Y <sub>1</sub> - Y <sub>240</sub>           |              | 0.5  | 1.0         | k    |

| resistance    | *1               | 150uA                   | $V_{MR}, V_{ML}$                      |                                             |              | 1.0  | 2.0         |      |

|               |                  |                         | $V_{1R}, V_{1L}$                      |                                             |              | 0.5  | 1.0         |      |

| Stand-by      | I <sub>STB</sub> | $VI = V_{DD}$           | $V_{DD}=3V$                           | $V_{DD}$                                    |              | 0.4  | 1.0         | mΑ   |

| current       | *2 *3            | 1 1 00                  | f <sub>XCK</sub> =25MHZ               |                                             |              |      |             |      |

| Consumed      | _                | \/I <b>-</b> \/cc       | f <sub>LP</sub> =100KHZ               | $V_{DD}$                                    |              | 1.0  | 6.0         | mA   |

|               | I <sub>DD</sub>  | VI – VSS                |                                       | v DD                                        |              | 1.0  | 0.0         | шд   |

| current       | *2 *3            |                         | f <sub>FR</sub> =4kHZ                 |                                             |              |      |             |      |

| Consumed      | $I_0$            |                         |                                       | $V_{0L}$ , $V_{0R}$                         |              | 0.4  | 1.0         | mΑ   |

| current       | *2               |                         |                                       |                                             |              |      |             |      |

### Table 6 DC characteristics 2

$(V_{SS} = GND = 0V, V_{DD} = 4.5V \text{ to } 5.5V, V_0 - Vss = 3.5 \text{ to } 5.5V, T_a = -30 - +75 ^{\circ}C)$

| Parameter     | Symbol           | Cor                                 | nditions                | Applicable pins                             | Min          | Type | Max         | Unit |

|---------------|------------------|-------------------------------------|-------------------------|---------------------------------------------|--------------|------|-------------|------|

| Input voltage | V <sub>IH</sub>  |                                     |                         | DI <sub>0</sub> -DI <sub>7</sub> , XCK,     | $0.7V_{DD}$  |      | $V_{DD}$    | V    |

|               | $V_{IL}$         |                                     |                         | LP,DIR,FR,EIO₁,                             | 0            |      | $0.3V_{DD}$ | V    |

|               |                  |                                     |                         | EIO <sub>2</sub> , /DSPOF,                  |              |      |             |      |

| Output        | 17               | 1 0.4m                              | Λ.                      | CC1 to CC4                                  | \/ O         |      |             | V    |

| Output        | V <sub>OH</sub>  | I <sub>OH</sub> =-0.4m              | A                       | EIO <sub>1</sub> , EIO <sub>2</sub>         | $V_{DD}$ -0. |      |             | V    |

| voltage       | V <sub>OL</sub>  | I <sub>OI</sub> =+0.4m              | ٠,٨                     | 1                                           | 4            |      | +0.4        | V    |

| Input leakage | I <sub>IL1</sub> | V <sub>I=</sub> V <sub>DD</sub> - \ |                         | DI <sub>0</sub> -DI <sub>7</sub> , XCK, LP, | -5           |      | +5          | uA   |

| current (1)   | 'IL1             |                                     | 55                      | DIR, FR, MD, EIO <sub>1</sub> ,             |              |      | 1.0         | uA   |

| ( )           |                  |                                     |                         | EIO <sub>2</sub> , /DSPOF                   |              |      |             |      |

| Input leakage | $I_{IL2}$        | $V_I = V_0 - V_S$                   | S                       | $V_{ML}, V_{MR}, V_{1L}, V_{1R}$            | -100         |      | +100        | uA   |

| current (2)   |                  |                                     |                         |                                             |              |      |             |      |

| Output        | R <sub>ON</sub>  | $I_{ON} =$                          | $V_{0R}, V_{OL}$        | Y <sub>1</sub> - Y <sub>240</sub>           |              | 0.5  | 1.0         | k    |

| resistance    | *1               | 150uA                               | $V_{MR}, V_{ML}$        |                                             |              | 1.0  | 2.0         |      |

|               |                  |                                     | $V_{1R}, V_{1L}$        |                                             |              | 0.5  | 1.0         |      |

| Stand-by      | I <sub>STB</sub> | $VI = V_{DD}$                       | $V_{DD}=5V$             | $V_{DD}$                                    |              | 1.0  | 2.0         | mΑ   |

| current       | *2 *3            |                                     | f <sub>XCK</sub> =40MHZ |                                             |              |      |             |      |

| Consumed      | I <sub>DD</sub>  | VI = Vss                            | f <sub>LP</sub> =160KHZ | $V_{DD}$                                    |              | 3.0  | 15          | mA   |

| current       | *2 *3            |                                     | f <sub>FR</sub> =6kHZ   |                                             |              |      |             |      |

| Consumed      | I <sub>0</sub>   |                                     |                         | $V_{0L}$ , $V_{0R}$                         |              | 0.4  | 2.0         | mA   |

| current       | *2               |                                     |                         |                                             |              |      |             |      |

Note: 1. Indicate the resistance between one of thwe pins Y1~Y240 and one of the voltage supply pins,when load current is applied to the Y pins. Defined under the following conditions:

$$V0-Vss = 5.5V$$

;  $VM = (V0=V1)/2$ ;  $V1 = Vss+1$

- V1 should be near the ground level, VM should be near the middle voltage between V1 and V0. V1should be within the range of V = 2.5V0, which is the range within which  $R_{ON}$ , the LCD driver circuit's output impedance, is stable. See figure 13

- 2. Input and output are excluded. When a CMOS input is left floating, excess the current flows from the power supply through the input circuit. To avoid this, VIH and VIL must be used at VDD and Vss, respectively.

- 3. VI = enable input,. When DIR = Vss, VI = EIO1. When DIR =  $V_{DD}$ , VI = EIO2

- 4. The voltage of each signal is show in figure 14

Figure 13.Relationship between driver output waveform and each level voltage

Figure 14. Signal voltage

### **ACElectricalcharacteristic**

Table 7 AC electrical characteristics 1

$(V_{SS} = GND=0V, V_{DD} = 2.7 \text{ to } 4.5V, V_0 - Vss = 3.5 \text{ to } 5.5V, T_a = 30~75^{\circ}C)$

| •                               |                   | •                     |     |     | ,   |      |

|---------------------------------|-------------------|-----------------------|-----|-----|-----|------|

| Parameter                       | Symbol            | Condition             | Min | Тур | Max | Unit |

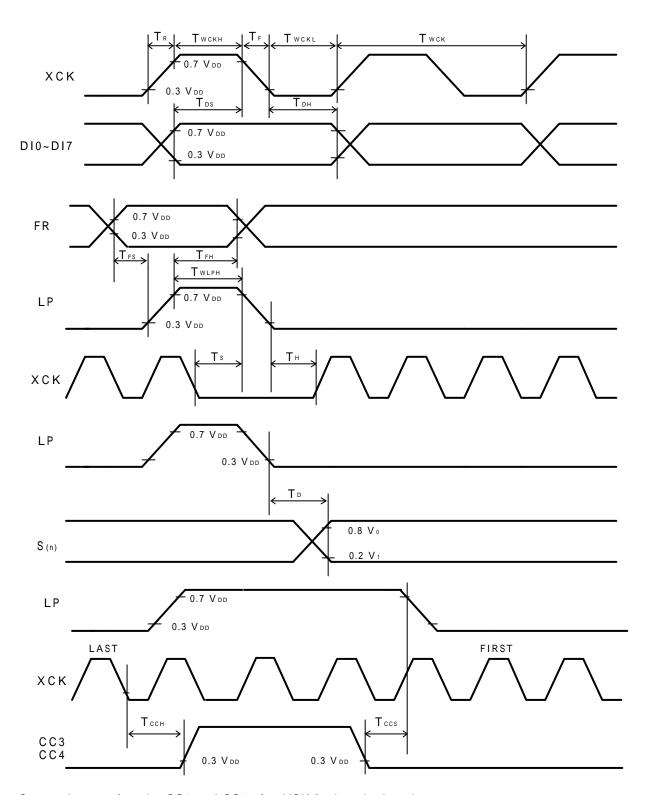

| Shift clock period              | T <sub>WCK</sub>  |                       | 40  |     |     | ns   |

| Shift clock "H" pulse width     | T <sub>WCKH</sub> |                       | 15  |     |     | ns   |

| Shift clock "L" pulse width     | T <sub>WCKL</sub> |                       | 15  |     |     | ns   |

| Data setup time                 | $T_{DS}$          |                       | 10  |     |     | ns   |

| Data hold time                  | $T_DH$            |                       | 10  |     |     | ns   |

| Latch pulse "H" pulse width     | $T_{WLPH}$        |                       | 30  |     |     | ns   |

| Shift and latch clock set up    | $T_S$             |                       | 20  |     |     | ns   |

| time                            |                   |                       |     |     |     |      |

| Shift and latch clock hold time | T <sub>H</sub>    |                       | 50  |     |     | ns   |

| Shift and latch clock rise time | $T_R$             |                       |     |     | 30  | ns   |

| Shift and latch clock fall time | $T_F$             |                       |     |     | 30  | ns   |

| FR set up time                  | $T_{FS}$          |                       | 20  |     |     | ns   |

| FR hold time                    | $T_FH$            |                       | 20  |     |     | ns   |

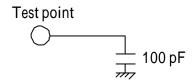

| Output delay time               | $T_D$             | C <sub>L</sub> =100pF |     |     | 500 | ns   |

| CC setup time                   | T <sub>CCS</sub>  |                       | 20  |     |     | ns   |

| CC hold time                    | T <sub>CCH</sub>  |                       | 20  |     |     | ns   |

#### Table 8 AC electrical characteristics 2

$(V_{SS} = GND = 0V, V_{DD} = 4.5 \text{ to } 5.5V, V_0 - Vss = 3.5 \text{ to } 5.5V, T_a = 30 \sim 75^{\circ}C)$

| Parameter                       | Symbol            | Condition             | Min | Тур | Max | Unit |

|---------------------------------|-------------------|-----------------------|-----|-----|-----|------|

| Shift clock period              | $T_{WCK}$         |                       | 25  |     |     | ns   |

| Shift clock "H" pulse width     | $T_{WCKH}$        |                       | 10  |     |     | ns   |

| Shift clock "L" pulse width     | T <sub>WCKL</sub> |                       | 10  |     |     | ns   |

| Data setup time                 | $T_{DS}$          |                       | 6   |     |     | ns   |

| Data hold time                  | $T_DH$            |                       | 6   |     |     | ns   |

| Latch pulse "H" pulse width     | $T_{WLPH}$        |                       | 25  |     |     | ns   |

| Shift and latch clock set up    | $T_S$             |                       | 20  |     |     | ns   |

| time                            |                   |                       |     |     |     |      |

| Shift and latch clock hold time | T <sub>H</sub>    |                       | 50  |     |     | ns   |

| Shift and latch clock rise time | $T_R$             |                       |     |     | 20  | ns   |

| Shift and latch clock fall time | $T_F$             |                       |     |     | 20  | ns   |

| FR set up time                  | $T_{FS}$          |                       | 20  |     |     | ns   |

| FR hold time                    | $T_FH$            |                       | 20  |     |     | ns   |

| Output delay time               | $T_D$             | C <sub>L</sub> =100pF |     |     | 500 | ns   |

| CC setup time                   | T <sub>CCS</sub>  |                       | 20  |     |     | ns   |

| CC hold time                    | T <sub>CCH</sub>  |                       | 20  |     |     | ns   |

NOTES: 1. The load must be less than 10 pF between the EIO1 and EIO2 connections of the EM65H134s.

2. connect the load circuit as shown in figure 15.

Figure 15. Load circuit for output delay time

### **Timing diagram**

Correct the waveform by CC3 and CC4 after XCK fetches the last data.

Complete correction before data from the next line is output at the falling edge of LP.

Figure 16. AC characteristics

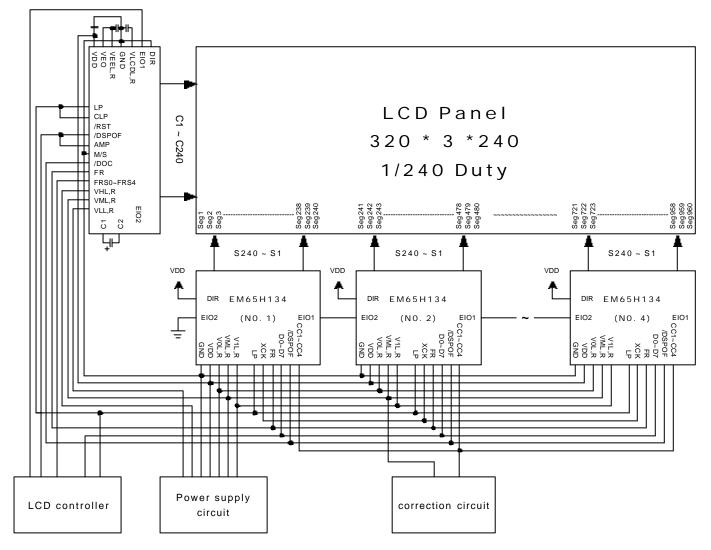

### **Applicationcircuit**

Figure 17. Application circuit