# IMI145156

SERIAL INPUT PLL FREQUENCY SYNTHESIZER

T-50-17

### PRODUCT FEATURES ---

- >30 MHz Typical Input Capability @ V<sub>DD</sub> = 5V

- On- or Off-Chip Reference Oscillator Operation with Buffered Output

- Compatible with the SPI (Serial Peripheral Interface) on CMOS MCU's

- Lock Detect Signal

- Two Open-Drain Switch Outputs

- Dual Modulus/Serial Programming

- 8 User-Selectable ÷R Values: 8, 64, 128, 256, 640, 1000, 1024, 2048

- ÷N Range = 3 to 1023; ÷A Range = 0 to 127

- Linearized Digital Phase Detector Enhances Transfer Function Linearity

- Two Error Signal Options: Single-Ended (3-State), Double-Ended

- Packaging Options Include: Plastic and Ceramic Dual-In-Line, Plastic J-Leaded, and Ceramic Leadless Chip Carriers, and Small-Outline Packages. Die are available for Hybrid Applications.

- Grades Available Include: Commercial, Military Operating Range, and Military Screened

### PRODUCT DESCRIPTION\*

The IMI145156 is one of a family of LSI PLL frequency synthesizers from International Microcircuits. In the 20-pln ceramic or plastic dual-in-line packages, this product is pin-for-pin compatible with the MC145156, and can be used as a direct replacement with identical or superior operating characteristics. This product can be alternatively packaged to meet your needs. MIL-STD-883 screening is available for high-reliability applications.

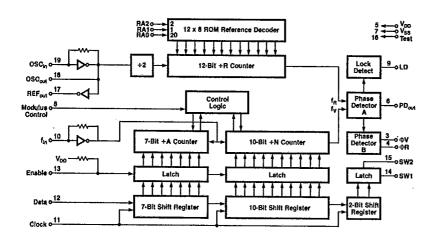

The IMI145156 is programmed by a clocked, serial input 19-bit data stream. The device features a reference oscillator, selectable-reference divider, digital-phase detector, 10-bit programmable ÷N counter and 7-bit programmable ÷A counter, and the necessary shift register and latch circuitry for accepting the serial input data. When combined with a loop filter and VCO, the IMI145156 can provide all the remaining functions for a PLL frequency synthesizer operating up to the device's frequency limit. For higher VCO frequency operation, a down mixer or a dual modulus prescaler can be used between the VCO and IMI145156.

The IMI145155, IMI145156, IMI145157, and IMI145158 CMOS PLL frequency synthesizers have serial programmable inputs with a single or dual modulus capability, transmit/receive offsets, selection of phase detector type, and choice of reference divider integer values.

If your application requires additional features, please contact our factory. Our engineers can quickly design a product to meet your requirements.

### BLOCK DIAGRAM

| MAXIMUM RATINGS                |                  |                           |      |  |  |  |  |

|--------------------------------|------------------|---------------------------|------|--|--|--|--|

| Rating                         | Symbol           | Value                     | Unit |  |  |  |  |

| DC Supply Voltage              | V <sub>DD</sub>  | -0.5 to +10               | Vdc  |  |  |  |  |

| Input Voltage,<br>All Inputs   | V <sub>iri</sub> | $-0.5$ to $V_{DD}$ $+0.5$ | Vdc  |  |  |  |  |

| Operating Temperature<br>Range | TA               | -55 to +125               | °C   |  |  |  |  |

| Storage Temperature<br>Range   | T <sub>stg</sub> | -65 to +150               | °C   |  |  |  |  |

(Voltage Referenced to V<sub>SS</sub>)

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, V<sub>in</sub> and V<sub>out</sub> should be constrained to the range:

$V_{SS} < (V_{in} \text{ or } V_{out}) < V_{DD}$

Unused inputs must always be tied to an appropriate logic voltage level (either  $V_{SS}$  or  $V_{DD}$ ).

| Se Lighting                                                                                                | المِيْدُرِد 🅶 الع |             | ECI                     | <b>IRIC</b>          | AL                      | CHA                  | <b>IRA</b> (                                  | HE:                  |                      | CS<                     | <b>b</b>             |                         | 1                    | Υ.,        |

|------------------------------------------------------------------------------------------------------------|-------------------|-------------|-------------------------|----------------------|-------------------------|----------------------|-----------------------------------------------|----------------------|----------------------|-------------------------|----------------------|-------------------------|----------------------|------------|

| Characteristic                                                                                             | Symbol            | Vpp         | -5                      | 5°C                  | -40                     |                      |                                               | 25°C                 |                      | 85                      |                      | 125                     |                      | Units      |

| Citalacteristic                                                                                            | Syllibor .        | עטי         | Min                     | Max                  | Min                     | Max                  | Min                                           | Тур                  | Max                  | Min                     | Max                  | Min                     | Max                  |            |

| Power Supply<br>Voltage                                                                                    | V <sub>DD</sub>   | _           | 3                       | 8                    | 3                       | 8                    | 3                                             |                      | 8                    | 3                       | 8                    | 3                       | 8                    | Vdc        |

| Output Voltage<br>V <sub>in</sub> ≓ V <sub>DD</sub> or 0                                                   | V <sub>OL</sub>   | 3<br>5<br>8 | _                       | 0.05<br>0.05<br>0.05 | =                       | 0.05<br>0.05<br>0.05 | _                                             | 0<br>0<br>0          | 0.05<br>0.05<br>0.05 | =                       | 0.05<br>0.05<br>0.05 | =                       | 0.05<br>0.05<br>0.05 | Vdc        |

| $V_{in} = 0$ or $V_{DD}$                                                                                   | VoH               | 3<br>5<br>8 | 2.95<br>4.95<br>7.95    | =                    | 2.95<br>4.95<br>7.95    | =                    | 2.95<br>4.95<br>7.95                          | 3<br>5<br>8          | =                    | 2.95<br>4.95<br>7.95    | _                    | 2.95<br>4.95<br>7.95    |                      | 140        |

| Input Voltage<br>V <sub>O</sub> = 2.5 or 0.5<br>V <sub>O</sub> = 4.5 or 0.5<br>V <sub>O</sub> = 7.5 or 1.5 | V <sub>IL</sub>   | 3<br>5<br>8 | -<br>-<br>-             | 0.9<br>1.5<br>2.4    | =                       | 0.9<br>1.5<br>2.4    | 111                                           | 1.35<br>2.75<br>3.65 | 0.9<br>1.5<br>2.4    | <u>-</u>                | 0.9<br>1.5<br>2.4    | _<br>                   | 0.9<br>1.5<br>2.4    | Vdc        |

| $V_O = 0.5 \text{ or } 2.5$<br>$V_O = 0.5 \text{ or } 4.5$<br>$V_O = 1.5 \text{ or } 7.5$                  | VIH               | 3<br>5<br>8 | 2.1<br>3.5<br>5.6       | -                    | 2.1<br>3.5<br>5.6       | _                    | 2.1<br>3.5<br>5.6                             | 1.65<br>2.75<br>4.45 | =                    | 2.1<br>3.5<br>5.6       |                      | 2.1<br>3.5<br>5.6       |                      | Vuc        |

| Output Current VOH = 2.7 VOH = 4.6 VOH = 7.5                                                               | Юн                | 3<br>5<br>8 | -1.6<br>2,4<br>4.8      | 111                  | -1.6<br>-2.4<br>-1.6    |                      | -1.4<br>-2.0<br>-3.6                          | -2.0<br>-2.8<br>-4.6 | _                    | -0.8<br>-1.6<br>-2.8    | 111                  | -0.8<br>-1.6<br>-2.8    |                      |            |

| V <sub>OH</sub> = 2.7 REF <sub>out</sub><br>V <sub>OH</sub> = 4.6 only<br>V <sub>OH</sub> = 7.5            | Гон               | 3<br>5<br>8 | -0.5<br>-1.1<br>-1.7    | 111                  | -0.45<br>-1.00<br>-1.55 | 111                  | -0.35<br>-0.60<br>-1.10                       | 1 1 1                | =                    | -0.28<br>-0.50<br>-0.90 | 1   1                | -0.28<br>-0.50<br>-0.90 | <del>-</del>         |            |

| V <sub>OH</sub> = 2.7 OSC <sub>out</sub><br>V <sub>OH</sub> = 4.6 only<br>V <sub>OH</sub> = 7.5            | Юн                | 3<br>5<br>8 | -0.17<br>-0.30<br>-0.35 | 1 1                  | -0.16<br>-0.28<br>-0.34 | <u> </u>             | 125<br>225<br>300                             | =                    |                      | 090<br>-0.18<br>-0.25   |                      | 090<br>-0.18<br>-0.25   |                      | mAdo       |

| V <sub>OL</sub> = 0.3<br>V <sub>OL</sub> = 0.4<br>V <sub>OL</sub> = 0.5                                    | loL               | 3<br>5<br>8 | 1.6<br>2.4<br>4.8       | 111                  | 1.6<br>2.4<br>4.8       | 1 1                  | 1.4<br>2.0<br>3.6                             | 2.0<br>2.8<br>4.6    |                      | 0.8<br>1.6<br>2.8       |                      | 0.8<br>1.6<br>2.8       | 1 - 1                |            |

| $V_{OL} = 0.3 \text{ REF}_{out}$<br>$V_{OL} = 0.4 \text{ onty}$<br>$V_{OL} = 0.5$                          | loL               | 3<br>5<br>8 | 0.6<br>1.1<br>2.2       | 111                  | 0.55<br>1.00<br>2.10    | 111                  | 0.42<br>0.90<br>1.70                          | _<br>_<br>_          |                      | 0.28<br>0.70<br>1.40    | <u>-</u>             | 0.28<br>0.70<br>1.40    | _<br>_<br>_          |            |

| $V_{OL} = 0.3 \text{ OSC}_{out}$<br>$V_{OL} = 0.4 \text{ only}$<br>$V_{OL} = 0.5$                          | loL               | 3<br>5<br>8 | 0.320<br>0.480<br>0.600 | 111                  | 0.310<br>0.470<br>0.580 | <u> </u>             | 0,250<br>0,400<br>0,500                       | <u>-</u>             | =                    | 0.180<br>0.300<br>0.400 | =                    | 0.180<br>0.300<br>0.400 | =                    |            |

| Input Current<br>Enable                                                                                    | I <sub>IL</sub>   | 8           | 1                       | -400                 | _                       | -400                 | _                                             | -90                  | 200                  |                         | -170                 |                         | -170                 |            |

| f <sub>in</sub> , OSC <sub>in</sub>                                                                        | IN                | 8           | _                       | ±50                  |                         | ±50                  |                                               | ±10                  | ±25                  |                         | ±22                  | <u> </u>                | ±22                  |            |

| Other Inputs                                                                                               | Iн                | 8           |                         | ±0.3                 |                         | ±0.3                 | <u>                                      </u> | ±.00001              | ±0.1                 |                         | ±1.0                 |                         | ±1.0                 | μAdd       |

| Input Capacitance                                                                                          | Cin               | 3-8         |                         | 10                   | _                       | 10                   |                                               | 6                    | 10                   |                         | 10                   |                         | 10                   | pF         |

| Output Capacitance 3-State Leakage                                                                         | C <sub>out</sub>  | 3-8<br>8    | <del>  -</del>          | ±0.1                 | _                       | 10<br>±0.1           | <u> </u>                                      | 6<br>±0.0001         | 10<br>±0.1           | <u> </u>                | ±10                  | <u> </u>                | 10<br>±10            | pF<br>μAdd |

| Quiescent Current<br>(Static)                                                                              | IDD               | 8           |                         | 150                  | _                       | 150                  | _                                             | 40                   | 150                  |                         | 150                  | _                       | 150                  | μAdd       |

| SWITCHING CHA                                                                     | ARACT                                | ERIS            | TICS-           | THE PARTY         | er Præss og er    |       |

|-----------------------------------------------------------------------------------|--------------------------------------|-----------------|-----------------|-------------------|-------------------|-------|

| Characteristic                                                                    | Symbol                               | V <sub>DD</sub> | Min             | Тур               | Max               | Units |

| Output Rise and Fall Time<br>OSC <sub>out</sub> REF <sub>out</sub>                | t <sub>TLH</sub>                     | 3<br>5<br>8     |                 | 30<br>20<br>10    | 40<br>30<br>20    |       |

| Others                                                                            | t <sub>THL</sub>                     | 3<br>5<br>8     | _<br>_          | 15<br>10<br>5     | 20<br>15<br>10    | ns    |

| Propagation Delay Time<br>f <sub>in</sub> to Modulus Control                      | t <sub>PLH</sub><br>t <sub>PHL</sub> | 3<br>5<br>8     |                 | 55<br>40<br>25    | 125<br>.80<br>50  | ns    |

| Propagation Delay Time<br>Enable to SW1, SW2                                      | t <sub>PHL</sub>                     | 3<br>5<br>8     |                 | 40<br>30<br>20    | 100<br>60<br>40   | ns    |

| Setup Time<br>Data to Clock                                                       | tsu                                  | 3<br>5<br>8     | 50<br>40<br>30  | 20<br>10<br>9     | _                 | ns    |

| Clock to Enable                                                                   | t <sub>SU</sub>                      | 3<br>5<br>8     | 100<br>50<br>30 | 30<br>15<br>10    |                   | лs    |

| Hold Time<br>Clock to Data                                                        | tн                                   | 3<br>5<br>8     | 10<br>15<br>20  | 5<br>8<br>10      |                   | ns    |

| Recovery Time<br>Enable to Clock                                                  | t <sub>REC</sub>                     | 3<br>5<br>8     | 10<br>15<br>20  | -2<br>-3<br>-3    | -<br>-            | ns    |

| Output Pulse Width<br>PHIR, PHIV with f <sub>R</sub> in Phase with f <sub>V</sub> | t <sub>WH(O)</sub>                   | 3<br>5<br>8     | 70<br>40<br>30  | 250<br>150<br>100 | 500<br>300<br>200 | ns    |

| Input Rise and Fall Times<br>OSC <sub>in</sub> , f <sub>in</sub>                  | t <sub>TLH</sub><br>t <sub>THL</sub> | 3<br>5<br>8     |                 | 10<br>5<br>2      | 5<br>2<br>0.5     | μs    |

| Input Pulse Width Clock, Enable                                                   | t <sub>W</sub>                       | 3<br>5<br>8     | 60<br>50<br>40  | 30<br>25<br>20    | 1 1 1             | ns    |

(TA = -55°C to +125°C, C<sub>L</sub> = 50 pF)

| FREQUENCY CHARACTERISTICS                                                                                                       |                  |                   |                 |                       |                |                      |         |

|---------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-----------------|-----------------------|----------------|----------------------|---------|

| Characteristic                                                                                                                  | Symbol           | Division<br>Ratio | V <sub>DD</sub> | −55°C to 125°C<br>Max | Typical        | -40°C to 85°C<br>Max | Units   |

| Operating Frequency f <sub>in</sub> OSC <sub>in</sub><br>Input=SQ Wave V <sub>DD</sub> -V <sub>SS</sub><br>or Sinewave 500mVP-P | f <sub>max</sub> | ≥10               | 3<br>5<br>8     | 10<br>15<br>20        | 28<br>30<br>30 | 11<br>17<br>21       | h 41 1- |

|                                                                                                                                 |                  | 3*                | 3<br>5<br>8     | 3.5<br>5<br>8         | 12<br>16<br>24 | 4<br>6<br>9          | MHz     |

\*NOTE: This frequency applies only to fin input.

### PIN DESCRIPTIONS

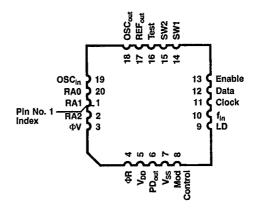

RAO, RA1, RA2 (Pins 20, 1, and 2) – These three inputs establish a code defining one of eight possible divide values for the total reference divider, as defined by the table below.

| Refe | erence Add<br>Code | Total<br>Divide Value |              |

|------|--------------------|-----------------------|--------------|

| RA2  | RA1                | RA0                   | Divide value |

| 0    | 0                  | 0                     | 8            |

| 0    | 0                  | 1                     | 64           |

| 0    | 1                  | 0                     | 128          |

| 0    | 1                  | 1                     | 256          |

| 1    | 0                  | 0                     | 640          |

| 1    | 0                  | 1                     | 1000         |

| 1    | 1                  | 0                     | 1024         |

| 1    | 1                  | 1                     | 2048         |

$\Phi$ **R**,  $\Phi$ **V** (Pins 3 and 4) – These phase detector outputs can be combined externally for a loop error signal. A single-ended output is also available for this purpose (see PD<sub>out</sub>).

If frequency  $f_V$  is greater than  $f_R$  or if the phase of  $f_V$  is leading, then error information is provided by  $\Phi V$  pulsing low.  $\Phi R$  remains essentially high.

If the frequency of  $f_V$  is less than  $f_R$  or if the phase of  $f_V$  is lagging, then error information is provided by  $\Phi R$  pulsing low.  $\Phi V$  remains essentially high.

If the frequency of  $f_V=f_R$  and both are in phase, both  $\Phi V$  and  $\Phi R$  remain high except for a small minimum time period when both pulse low in phase.

V<sub>DD</sub> (Pin 5) -- Positive power supply.

**PD**<sub>out</sub> (**Pin 6**) – Three state output of phase detector for use as loop error signal. Double-ended outputs are also available for this purpose (see  $\Phi V$  and  $\Phi R$ ).

Frequency  $f_V > f_R$  or  $f_V$  leading: negative pulses Frequency  $f_V < f_R$  or  $f_V$  lagging: positive pulses Frequency  $f_V = f_R$  and phase coincidence: High-impedance state.

V<sub>SS</sub> (Pin 7) - Circuit ground.

MODULUS CONTROL (Pin 8) – Signal generated by the on-chip control logic circuitry for controlling an external dual modulus pre-scaler. The modulus control level will be low at the beginning of a count cycle and will remain low until the ÷A counter has counted down

from its programmed value. At this time, modulus control goes high and remains high until the  $\div N$  counter has counted the rest of the way down from its programmed value (N - A additional counts since both  $\div N$  and  $\div A$  are counting down during the first portion of the cycle). Modulus control is then set back low, the counters preset to their respective programmed values, and the above sequence repeated. This provides for a total programmable divide value (N<sub>T</sub>)=N\*P+A, where P and P+1 represent the dual modulus prescaler divide values respectively for low and high modulus control levels; N the number programmed into the  $\div N$  counter, and A the number programmed into the  $\div A$  counter.

**LD (Pin 9)** – Lock detector signal. High level when loop is locked (f<sub>R</sub>, f<sub>V</sub> same phase and frequency). Pulses low when loop is out of lock.

$f_{in}$  (Pin 10) – Input to the positive edge triggers  $\div N$  and  $\div A$  counters,  $f_{in}$  is typically derived from a dual modulus prescaler and is AC coupled into Pin 10. For larger amplitude signals (standard CMOS logic levels) DC coupling may be used.

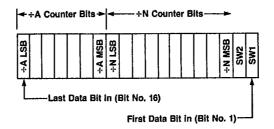

**CLOCK, DATA (Pins 11 and 12)** – Shift register clock and data input. Each low-to-high transition clocks one bit into the on-chip 19-bit shift register. The data is presented on the DATA input at the time of the positive clock transition. The DATA input provides programming information for the 10-bit  $\div N$  counter, the 7-bit  $\div A$  counter, and the two switch signals SW1 and SW2. The entry format is as follows:

**ENABLE (Pin 13)** – When high (1) transfers contents of the shift register into the latches, and to the programmable counter inputs and the switch outputs SW1 and SW2. When low (0) inhibits the above action and allows changes to be made in the shift register data without affecting the counter programming and switch outputs. An on-chip-pull-up establishes a continuously high level for ENABLE when no external signal is applied to Pin 13.

SW1, SW2 (Pins 14 and 15) - SW1 and SW2 provide latched open drain outputs corresponding to data bits numbers one and two. These will typically be used for band switch functions. A logic one will cause the output to assume a high-impedance state, while a logic zero will cause an output logic zero.

TEST (Pin 16) - Used in manufacturing. Must be left open or tied to Vss.

REFout (Pin 17) - Buffered output of on-chip reference oscillator or externally provided reference-input signal.

OSCout, OSCin (Pins 18 and 19) - These pins form an on-chip reference oscillator when connected to terminals of an external parallel resonant crystal. Frequency-setting capacitors of appropriate value must be connected from OSC<sub>in</sub> to ground and OSC<sub>out</sub> to ground. OSC<sub>in</sub> may also serve as input for an externally generated reference signal. This signal will typically be AC coupled to OSC<sub>in</sub>, but for larger amplitude signals (standard CMOS logic levels) DC coupling may also be used. In the external reference mode, no connection is required to OSCout.

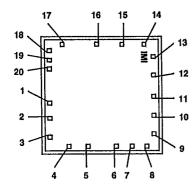

### CONNECTION

### DUAL-IN-LINE PACKAGES\*

### 20 ☐ RAO RA1 osc<sub>in</sub> RA2 2 19 Ф**V** [ 18 □ osc∞া ΦR □ 17 ☐ REFout Test V<sub>DO</sub> □ 16 PD<sub>out</sub> SW2 15 Vss 🗀 SW1 14 \_\_ Enable Mod Control □ 13 LD [ 12 🔲 Data fin 🗆 11 🔲 Clock

NOTE: Pin numbers correspond to DIP pin-out.

### ORDERING INFORMATION

### **VALID COMBINATIONS:**

IMI145156020PB IMI145156020QB IMI145156020XB IMI145156020ST IMI145156020**SK** IMI145156020LT IMI145156020LK IMI145156000DG IMI145156000DQ

For detailed ordering information see page 2.

## DUAL MODULUS

The technique of dual modulus prescaling is well established as a method of achieving high-performance frequency synthesizer operation at high frequencies. The approach allows relatively low-frequency programmable counters to be used as high-frequency programmable counters with speed capability of several hundred MHz. This is possible without the sacrifice in system resolution and performance that would otherwise result if a fixed (single modulus) divider was used for the prescaler.

In dual modulus prescaling, the lower-speed counters must be uniquely configured. Special control logic is necessary to select the divide value P or P+1 in the prescaler for the required amount of time (see modulus control definition). The IMI145156 contains this feature, and can be used with a variety of dual modulus prescalers to allow speed, complexity, and cost to be tailored to the system requirements. Prescalers with P. P+1 divide values in the range of  $\div 3/\div 4$  to  $\div 128/$ ÷129 can be controlled by the IMI145156.

# DESIGN GUIDELINES APPLICABLE TO THE IMI145156

The system total divide value (Ntotal) will be dictated by the application:

frequency into the prescaler = N\*P+Afrequency into the phase detector

N is the number programmed into the ÷N counter; A is the number programmed into +A counter. P and P+1 are two selectable divide ratios available in the two modulus prescalers. To have a range of N<sub>total</sub> values in sequence, the +A counter is programmed from zero through P-1 for a particular value N in the +N counter. N is then incremented to N+1, and the ÷A is sequenced from zero through P-1 again.

There are minimum and maximum values that can be achieved for N<sub>total</sub>. These are a function of P and the size of the +N and +A counters. The constraint N>A always applies. If  $A_{max}=P-1$ , then  $N_{min} \ge P-1$ ; then  $N_{total-min}=(P-1)P+A$  or (P-1)P, since A is free to assume the value of zero.

$$N_{total-max} = N_{max}^*P + A_{max}$$

To maximize system frequency capability, the dual modulus prescaler's output must go from low to high after each group of P or P+1 input cycles. The prescaler should divide by P when its modulus control line is high, and by P+1 when its modulus control is low.

For the maximum frequency into the prescaler ( $F_{VCO}$  max), the value used for P must be large enough so that:

A. F<sub>VCO</sub> max divided by P may not exceed the frequency capability of Pin 10 of the IMI145156.

- B. The period of F<sub>VCO</sub> divided by P must be greater than the sum of the times:

- a. Propagation delay through the dual modulus prescaler.

- b. Prescaler setup or release time relative to its modulus control signal.

- c. Propagation time from fin to the modulus control output for the IMI145156.

A sometimes useful simplification in the IMI145156 programming code can be achieved by choosing the values for P of 8, 16, 32, 64, or 128. For these cases, the desired value to Ntotal will result when Ntotal in binary is used as the program code to the ÷N and ÷A counters in the following manner:

- Assume the +A counter contains "b" bits where

- B. Always program all higher order ÷A counter bits above "b" to zero.

- C. Assume the ÷N counter and ÷A counter (with all the higher order bits above "b" ignored) combined into a single binary counter of 10+b bits in length. The MSB of this hypothetical counter is to correspond to the MSB of  $\div N$ , and the LSB is to correspond to the LSB of ÷A. The system divide value, N<sub>total</sub>, now results when the value of Ntotal in binary is used to program the "new" 10+b bit counter.