# LMC1982

# Digitally-Controlled Stereo Tone and Volume Circuit with Two Selectable Stereo Inputs

# **General Description**

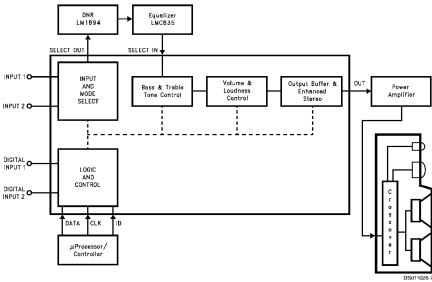

The LMC1982 is a monolithic integrated circuit that provides volume, balance, tone (bass and treble), enhanced stereo, and loudness controls and selection between two pairs of stereo inputs. These functions are digitally controlled through a three-wire communication interface. There are two digital inputs for easy interface to other audio peripherals such as stereo decoders. The LMC1982 is designed for line level input signals (300 mV–2V) and has a maximum gain of –0.5 dB. Volume is set at minimum and tone controls are flat when supply voltage is first applied.

Low noise and distortion result from using analog switches and poly-silicon resistor networks in the signal path.

Additional tone control can be achieved using the LMC835 stereo 7-band graphic equalizer connected to the LMC1982's SELECT OUT/SELECT IN external processor loop.

#### **Features**

- Low noise and distortion

- Two pairs of stereo inputs

- Enhanced stereo function

- Loudness compensation

- 40 position 2 dB/step volume attenuator plus mute

- Independent left and right volume controls

- Low noise-suitable for use with DNR® and Dolby® noise reduction

- External processor loop

- Signal handling suitable for compact discs

- Pop-free switching

- Serially programmable: INTERMETAL bus (IM) interface

- 6V to 12V single supply operation

- 28 Pin DIP or PLCC package

# **Applications**

- Stereo television

- Music reproduction systems

- Sound reinforcement systems

- Electronic music (MIDI)

- Personal computer audio control

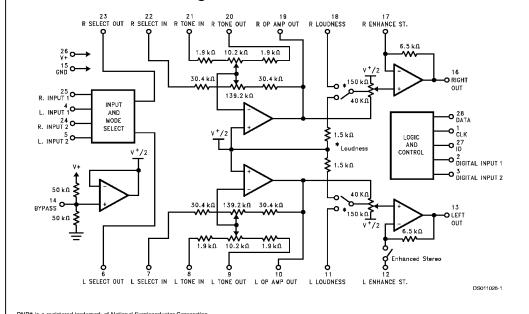

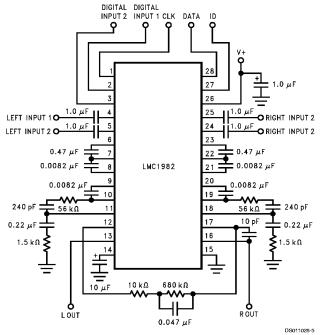

# **Block and Connection Diagrams**

DNR\* is a registered trademark of National Semiconductor Corporation. Dolby\* is a registered trademark of Dolby Labs.

© 1999 National Semiconductor Corporation

DS011028

# **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (V $^+$  – GND) 15V Voltage at any Pin GND – 0.2V to V $^+$  + 0.2V Input Current at any Pin (Note 3) 5 mA

Package Input Current (Note 3)

20 mA

Power Dissipation (Note 4)

500 mW

Junction Temperature

+125°C

Storage Temperature

-65°C to +150°C

Lead Temperature

N Package, (Soldering, 10 Seconds) +260°C V Package, (Vapor Phase, 60 Seconds) 215°C Infrared, (15 Seconds) 220°C

2 kV

Infrared, (15 Seconds)

ESD Susceptability (Note 5)

Operating Ratings(Notes 1, 2)

Temperature Range  $T_{MIN} \leq T_{A} \leq T_{MAX}$  LMC1982CIV, LMC1982CIV  $-40^{\circ}C \leq T_{A} \leq +85^{\circ}C$  Supply Voltage Range (V<sup>+</sup> – V<sup>-</sup>) 6V to 12V

# **Electrical Characteristics**

The following specifications apply for V<sup>+</sup> = 9V,  $f_{1N}$  = 1 kHz, input signal (300 mV) applied to INPUT 1, volume = 0 dB, bass = 0 dB, treble = 0 dB, enhanced stereo is off, and loudness is off unlessotherwise specified. All limits apply for  $T_A = T_J = +25^{\circ}C$ .

| Symbol           | Parameter                 | Conditions                                               | Typical  | Limit    | Unit                   |

|------------------|---------------------------|----------------------------------------------------------|----------|----------|------------------------|

|                  |                           |                                                          | (Note 6) | (Note 7) | (Limit)                |

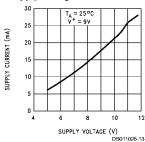

| Is               | Supply Current            |                                                          | 15       | 25       | mA (max)               |

| V <sub>IN</sub>  | Input Voltage             | Clipping Level (1,.0% THD),                              | 2.3 2    | 2.0      | V <sub>rms</sub> (min) |

|                  |                           | Select Out (Pins 6, 23)                                  |          |          |                        |

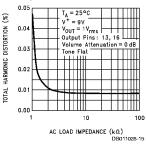

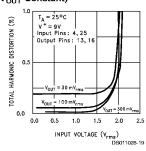

| THD              | Total Harmonic Distortion | Left and Right channels;                                 |          |          |                        |

|                  |                           | Output Pins 13, 16                                       |          |          |                        |

|                  |                           | $V_{IN} = 0.3 V_{rms};$                                  | 0.008    | 0.1      | % (max)                |

|                  |                           | f <sub>IN</sub> = 100 Hz, 1 kHz, 10 kHz                  |          |          |                        |

|                  |                           | $V_{IN} = 2.0 V_{rms};$                                  | 0.4      | 1.0      | % (max)                |

|                  |                           | f <sub>IN</sub> = 100 Hz, 1 kHz                          |          |          |                        |

|                  |                           | $V_{IN} = 2.0 V_{rms};$                                  | 0.5      | 1.0      | % (max)                |

|                  |                           | f <sub>IN</sub> = 10 kHz                                 |          |          |                        |

|                  |                           | V <sub>IN</sub> = 0.5 V <sub>rms</sub> ; Bass and Treble | 0.07     | 0.5      | % (max)                |

|                  |                           | Tone Controls Set at Maximum                             |          |          |                        |

|                  |                           | V <sub>IN</sub> = 0.3 V <sub>rms</sub> ; Volume          |          |          |                        |

|                  |                           | Attenuator at -20 dB, Bass and Treble                    | 0.06     | 0.15     | % (max)                |

|                  |                           | Tone Controls Set at Maximum                             |          |          |                        |

|                  | DC Shifts                 | V <sub>IN</sub> = 0.3 V <sub>rms</sub> ; Between Any     | 2.0      | 4.0      | mV (max)               |

|                  |                           | Two Adjacent Control Settings                            |          |          |                        |

|                  |                           | $V_{IN} = 0.3 V_{rms};$                                  | 18       | 20       | mV (max)               |

|                  |                           | All Mode and Input Positions                             |          |          | l                      |

| R <sub>OUT</sub> | AC Output Impedance       | Pins 6, 23, (470Ω to Ground at Input)                    | 150      | 200      | Ω (max)                |

|                  |                           | Pins 13, 16                                              | 26       | 40       | Ω (max)                |

| R <sub>IN</sub>  | AC Input Impedance        | Pins 4, 5, 24, 25                                        | 50       | 72       | kΩ (max)               |

|                  |                           |                                                          |          | 35       | kΩ (min)               |

|                  | Volume Attenuator Range   | Pins 13, 16; Volume                                      | 0.5      | 1.5      | dB (max)               |

|                  |                           | Attenuation at 0100010XXX000000 (0 dB)                   |          |          |                        |

|                  |                           | 0100010XXX101XXX (80 dB);                                | 80       | 78       | dB (min)               |

|                  |                           | (Relative to Attenuation at                              |          | 82       | dB (max)               |

|                  |                           | the 0 dB Setting)                                        |          |          |                        |

|                  | Volume Step Size          | All Volume Attenuation Settings                          |          |          |                        |

|                  |                           | from 0100010XXX101XXX (80 dB) to                         | 2.0      | 1.5      | dB (min)               |

|                  |                           | 0100010XXX000000 (0 dB) (Note 9)                         |          | 2.5      | dB (min)               |

#### **Electrical Characteristics** (Continued)

The following specifications apply for  $V^+ = 9V$ ,  $f_{\text{IN}} = 1$  kHz, input signal (300 mV) applied to INPUT 1, volume = 0 dB, bass = 0 dB, treble = 0 dB, enhanced stereo is off, and loudness is off unlessotherwise specified. All limits apply for  $T_A = T_J = +25^{\circ}C$ .

| Symbol              | Parameter                         | Conditions                                                          | Typical  | Limit    | Unit         |

|---------------------|-----------------------------------|---------------------------------------------------------------------|----------|----------|--------------|

|                     |                                   |                                                                     | (Note 6) | (Note 7) | (Limit)      |

|                     | Channel-to-Channel Volume         | All Volume Attenuation Settings                                     |          |          |              |

|                     | Tracking Error                    | from 0100010XXX101XXX (80 dB)                                       | ±0.1     | ±1.5     | dB (min)     |

|                     |                                   | to 0100010XXX000000 (0 dB)                                          |          |          |              |

|                     | Mute Attenuation                  | $V_{IN} = 1.0 V_{rms}$                                              | 105      | 86       | dB (max)     |

|                     | Bass Gain Range                   | f <sub>IN</sub> = 100 Hz, Pins 13, 16                               | ±12      | ±10.0    | dB (min)     |

|                     |                                   |                                                                     |          | ±14.0    | dB (max)     |

|                     | Bass Tracking Error               | f <sub>IN</sub> = 100 Hz, Pins 13, 16                               | ±0.1     | ±1.5     | dB (max)     |

|                     | Bass Step Size                    | f <sub>IN</sub> = 100 Hz, Pins 13, 16                               | 2.0      | 1.5      | dB (min)     |

|                     |                                   | (Relative to Previous Level)                                        |          | 2.5      | dB (max)     |

|                     | Treble Gain Range                 | f <sub>IN</sub> = 10 kHz, Pins 13, 16                               | ±12      | ±10.0    | dB (min)     |

|                     |                                   |                                                                     |          | ±14.0    | dB (max)     |

|                     | Treble Tracking Error             | f <sub>IN</sub> = 10 kHz, Pins 13, 16                               | ±0.1     | ±1.5     | dB (max)     |

|                     | Treble Step Size                  | f <sub>IN</sub> = 10 kHz, Pins 13, 16                               | 2.0      | 1.5      | dB (min)     |

|                     |                                   | (Relative to Previous Level)                                        |          | 2.5      | dB (max)     |

|                     | Enhanced Stereo Cross<br>Coupling | (Note 10)                                                           | -4.4     | -2.5     | dB (min)     |

|                     |                                   |                                                                     |          | -6.9     | dB (max)     |

|                     | Frequency Response                | V <sub>IN</sub> Applied to Input 1 and Input 2;                     |          |          |              |

|                     |                                   | f <sub>IN</sub> = 20 Hz – 20 kHz                                    | ±0.1     | ±1.0     | dB (max)     |

|                     |                                   | (Relative to Signal Amplitude at 1 kHz)                             |          |          |              |

|                     | Loudness                          | Volume Attenuator = 40 dB, Loudness                                 |          |          |              |

|                     |                                   | on (See Figure 5)                                                   |          |          |              |

|                     |                                   | Gain at 100 Hz (Referenced                                          | 11.5     | 13.5     | dB (max)     |

|                     |                                   | to Gain at 1 kHz)                                                   |          | 9.5      | dB (min)     |

|                     |                                   | Gain at 10 kHz (Referenced                                          | 6.5      | 8.5      | dB (max)     |

|                     |                                   | to Gain at 1 kHz)                                                   |          | 4.5      | dB (min)     |

|                     | Signal-to-Noise Ratio             | V <sub>IN</sub> = 1.0 V <sub>rms</sub> , A Weighted,                | 95       | 90       | dB (min)     |

|                     |                                   | Measured at 1 kHz, $R_S = 470\Omega$                                |          |          |              |

|                     | Channel Balance                   | All Volume Settings                                                 | 0.2      | 1.0      | dB (max)     |

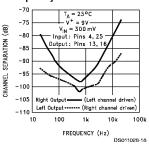

|                     | Channel Separation                | Input Pins 4, 25: Output Pins 13, 16;                               | 80       | 60       | dB (min)     |

|                     |                                   | $V_{IN} = 1.0V_{rms}$ (Note 8)                                      |          |          |              |

|                     | Input-Input Isolation             | 470Ω to AC Ground on Unused Input                                   | 95       | 60       | dB (min)     |

| PSSR                | Power Supply Rejection Ratio      | V <sup>+</sup> = 9 V <sub>DC</sub> ; 200 mV <sub>rms</sub> , 100 Hz | 32       | 28       | dB (min)     |

|                     |                                   | Sinewave Applied to Pin 26                                          |          |          |              |

| f <sub>CLK</sub>    | Clock Frequency                   |                                                                     | 5.0      | 1.0      | MHz<br>(max) |

| V <sub>IN(1)</sub>  | Logic "1" Input Voltage           | Pins 1, 27, 28 (IM Bus)                                             | 1.3      | 2.0      | V (min)      |

| ` '                 |                                   | Pins 2, 3                                                           | 2.9      | 5.5      | V (min)      |

| V <sub>IN(O)</sub>  | Logic "0" Input Voltage           | Pins 1, 27, 28 (IM Bus)                                             | 0.4      | 0.8      | V (max)      |

| ` '                 |                                   | Pins 2, 3                                                           | 1.2      | 3.5      | V (max)      |

| V <sub>OUT(1)</sub> | Logic "1" Output Voltage          | Pin 28 (IM Bus)                                                     |          | 2.0      | V (min)      |

| V <sub>OUT(0)</sub> | Logic "0" Output Voltage          | Pin 28 (IM Bus)                                                     | 0.4      | 0.8      | V (max)      |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the deivce may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are specified with respect to ground.

Note 3: When the input voltage  $(V_{IN})$  at any pin exceeds the power supply voltages  $(V_{IN} < V^- \text{ or } V_{IN} > V^+)$  the absolute value of the current at that pin should be limited to 5 mA or less. The 20 mA package input current limits the number of pins that can exceed the power supply voltages with 5 mA current limit to four.

#### Electrical Characteristics (Continued)

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is  $P_D = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For the LMC1982CIN,  $T_{JMAX} = +125^{\circ}C$ , and the typical junction-to-ambient thermal resistance, when board mounted, is 67°C/W.

Note 5: Human body model; 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 6: Typicals are at  $T_J = +25^{\circ}C$  and represent the most likely parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: The Input-Input Isolation is tested by driving one input and measuring the output when the undriven input are selected.

Note 9: The Volume Step Size is defined as the change in attenuation between any two adjacent volume attenuation settings. The nominal Volume Step Size is 2 dB.

Note 10: Enhanced Stereo Cross Coupling is a measure of the ratio between the undriven right channel output signal and the driven left channel output signal. It is measured by driving the left inputs with a 300 mV<sub>rms</sub> signal while the right inputs are grounded.

# **Typical Performance Characteristics**

# Supply Current vs Supply Voltage

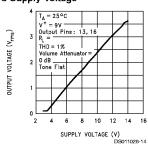

# Output Voltage vs Supply Voltage

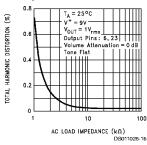

#### THD vs Load Impedance

#### THD vs Load Impedance

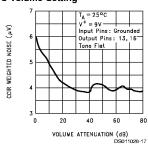

# CCIR Output Noise vs Volume Setting

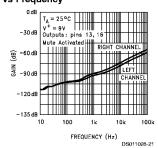

Channel Separation vs Frequency

#### THD vs V<sub>IN</sub> (V<sub>OUT</sub> Constant)

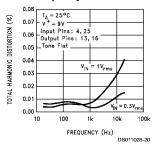

THD vs Frequency

Mute Gain vs Frequency

# Pin Description (Continued)

TABLE 1. IM Bus Programming Codes for LMC1982

| Address  | Function                  | Data       | Function             |  |

|----------|---------------------------|------------|----------------------|--|

| (A7-A0)  |                           |            | Selected             |  |

| 01000000 | Input Select + Mute       | XXXXXX00   | INPUT1               |  |

|          |                           | XXXXXX01   | INPUT2               |  |

|          |                           | XXXXXX10   | N/A                  |  |

|          |                           | XXXXXX11   | MUTE                 |  |

| 01000001 | Loudness, Enhanced Stereo | XXXXXX00   | Loudness OFF         |  |

|          |                           |            | Enhanced Stereo OFF  |  |

|          |                           | XXXXXX01   | Loudness ON          |  |

|          |                           |            | Enhanced Stereo OFF  |  |

|          |                           | XXXXXX10   | Loudness OFF         |  |

|          |                           |            | Enhanced Stereo ON   |  |

|          |                           | XXXXXX11   | Loudness ON          |  |

|          |                           |            | Enhanced Stereo ON   |  |

| 01000010 | Bass                      | XXXX0000   | –12 dB               |  |

|          |                           | XXXX0011   | −6 dB                |  |

|          |                           | XXXX0110   | FLAT                 |  |

|          |                           | XXXX1001   | +6 dB                |  |

|          |                           | XXXX11XX   | +12 dB               |  |

| 01000011 | Treble                    | XXXX0000   | –12 dB               |  |

|          |                           | XXXX0011   | −6 dB                |  |

|          |                           | XXXX0110   | FLAT                 |  |

|          |                           | XXXX1001   | +6 dB                |  |

|          |                           | XXXX11XX   | +12 dB               |  |

| 01000100 | Left Volume               | XX000000   | 0 dB                 |  |

|          |                           | XX010100   | -40 dB               |  |

|          |                           | XX101XXX   | -80 dB               |  |

|          |                           | XX11XXXX   | -80 dB               |  |

| 01000101 | Right Volume              | XX000000   | 0 dB                 |  |

|          |                           | XX010100   | -40 dB               |  |

|          |                           | XX101XXX   | -80 dB               |  |

|          |                           | XX11XXXX   | -80 dB               |  |

| 01000110 | Mode Select               | XXXXX100   | Left Mono            |  |

|          |                           | XXXXX101   | Stereo               |  |

|          |                           | XXXXX11X   | Right Mono           |  |

| 01000111 | Read Digital Input 1      | XXXXXXD1D0 | D0 = Digital Input 1 |  |

|          | or                        |            | D1 = Digital Input 2 |  |

|          | Digital Input 2           |            |                      |  |

|          | on IM Bus                 |            |                      |  |

#### **General Information**

The LMC1982 is a CMOS/bipolar building block intended for high fidelity audio signal processing. It is designed for line level inputs signals (300 mV - 2V) and has a maximum gain of -0.5 dB. While the LMC1982 is manufactured with CMOS processing, NPN transistors are used to build low noise op amps. The combination of CMOS switches, bipolar op amps, and poly-silicon resistors make it possible to achieve an order of magnitude quality improvement over other bipolar circuits that use analog multipliers to accomplish gain adjustment. Internal circuits set the volume to minimum, tone controls to flat, the mute to on, and all other functions off

when power is first applied. Individual left and right volume controls are software programmed to achieve the stereo balance function. *Figure 1* shows the connection diagram of a typical LMC1982 application.

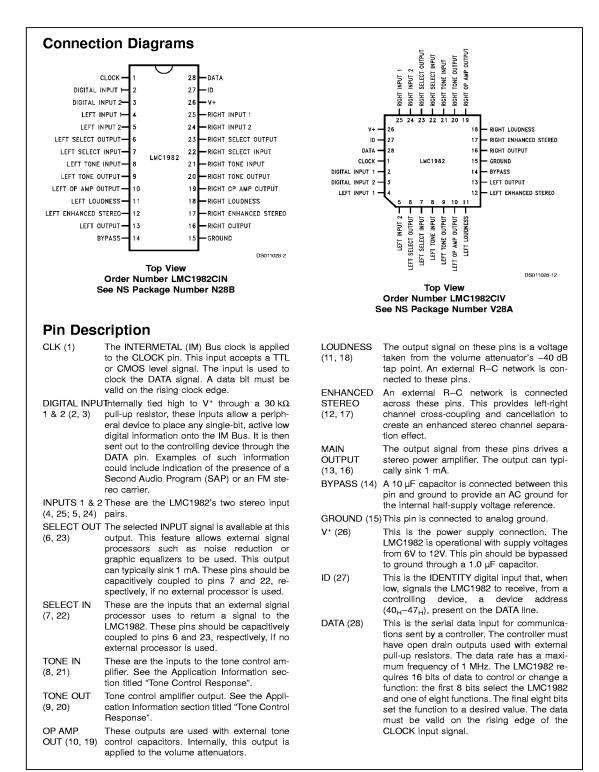

The LMC1982 has internal decoding logic that allows a microprocessor ( $\mu P$ ) or microcontroller ( $\mu C$ ) to communicate directly to the audio control circuitry through an INTERMETAL (IM) Bus interface. This three-wire interface consists of a bi-directional DATA line, a Clock (CLK) input line, and an Identity (ID) line. Address and function selection data (8 bits)

#### General Information (Continued)

are serially shifted from the controller to the LMC1982. This is followed by 8 bits of function value data. Data present in the internal shift register is latched and the instruction is executed.

FIGURE 1. Typical Application

8

# **Application Information**

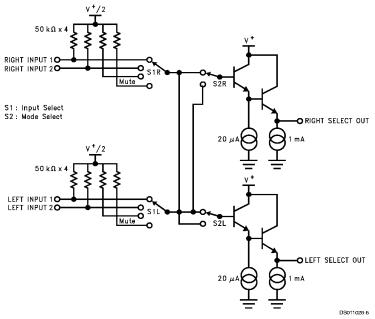

#### INPUT SELECTOR

The LMC1982's input selector and mode control are shown in Figure 2. The input selector selects one of two stereo signal sources or a mute function with typical attenuation of 100 dB. The selected signals are then sent to a mode control matrix. As shown in Table 1, the matrix provides normal stereo or can direct either channel to both LEFT or RIGHT SELECT OUTPUTs. The third matrix mode is normal stereo. The control matrix output is buffered and appears on each channel's respective SELECT OUT pin (6, 23). Switching noise is kept to a minimum when mute is selected by using a 50 k $\Omega$  bias resistor.

Noise performance is optimized through the use of emitter followers in the mode control matrix's output. Internal  $50~k\Omega$  resistors are connected to each input selector pin to provide the proper bias point for the emitter follower buffers. Each internal  $50~k\Omega$  bias resistor is connected to a common half-supply (V\*/2) source. This produces a voltage at pins 6 and 23 (SELECT OUT) that is 1.4V below V\*/2 (typically 3.1V with V\* = 9V). Since a DC voltage is present at the input pins (4, 5, 24, and 25), input signal should be AC coupled through a 1  $\mu\text{F}$  capacitor.

The output signal at pins 6 and 23 can be used to drive exteral audio processing circuits such as noise reduction (LM1894—DNR or Dolby) or graphic equalizers (LMC835). It is important that if any noise reduction is used it be placed ahead of any tone controls or equalizers in the external circuit path to preserve the frequency spectrum of the selected input signal. Otherwise, any frequency equalization could prevent the proper operation of the noise reduction circuit. If no external processor is used, a capacitor should be used to couple the SELECT OUT signals directly to pins 7 and 22, respetively.

#### MINIMUM LOAD IMPEDANCE

The LMC1982 employs emitter-followers to buffer the selected stereo channels. The buffered signals are available at pins 6 and 23 (SELECT OUT). The SELECT OUT buffers operate with a typical bias current 1 mA.

The Electrical Specifications table lists a maximum input signal of 2.0  $V_{rms}$  (2.5  $V_{peak})$  for 1% THD at the SELECT OUT pins. This distortion level is achieved when the minimum AC load impedance seen by the SELECT OUT pins is 2.5  $k\Omega$  (2.5V/1 mA). Using lower load impedances results in clipping at lower output levels. If the load impedance is DC-coupled, an increased quiescent current can flow. Latch-up may occur

## **Application Information** (Continued)

if the total emitter current exceeds 5 mA. Thus, maximum output voltage can be increased and much lower distortion levels can be achieved using load impedances of at least 25 k $\Omega$ .

#### INPUT IMPEDANCE

The input impedance of pins 4, 5, 24 and 25 is defined by internal bias resistors and is typically 50  $k\Omega.$

The SELECT IN pins have an input impedance that varies with the BASE and TREBLE control settings. The input impedance is  $100~k\Omega$  at DC and  $19~k\Omega$  at 1 kHz when the controls are set at 0 dB. Minimum input impedance of  $30.4~k\Omega$  at DC and  $16~k\Omega$  at 1 kHz occurs when maximum boost is selected. At 10~kHz the minimum input impedance, with the tone controls flat, is  $6.8~k\Omega$  and, with the tone controls at maximum boost, is  $2.5~k\Omega$ .

FIGURE 2. Input and Mode Select Circuitry

#### **EXTERNAL SIGNAL PROCESSING**

The SELECT OUT pins (6 and 23) enable greater system design flexibility by providing a means to implement an external processing loop. This loop can be used for noise reduction circuits such as DNR (LM1894) or multi-band graphic equalizers (LMC835). If both are used, it is important to ensure that the noise reduction circuitry precede the equalization circuits. Failure to do so results in improper operation of the noise reduction circuits. The system shown in Figure 3 utilizes the external loop to include DNR and a multi-band equalizer.

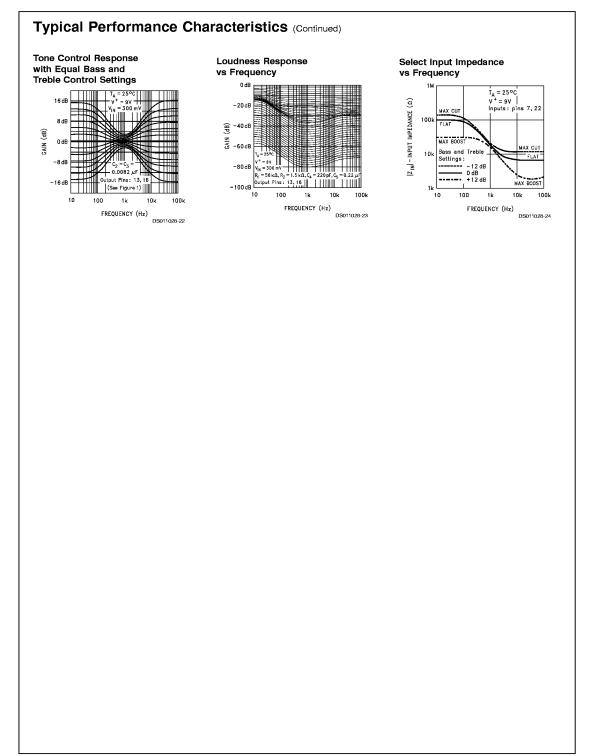

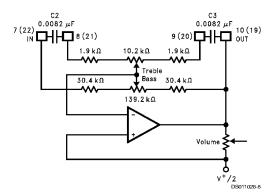

#### TONE CONTROL RESPONSE

Bass and treble tone controls are included in the LMC1982. The tone controls used just two external capacitors for each stereo channel. Each has a corner frequency determined by the value of C2 and C3 (see *Figure 4*) and internal resistors in the feedback loop of the internal tone amplifier. The maximum-boost or cut is determined by the data sent to the LMC1982 (see *Table 1*).

The typical tone control response shown in Typical Performance Curves were generated with C2 = C3 = 0.0082  $\mu F$  and show the response for each step. When modifying the

tone control response it is important to note that the ratio of C3 and C2 sets the mid-frequency gain. Symmetrical tone response is achieved when C2 = C3. However, with C2 = 2(C3) and the tone controls set to "flat", the frequency response will be flat at 20 Hz and 20 kHz, and +6 dB at 1 kHz

The frequency where a tone control begins to deviate from a flat response is referred to as the turn-over frequency. With C=C2=C3, the LMC1982's treble turn-over frequency is nominally

$$f_{TT} = \frac{1}{2\pi C(14 k\Omega)}$$

# Application Information (Continued)

The bass turn-over frequency is nominally

$$f_{BT} = \frac{1}{2\pi C(30.4 \, k\Omega)}$$

when maximum boost is chosen. The inflection points (the frequencies where the boost or cut is within 3 dB of the final value) are for treble and bass

$$f_{TI} = \frac{1}{2\pi C(1.9 \text{ k}\Omega)}$$

$$f_{BI} = \frac{1}{2\pi C(169.6 \text{ k}\Omega)}$$

FIGURE 3. System Block Diagram Utilizing the External Processing Loop (One Channel Shown)

10

FIGURE 4. The Tone Control Amplifier

Increasing the values of C2 and C3 decreases the turnover and inflection frequencies: i.e., the Tone Control Response Curves shown in Typical Performance Curves will shift left when C2 and C3 are increased and shift right when C2 and C3 are decreased. With C2 = C3 = 0.0082  $\mu\text{F}$ , 2 dB steps are achieved at 100 Hz and 10 kHz. Changing C2 and C3 to 0.01  $\mu\text{F}$  shifts the 2 dB per step frequency to 72 Hz and

8.3 kHz. If the tone control capacitors size is decreased these frequencies will increase. With C2 = C3 = 0.0068  $\mu F$  the 2 dB steps take place at 130 Hz and 11.2 kHz.

#### LOUDNESS

The human ear has less sensitivity to high and low frequencies relative to its sensitivity to mid-range frequencies between 2 kHz and 6 kHz for any given acoustic level. The low and high frequency sensitivity decreases faster than the sensitivity to the mid-range frequencies as the acoustic level drops. The LMC1982's loudness function can be used to help compensate for the decreased sensitivity by boosting the gain at low and high frequencies as the volume control attenuation increases (see the curve labeled "Gain vs Frequency with Loudness Active").

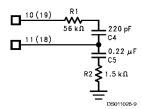

The LMC1982's loudness function uses external components R1, R2, C4 and C5, as shown in *Figure 5*, to select the frequencies where bass and treble boost begin. The amount of boost is dependent on the volume attenuator's setting. The loudness characteristic, with the volume attenuator set at 40 dB. has a transfer function of

$$\frac{V_0}{V_1} = \frac{(sC5R2 + 1)[sC4(R1 + 156k) + 1]}{(s^2)C4C5R2(163k) + s[C4(156k) + C5(4.9R2 + 156k)] + 1}$$

The external components R1 and C4 can be eliminated and pin 10(19) left open if bass boost is the only desired loudness characteristic.

## **Application Information** (Continued)

As shown in *Table 1*, loudness and enhanced stereo are controlled through the same address. It is important to remember to set both functions to the correct value any time either of these functions is updated.

FIGURE 5. Loudness Control Circuit

#### **ENHANCED STEREO**

The LMC1982 has an enhanced stereo effect that can be achieved by cross-coupling reverse phase information between the left and right stereo channels. This feature can help improve the apparent stereo channel separation when, because of cabinet or equipment limitations, the left and right speakers are closer to each other than optimum.

Enhanced stereo is created by connecting an external frequency shaping RC network between the OUTPUT operational amplifiers' inverting inputs through an internal CMOS switch (see *Figure 6*). The external network couples 60% of each channel's output to the opposite channel's inverting input. This cancels a portion of the signal common to both channels.

FIGURE 6. Enhanced Stereo Circuit

The desired 60% cross-coupling is accomplished through the internal 6.5 k $\Omega$  feedback resistor and an external 10 k $\Omega$  resistor. Bass frequency cancellation is prevented by using a 0.047  $\mu$ F coupling capacitor to couple only frequencies above 330 Hz. Switching noise is eliminated by using a 680 k $\Omega$  resistor across the 0.047  $\mu$ F. R3, R4 and C6 can be eliminated if enhanced stereo is not desired

As shown in *Table 1*, enhanced stereo and loudness are controlled through the same address. It is important to remember to set both functions to the correct value any time either of these functions is updated.

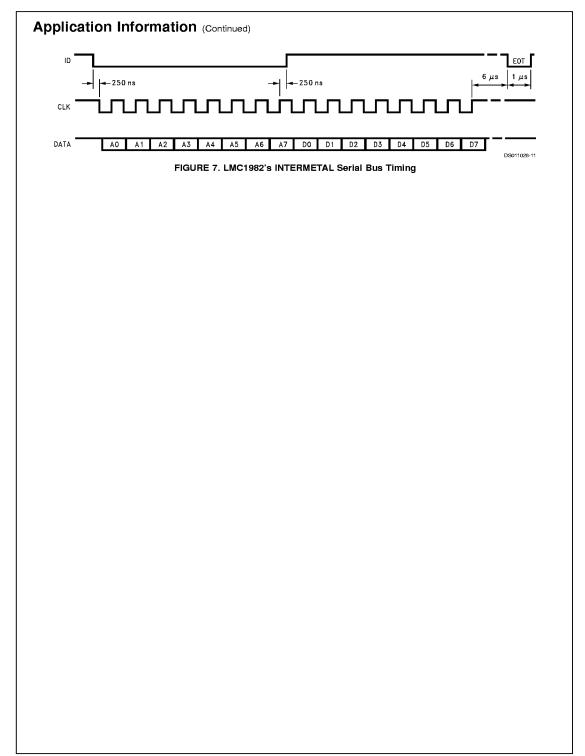

#### SERIAL DATA COMMUNICATION

The LMC1982 uses the INTERMETAL serial bus (IM Bus) standard. Serial data information is sent to the LMC1982 over a three wire IM Bus consisting of Clock (CLK), Data (DATA), and Identity (ID). The DATA line is bidirectional and the CLK and ID lines are unidirectional from the microprocessor or micontroller to the LMC1982. The LMC1982's bidi-

rectional capability is accomplished by using an open drain output on the DATA line and an external 1 k $\Omega$  pull-up resistor. The LMC1982 responds to address values from 01000000  $(40_{\rm H})$  through 01000111 (47  $_{\rm H}).$  The addresses select one of the eight available functions (see Table 1). The IM Bus' lines have a logic high standby state when using TTL logic levels. As shown in Figure 7, data transmission is initiated by low levels on CLK and ID. Next, eight address bits are sent. This address information includes the code to select one of the LMC1982's desired functions. Each address bit is clocked in on the rising edge of CLK. The ID line is taken high after the eight bits of address data are received by the LMC1982. The controlling system continues toggling the CLK line eight more times. Data that determines the selected function's operating point is written into, or single bit information on DIGI-TAL INPUT 1 or DIGITAL INPUT 2 is read from, the LMC1982. Finally, the end of transmission is signalled by pulsing the ID line low for a minimum of 1 µs. The transmit-

Table 1 also details the serial data structure, range, and bit assignments that sets each function's operating point. The volume and tone controls' function control data binarily increments from zero to maximum as the function's operating point changes from 80 dB attenuation to 0 dB attenuation (volume) or -12 dB to +12 dB (tone controls). Note that not all data bits are needed by each function. The extra bits shown as "X"s ("don't cares") are position holders and have no affect on a respective function. They are necessary to properly position the data in the LMC1982's internal data shift register. Unexpected results may take place if these bits are not sent.

ted function data is latched and the function changes to its

The LMC1982's internal data shift register can handle either a 16-bit word or two 8-bit serial data transmissions. It is the final 8 bits of data received before the ID line goes high that are used as the LMC1982 selection and function addresses. The final eight bits after the ID line returns high are used to change a function's operating point. CLK must be stopped when the final 8 data bits are received. The data stored in the internal data latch remains unchanged until the ID is pulsed, signifying the end of data transmission. When ID is pulsed, the new data in the data shift register is latched into the data latch and the selected function takes on a new operating point.

A complete description and more information concerning the IM Bus is given in the appendix of ITT's CCU2000 datasheet.

#### DIGITAL I/C

new setting.

The LMC1982's two Digital Input pins, 2 and 3, provide single-bit communication between a peripheral device and the controller over the IM Bus. Each pin has an internal 30 k $\Omega$  pull-up resistor. Therefore, these pins should be connected to open collector/drain outputs. The type of information that could be received on these lines and retrieved by a controller include FM stereo pilot indication, power on/off, Secondary Audio Program (SAP), etc.

According to Table 1, the logic state of DIGITAL INPUT 1 and DIGITAL INPUT 2 is latched and can be retrieved over the IM Bus using the read command (47 $_{\rm H}).$  The single-bit information sent on the IM Bus is active low since these lines are internally pulled high.

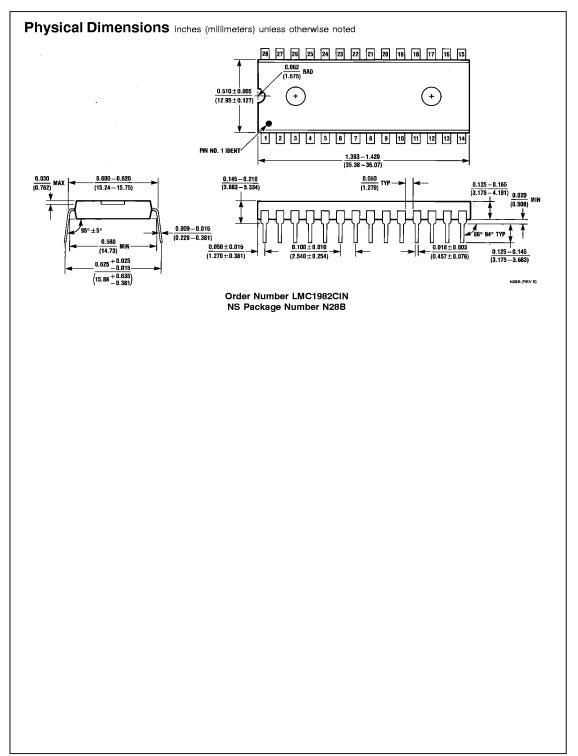

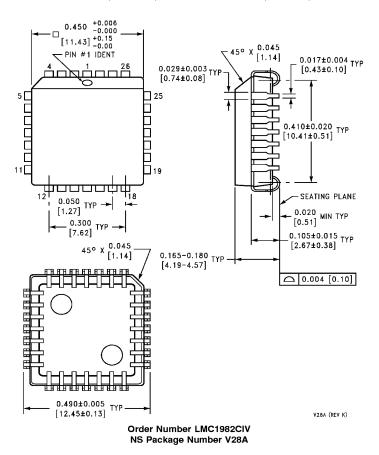

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation

Americas

Tel: 1-800-272-9959

Fax: 1-800-737-7018 Email: support@nsc.com

National Semiconductor

Fax: +49 (0) 1 80-530 85 86 Fax: +49 (0) 1 80-530 85 86

Email: europe support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-534 95 58

Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconducto Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466

Email: sea.support@nsc.com

National Semiconductor Japan Ltd.

Tel: 81-3-5639-7560

Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications