| LTR                              |               |              |      |                   |               |                                 |                | RE             | VISI           | ONS        |              |           |                     |              |                   | r                                                |                 |        |              |              |

|----------------------------------|---------------|--------------|------|-------------------|---------------|---------------------------------|----------------|----------------|----------------|------------|--------------|-----------|---------------------|--------------|-------------------|--------------------------------------------------|-----------------|--------|--------------|--------------|

| LIK                              |               |              |      |                   | DI            | ESCRI                           | PTIC           | N              |                |            |              |           | DATE                | YR-          | MO-DA)            |                                                  |                 | APPRO  |              | <del>,</del> |

| A                                | code          | 617<br>lor 0 | 72 t | o de<br>code      | vice<br>617   | and (<br>type<br>72 fe<br>itor: | es 03<br>or de | 3 and<br>evice | 1 04.<br>• typ | De<br>es O | lete<br>l an | d         | 92-                 | 10-1         | 4                 |                                                  | M               | 1. For | S.E.         | 7            |

|                                  |               |              |      |                   |               |                                 |                |                |                |            |              |           |                     |              |                   |                                                  |                 |        |              |              |

|                                  |               |              |      |                   |               |                                 |                |                |                |            |              |           |                     |              |                   |                                                  |                 |        |              |              |

| REV                              |               |              |      |                   |               |                                 |                | <u> </u>       |                |            |              |           |                     |              |                   |                                                  |                 |        |              |              |

|                                  |               |              |      |                   |               |                                 |                |                |                |            |              |           |                     |              |                   |                                                  |                 |        |              |              |

| SHEET .                          | A             | A            | A    |                   |               |                                 |                |                |                |            |              |           |                     |              |                   |                                                  |                 |        |              |              |

| SHEET .                          |               | A 16         |      |                   |               |                                 |                |                |                |            |              |           |                     |              |                   |                                                  |                 |        |              |              |

| SHEET REV SHEET REV STAT         | 15<br>US      |              |      | RE                | v             |                                 | A              | A              | A              | A          | A            | A         | A                   | A            | A                 | A                                                | A               | A      | A            |              |

| SHEET REV SHEET REV STAT         | 15<br>US      |              |      |                   | V             |                                 | A 1            | A 2            | A 3            | A 4        | A 5          | A 6       | A 7                 | A 8          | A 9               | A 10                                             | A 11            | A 12   | A 13         | -            |

| SHEET  SHEET  REV STATE OF SHEET | 15<br>US<br>S | 16           |      | SH                | EET<br>ARED B | Y                               | 1              | <del> </del>   |                | 4          | 5            | 6<br>SE E | 7<br>LECTI          | 8 RONIC      | 9<br>S SU         | <del>                                     </del> | 11<br>CEN       | 12     | <del> </del> |              |

|                                  | 15<br>US<br>S | 16           | 17   | SH<br>PREPA<br>Ma | EET ARED B    | ellehe                          | 1              | <del> </del>   |                | 4<br>D     | 5<br>EFEN:   | 6<br>SE E | 7<br>LECTE<br>DAYTO | 8 RONICON, C | 9<br>S SU<br>OHIO | 10<br>JPPLY                                      | 11<br>CEN<br>44 | 12 TER | 13           | 1            |

CAGE CODE

1

67268

OF

17

SIZE

Α

SHEET

DESC FORM 193 JUL 91

DEPARTMENT OF DEFENSE

AMSC N/A

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

DRAWING APPROVAL DATE

88-06-30

REVISION LEVEL

**■ 9004708 0010837 859 ■**

5962-E520-92

5962-88657

## 1. SCOPE

1.1 <u>Scope</u>. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

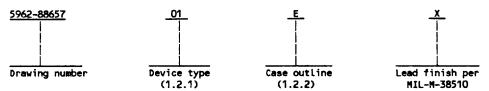

1.2 Part or Identifying Number (PIN). The complete PIN shall be as shown in the following example:

1.2.1 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device ty | /pe        | Generic number        | <u>Circuit function</u>                                                                                          |

|-----------|------------|-----------------------|------------------------------------------------------------------------------------------------------------------|

| 01        | _          | 54FCT163              | Synchronous presettable binary counter, TTL compatible                                                           |

| 02<br>03  | <u>2</u> / | 54FCT163A<br>54FCT163 | Synchronous presettable binary counter, TTL compatible<br>Synchronous presettable binary counter, TTL compatible |

| 04        |            | 54FCT163A             | Synchronous presettable binary counter, TTL compatible                                                           |

1.2.2 <u>Case outline(s)</u>. The case outline(s) shall be as designated in appendix C of MIL-M-38510, and as follows:

| outline letter | case outline                                                          |

|----------------|-----------------------------------------------------------------------|

| E              | D-2 (16-lead, .840" x .310" x .200"), dual-in-line package            |

| F              | F-5 (l6-lead, .440" x .285" x .085"), flat package                    |

| 2              | C-2 (20-terminal, .358" x .358" x .100"), square chip carrier package |

1.3 Absolute maximum ratings. 2/

| Supply voltage range (V <sub>CC</sub> )   | -0.5 V dc to +7.0 V dc                                                         |

|-------------------------------------------|--------------------------------------------------------------------------------|

| Supply voltage range (V <sub>CC</sub> )   | -0.5 V dc to V <sub>CC</sub> to +0.5 V dc 3/                                   |

| Output voltage range                      | $-0.5 \text{ V dc to } V_{CC}^{CC} \text{ to } +0.5 \text{ V dc } \frac{3}{2}$ |

| DC input diode current (I <sub>IK</sub> ) | -20 mA                                                                         |

| DC output diode current (Inv)             | -50 mA                                                                         |

| DC output current                         | ±100 mA                                                                        |

| Power dissipation (PD) 4/                 | 500 mW                                                                         |

| Thermal resistance $(\Theta_{10})$        | See MIL-M-38510, appendix C                                                    |

| Storage temperature range                 | -65°C to +150°C                                                                |

| Junction temperature (T <sub>j</sub> )    | +175°C                                                                         |

| Lead temperature (soldering, 10 seconds)  | +300°C                                                                         |

$<sup>\</sup>underline{2}'$  All voltages referenced to GND.  $\underline{3}'$  For  $V_{CC}>6.5$  V dc, the upper bound is limited to +7.0 V.  $\underline{4}'$  Must withstand the added  $P_{D}$  due to short circuit test e.g.,  $I_{OS}$ .

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-88657 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>2 |

DESC FORM 193A

JUL 91 F

9004708 0010838 795 🚃

<sup>1/</sup> Due to internal noise problems, device types 01 and 02 do not meet the minimum  $V_{\mathrm{IH}}$  threshold limit characteristic of the FCT family or the limits specified on this drawing. These device types are no longer available for acquisition.

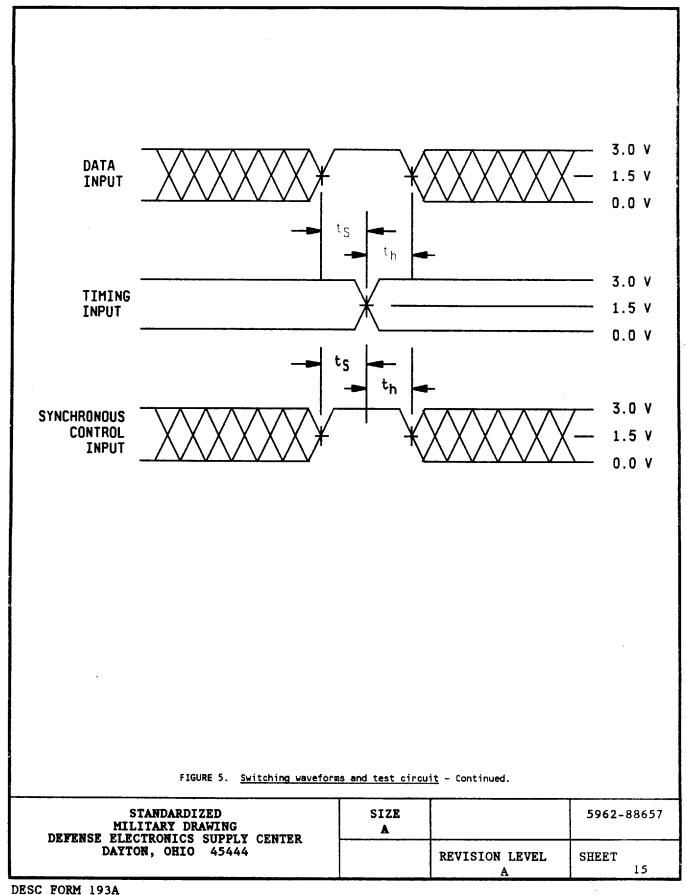

# 1.4 Recommended operating conditions +4.5 V dc to +5.5 V dc 0.8 V dc 2.0 V dc 3.0 V dc -55°C to +125°C Minimum setup time, high or low (Pn to CP) (ts): Device types 01 and 03 - - - - - - - - - - - -Device types 01 and 03 - - - - -5.5 ns Device types 02 and 04 - - - - - - - - - - - - -4.5 ns Minimum setup time, high or low (CEP, CET to CP) (tg): Device types 01 and 03 - - - - - - - - - - - -13.0 ns Device types 02 and 04 - - - - - - - - - -11.0 ns Minimum hold time, high or low $(\underline{P}_n$ to CP) $(t_h)$ - - - Minimum hold time, high or low (CEP, CET to CP) $(t_h)$ -2.0 ns 0.0 ns Minimum CP pulse width, high, low (load) (t\_): 5.0 ns 4.0 ns Minimum CP pulse width, high, low (count) (tu): 8.0 ns 7.0 ns 13.5 ns 11.5 ns Minimum hold time, (SR, PE) to CP (th): Device types 01, 02, 03, and 04 - - - - - - - -1.5 ns 2. APPLICABLE DOCUMENTS 2.1 Government specification, standard, and bulletin. Unless otherwise specified, the following specification, standard, and bulletin of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein. SPECIFICATION **MILITARY** MIL-M-38510 - Microcircuits, General Specification for. STANDARD MILITARY MIL-STD-883 - Test Methods and Procedures for Microelectronics. BULLETIN **MILITARY** MIL-BUL-103 - List of Standardized Military Drawings (SMD's). (Copies of the specification, standard, and bulletin required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

<sup>1/</sup> For dynamic operation of device types 03 and 04, a V<sub>IH</sub> level between 2.0 V and 3.0 V may be recognized by this device as a high logic level input. For static operation of device types 03 and 04, a V<sub>IH</sub> ≥ 2.0 V will be recognized by these devices as a high logic level input. Users are cautioned to verify that this change will not affect their system.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE |                     | 5962-88657 |

|-----------------------------------------------------------------|------|---------------------|------------|

| DAYTON, OHIO 45444                                              |      | REVISION LEVEL<br>A | SHEET<br>3 |

DESC FORM 193A JUL 91

9004708 0010839 621

- 2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

- 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

- 3.2.1 <a href="mailto:case outline(s">case outline(s)</a>. The case outline(s) shall be in accordance with 1.2.2 herein.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1 herein.

- 3.2.3 Truth table. The truth table shall be as specified on figure 2 herein.

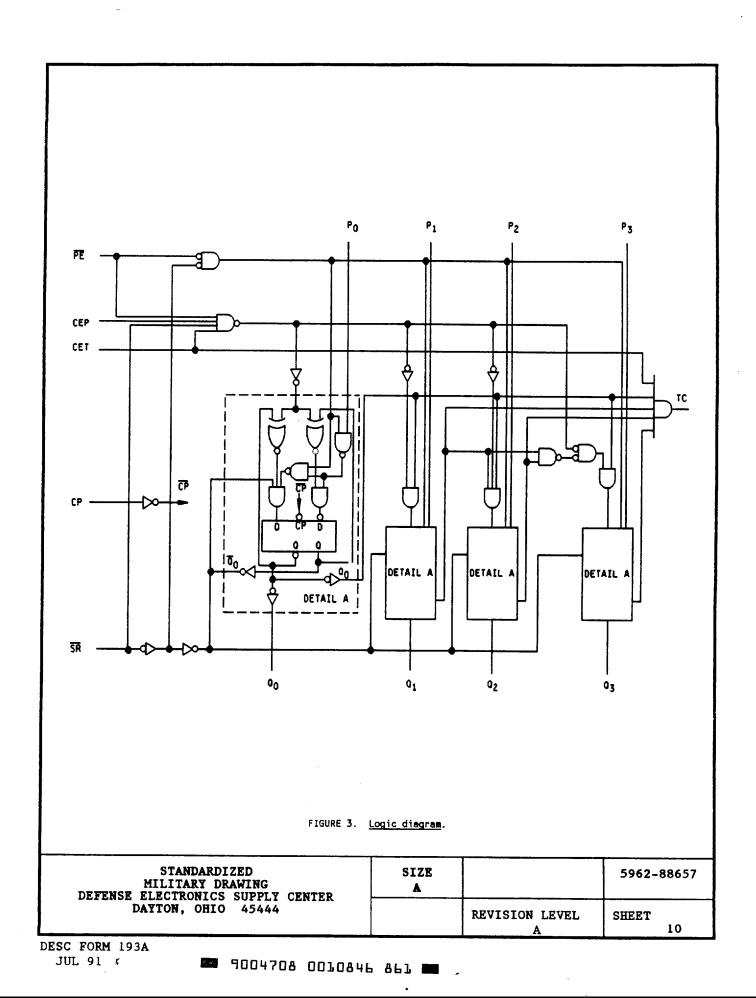

- 3.2.4 Logic diagram. The logic diagram shall be as specified on figure 3 herein.

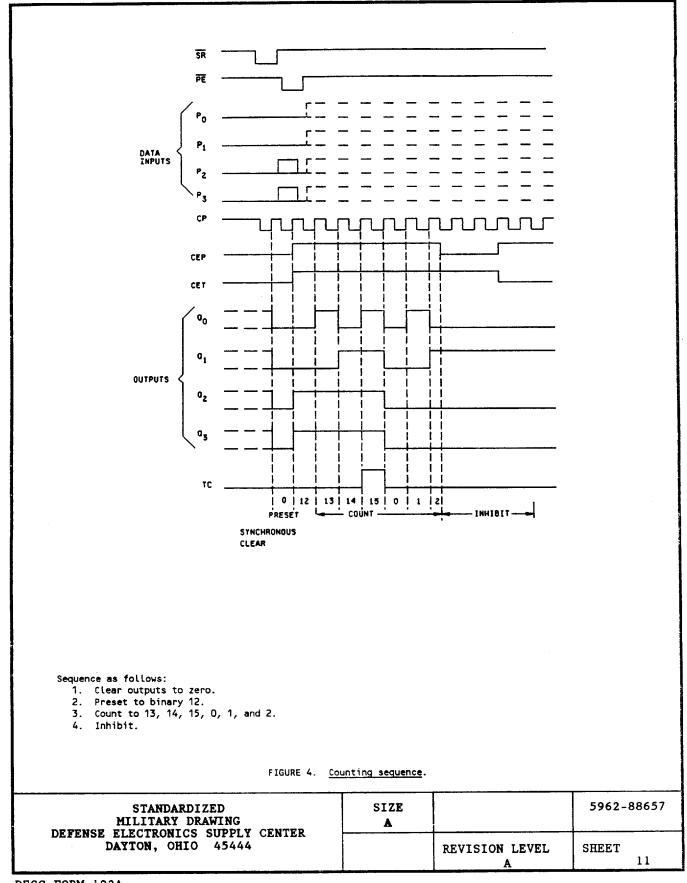

- 3.2.5 Counting sequence. The counting sequence shall be as specified on figure 4.

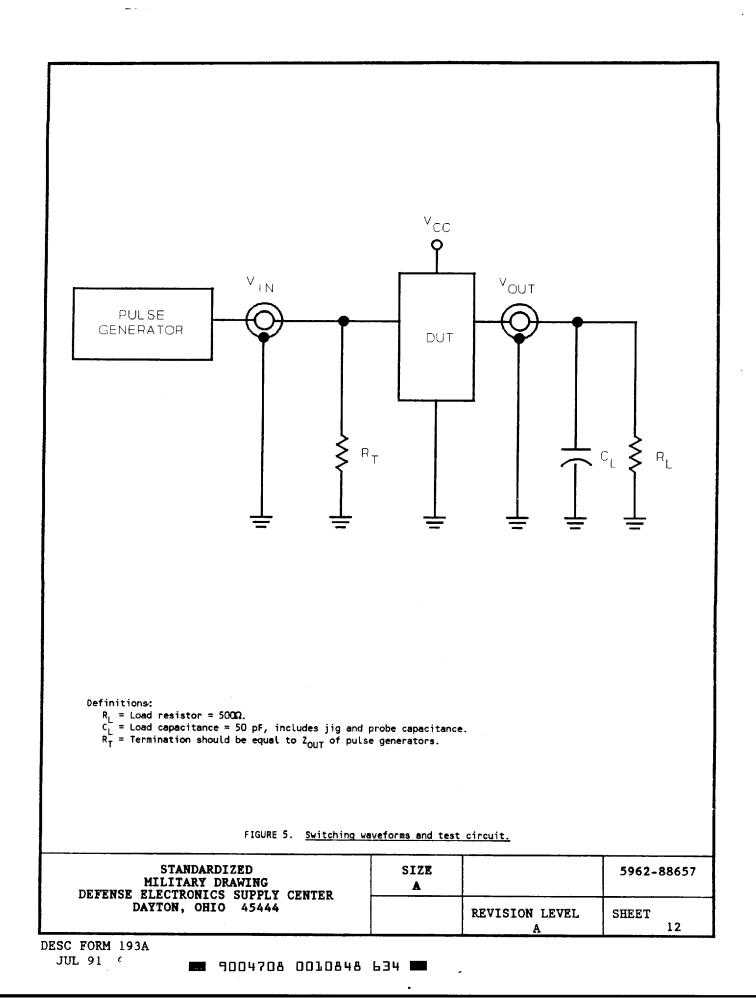

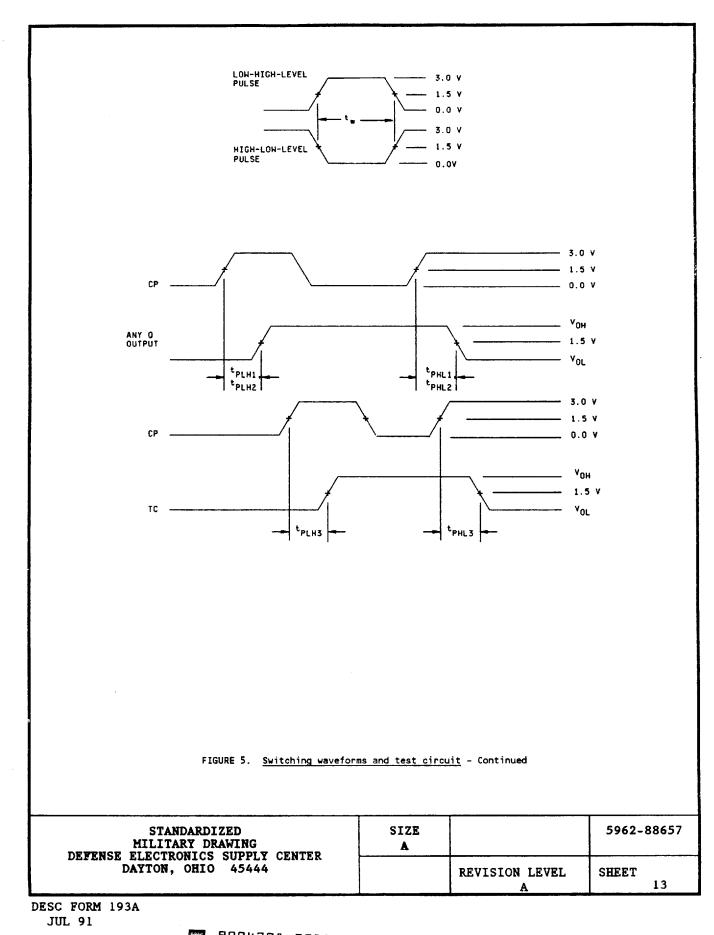

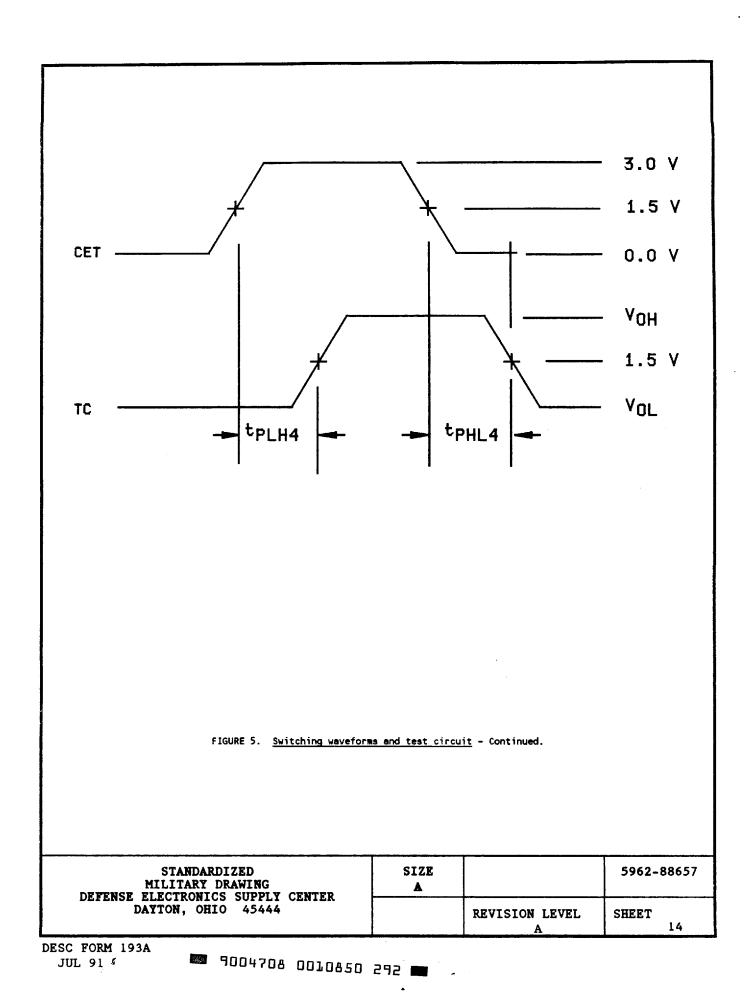

- 3.2.6 <u>Switching waveforms and test circuit</u>. The switching waveforms and test circuit shall be as specified on figure 5.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103 (see 6.6 herein).

- 3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.6 herein). The certificate of compliance submitted to DESC-ECC prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change</u>. Notification of change to DESC-ECC shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.9 <u>Verification and review</u>. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-88657 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>4 |

DESC FORM 193A JUL 91 4

| Test                                               | Symbol              | Conditions $-55^{\circ}C \leq T_{C} \leq +125$                                                                                                                                                               | 5°C                                           | Device<br>type | Group A<br>subgroups | Lim.       | its  | Unit            |

|----------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------|----------------------|------------|------|-----------------|

|                                                    | ļ                   | V <sub>CC</sub> = 5.0 V dc<br>unless otherwise                                                                                                                                                               | ±10%<br>specified                             |                |                      | <br>  Min  | Max  | 1               |

| High level output<br>voltage                       | v <sub>он1</sub>    | V <sub>CC</sub> = 4.5 V<br>  V <sub>IL</sub> = 0.8 V maximum                                                                                                                                                 | I <sub>OH</sub> = -300 μA                     | 01, 02         | 1, 2, 3              | 4.3        |      | \               |

|                                                    |                     | <br>                                                                                                                                                                                                         | <br>  I <sub>OH</sub> = -12 mA<br>            |                |                      | 2.4        |      |                 |

|                                                    | V <sub>OH2</sub> 1/ | V <sub>CC</sub> = 4.5 V<br>  V <sub>IL</sub> = 0.8 V maximum   V <sub>IH</sub> = 3.0 V minimum                                                                                                               | I <sub>OH</sub> = -300 µA                     | 03, 04         | 1, 2, 3              | 4.3        |      | V               |

|                                                    |                     |                                                                                                                                                                                                              | I <sub>OH</sub> = -12 mA                      |                |                      | 2.4        |      |                 |

| Low level output<br>voltage                        | V <sub>OL</sub> 1   | V <sub>CC</sub> = 4.5 V                                                                                                                                                                                      | I <sub>OL</sub> = 300 μA                      | _  01, 02      | 1, 2, 3              |            | 0.2  | <br>  V<br>     |

|                                                    |                     | <del>*</del> ''<br> <br>                                                                                                                                                                                     | I <sub>OL</sub> = 32 mA                       |                |                      |            | 0.5  |                 |

|                                                    | V <sub>OL2</sub> 1/ | V <sub>CC</sub> = 4.5 V<br>  V <sub>IL</sub> = 0.8 V maximum   V <sub>IH</sub> = 3.0 V minimum                                                                                                               | I <sub>OL</sub> = 300 μA<br><u>2</u> /        | 03, 04         | 1, 2, 3              |            | 0.2  | V               |

|                                                    |                     | <del></del><br> <br>                                                                                                                                                                                         | <br>  I <sub>OL</sub> = 32 mA                 |                |                      | ]<br> <br> | 0.5  |                 |

| Input clamp voltage                                | VIK                 | v <sub>CC</sub> = 4.5 v, I <sub>IN</sub> = -1                                                                                                                                                                | 18 mA                                         | Ali            | 1                    |            | -1.2 | V               |

| High level input<br>current                        | IIH                 | V <sub>CC</sub> = 5.5 V, V <sub>IN</sub> = 5.                                                                                                                                                                | .5 V                                          | All            | 1, 2, 3              |            | 5.0  | <br>  µА<br>    |

| Low level input<br>current                         | IIL                 | V <sub>CC</sub> = 5.5 V, V <sub>IN</sub> = GN                                                                                                                                                                | ND                                            | ALL            | 1, 2, 3              |            | -5.0 |                 |

| Short circuit<br>output current                    | I os                | <br> V <sub>CC</sub> = 5.5 V <u>3</u> /<br> V <sub>OUT</sub> = GND                                                                                                                                           |                                               | All            | 1, 2, 3              | -60        |      | mA              |

| Quiescent power<br>supply current<br>(CMOS inputs) | 1 <sub>CCQ</sub>    | $ V_{CC}  = 5.5 \text{ V}, V_{IN} \le 0.$ $ V_{IN}  \ge 5.3 \text{ V}, f_{I} = f_{CH}$                                                                                                                       | .2 V or<br><sub>P</sub> = 0 MHz               | All            | 1, 2, 3              |            | 1.5  | mA              |

| Quiescent power<br>supply current<br>(TTL inputs)  | ΔICC                | $v_{cc} = 5.5 \text{ v}, v_{\underline{1}} = 3.$                                                                                                                                                             | .4 V                                          | All            | 1, 2, 3              |            | 2.0  |                 |

| Dynamic power<br>supply current                    | ICCD                | $ V_{CC}  = 5.5 \text{ V}, \underline{V}_{IN} \ge 5.$ $ V_{IN}  \le 0.2 \text{ V}, \text{SR} = V_{CC}$ $ \text{outputs open, one bi} $ $ f_T  = 5 \text{ MHz}, f_{CP} = 10$ $ \text{50 percent duty cyclo} $ | t toggling,<br>MHz <u>5</u> /<br><del>e</del> | ALL            |                      |            | 0.25 | mA/MHz<br> <br> |

| See footnotes at en                                | d of tabl           | CEP = CET = PE = GND<br>.e.                                                                                                                                                                                  |                                               |                |                      |            |      | <u>i</u>        |

|                                                    | LLITAR              | ARDIZED<br>Y DRAWING                                                                                                                                                                                         |                                               | SIZE<br>A      |                      |            | 596  | 2-8865          |

|                                                    |                     | ICS SUPPLY CENTI<br>HIO 45444                                                                                                                                                                                | ER                                            |                | REVISION             | LEVEL<br>A | SHEE | T 5             |

DESC FORM 193A JUL 91

9004708 0010841 28T 📟

| Test                                                                       | Symbol                        | Conditions<br>  -55°C ≤ T <sub>C</sub> ≤ +125°C<br>  V <sub>CC</sub> = 5.0 V dc ±10%                                                                                                        |               | Device<br>type | Group A         | Lim | its            | Unit                                  |

|----------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|-----------------|-----|----------------|---------------------------------------|

|                                                                            |                               | unless otherwise specif                                                                                                                                                                     | ied           |                |                 | Min | Max            |                                       |

| Total power supply<br>current                                              | <sup>I</sup> cc<br><u>6</u> / | $V_{\rm CC}$ = 5.5 V, f <sub>CP</sub> = 10 MHz, outputs open, $V_{\rm IN} \geq$ 5.3 V o $V_{\rm IN} \leq$ 0.2 V, PE = CET = CET one bit toggling, at f <sub>I</sub> = 50 percent duty cycle | or<br>P = GND | All<br> <br>   | 1, 2, 3         |     | 4.0            | m <b>A</b><br>  m <b>A</b><br> <br>   |

|                                                                            |                               | $V_{CC}$ = 5.5 V, $f_{CP}$ = 10 MHz, outputs open, $V_{IN}$ = 3.4 V over $V_{IN}$ = GND, one bit toggling at $f_{I}$ = 5 MHz, 50 percent over $V_{IN}$ = CEP = PE = GND                     |               | ALL            | 1, 2, 3         |     | 6.0            |                                       |

|                                                                            |                               | $V_{\rm CC}$ = 5.5 V, $f_{\rm CP}$ = 10 MHz, outputs open, $V_{\rm IN} \geq$ 5.3 V o $V_{\rm IN} \leq$ 0.2 V, PE = CET = CEP four bits toggling, at $f_{\rm II} = 100$ percent duty cycle   | = GND 7/      | ALL            | 1, 2, 3         |     | 7.8            |                                       |

| -                                                                          |                               | $V_{CC}$ = 5.5 V, $f_{CP}$ = 10 MHz,<br>outputs open, $V_{IN}$ = 3.4 V o<br>$V_{IN}$ = GND, four bits toggLi<br>lat $f_{I}$ = 5 MHz, 50 percent d<br>CET = CEP = PE = GND                   | ng <u>/</u> / | ALL            | 1, 2, 3         |     | 12.8           |                                       |

| Functional tests                                                           | 8/                            | <br> See 4.3.1d<br>                                                                                                                                                                         |               | ALL            | 7, 8            |     |                |                                       |

| Input capacitance                                                          | cIN                           | <br> See 4.3.1c                                                                                                                                                                             |               | All            | 4               |     | 10             | pF                                    |

| Output capacitance                                                         | Cour                          | <br> See 4.3.1c                                                                                                                                                                             |               | ALL            | 4               |     | 12             | ρF                                    |

| Propagation delay<br>t <u>im</u> e CP to Q <sub>n</sub><br>(PE input high) | t<br>PLH1<br>t<br>PHL1        | C <sub>L</sub> = 50 pF<br>R <sub>L</sub> = 500Ω <u>9</u> /<br>See figure 5                                                                                                                  |               | 01,03          | 9,10,11         | 2.0 | 11.5           | ns                                    |

|                                                                            |                               |                                                                                                                                                                                             |               | 02,04          | -               | 2.0 | 7.5            | -                                     |

| ropagation delay                                                           | t <sub>PLH2</sub>             |                                                                                                                                                                                             |               | 01,03          |                 | 2.0 | 10.0           | _                                     |

| (PE input low)                                                             | <del> </del>                  |                                                                                                                                                                                             | <u> </u>      | 02,04          |                 | 2.0 | 6.5            | _ <br>_                               |

| ropagation delay<br>time CP to TC                                          | t <sub>PLH3</sub>             |                                                                                                                                                                                             | <u>.</u>      | 01,03          | <br>            | 2.0 | <br>  16.5<br> | <br>                                  |

|                                                                            | <del> </del>                  |                                                                                                                                                                                             |               | 02,04          |                 | 2.0 | 10.8           | ]<br>_[                               |

| ropagation delay<br>time CET to TC                                         | t <sub>PLH4</sub>             |                                                                                                                                                                                             |               | 01,03          | 1               | 1.5 | 9.0            | -!                                    |

| ee footnotes at end                                                        | of table.                     |                                                                                                                                                                                             |               | 02,04          |                 | 1.5 | 6.5            | <u> </u>                              |

|                                                                            |                               |                                                                                                                                                                                             |               |                |                 |     |                |                                       |

| S<br>MTT                                                                   | TANDAR                        | DIZED<br>DRAWING                                                                                                                                                                            | SIZE          |                |                 |     | 5962-          | 88657                                 |

| DEFENSE ELE                                                                | CTRONIC                       | S SUPPLY CENTER O 45444                                                                                                                                                                     | A             |                | <del></del>     |     |                | · · · · · · · · · · · · · · · · · · · |

|                                                                            | , 0111                        | - 1611 <b>1</b>                                                                                                                                                                             |               | RE             | EVISION LE<br>A | VEL | SHEET          | 6                                     |

DESC FORM 193A JUL 91 g

**9004708 0010842 116 📼**

## TABLE I. <u>Electrical performance characteristics</u> - Continued.

- 1/ For dynamic operation of device types 03 and 04 a  $V_{IH}$  level between 2.0 V and 3.0 V may be recognized by these devices as a high logic level input. For static operation of device types 03 and 04 a  $V_{IH} \ge 2.0$  V will be recognized by these devices as a high logic level input. Users are cautioned to verify that this change will not affect their system.

- $\underline{\mathbf{Z}}$ / Guaranteed by testing at worst case condition of  $\mathbf{V}_{CC}$  = 3 volts.

- $\underline{\underline{3}}$ / Not more than one output should be shorted at one time. Duration of the short circuit test should not exceed 1 second.

- $\underline{4}$ / In accordance with TTL driven input ( $V_{IN} = 3.4 \text{ V dc}$ ); all other outputs at  $V_{CC}$  or GND.

- 5/ This parameter is not directly testable, but is derived for use in total power supply calculations.

- $\underline{6}$ /  $I_{CC} = I_{CCQ} + (\Delta I_{CC} \times D_H \times N_T) + I_{CCD} (f_{CP}/2 + f_I \times N_I).$

Where:  $D_H = Duty$  cycle for TTL inputs high.  $N_T = Number of TTL inputs at <math>D_H$ .

$f_I^{\dagger}$  = Input frequency in MHz.  $N_I^{\dagger}$  = Number of inputs at  $f_I^{\dagger}$ .  $f_{CP}^{\dagger}$  = Clock input frequency in MHz.

- 7/ Guaranteed, if not tested.

- 8/ Due to internal noise problems, device types 03 and 04 cannot meet the threshold limits required in accordance with MIL-STD-883, test method 5004, for the  $V_{IH}$  minimum limit (2.0 V) of this technology family. For device types 03 and 04, use a  $V_{IH}$  limit of 3.0 V. The  $V_{IL}$  limit (0.8 V) remains unchanged. Users are cautioned to verify that this change will not affect their system.

- $\underline{9}$ / Minimum limits are guaranteed, if not tested on propagation delays.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-88657 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET 7    |

DESC FORM 193A JUL 91

9004708 0010843 052

| <br>  Device types                                     | 01, 02, 0               | 3 and 04                                                                              |

|--------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------|

| Case outlines                                          | E and F                 | 2                                                                                     |

| Terminal<br>number                                     | <br>  Term<br>  syml    |                                                                                       |

| 1 1 2 3 4 5 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 | SRP OT 23PD T SO CI III | NCRP OTIC 2 APP D C GNC ET CC GNC ET CC GNC ET CC GNC GNC GNC GNC GNC GNC GNC GNC GNC |

|                   | PIN description                         |

|-------------------|-----------------------------------------|

| Terminal symbol   | Description                             |

| CEP               | Count enable parallel input             |

| CET               | Count enable trickle input              |

| СР                | Clock pulse input (active rising edge)  |

| SR                | Synchronous reset input (active low)    |

| P <sub>0</sub> -3 | Parallel data inputs                    |

| PE                | <br> Parallel enable input (active low) |

| <sup>Q</sup> 0-3  | <br> Flip-flop outputs                  |

| TC                | <br> Terminal count output              |

FIGURE 1. <u>Terminal connections</u>.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                     | <b>5962-</b> 88657 |

|------------------------------------------------------------------------------------|-----------|---------------------|--------------------|

|                                                                                    |           | REVISION LEVEL<br>A | SHEET<br>8         |

DESC FORM 193A

JUL 91 #

3004708 0010844 T99 📼

| SR | PE           | CET     | CEP | <br>  Function    |       |

|----|--------------|---------|-----|-------------------|-------|

| L  | X            | x       | X   | Reset (clear)     | 1/    |

| н  | L            | <br>  x | X   | Load (Pn to Qn)   | 1/ 2/ |

| Н  | <br>  H<br>! | н       | н   | Count (increment) | 1/ 2/ |

| н  | <br>  H      | L       | x   | No change (hold)  | 1/    |

| H  | <br>  H      | х       | Ļ   | No change (hold)  | 1/    |

H = High voltage level steady-state.

# NOTES:

- Action on the rising clock (CP) edge. For any other clock state, the outputs remain unchanged.

- The TC output goes to a high logic voltage level, iff all Qn and CET inputs are at a logic voltage level, else TC is at a low logic voltage level.

FIGURE 2. Truth table.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                     | 5962-88657 |

|---------------------------------------------------------------------------------------------|-----------|---------------------|------------|

|                                                                                             |           | REVISION LEVEL<br>A | SHEET<br>9 |

DESC FORM 193A JUL 91

9004708 0010845 925

L = Low voltage level steady-state.

X = Irrelevant.

DESC FORM 193A JUL 91

9004708 0010847 7T8 **=**

Powered by ICminer.com Electronic-Library Service CopyRight 2003

9004708 0010849 570

DESC FORM 193A JUL 91

- 9004708 0010851 129 **-**

### 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

TABLE II. <u>Electrical test requirements</u>.

| MIL-STD-883 test requirements                                      | Subgroups<br>(per method<br>5005, table I) |

|--------------------------------------------------------------------|--------------------------------------------|

| Interim electrical parameters (method 5004)                        |                                            |

| Final electrical test parameters (method 5004)                     | <br>  1*, 2, 3, 7,<br>  8, 9, 10, 11       |

| Group A test requirements<br>(method 5005)                         | 1, 2, 3, 4, 7,<br>8, 9, 10, 11             |

| Groups C and D end-point<br>electrical parameters<br>(method 5005) | 1, 2, 3                                    |

<sup>\*</sup> PDA applies to subgroup 1.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. C<sub>IN</sub> and C<sub>OUT</sub> shall be measured only for initial qualification and after process or design changes which may affect capacitance. Capacitance shall be measured between the designated terminal and GND at a frequency of 1 MHz. Test all applicable pins on 5 devices with no failures.

- d. Subgroups 7 and 8 tests shall include verification of the truth table.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                     | <b>5962-88</b> 657 |

|------------------------------------------------------------------------------------|-----------|---------------------|--------------------|

|                                                                                    |           | REVISION LEVEL<br>A | SHEET<br>16        |

DESC FORM 193A JUL 91 F

**■ 9004708 0010852 065** ■

### 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition A, B, C, or 0 using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125$ °C, minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

#### PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

#### 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-481 using DD Form 1693, Engineering Change Proposal (Short Form).

- 6.4 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and the applicable SMD. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronics devices (FSC 5962) should contact DESC-ECC, telephone (513) 296-6047.

- 6.5 <u>Comments</u>. Comments on this drawing should be directed to DESC-ECC, Dayton, Ohio 45444, or telephone 513-296-8525.

- 6.6 <u>Approved sources of supply</u>. Approved sources of supply are listed in MIL-BUL-103. Additional sources will be added to MIL-BUL-103 as they become available. The vendors listed in MIL-BUL-103 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DESC-ECC. The approved sources of supply listed below are for information purposes only and are current only to the date of the last action of this document.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-88657 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET      |

DESC FORM 193A JUL 91

£

■ 9004708 0010853 TT1 **■**