# ICs for Communications

4 Channel ADPCM Controller Quad ADPCM

PEB 7274 Version 1.2 PEF 7274 Version 1.2

Data Sheet 08.97

| PEB 7274<br>Revision History:    |                             | Current Version: 08.97                                                                     |

|----------------------------------|-----------------------------|--------------------------------------------------------------------------------------------|

| Previous Ver                     | sion: Prelimi               | inary Data Sheet 01.97                                                                     |

| Page<br>(in previous<br>Version) | Page<br>(in new<br>Version) | Subjects (major changes since last revision)                                               |

| -                                | 5                           | List of figures (new)                                                                      |

| 52                               | 52                          | Note added (The last 15 bits)                                                              |

| 72                               | 72                          | Input leakage current (Values added for neg. temperature range, XTAL1)                     |

| 72                               | 72                          | Input/Output voltage (addapted to TTL levels, test conditions added)                       |

| 74                               | 74                          | Frame strobe delay t <sub>FSD</sub> (new)                                                  |

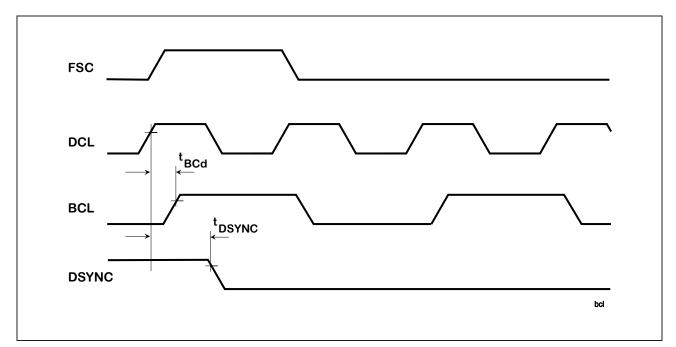

| 77                               | 77                          | Bit clock delay t <sub>BCd</sub> = 25 ns (changed)<br>DSYNC delay t <sub>DSYNC</sub> (new) |

#### Edition 08.97

This edition was realized using the software system FrameMaker®.

Published by Siemens AG, HL SW Balanstraße 73, 81541 München © Siemens AG 08.97. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

**Components used in life-support devices or systems must be expressly authorized for such purpose!** Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endan-

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.6.1<br>1.6.2<br>1.6.3<br>1.6.4                                            | Overview         Features         Logic Symbol         Pin Configuration         Pin Definitions and Functions         Functional Block Diagram         System Integration         PCM-4 System         PCM-4 System using Standard Codec Filters         PCM-8 System         DECT Linecard                                                                                                                                                                                                                                              | 7<br>8<br>9<br>.10<br>.13<br>.14<br>.14<br>.16<br>.17                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.4.2.1<br>2.4.2.2<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.10.1 | Functional DescriptionADPCM CoderPCM InterfacePropagation DelayEchosuppression and Speech DetectionEchosuppressionSpeech DetectorNoise MonitorSpeech Detection PreprocessingFax/Modem DetectionArtificial Echo LossCongestion Tone GeneratorFrame Strobe OutputsSerial Microcontroller InterfaceBoundary Scan Test ControllerTAP Controller                                                                                                                                                                                               | .19<br>.20<br>.21<br>.25<br>.25<br>.29<br>.30<br>.32<br>.35<br>.38<br>.39<br>.42<br>.43 |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14                   | Register and DSP RAM Location DescriptionConfiguration Register (CR)Compression Rate Register (CRR)Uncompressed Time slot Registers (UT0 UT3)Decoder PCM Position Register (DPP)MSB of PCM Time Slots Register (MSB)Echo Suppressor Enable Register (ESE)Additional Feature Register (ADF)Additional Feature Register 2 (ADF2)Fax/Modem Detection Enable Register (FDE)Fax / Modem Detection Status Register (FDS)DSP Status Register (DST)Command Register (COM)Address of DSP RAM Register (ADR)DSP RAM Data High Byte Register (DATAH) | .48<br>.49<br>.50<br>.52<br>.53<br>.54<br>.55<br>.56<br>.56<br>.57<br>.58               |

| DSP RAM Data Low Byte Register (DATAL).58DSP RAM Loactions.59Programming DSP RAM Cells for Extended Features.60Congestion Tone Generator.61Tone Filter.62Artificial Echo Loss Gain (AEL_GAIN).63Speech Detector and Noise Monitor.64Echo Suppressor.66Fax/Modem Detection.68 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical Characteristics.71Absolute Maximum Ratings.71DC Characteristics.72Capacitances.73AC Characteristics.73PCM Interface Timing.74Serial Microcontroller Interface Timing.75Boundary Scan Timing.76BCL Timing.77                                                       |

| Package Outlines                                                                                                                                                                                                                                                             |

| Appendix.79Proposed Default Values for DSP Locations.79Working Sheet for Register Programming.80Development Tools.81STSI 4000 PCM-4 Userboard Kit.81SIPB 7274 Quad ADPCM Kit.82                                                                                              |

|                                                                                                                                                                                                                                                                              |

| Figure 1:  | Logic Symbol                                               | . 8 |

|------------|------------------------------------------------------------|-----|

| Figure 2:  | Pin Configuration (top view)                               | . 9 |

| Figure 3:  | Block Diagram                                              | 13  |

| Figure 4:  | Integration in PCM-4 System                                | 14  |

| Figure 5:  | Integration in PCM-4 System with Automatic Modem Handling  | 15  |

| Figure 6:  | Integration in PCM-4 Systems using Standard Codec Filters  | 16  |

| Figure 7:  | Integration in PCM-8 Systems                               | 17  |

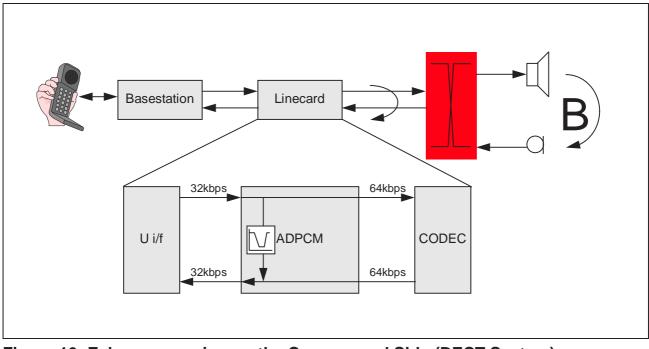

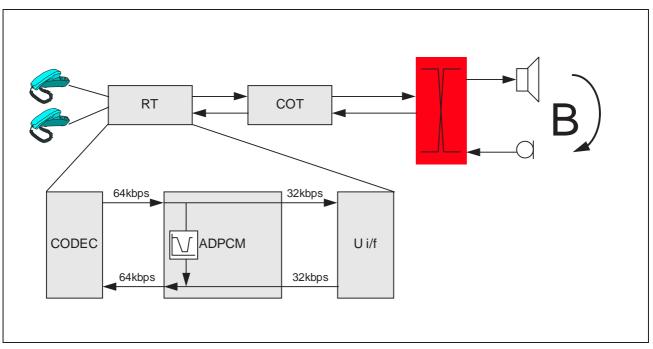

| Figure 8:  | Integration in a DECT Linecard                             | 18  |

| Figure 9:  | Encoder Block Diagram                                      | 19  |

| Figure 10: | Decoder Block Diagram                                      | 20  |

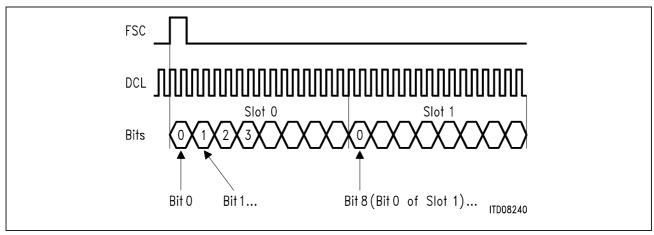

| Figure 11: | Allocation of Data to Slots and within the Slots           | 21  |

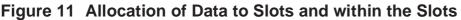

| Figure 12: | Decoder / Encoder Timing in a PCM-4 System                 | 22  |

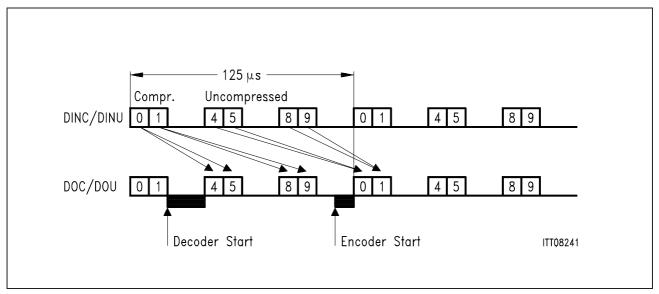

| Figure 13: | Decoder / Encoder Timing in a PCM-8 System                 | 22  |

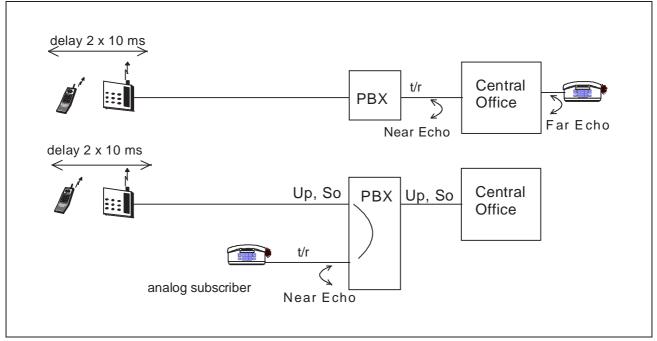

| Figure 14: | Echo Sources in a DECT PBX System                          | 25  |

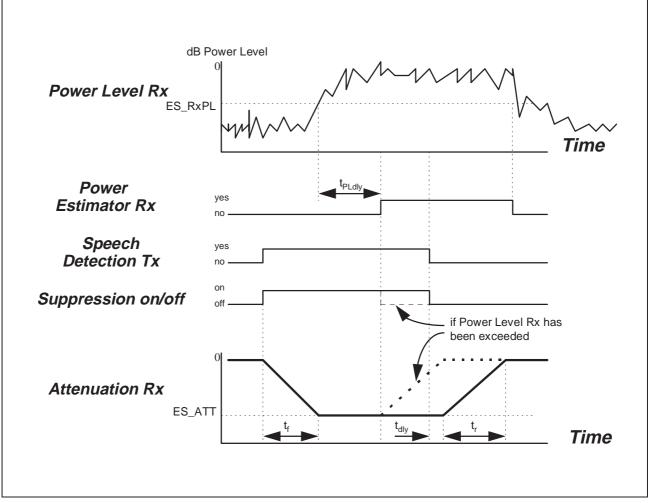

| Figure 15: | Echosuppressor Functionality                               | 26  |

| Figure 16: | Echosuppression on the Compressed Side (DECT System)       | 27  |

| Figure 17: | Echosuppresion on the Uncompressed Side (PCM-4/8 System)   | 27  |

| Figure 18: | Speech Detector Mechanism                                  | 29  |

| Figure 19: | Speech Detector Parameters                                 | 30  |

| Figure 20: | Speech Detection Principle                                 | 33  |

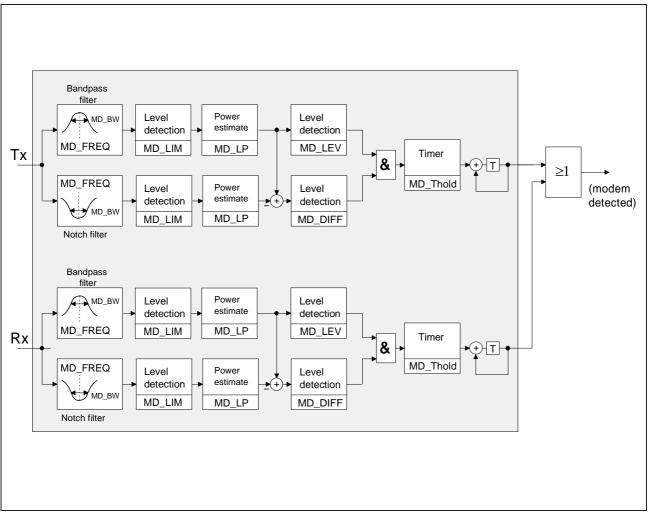

| Figure 21: | Fax/Modem Tone Detection                                   | 36  |

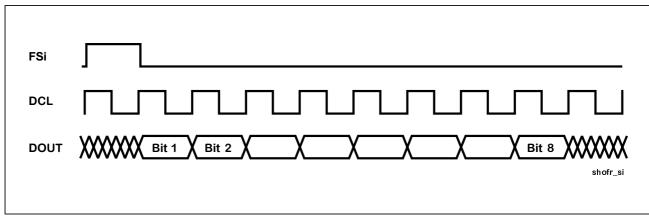

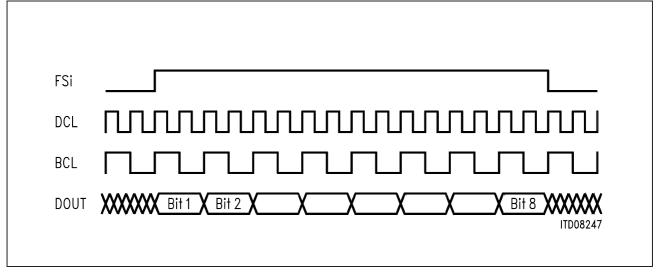

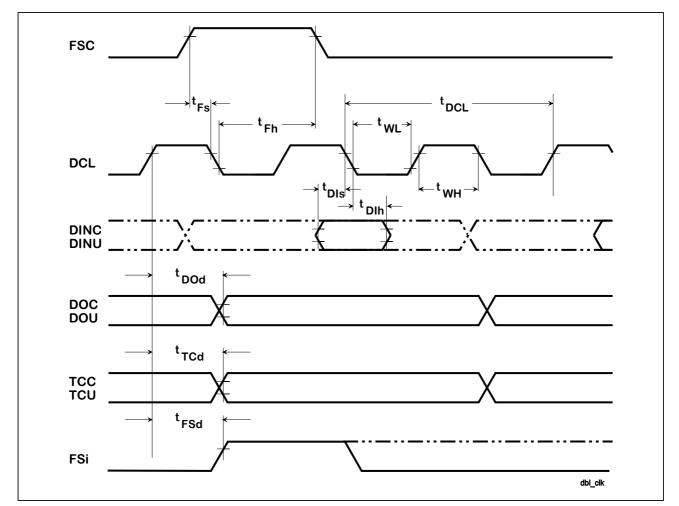

| Figure 22: | Frame Strobe Output: Short Frame Timing, Single Clock Mode | 40  |

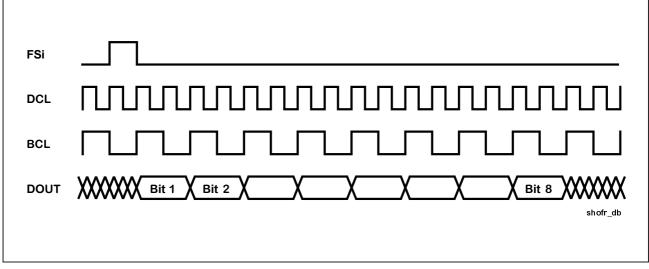

| Figure 23: | Frame Strobe Output: Short Frame Timing, Double Clock Mode | 40  |

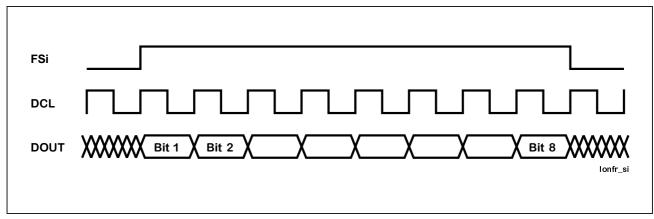

| Figure 24: | Frame Strobe Output: Long Frame Timing, Single Clock Mode  | 41  |

| Figure 25: | Frame Strobe Output: Long Frame Timing, Double Clock Mode  | 41  |

| Figure 26: | Microcontroller Interface Timing: Write Access             | 42  |

| Figure 27: | Microcontroller Interface Timing: Read Access              | 42  |

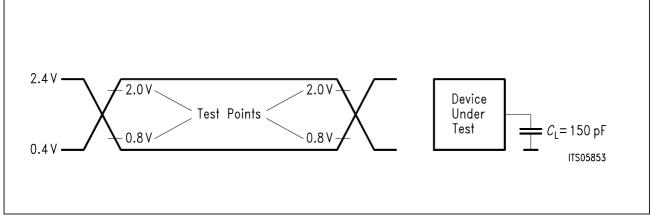

| Figure 28: | I/O Waveforms for AC Tests                                 | 73  |

| Figure 29: | PCM Interface Timing in Double Clocking Model              | 74  |

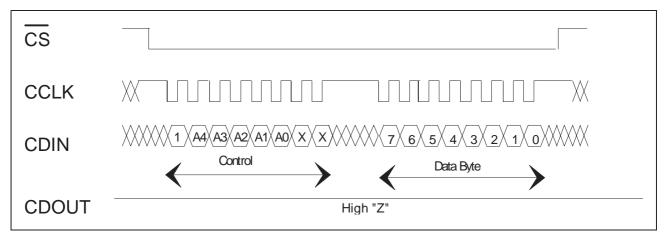

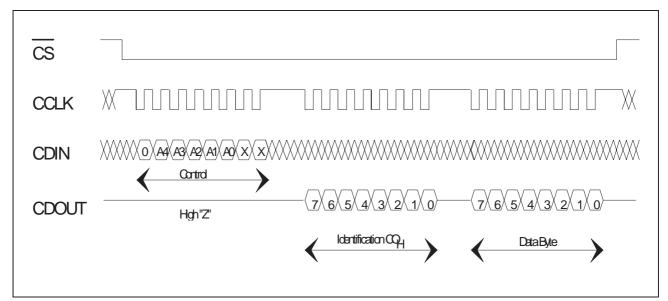

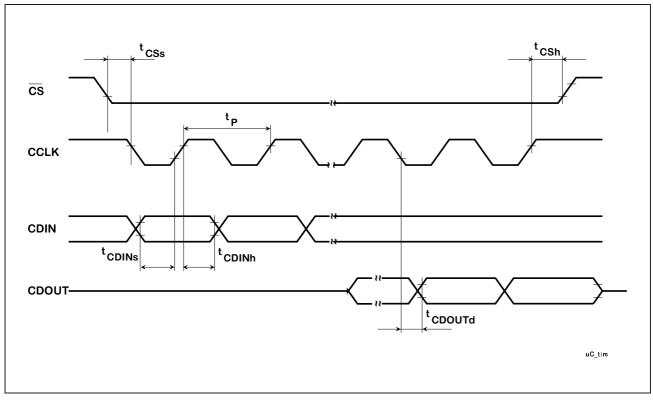

| Figure 30: | Serial µC Interface Timing                                 | 75  |

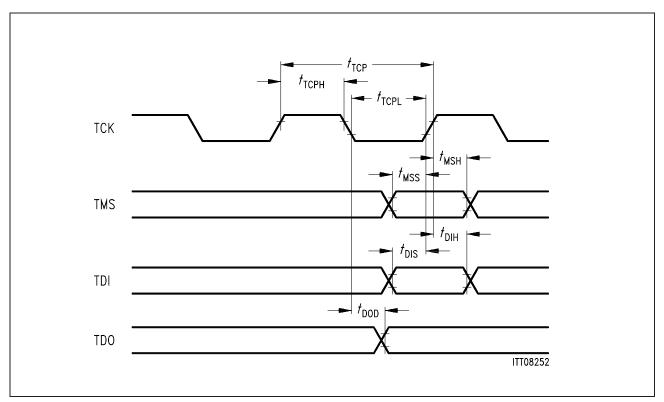

| Figure 31: | Boundary Scan Timing                                       | 76  |

| Figure 32: | Bit Clock Timing                                           | 77  |

|            | Working Sheet for Register Programming                     |     |

|            | STSI 4000 PCM4 Userboard Kit (Euroset not included in Kit) |     |

| Figure 35: | SIPB 7274 Quad ADPCM Kit                                   | 82  |

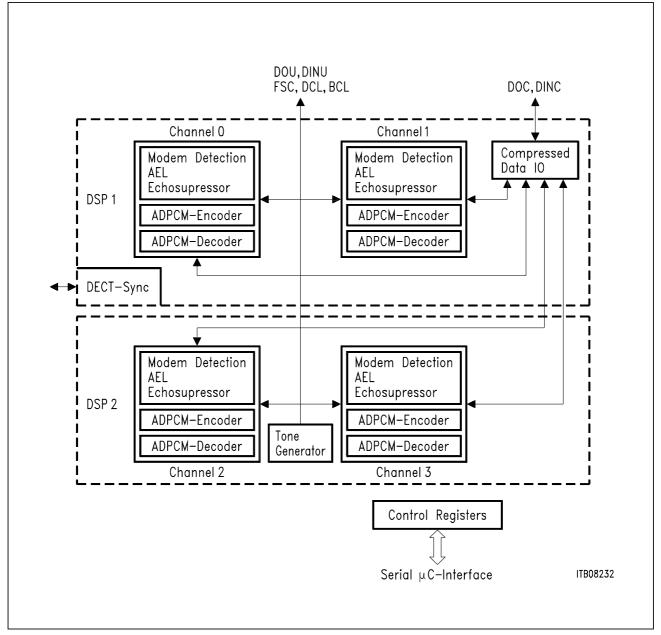

#### 1 Overview

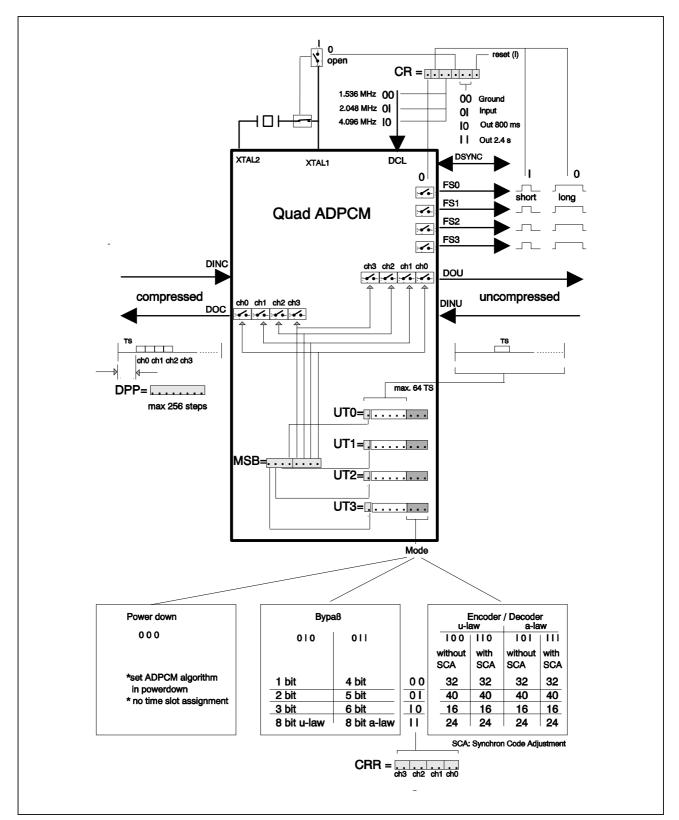

The four channel ADPCM Controller PEB 7274 (Quad ADPCM) features four independent full duplex Adaptive Differential Pulse Code Modulation voice coders with individually selectable compression down to 16, 24, 32 or 40 kbit/s as specified by CCITT Recommendation G.726. A-law,  $\mu$ -law or 16-bit linear operation is provided.

An optional echosupression algorithm is included as well as Artificial Echo loss insertion and a programmable tone generation.

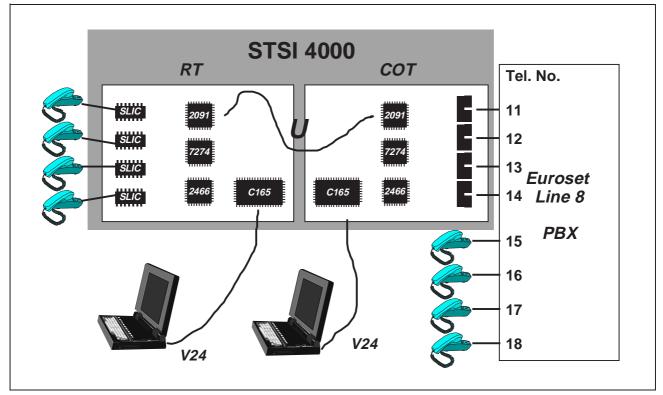

The device is optimized for operation in PCM-4 and PCM-8 systems together with the PEB 2466 SICOFI-4- $\mu$ C and the PEB 2091 IEC-Q V5.x. An internal FAX/Modem recognition allows simple allocation of the data rate needed for modem transmission or connection of modems/data rate convertors as the PSB 7110 ISAR.

The Quad ADPCM provides two PCM interfaces allowing free selection of input and output time slots via register bit setting. A bypass mode facilitates data over voice applications.

Flexible applications are supported by connecting a low cost microcontroller via a serial processor interface. Indirect access to DSP RAM is provided via the controller interface.

Additional frame synchronization signals for each channel with selectable timing conditions allow the direct connection to standard codec filters.

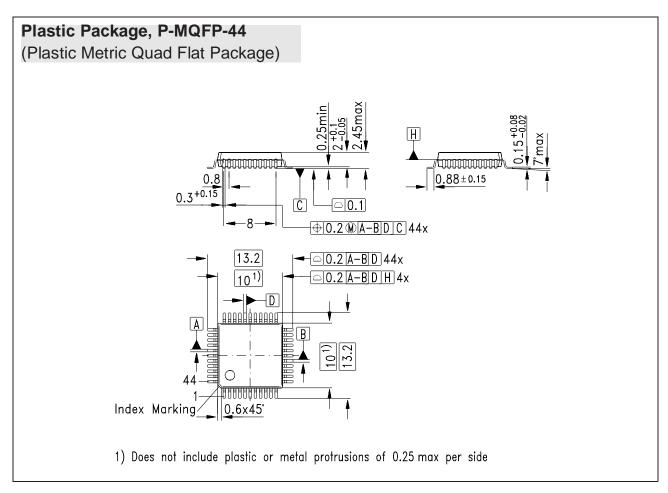

The Quad ADPCM is a low power consuming CMOS device. It comes in a P-MQFP-44 package.

# **4 Channel ADPCM Controller** Quad ADPCM

# Version 1.2

#### 1.1 **Features**

- 4 full duplex ADPCM Voice Coders

- 16/24/32/40 kbit/s compression rate

- CCITT G.726, G.721 compliant

- · Compression rate individually programmable during operation

- Cascadable for PCM-8 Systems

- Parameterizable Echosupression

- Programmable tone generation

- A-Law, µ-Law or 16 bit linear operation

- Pprogrammable FAX/Modem-tone detection, compliant to G.164

- Optional Artificial Echo Loss compliant to ETSI ETS 300 175

- Stand-alone operation in PCM-4 Systems without microcontroller

- A-law or µ-law default set per pin strapping

- 2 PCM-Interfaces 1.536, 2.048 or 4.096 MHz providing 12 to 64 time slots

- Frame Strobe Signals for standard codec filters, long frame and short frame timing

- Serial Microcontroller Interface

- DECT synchronization clock

- JTAG Boundary Scan compliant to IEEE 1149.1

- Sub-micron CMOS Technology

- P-MQFP-44 Package

| CMOS       |  |

|------------|--|

| STRAKE STR |  |

|            |  |

P-MQFP-44

7

**PEB 7274**

**PEF 7274**

PEB 7274 PEF 7274

#### **Overview**

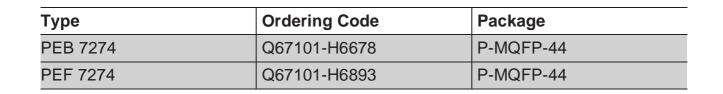

# 1.2 Logic Symbol

Figure 1 Logic Symbol

PEB 7274 PEF 7274

#### **Overview**

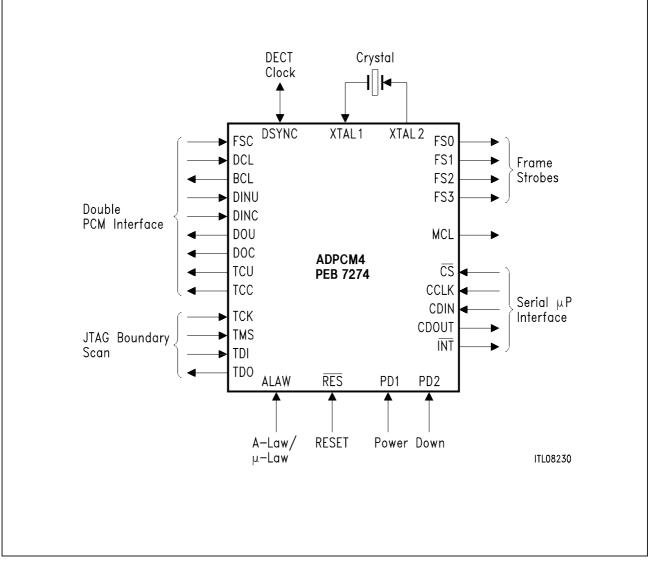

# 1.3 Pin Configuration

(top view)

Figure 2 Pin Configuration (top view)

# Overview

# 1.4 Pin Definitions and Functions

| Pin No. | Symbol | Input (I)  | Function |

|---------|--------|------------|----------|

|         |        | Output (O) |          |

|         |        | Open       |          |

|         |        | Drain (OD) |          |

# Power Supply Pins

| 7, 29 | V <sub>DD</sub> |  | Supply Voltage (5 V +/-5 %) |

|-------|-----------------|--|-----------------------------|

| 6, 28 | V <sub>SS</sub> |  | Ground (0 V)                |

# JTAG Boundary Scan

| 17 | ТСК | 1 | Test Clock                        |

|----|-----|---|-----------------------------------|

| 35 | TMS | 1 | Test Mode Select, internal pullup |

| 36 | TDI | 1 | Test Data Input, internal pullup  |

| 18 | TDO | 0 | Test Data Output                  |

# PCM Interface

| 11 | DINC | I      | Data in Compressed. Input of ADPCM data synchronous to DCL clock                                   |

|----|------|--------|----------------------------------------------------------------------------------------------------|

| 10 | DOC  | O (OD) | Data out Compressed. Output of ADPCM data synchronous to DCL clock. Open drain.                    |

| 42 | DINU | I      | Data in Uncompressed. Input of PCM data synchronous to DCL clock                                   |

| 9  | DOU  | O (OD) | Data out Uncompressed. Output of PCM data synchronous to DCL clock. Open drain.                    |

| 40 | FSC  | I      | Frame synchronization clock. The start of time slot 0 is marked.                                   |

| 41 | DCL  | I      | Data clock. Clock range 1.536 to 4.096 MHz.                                                        |

| 23 | BCL  | 0      | Bit clock. Half the DCL clock is output on this pin.                                               |

|    |      |        | Note: This pin is not included in the boundary scan path.                                          |

| 14 | TCC  | 0      | Transmit Control Compressed, low active. TCC is low during the slots data is transmitted on DOC.   |

| 15 | TCU  | 0      | Transmit Control Uncompressed, low active. TCU is low during the slots data is transmitted on DOU. |

| Pin No. | Symbol | Input (I)  | Function |

|---------|--------|------------|----------|

|         |        | Output (O) |          |

|         |        | Open       |          |

|         |        | Drain (OD) |          |

# Microcontroller Interface

| 5 | CS    | I      | Chip Select enable to read or write data, active low. Connect to $V_{\text{DD}}$ if not used.       |

|---|-------|--------|-----------------------------------------------------------------------------------------------------|

| 8 | CCLK  | I      | Controller data clock. Shifts data from or to the device. Connect to $V_{DD}$ if not used.          |

| 4 | CDIN  | I      | Controller Data In. CCLK determines the data rate. Connect to $V_{DD}$ if not used.                 |

| 3 | CDOUT | 0      | Controller Data Out. CCLK determines the data rate.<br>CDOUT is "high Z" if no data is transmitted. |

| 2 | INT   | 0 (0D) | Interrupt. Low active, open drain.                                                                  |

#### **Miscellaneous Function Pins**

| 24 | MCL  | 0 | Master Clock. The crystal clock is output to act as a DSP master clock for another Quad ADPCM. The signal is enabled by setting the bit ADF2:MCE. |

|----|------|---|---------------------------------------------------------------------------------------------------------------------------------------------------|

|    |      |   | Note: This pin is not included in the boundary scan path.                                                                                         |

| 43 | FS0  | 0 | Frame Sync 0. High during the time the uncompressed data of channel 0 is active on the PCM bus.                                                   |

| 39 | FS1  | 0 | Frame Sync 1. High during the time the uncompressed data of channel 1 is active on the PCM bus.                                                   |

| 38 | FS2  | 0 | Frame Sync 2. High during the time the uncompressed data of channel 2 is active on the PCM bus.                                                   |

| 44 | FS3  | 0 | Frame Sync 3. High during the time the uncompressed data of channel 3 is active on the PCM bus.                                                   |

| 1  | ALAW | I | Select A-law (ALAW = high) or $\mu$ -law (ALAW = low) as default setting after reset.                                                             |

| 16                                      | RES            | 1   | Master Reset, low active.                                                                                                                                                               |

|-----------------------------------------|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27                                      | XTAL1          | 1   | Crystal In. 20.48 MHz crystal or 20.48 MHz clock signal is connected.                                                                                                                   |

| 26                                      | XTAL2          | 0   | Crystal Out. 20.48 MHz crystal is connected. Leave open, if no crystal is connected.                                                                                                    |

| 37                                      | DSYNC          | I/O | DECT Sync. Output or Input of 800 ms or 2.4 s DECT master clock.                                                                                                                        |

| 13                                      | PD1            | 1   | Power Down 1. A '1' disables DSP 1. DSP 1 holds<br>operation of channels 0 and 1. Also disables data<br>input and output on the compressed side as well as<br>the DECT-sync generation. |

| 12                                      | PD2            | I   | Power down 2: A '1' disables DSP 2. DSP 2 holds operation of channels 2 and 3. Disables Congestion tone generator.                                                                      |

| 20, 21,<br>22, 30,<br>31, 32,<br>33, 34 | TEST0<br>TEST7 | 0   | Test pins. Used for production testing only. Do not connect.                                                                                                                            |

| 19                                      | TMEN           | 1   | Test pin. Used for production testing only. Active low.<br>Internal pullup. Do not connect.                                                                                             |

# Miscellaneous Function Pins (cont'd)

PEB 7274 PEF 7274

#### Overview

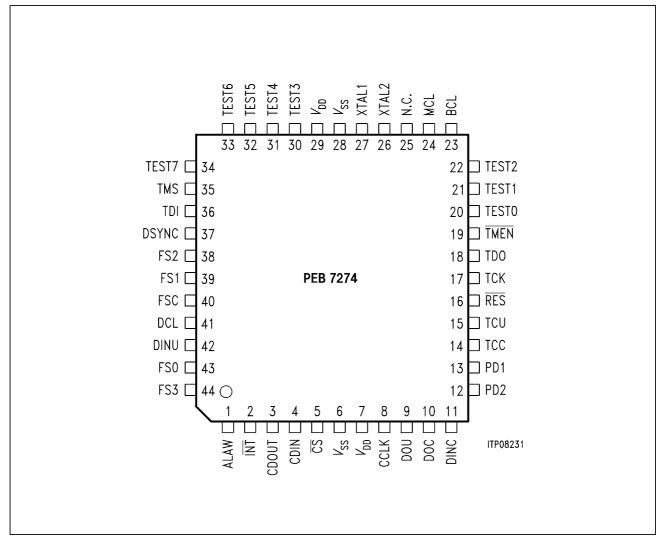

# 1.5 Functional Block Diagram

#### Figure 3 Block Diagram

Two DSP cores contain two ADPCM coders each. The I/O of the compressed data is handled by DSP 1. The tone generator resides in DSP 2. Hence, if DSP 1 is disabled (pin PD1 high), no input/output of compressed data of all four channels is possible. If DSP 2 is disabled, no tone generator is provided.

# 1.6 System Integration

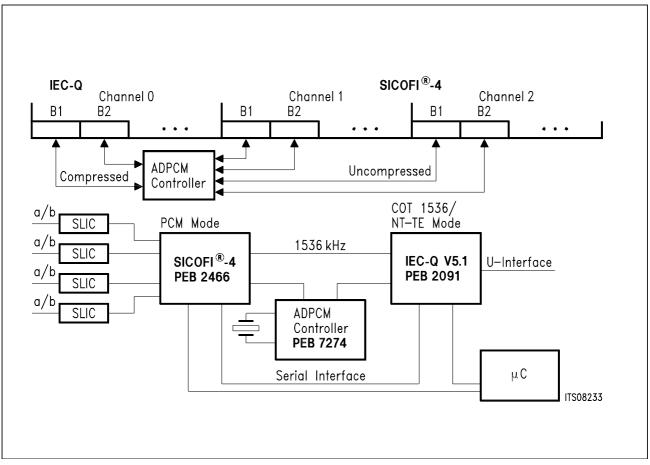

#### 1.6.1 PCM-4 System

**Figure 4** gives a general overview of integration in a PCM-4 system. The register set of the Quad ADPCM is in a default configuration. No connection to the microcontroller is necessary. The PCM interface is working with a double data clock of 1.536 MHz coming from the IEC-Q V5.x. This corresponds to a number of 12 PCM time slots or 3 IOM-channels respectively. The DINU and DINC pins are tied together as well as the DOU and DOC pins. This way, the two PCM busses are using the same physical lines. The IEC-Q is in the NT-TE-1536 mode at the NT side and the COT-1536 mode at the LT side. It uses the PCM slots 0 and 1. There, the Quad ADPCM reads and writes the compressed data. It takes the uncompressed data from the time slots 4, 5, 8 and 9 (see figure below, the most left timeslot being slot 0). The SICOFI-4- $\mu$ C is programmed to read/write these time slots.

Note that the IEC-Q uses an IOM-2 interface where control information such as C/lcommands and Monitor messages are exchanged on time slots 2 and 3. These time slots should consequently not be used to exchange compressed or uncompressed data.

Figure 4 Integration in PCM-4 System

The SICOFI-4- $\mu$ C uses the 1.536 MHz PCM clock to internally generate its masterclock. The IEC-Q also issues a 7.68 MHz clock. This clock can be used as microcontroller clock. The IEC-Q V5.x allows to program this clock rate between 0.92 and 7.68 MHz.

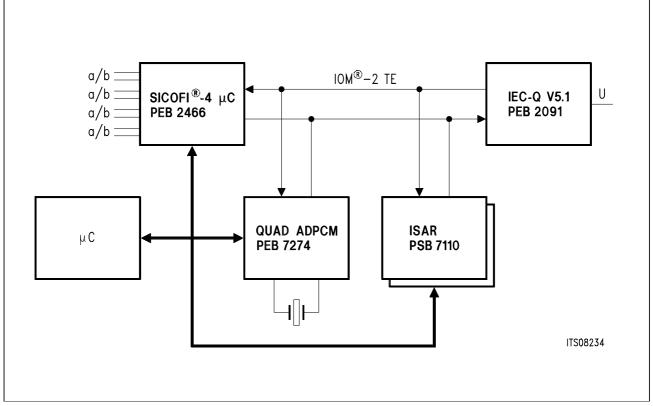

The automatic modem detection enables the PEB 7274 Quad ADPCM to monitor the compressed and uncompressed side of the PCM highway in all four channels in parallel. This allows to dynamically allocate the data rate needed for the transmission of high speed modem signals or to hand over the control to the PSB 7110 ISAR. The Quad ADPCM detects a fax/modem tone. The microcontroller then sets the compressed output of the according channel to a highly impedant state. The PSB 7110 ISAR takes over the uncompressed receive data, performs modem operation and data rate adaptation and passes the output data onto the timeslot left open by the Quad ADPCM.

#### Figure 5 Integration in PCM-4 System with Automatic Modem Handling

Two PSB 7110 ISAR provide 14.4 kbit/s modem transmission on all four channels. The ISAR occupies 3 bit leaving 5 bit for direct 14.4 kbit/s modem transmission. One ISAR can be used if fax operation is not expected on all four channels simultaneously.

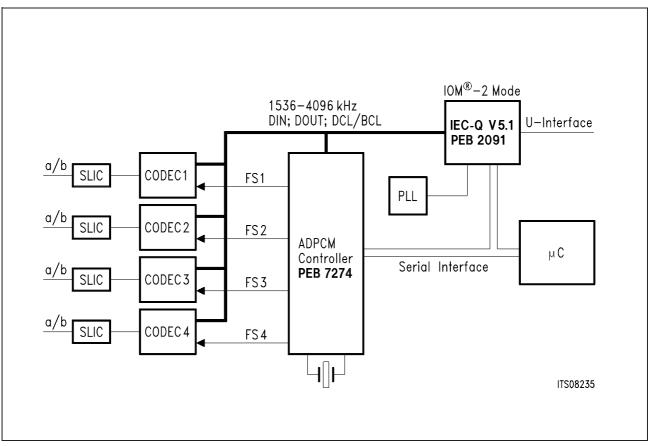

# 1.6.2 PCM-4 System using Standard Codec Filters

The Quad ADPCM provides additional frame sync signals for each channel. In case the data clock is not at a rate of 1.536 MHz, it has to be generated with an additional PLL. The microcontroller selects the appropriate timing conditions for the frame sync pulses. Short frame and long frame mode are provided.

An additional bit clock (BCL) allows to easily connect single clock mode devices (e.g. CODECs) and double clock mode devices (e.g. IEC-Q V5.x) as well.

Figure 6 Integration in PCM-4 Systems using Standard Codec Filters

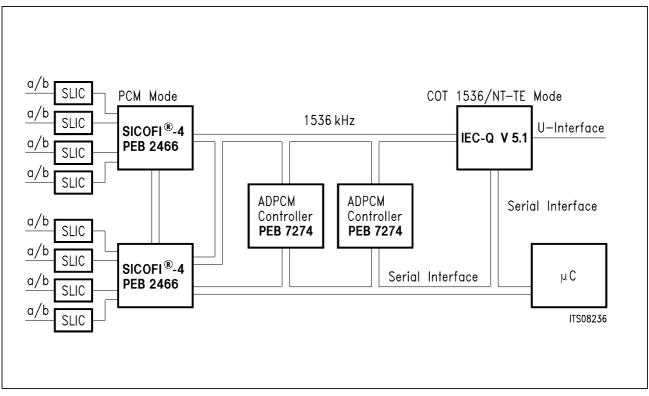

#### 1.6.3 PCM-8 System

Figure 7 Integration in PCM-8 Systems

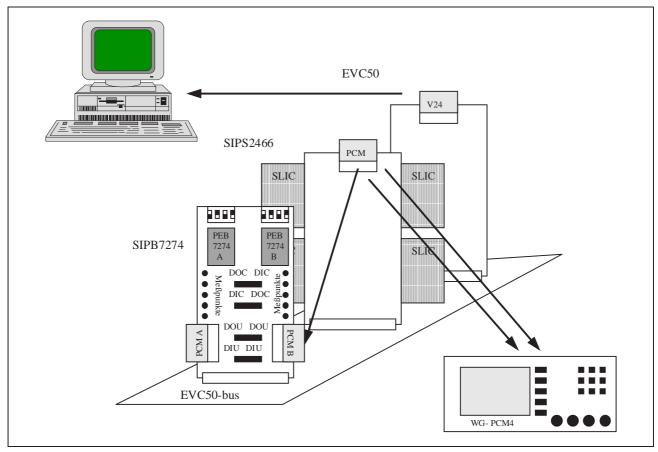

**Figure 7** depicts an integration in a PCM-8 system. The PCM interface is working with a double data clock of 1.536 MHz coming from the IEC-Q V5.x. This corresponds to a number of 12 PCM time slots or 3 IOM-channels respectively. The IEC-Q is in the NT-TE-1536 mode at the NT side and the COT-1536 mode at the LT side. It uses the PCM slots 0 and 1. There, the two Quad ADPCM read and write the compressed data. They take the uncompressed data from the time slots 4 to 11 (time slots count 0 to 11). The two SICOFI-4- $\mu$ C are programmed to read/write these time slots. The DINU and DINC pins of both Quad ADPCM are tied together as well as the DOU and DOC pins. This way, the two PCM busses of the Quad ADPCM are using the same physical lines. This is possible by proper time slot assignment.

Note that the IEC-Q uses an IOM-2 interface where control information such as C/Icommands and Monitor messages are exchanged on time slots 2 and 3. These two slots should not be used for compressed or uncompressed data transfer.

No additional clock generator for the PCM data clock is necessary because the 1.536 MHz PCM clock is issued by the IEC-Q.

The IEC-Q also issues a 7.68 MHz clock which can be used as microcontroller clock.

PEB 7274 PEF 7274

#### Overview

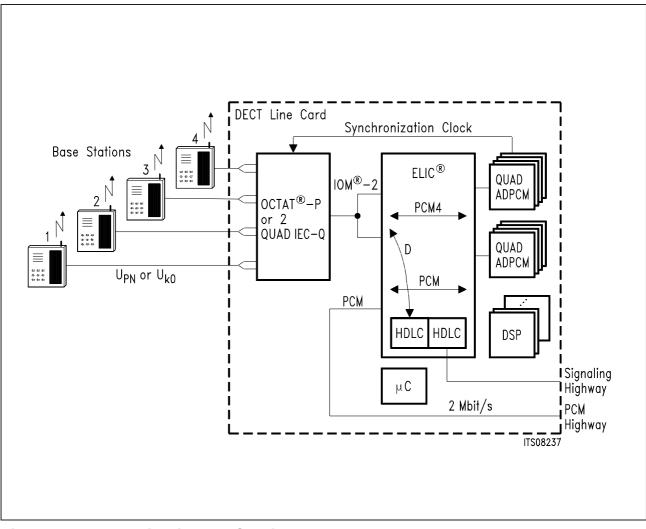

#### 1.6.4 DECT Linecard

Figure 8 Integration in a DECT Linecard

Figure **8** presents the integration in a linecard for a PBX featuring DECT basestations. The Quad ADPCM features flexible access to arbitrary time slots of the PCM highway by it's two PCM interfaces. One of the Quad ADPCM provides a DECT synchronization clock of either 800 ms or 2.4 s period. The other Quad ADPCM receive this clock for synchronized reprogramming of e.g. the data rates or other registers.

Together with the PEB 2096 OCTAT-P or the PEB 24902/PEB 24911 Quad IEC-Q as layer-1 transceivers, seamless handover is possible in the linecard.

#### 2 Functional Description

#### 2.1 ADPCM Coder

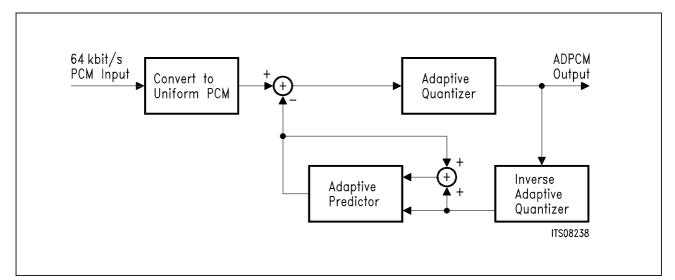

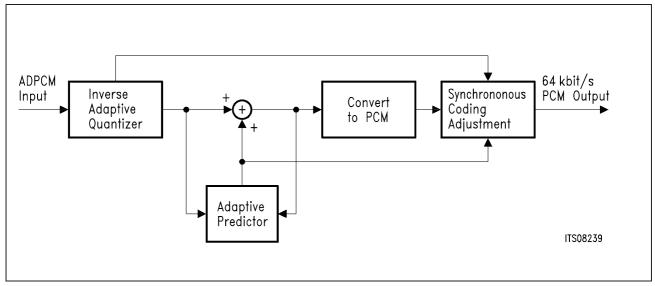

The Quad ADPCM contains two DSP cores each implementing the algorithms for two channels. It supports full duplex ADPCM coding and encoding as specified by CCITT recommendation G.726. A-law,  $\mu$ -law and 16 bit linear operation are selectable separately for each channel by setting the UTi-register corresponding to channel i.

The synchronous coding adjustment (SCA) unit of the decoder (see fig. **10**) prevents cumulative distortion occurring on tandem operation, e.g. ADPCM - PCM - ADPCM. It can optionally be disabled to improve the signal/noise ratio when going from PCM to analog coding.

Figure 9 shows the structure of the encoder as given in CCITT rec. G.726.

#### Figure 9 Encoder Block Diagram

Figure **10** illustrates the structure of the decoder.

# **Functional Description**

# 2.2 PCM Interface

The Quad ADPCM allows most flexible use of the PCM interface. It can select the time slots of the four uncompressed data streams as well as the beginning of the compressed data stream via register programming. There is a data-in line for the uncompressed data (pin DINU) and a data-in line for the compressed data (pin DINC) as well as two data-out lines for uncompressed data and compressed data respectively (pins DOU and DOC). If the time slots of both data streams do not overlap, both outputs and both inputs can be electrically connected.

Four time slots can be assigned to the four uncompressed data streams. They select the input as well as the output of the uncompressed data. The uncompressed channel assignments are controlled by the UTi registers (i being the channel number 0..3). In case of single clock mode the bit MSB:UTMi is used to extend the programming range to a maximum of 64 time slots.

The compressed data can start at any bit. The four compressed data streams are tied together. The compressed data of channel 0 comes first, then the compressed data of channel 1 etc. In the DPP register, the number *n* of the first compressed data bit is selected. Depending on the compression rate, two, three, four or five compressed bits will be placed at the bit positions n, n+1, n+2 etc. The first compressed bit of the second channel directly follows the last bit of the first channel. The first bit of the third channel directly follows the last bit of the second channel etc. If the compression rate is changed the bit positions of the higher channels change as well. In case of bitwise bypassing or a combination of compression and bypassing the same principle applies.

Figure **11** illustrates the relation of the frame sync signal at the FSC pin, the numbering of the bits in the frame and the beginning of the slots. Double data clock mode is

assumed. The user has to take care not to 'overlap' data by multiple allocation of channels to same timeslots.

The rising edge of the FSC marks the start of the 125  $\mu$ s frame. Each slot consists of 8 bits. The beginning of the compressed data can be set to every bit of the frame as given in figure **11**. The compressed channel assignment is programmed via the register DPP. In case of single clock mode at 4.096 MHz only the first 256 bits may be selected as start position. Care has to be taken by proper programming of the DPP and UTi registers not to overlap data if the two PCM interfaces shall work on one PCM highway.

Input data and output data is always allocated to the same time slots.

Start and execution time of the DSP programs are such that coding and decoding are performed in one single frame if the slot assignment is properly chosen. That is, for the default time slot assignment as given in figure **4** as well as for the PCM-8 system shown in figure **7**, the propagation delay through two ADPCM channels in a system (coding on one side, decoding on the other side) is one single frame.

# 2.3 **Propagation Delay**

The begin of the decoder and the encoder program is tied to the frame clock at FSC. It is optimized to provide a one frame group delay for the complete encoding/decoding operation on all four channels if the time slots of uncompressed data and compressed data are assigned properly.

Figure **12** gives the location of the decoder start time and the encoder start time in the frame. If the uncompressed input data is read in the time slots before the encoder starts, it is available to the compressed output immediately after the encoder stops. If the compressed input data is read before the decoder starts, the uncompressed data is available to the uncompressed output immediately after the decoder stops. In the example of figure **12**, the uncompressed data is read at the time slots 4, 5, 8 and 9 before the encoder starts. It is compressed during time slot 11 and put to the DOC pin in time slots 0 and 1 of the next frame.

The compressed data is read at time slots 0 and 1 before the decoder starts. It is decoded during time slots 2 and 3 and put to the DOU pin during time slots 4, 5, 8 and 9 in the same frame it has been read. Note that the decoding takes longer than the encoding.

Hence, with the default time slot assignment as described in section**1.6.1**, the delay to compress data is one frame and the uncompressed data is available in the same frame.

Figure 12 Decoder / Encoder Timing in a PCM-4 System

If two Quad ADPCM devices are put together in a PCM-8 system and the DCL clock is 1.536 MHz, there are not enough time slots for the uncompressed data left before the start of the encoder. Therefore, the encoder start position can be shifted to the begin of the frame by setting the ADF2:ENS bit to '1'. If this is done in one of the two Quad ADPCM, the timing as given in figure **13** results.

Figure 13 Decoder / Encoder Timing in a PCM-8 System

The uncompressed data of slots 4 to 7 is processed during time slot 11 in the encoder of device 1 and passed to DOC at slot 0 of the next frame. The uncompressed data of slots 8 to 11 is processed during slot 0 of the next frame and put to DOC at slot 1. Again, all channels have a one frame delay for the complete encoding/decoding operation.

If the time slots are not assigned as proposed above, the delay of one or more channels may be two frames.

If the DCL clock rate is higher than 1.536 MHz more than 12 time slots are available. In this case, there are several ways to assign the time slots appropriately for minimum delay. Note however that the encoding time then is longer than one time slot and the decoding takes more than two time slots.

The exact start and end of the decoder and the encoder at the different DCL clock rates is given in the tables below:

#### Decoder start after slot number

|             | ADF2:DCLK = 0 | ADF2:DCLK = 1 |

|-------------|---------------|---------------|

| ADF2:ENS= 0 | 1             | 3             |

| ADF2:ENS= 1 | 2             | 5             |

#### Decoder end after slot number

| DCL = 1536 kHz | ADF2:DCLK = 0 | ADF2:DCLK = 1 |

|----------------|---------------|---------------|

| ADF2:ENS= 0    | 3             | 7             |

| ADF2:ENS= 1    | 4             | 9             |

| DCL = 2048 kHz | ADF2:DCLK = 0 | ADF2:DCLK = 1 |

|----------------|---------------|---------------|

| ADF2:ENS= 0    | 4             | 9             |

| ADF2:ENS= 1    | 5             | 11            |

| DCL = 4096 kHz | ADF2:DCLK = 0 | ADF2:DCLK = 1 |

|----------------|---------------|---------------|

| ADF2:ENS= 0    | 7             | 14            |

| ADF2:ENS= 1    | 8             | 16            |

#### Encoder start after slot number

| DCL = 1536 kHz | ADF2:DCLK = 0       | ADF2:DCLK = 1       |

|----------------|---------------------|---------------------|

| ADF2:ENS= 0    | 10                  | 21                  |

| ADF2:ENS= 1    | start of next frame | start of next frame |

| DCL = 2048 kHz | ADF2:DCLK = 0 | ADF2:DCLK = 1 |

|----------------|---------------|---------------|

| ADF2:ENS= 0    | 13            | 27            |

| ADF2:ENS= 1    | 14            | 29            |

| DCL = 4096 kHz | ADF2:DCLK = 0 | ADF2:DCLK = 1 |

|----------------|---------------|---------------|

| ADF2:ENS= 0    | 25            | 51            |

| ADF2:ENS= 1    | 26            | 53            |

Encoder end after slot number

| ADF2:DCLK = 0       | ADF2:DCLK = 1                                                                                                            |

|---------------------|--------------------------------------------------------------------------------------------------------------------------|

| start of next frame | start of next frame                                                                                                      |

| 0 of next frame     | 1 of next frame                                                                                                          |

|                     |                                                                                                                          |

| ADF2:DCLK = 0       | ADF2:DCLK = 1                                                                                                            |

| start of next frame | 30                                                                                                                       |

| 0 of next frame     | 0 of next frame                                                                                                          |

|                     |                                                                                                                          |

| ADF2:DCLK = 0       | ADF2:DCLK = 1                                                                                                            |

| 28                  | 57                                                                                                                       |

| 29                  | 59                                                                                                                       |

|                     | start of next frame<br>0 of next frame<br>ADF2:DCLK = 0<br>start of next frame<br>0 of next frame<br>ADF2:DCLK = 0<br>28 |

Note: IF ADF2:ENS is set to '0', 16 bit are issued at DOC. If ADF2:ENS is set to '1', only 8 bit are issued at DOC.

# 2.4 Echosuppression and Speech Detection

The PEB 7274 Quad ADPCM has a very flexible echosuppressor integrated. In addition to the direction of the echosuppressor (attenuation on the compressed or uncompressed side) all parameters required to optimize the speech detection and signal suppression are also fully programmable. All parameters are part of the DSP RAM and need to be reprogrammed after every reset. No reset settings exist for DSP RAM parameters. Refer to the section **3.16.1** for the procedure of programming DSP RAM cells.

# 2.4.1 Echosuppression

To account for echos from the far end side with up to 70 ms delay an echosuppressor is implemented in the DSP algorithms of the PEB 7274. Echos mainly result when converting digital speech/data information (e.g. from U interface,  $S_0$  interface or DECT interface) into analog tip/ring signals. Depending on the origin of the echo the delay of the echo varies. Figure **14** shows typical sources of echos in a DECT PBX system connected to the public exchange with analog and digital trunk lines.

# Figure 14 Echo Sources in a DECT PBX System

Far end echos are unpredictable with respect to duration and delaytime because these parameters change with each communication connection established. Unlike near end echos where these parameters can only vary within a limited bandwidth far end echos can not be cancelled. The suppression implemented instead consists of a gain stage which adds an additional attenuation to the receive path (typically 9 dB) while speech is recognized in the transmit path and the receive power level does not exceed a specified limit. The receive power level limit guarantees that despite of echosuppression the participant on the other side of the line can switch echosuppression off by speaking loud.

The signal flow path with all programmable echosuppression parameters is illustrated in figure **15**. The programming parameters of the echosuppression are described in section **3.16.6**.

Figure 15 Echosuppressor Functionality

The echosuppressor is switched off with time constant  $t_r$  without any delay when the estimated receive power level is above the value programmed in ES\_RxPL during the time constant  $t_{PLdly}$ .

As figures **16** and **17** show the PEB 7274 allows also to select the direction of suppression. In DECT systems typically the suppression would be performed on the compressed side (figure **16**). This ensures that local echos which would be noticed by the speaker on side A (handy) due to the 2 x 10 ms delay are attenuated.

# **Functional Description**

Figure 16 Echosuppression on the Compressed Side (DECT System)

In non-DECT systems like PCM-4 applications (i.e. without delay in the order of milliseconds) the far end echo from side B must be attenuated. For this reason the uncompressed PEB 7274 output of side A ( = receive signal containing far end echo) will be suppressed as soon as speech is detected in the transmit path (= uncompressed input of PEB 7274). This guarantees improved speech quality for side A. Refer to figure **17** for details.

### **Echosuppressor Related Parameters**

All parameters used in conjunction with the echsuppressor are located in the DSP RAM. A summery is given in the table below. For a detailed description please refer to section **3.16.6**.

| Parameter | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ES_ATT    | Echosuppressor Attenuation<br>Determines the level of attenuation in the receive path if speech<br>is detected in the transmit path and the estimation of receive<br>power is below the specified limit.                                                                                                                                                                                                                                         |

| ES_DLY    | Echosuppressor Delay<br>Specifies the delay time t <sub>dly</sub> between the disappearance of<br>speech (speechdetector: no speech) and the start of the rise time<br>of the echosuppressor.                                                                                                                                                                                                                                                    |

| ES_RISE   | Echosuppressor Rise Time Specifies the time $t_r$ in which the attenuation is increased from the programmed value to 0 dB.                                                                                                                                                                                                                                                                                                                       |

| ES_FALL   | Echosuppressor Fall Time<br>Specifies the time t <sub>f</sub> in which the attenuation is decreased from<br>0 dB to the programmed value if speech is detected in the<br>transmit path.                                                                                                                                                                                                                                                          |

| ES_PLdly  | Echosuppressor Receive Power Level Delay<br>This coefficient is the time constant t <sub>PLdly</sub> for the power estimator<br>of the receive signal.                                                                                                                                                                                                                                                                                           |

| ES_RxPL   | Echosuppressor Receive Power Level<br>This parameter specifies the power level threshold for receive<br>direction. If the signal in the receive path exceeds the<br>programmed value the attenuation added by the echsuppressor<br>will be switched off after t <sub>PLdly</sub> has elapsed. This guarantees that<br>despite of echosuppression the subscriber on the other end of<br>the line can switch echosuppression off by speaking loud. |

### 2.4.2 Speech Detector

Basically the speech detector makes use of the burst characteristic of speech. That means, every fast change in signal amplitude compared to the average signal level is recognized as speech. This is done by averaging the input signal with a lowpass filter (noise monitor lowpass) and comparing the output of this lowpass with the input signal itself.

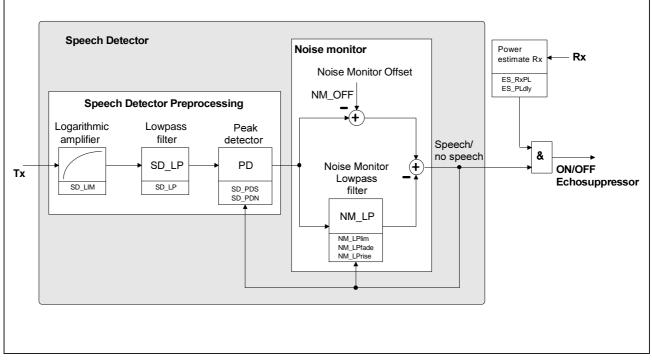

As shown in figure **18** the speech detector mechanism is composed of three seperate blocks:

- Power estimator in the receive path

- Speech detection preprocessing in the transmit path

- Noise monitor in the transmit path

#### Figure 18 Speech Detector Mechanism

The speech detection is performed by components which offer programmable parameters. These components are the logarithmic amplifier, the speech detection lowpass filter, the peak detector and the noise monitor.

They have the following functions:

- Logarithmic Amplifier Compression of the signal area of the incoming transmit signal.

- Speech Detection Lowpass Filter Spike reduction of the incoming signal.

Peak Detector

Improvement of speech detection by offering different time constants for detected and non-detected speech.

Noise Monitor

Discriminates between speech and noise. The noise monitor comprises a lowpass filter and an programmable offset. For a detailed description refer to section **2.4.2.1**.

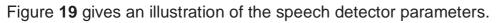

Figure 19 Speech Detector Parameters

# 2.4.2.1 Noise Monitor

The tasks of the noise monitor are to differentiate voice signals from background noise, even if it exceeds the voice level, and to recognize voice signals without any delay. Therefore the Noise Monitor consists of the Noise Monitor Lowpass Filter (NM\_LP) and the Noise Monitor Offset (NM\_OFF) in two separate branches. Basically it works on the burst-characteristic of the speech: voice signals consist of short peaks with high power (bursts). In contrast, background noise can be regarded approximately stationary from its average power.

The noise monitor is able to discriminate between speech and noise. It consists of the noise monitor lowpass filter NM\_LP and the offset NM\_OFF. Basically it works on the burst-characteristic of the speech: Voice signals consist of short peaks with high power (bursts). Background noise can be regarded approximately stationary from its averaged power. The task of the noise monitor is to recognize voice signals without any delay and to recognize background noise. Since only a difference between the average signal level and the instant signal leads to speech recognition, the influence of noise on the decision is cancelled, even if the noise level exceeds the voice level. See figure **19** for illustration of the programmable parameters of the Noise Monitor.

# Noise Monitor Lowpass Filter

The noise monitor lowpass filter NM\_LP provides different time constants for noise (nondetected speech) and speech. It determines the average of the noise reference level. In case of background noise the level at the output of the lowpass filter is approximately the level of the input. Due to the offset NM\_OFF the comparator remains in the initial state. In case of speech the difference of the signal level between the offset branch and the lowpass branch at the comparator increases and the comparator output changes its state. At speech bursts the digital signals arriving at the comparator via the offset branch change faster than those via the lowpass branch so that the comparator output changes polarity.

Hence two logical levels are generated

- one for speech and

- one for noise.

A small fade constant NM\_LPfade enables a fast discharging of the lowpass after the end of the speech recognition. It is recommended to choose a large rising constant NM\_LPrise so that speech itself charges the lowpass very slowly.

Generally it is not recommended to program an infinite rise time NM\_LPrise because in that case noise approximation is disabled. The maximum value for the lowpass is limited to the programmable value NM\_LPlim to detect continuous tones as speech and activate the echosuppressor.

#### Offset

The offset stage NM\_OFF represents a level threshold between signal and averaged noise. By this parameter a reference level is programmed to a percentage of full speech signal.

#### **Noise Monitor Related Parameters**

All parameters used in conjunction with the noise monitor are located in the DSP RAM. A summery is given in the table below. For a detailed description please refer to section **3.16.5**.

| Parameter | Description                                                                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NM_LPlim  | Noise Monitor Lowpass Limit<br>This value limits the charging off the lowpass filter. A continous<br>input signal, that has to be detected as speech, has to be above<br>this limit. |

| NM_LPfade | Noise Monitor Lowpass Fade Constant<br>Enables the fast discharge of the noise monitor lowpass after the<br>end of speech recognition.                                               |

| NM_LPrise | Noise Monitor Lowpass Rise Time<br>Determines the time the noise monitor lowpass is charged after<br>speech is recognized.                                                           |

| NM_OFF    | Noise Monitor Offset<br>Specifies a level threshold between signal and noise. Speech<br>bursts mus be NM_OFF dB above the average signal to be<br>recognized.                        |

#### 2.4.2.2 Speech Detection Preprocessing

As described in the preceding chapter, the Noise Monitor is able to discriminate between speech and noise. In very short speech pauses e.g. between two words, however, it changes immediately to non-speech, which is equal to noise. Therefore a peak detection is required in front of the Noise Monitor.

#### **Peak detector**

The peak detector bridges the very short speech pauses during a monologue so that the respective time constant has to be long. Furthermore, the speech bursts are stored so that a sure speech detection is guaranteed. But if no speech is recognized the noise monitor lowpass must be charged very fast to the averaged noise level. Additionally the noise edges are to be smoothed. Therefore two time constants are necessary and have to be programmed separately: SD\_PDS for speech and SD\_PDN for noise (background) signals. Hence 'speech mode' may be detected faster and kept longer than 'no speech mode' so that smaller breaks may not cause switching. Also noise is smoothened.

### Speech Detection Lowpass Filter

The peak detector is very sensitive to spikes. The lowpass SD\_LP filters the receive signal containing noise in a way that main spikes are eliminated. Due to the programmable time constant SD\_LP it is possible to defuse high-energy sibilants and noise edges.

# Logarithmic Amplifier

To compress the speech signals in their amplitudes and to ease the detection of speech, the signals have to be companded logarithmically. Hereby, the speech detector should not be influenced by the system noise which is always present but should discriminate between speech and background noise. The limitation of the logarithmic amplifier can be programmed via the parameter SD\_LIM. SD\_LIM is related to the maximum PCM level. A signal exceeding the limitation defined by SD\_LIM is getting amplified logarithmically, while very smooth system noise below is neglected. It should be the level of the minimum system noise which is always existing.

# **Principle of Speech Detection**

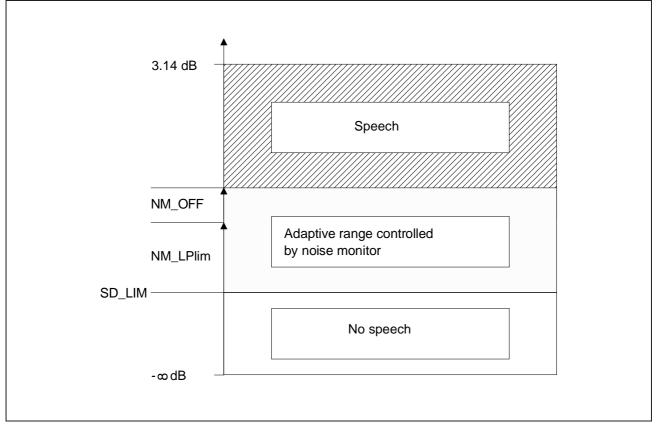

The diagrams in figure **20** graphically describe the inputs and outputs of the speech detector blocks. The result is not completely identical to the implementation in the Quad ADPCM echosupressor but helps to understand the function of the speech detector.

Figure 20 Speech Detection Principle

The first diagram shows the analog representation of the input signal, since this signal form is more convenient for the readers understanding of the signal processing. In the ADPCM circuits the signal is delivered to the speech detector digitally. The peak detector output is the envelope of the input signal, where short pauses are bridged. The next diagram explains the function of the noise monitor with the two branches (noise monitor offset input and noise monitor lowpass filter). In the lower diagram the result of the signal processing in the speech detector is shown.

# **Speech Detector Related Parameters**

All parameters used in conjunction with the speech detection are located in the DSP RAM. A summery is given in the table below. For a detailed description please refer to section **3.16.5**.

| Parameter | Description                                                                                                                                                                                                                        |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD_LIM    | Speech Detection Limit<br>Input signals below the level determined by SD_LIM are not<br>processed by the speech detector. Usually SD_LIM is<br>programmed for a threshold that is a few dB above the noise floor<br>of the system. |

| SD_LP     | Speech Detection Lowpass<br>This time constant determines how the main spikes are being<br>eliminated. Note that if SD_LP is large the response time of the<br>speechdetector is long.                                             |

| SD_PDS    | Speech Detection Peak Detector 'Speech'<br>This coefficient specifies the time constant for speech signals. A<br>large value should be programmed to avoid quick charging<br>during speech.                                        |

| SP_PDN    | Speech Detection Peak Detector 'Noise'<br>This coefficient specifies the time constant for noise signals.<br>Small time constants allow quick adaptation to changes of the<br>noise level.                                         |

#### 2.5 Fax/Modem Detection

A fax/modem tone detection is implemented in each channel of the Quad ADPCM. Typically a 2.1 kHz tone is used to indicate the remote side that a fax or modem is requesting a connection. To guarantee a reliable detection of this tone fully programmable parameters are provided. These parameters allow an adjustment to individual requirements. As soon as a tone which fullfills all programmed conditions is detected, an interrupt will be generated (provided the interrupt generation was enabled with the FDE register). In the register FDS the source of the interrupt can be read. The Quad ADPCM indicates the successfull detection seperately for compressed and uncompressed side with a '1'.

Reading the FDS register will automatically reset the interrupt line ( $\overline{INT}$  = high). Every transition of bits in the FDS register generates an interrupt. A '1' to '0' transition will however occure only after the device detected that no information is sent any more (power monitoring). The stopping of the 2.1 kHz tone will not cause a '1' to '0' transition. Optionally each channel bit in the FDS register may individually be reset to '0'. This reset is performed by programming the corresponding FDE:EMi bit to '0' (resets the two FDS detection bits of channel i for of uncompressed and compressed side to '0'). After reprogramming the FDE:EMi bit to '1' the next interrupt will be generated as soon as the fax/modem tone criterias are fullfilled again.

Note: No default DSP RAM values are available after a reset. All parameters need to be programmed after reset.

The operation of the fax/modem detection is illustrated in figure **21**. For reliable tone detection a combination of frequency criteria and time criteria must be met.

# **Functional Description**

#### Figure 21 Fax/Modem Tone Detection

The upper branches of the Rx- and Tx-path contain the bandpass filter and can detect modem tones. The lower branches contain the notch filter to filter out the modem signal so that the output signals of these branches represent the power in the remaining band.

For speech signals the output signal of the lower branch will be large compared to the output of the upper path and vice versa for modem signals.

The center frequency and bandwidth of the modem filters can be programmed using parameters MD\_FREQ and MD\_BW (bandpass and notch filter). The filter outputs are averaged using a lowpass filter with parameter MD\_LP so that the power estimate of the signals are obtained.

A minimum modem level of -40 dB which has to be detected is specified by CCITT standard G.164. A respective limit value can be programmed using parameter MD\_LIM.

The difference value MD\_DIFF is implemented for modem signal detection in the transmit path. If the difference of the signal energy in the modem frequency band and out of the modem frequency band is larger than MD\_DIFF a modem signal can be detected.

For large values of MD\_DIFF erraneous fax/modem detection for speech input signals is avoided. On the other hand modem signals with small frequency deviations or additional noise are not detected anymore. Smaller values of MD\_DIFF allow fax/modem detection in a noisy environment. Protection against erraneous fax/modem detection for speech input signals is however reduced.

The timer (MD\_Thold)has been implemented to eliminate the influence of transients. Adjustment should be such that modem tones of minimum duration 500 ms duration can be detected as required by CCITT specification G.164.

#### **Fax/Modem Detection Related Parameters**

All parameters used in conjunction with the fax/modem detection are located in the DSP RAM. A summery is given in the table below. For a detailed description please refer to section **3.16.7**.

| Parameter | Description                                                                                                                                                                                                                                                                                                          |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MD_FREQ   | Fax/Modem Detection Center Frequency<br>Should be adjusted to the frequency of the modem signal to be<br>detected (2.1 kHz tones).                                                                                                                                                                                   |  |  |  |

| MD_BW     | Fax/Modem Detection Bandwidth<br>Determines the bandwidth of the modem filter.                                                                                                                                                                                                                                       |  |  |  |

| MD_LP     | Fax/Modem Detection Lowpass<br>Specifies the time constant for the power estimator.                                                                                                                                                                                                                                  |  |  |  |

| MD_Tbreak | Fax/Modem Detection Break Time<br>Tone breaks of less than the specified time are ignored.                                                                                                                                                                                                                           |  |  |  |

| MD_Thold  | Fax/Modem Detection Hold Time<br>Specifies the time the detection conditions have to be valid for<br>fax/modem detection.                                                                                                                                                                                            |  |  |  |

| MD_DIFF   | Fax/Modem Detection Difference<br>This parameter specifies the difference the outputs of the<br>bandpass and the notch filter have to exceed. If the difference of<br>the signal energy in the modem frequency band and out of the<br>modem frequency band is larger than MD_DIFF a modem signal<br>can be detected. |  |  |  |

| MD_LEV    | Fax/Modem Detection Level<br>Determines the threshold below which noise or signals are<br>ignored.                                                                                                                                                                                                                   |  |  |  |

| MD_LIM    | Fax/Modem Detection Limit<br>The level programmed in MD_LIM is compared with the output of<br>the modem filter. If the level of the modem signal is above<br>MD_LIM modem detection can be activated.                                                                                                                |  |  |  |

| MD_LEVE | The parameter specifies the level for the end of the fax/modem detection.             |

|---------|---------------------------------------------------------------------------------------|

| MD_TIME | The parameter specifies the timing conditions for the end of the fax/modem detection. |

#### 2.6 Artificial Echo Loss

An Artificial Echo Loss (AEL) can be added to the receive path. The AEL gain can be programmed from -45 dB to 0 dB. The direction of the AEL is opposite to the direction of the echo suppression as set in the ESE register. The AEL can be enabled for each channel independently by setting the ADF register bits EA3 ... EA0 to '1'.

#### **Artificial Echo Loss Related Parameters**

The parameter used in conjunction with the AEL is located in the DSP RAM. A summery is given in the table below. For a detailed description please refer to section **3.16.4**

| Parameter | Description                                                |  |  |  |

|-----------|------------------------------------------------------------|--|--|--|

| AEL_GAIN  | Artificial Echo Loss Gain                                  |  |  |  |

|           | Determines the level of the AEL added to the receive path. |  |  |  |

#### 2.7 Congestion Tone Generator

A programmable tone with an amplitude between -45 dBm and 0 dBm and a frequency between 0 Hz and 1 kHz can be put to the uncompressed data output instead of the PCM data. The ADPCM data is not evaluated if the congestion tone generator is enabled.

The tone can be used to create a 'line occupied' signal already in the terminal side of a wireless local loop system in the case the air interface is occupied. The tone can be enabled for each channel independently by setting the ADF register bits EC3 ... EC0 to '1'. It's modulation is done by enabling and disabling it at the appropriate rate. DSP 2 has to be enabled for the tone generation.

#### **Congestion Tone Generator Related Parameters**

All parameters used in conjunction with the congestion tone generator are located in the DSP RAM. A summery is given in the table below. For a detailed description please refer to section **3.16.2**.

| Parameter | Description                                 |  |  |  |  |

|-----------|---------------------------------------------|--|--|--|--|

| CT_FREQ   | Congestion Tone Frequency                   |  |  |  |  |

| CT_LEV    | Determines the level of the Congestion Tone |  |  |  |  |

| CT_GAIN   | Specifies the frequency gain                |  |  |  |  |

#### 2.8 Frame Strobe Outputs

The application in pair gain systems together with standard codec filters is supported with one Frame Strobe output per channel at the pins FSi (i = 0 to 3 being the channel number).

There are two different timings available, referred to as short frame and long frame, respectively. The selection is done with the FST bit in the configuration register CR. CR:FST set to '1' selects short frame timing. CR:FST set to '0' selects long frame timing.

If CR:FSEN is set to '0', all four FSi outputs are tied to  $V_{SS}$ . Figures **22** and **23** give the timings for short framing. Figure **24** and **25** illustrate the long frame timings.

In short frame timings the first bit starts with the falling edge of FSi. The frame strobe signal is high during one DCL period in single clock mode (ADF2:DCLK = '1') as well as in double clock mode (ADF2:DCLK = '0').

Figure 22 Frame Strobe Output: Short Frame Timing, Single Clock Mode

Figure 23 Frame Strobe Output: Short Frame Timing, Double Clock Mode

In double clock mode, the BCL signal can be used by the recieving device to determine when the PCM data is shifted in.

# SIEMENS

#### **Functional Description**

At long frame timing the time slots are nominally coincident with the rising edge of FSi. The frame strobe signal is high during all 8 (single clock mode), 16 (double clock mode) respectively, DCL periods marking one complete time slot.

Figure 24 Frame Strobe Output: Long Frame Timing, Single Clock Mode

Figure 25 Frame Strobe Output: Long Frame Timing, Double Clock Mode

In double clock mode, the BCL signal can be used by the recieving device to determine when the PCM data is shifted in.

# SIEMENS

#### **Functional Description**

#### 2.9 Serial Microcontroller Interface

The serial microcontroller interface consists of four lines:  $\overline{CS}$ , CCLK, CDIN and CDOUT.  $\overline{CS}$  is used to start a serial access to the registers. Following a falling edge of  $\overline{CS}$ , the first eight bits received on CDIN specify the command. The following data byte is stored in the selected register with the rising edge on  $\overline{CS}$ . The first received bit specifies a read (bit = '0') command or a write command (bit = '1'). The following five bits give the register address (MSB first).

Figure 26 Microcontroller Interface Timing: Write Access

Figure 27 Microcontroller Interface Timing: Read Access

In a read access an ID-Byte ( $CO_H$ ) is issued before the data byte as shown in figure **27**. The maximum data clock frequency to be applied at pin CCLK is 7.68 MHz. CCLK may pause between control and read/write byte(s). These breaks may be arbitrarly long or missing at all.

Data bits at CDIN are latched by the device with the rising edge of CCLK. The bits at CDOUT are put to the line with the falling edge of CCLK, they may therfore be latched by the  $\mu$ C with the rising edge.

Indirect Access to the DSP RAM is provided via the COM register, the DST register, the DATA registers and the ADR register. The DATA registers are used to either read data from or write data to the DSP RAM. The read access of the other registers is only used to control the register contents.

Data put into the registers at an arbitrary time is valid with the next rising edge of the frame clock at FSC. If the DSYNC pin is input, data is valid at the next rising edge of the frame at FSC after the next falling edge of the clock at DSYNC.

#### 2.10 Boundary Scan Test Controller

The Quad ADPCM provides a boundary scan support for a cost effective board testing. It consists of:

- -Complete boundary scan for 22 signals (pins) according to IEEE Std. 1149.1 specification

- -Test access port controller (TAP)

- –Four dedicated pins (TCK, TMS, TDI, TDO)

- -One 32-bit IDCODE register

All pins except the power supply pins, the 'not connected' pin and pins BCL, MCL, TDI, TDO, TCK, TMS, XTAL1 and XTAL2 are included in the boundary scan.

When the TAP controller is in the appropriate mode data is shifted into or out of the boundary scan via the pins TDI/TDO using clock at pin TCK. The clock rate at pin TCK may be up to 10 MHz.

Depending on the pin functionality one, two or three boundary scan cells are provided.

Note: There are several pins, which for chip test are used as I/O pins. Please refer to section 1.4 whether these pins are inputs or outputs. However, they are included to the boundary scan as I/O pins with three scan cells.

| Pin Type | Number of Boundary Scan<br>Cells | Usage                 |

|----------|----------------------------------|-----------------------|

| Input    | 1                                | input                 |

| Output   | 2                                | output, enable        |

| I/O      | 3                                | input, output, enable |

| Boundary Scan<br>Number<br>TDI —> | Pin Number | Pin Name | Туре | Number of<br>Scan Cells |

|-----------------------------------|------------|----------|------|-------------------------|

| 1                                 | 37         | DSYNC    | I/O  | 3                       |

| 2                                 | 38         | FS2      | 0    | 2                       |

| 3                                 | 39         | FS1      | 0    | 2                       |

| 4                                 | 40         | FSC      | I    | 1                       |

| 5                                 | 41         | DCL      | I    | 1                       |

| 6                                 | 42         | DINU     | I    | 1                       |

| 7                                 | 43         | FS0      | 0    | 2                       |

| 8                                 | 44         | FS3      | 0    | 2                       |

| 9                                 | 1          | ALAW     | I    | 1                       |

| 10                                | 2          | INT      | 0    | 2                       |

| 11                                | 3          | CDOUT    | 0    | 2                       |

| 12                                | 4          | CDIN     | I    | 1                       |

| 13                                | 5          | CS       | I    | 1                       |

| 14                                | 8          | CCLK     | I    | 1                       |

| 15                                | 9          | DOU      | 0    | 2                       |

| 16                                | 10         | DOC      | 0    | 2                       |

| 17                                | 11         | DINC     | I    | 1                       |

| 18                                | 12         | PD2      | I    | 1                       |

| 19                                | 13         | PD1      | I    | 1                       |

| 20                                | 14         | TCC      | 0    | 2                       |

| 21                                | 15         | TCU      | 0    | 2                       |

| 22                                | 16         | RES      | I    | 1                       |

The pins are included in the following sequence in the boundary scan:

#### 2.10.1 TAP Controller

The *Test Access Port* (TAP) controller implements the state machine defined in the JTAG standard IEEE Std. 1149.1. Transitions on the pin TMS cause the TAP controller to perform a state change.

Following the standard definition 7 instructions are executable.

#### TAP controller instructions:

| Code | Instruction               | Function                                 |  |  |

|------|---------------------------|------------------------------------------|--|--|

| 000  | EXTEST                    | External testing                         |  |  |

| 001  | 1 INTEST Internal testing |                                          |  |  |

| 010  | SAMPLE/PRELOAD            | Snap-shot testing                        |  |  |

| 011  | IDCODE                    | Reading ID code                          |  |  |

| 100  | CLAMP                     | Reading outputs                          |  |  |

| 101  | HIGHZQ                    | Z-State of all boundary scan output pins |  |  |

| 11X  | BYPASS                    | Bypass operation                         |  |  |

**EXTEST** is used to examine the board interconnections.

When the TAP controller is in the state "update DR", all output pins are updated with the falling edge of TCK. When it has entered state "capture DR" the levels of all input pins are latched with the rising edge of TCK. The in/out shifting of the scan vectors is typically done using the instruction SAMPLE/PRELOAD.

**INTEST** supports internal chip testing.

When the TAP controller is in the state "update DR", all inputs are updated internally with the falling edge of TCK. When it has entered state "capture DR" the levels of all outputs are latched with the rising edge of TCK. The in/out shifting of the scan vectors is typically done using the instruction SAMPLE/PRELOAD.

Note: 001 (INTEST) is the default value of the instruction register.

**SAMPLE/PRELOAD** provides a snap-shot of the pin level during normal operation or is used to preload (TDI) / shift out (TDO) the boundary scan with a test vector. Both activities are transparent to the system functionality.

**BYPASS**, a bit entering TDI is shifted to TDO after one TCK clock cycle, e.g. to skip testing of selected ICs on a printed circuit board.

**HIGHZQ** sets all pins included to the boundary scan path into a high impedance state. In this state, an in-circuit test system may drive signals onto these pins.

**CLAMP** allows the state of the signals included in the boundary scan driven from the Quad ADPCM to be determined from the boundary scan register while the bypass register is selected as the serial path between TDI and TDO. These signals will not change while CLAMP is selected.

**IDCODE** serially reads out the 32-bit identification register via TDO. It contains the version number (4 bits), the device code (16 bits) and the manufacturer code (11 bits). The LSB is fixed to "1".

| Version | n Device Code Manufacturer Code |               |   | Output   |

|---------|---------------------------------|---------------|---|----------|

| 0001    | 0000 0000 0011 0011             | 0000 1000 001 | 1 | ><br>TDO |

Note: In the state 'test logic reset' the code '011' is loaded into the instruction code register.

#### 3 Register and DSP RAM Location Description

Operational modes are set per register programming. The default state of all registers after reset is such that operation in a PCM-4 system is possible without access of the microcontroller to the Quad ADPCM. A-law or  $\mu$ -law operation can then be set by pin strapping.

All registers except the FDS and the DST register are of read / write type. These can be used to control the register contents and to read DSP RAM data of the DATAL and DATAH registers. The address map and a register summary are given in the following table. Registers with addresses  $12_{\rm H}$  to  $1F_{\rm H}$  are not accessible to the user. They are used for test purposes only.

Note: Defaults of registers with two default values given depend on the setting of the ALAW pin.

ALAW pin low: left reset value is valid. ALAW pin high: right rest value is valid.

# SIEMENS

#### **Register and DSP RAM Location Description**

### Table 1Register Summary

| Addres<br>s (hex) | Register<br>Name | Reset<br>value<br>(hex) | Description                                      | Refer<br>to page |

|-------------------|------------------|-------------------------|--------------------------------------------------|------------------|

| 00                | UT0              | 26 or 27                | Uncompressed Timeslot of channel 0 <sup>1)</sup> | 50               |

| 01                | UT1              | 2E or 2F                | Uncompressed Timeslot of channel 1 <sup>1)</sup> | 50               |

| 02                | UT2              | 46 or 47                | Uncompressed Timeslot of channel 2 <sup>1)</sup> | 50               |

| 03                | UT3              | 4E or 4F                | Uncompressed Timeslot of channel 3 <sup>1)</sup> | 50               |

| 04                | MSB              | 00                      | MSB of PCM time slots <sup>1)</sup>              | 53               |

| 05                | CRR              | 00                      | Compression Rate Register <sup>1)</sup>          | 49               |

| 06                | DPP              | 00                      | Decoding PCM Position <sup>1)</sup>              | 52               |

| 07                | ADF              | 00                      | Additional Features Register                     | 54               |

| 08                | ADF2             | 00                      | Additional Features Register 2 <sup>2)</sup>     | 54               |

| 09                | CR               | 00                      | Configuration Register <sup>2)</sup>             | 48               |

| 0A                | ESE              | 00                      | Echosuppressor enable                            | 53               |

| 0B                | FDE              | FF                      | FAX Detection Enable Register                    | 55               |

| 0C                | FDS              | 00                      | FAX Detection Status Register <sup>3)</sup>      | 56               |

| 0D                | DST              | 00                      | DSP Status Register <sup>3)</sup>                | 56               |