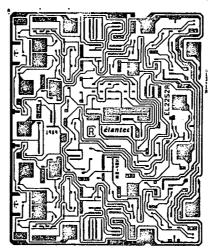

## EL2252D Die

Dual 50 MHz Comparator/Pin Receiver

T-45-17

## Absolute Maximum Ratings (TA = 25°C)

Voltage between V+ and V 36V

Voltage at V+

18V

Voltage between ~IN and +IN Pins

36V

Output Current

12 mA

Current into +IN, ~IN, HYS, or /TTL

5 mA

Maximum Junction Temperature

175°C

## Important Note:

$T_J$

For AC electrical characteristics, refer to the typical electrical table and performance curves in the package data sheet. These characteristics are guaranteed but not tested in die form. Unless otherwise noted, all tests are pulsed tests, therefore  $T_J = T_C = T_{AC}$

Test Level

Test Procedure

100% production tested in wafer form.

See remarks under Electrical Testing

in the General Die section.

DIE SIZE: 65 x 77 MILS

## DC Electrical Characteristics $v_S = \pm 15V$ ; HYS and i/m TTL grounded; $T_A = 25^{\circ}C$

| Parameter                              | Description                                                 | Min    | Тур   | Max | Test Level   | Units |

|----------------------------------------|-------------------------------------------------------------|--------|-------|-----|--------------|-------|

| vos                                    | Input Offset Voltage                                        |        | 1     | 6   | 1            | mV    |

| IB                                     | Input Bias Current V <sub>CM</sub> = 0V, pin 2 or 3         |        | 6     | 12  | 1            | μΑ    |

| Ios                                    | Input Offset Current V <sub>CM</sub> = 0V                   |        | 0.2   | 1   | 1            | μΑ    |

| CMRR                                   | Common-Mode Rejection Ratio (Note 1)                        | 70     | 95    |     | r Y          | dB    |

| PSRR                                   | Power Supply Rejection Ratio (Note 2)                       | 70     | 90    |     | 22 41        | dB    |

| V <sub>CM</sub> +<br>V <sub>CM</sub> - | Common Mode Input Range                                     | 10     | 13    |     | I V          | v     |

|                                        |                                                             | 9      | -12   |     | 18 7 T 18 18 | v     |

| A <sub>VOL</sub>                       | Large Signal Voltage Gain (V <sub>OUT</sub> = 0.8V + 0.20V) | 4,000  | 8,000 |     | 1            | V/V   |

| V <sub>OL</sub>                        | Output Voltage Logic Low I <sub>OL</sub> = 0 MA             | -0.2   | 0.2   | 0.4 | 1            | v     |

|                                        | $I_{OL} = 5 MA$                                             | -0.2 . | 0.4   | 0.8 | I            | v     |

| V <sub>OH</sub>                        | Output Voltage Logic High<br>CMOS Mode                      | 4      | 4.6   | 5.1 | ì            | v     |

|                                        | TTL Mode                                                    | 2.4    | 2.7   | 3.2 | 1            | v     |

| I <sub>S</sub> +                       | Positive Supply Current                                     |        | 16    | 19  | 1            | mA    |

| ı <sub>s</sub> -                       | Negative Supply Current                                     |        | 17    | 20  | r            | mA    |

Note 1: Two tests are performed with  $V_{CM} = 0V$  to -9V and  $V_{CM} = 0V$  to 10V.

Note 2: Two tests are performed with V+ = +15V, V- changed from -10V to -15V; V- = -15V, V+ changed from 10V to 15V.