# Class A Amplifier with 3 Independent Gain Blocks

LC508 DATA SHEET

#### **FEATURES**

- 1 μV input referred noise

- 1.0 to 5 VDC operating range

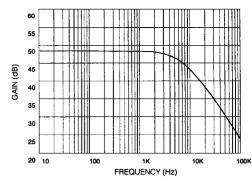

- 73 dB typical gain (adjustable)

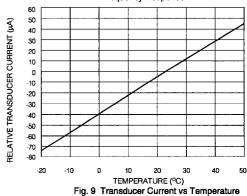

- 0.28 to 2.0 mA range of transducer current

- 1% electrical distortion

- the first and second blocks, or second and third blocks can be DC coupled

- 100 Hz to 50 kHz frequency response

- suitable for active filtering

#### STANDARD PACKAGING

- 10 PIN MICROpac

- 10 pin MINIpac

- •10 pin PLID®

- 10 pin SLT

- Chip (52 x 49 mils)

#### DESCRIPTION

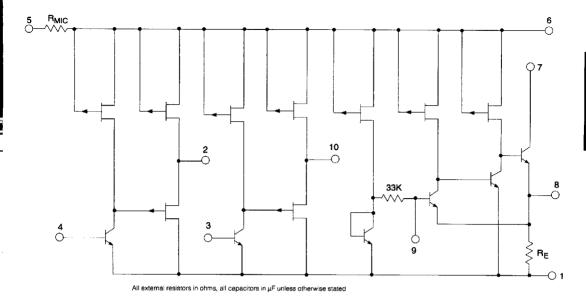

The LC508 is a 10 pin Class A amplifier utilizing Gennum's proprietary low voltage bipolar JFET technology. It consists of 3 single ended, low noise inverting gain blocks. The first two blocks have a typical open loop gain of 50 dB. The closed loop gain is set by the ratio of the feedback resistor to the source impedance. The third block is an open collector output stage with the bias being set by  $R_{\rm F}$  and  $V_{\rm BF}$  at pin 8 which is 54 mV.

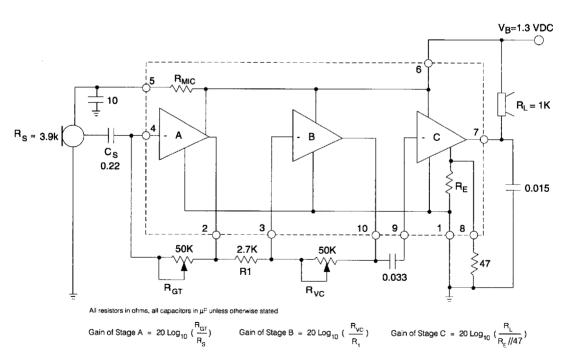

Typically, the gain of the first two blocks is set to 25 dB each, with the third block at 23 dB, giving a total gain of 73 dB.

Gain trim can be accomplished with the use of a feedback resistor on the first block, while the volume control is used as the feedback control on the second block. This gives a volume control range greater than 40 dB.

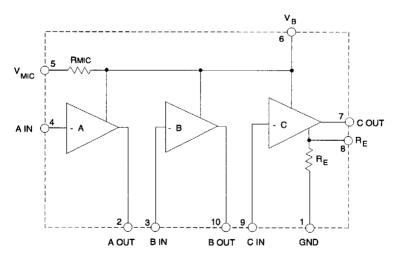

**BLOCK DIAGRAM**

Revision Date: January 1996

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | VALUE / UNITS  |  |  |

|-----------------------|----------------|--|--|

| Supply Voltage        | 5V DC          |  |  |

| Power Dissipation     | 25 mW          |  |  |

| Operating Temperature | -10° to + 40°C |  |  |

| Storage Temperature   | -20° to + 70°C |  |  |

|                       |                |  |  |

| CAUTION               |                |  |  |

#### V<sub>MIC</sub> C OUT AIN [ BIN [ A OUT CIN B OUT GND [

PIN CONNECTION

# **CLASS 1 ESD SENSITIVITY**

#### **ELECTRICAL CHARACTERISTICS**

Conditions: Supply Voltage =1.3 VDC, Frequency = 1 kHz, Temperature = 25 °C

| PARAMETER                         | SYMBOL               | CONDITIONS                   | MIN | TYP | MAX | UNITS |

|-----------------------------------|----------------------|------------------------------|-----|-----|-----|-------|

| Gain (Closed Loop)                | A <sub>CL</sub>      | V <sub>OUT</sub> = 500 VRMS  | 69  | 73  | 77  | dB    |

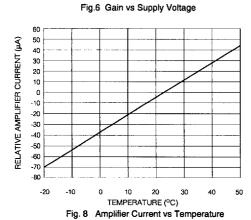

| Amplifier Current                 | I <sub>AMP</sub>     | $I_{AMP} = I_A + I_{MIC}$    | 160 | 245 | 340 | μΑ    |

| Transducer Current                | I <sub>TRANS H</sub> | R <sub>E</sub> = 47.5        | 1.1 | 1.3 | 1.7 | mA    |

| Transducer Current                | I <sub>TRANS L</sub> | R <sub>E</sub> = ∞           | 200 | 275 | 350 | μА    |

| Distortion                        | THD                  | V <sub>OUT</sub> = 500 VRMS  | -   | 1   | 4   | %     |

| Input Referred Noise              | IRN                  | NFB 0.2 to 10kHz at 12dB/Oct | -   | 1   | 2   | μV    |

| Stable with Battery Resistance to | R <sub>B</sub>       |                              | -   | -   | 22  | Ω     |

| Input Bias Current                | I <sub>B</sub>       |                              | -50 | 0   | 50  | nA    |

| On Chip Emitter Resistor          | R <sub>E</sub>       |                              | -   | 200 | -   | Ω     |

| Emitter Bias Voltage (pin 8)      | V <sub>RE</sub>      |                              | -   | 54  | -   | mV    |

| Microphone Decoupling Resistor    | R <sub>MIC</sub>     |                              | -   | 4   | -   | kΩ    |

All switches and parameters remain as shown in Test Circuit unless otherwise stated in Conditions column.

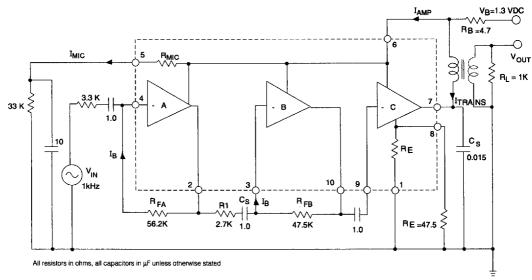

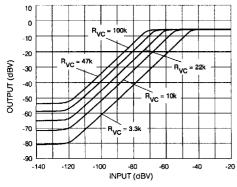

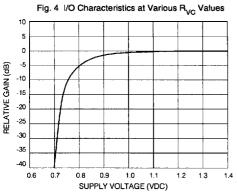

Fig. 1 Test Circuit

Fig. 2 Functional Schematic

Fig. 3 Typical Hearing Aid Application

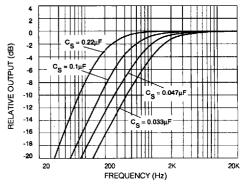

Fig. 5 Frequency Response at Various C<sub>S</sub> Values

Fig.7 Preamplifier A Open Loop Frequency Response

**REVISION NOTES**

Au bump removed.

Gennum Corporation assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement. © Copyright 1989 Gennum Corporation. All rights reserved. Printed in Canada.

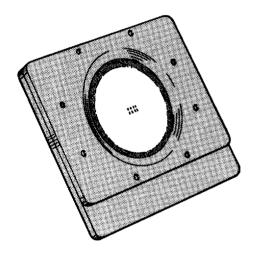

# **Assembly Methods for SLT** Packaged Integrated Circuits

# 8 & 10 PIN SLT APPLICATION NOTE

### STENCIL DESIGN

T-90-20

#### INTRODUCTION

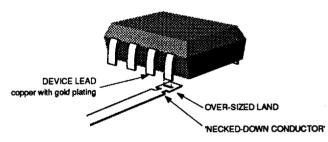

The SLT is a miniature fine pitch plastic encapsulation housing an integrated circuit. The packaging utilizes tape automated bonding (TAB) technology, and has leads folded on the side of the plastic capsule. The distance between the leads is 2.38mm (0.094") with overall height of 1.17mm (0.046") maximum. The outline dimensions of the packages are:

2.38 (0.094") x 2.40 (0.094") x 1.17 mm (0.046") 10 Pin 2.38 (0.094") x 2.91 (0.115") x 1.17 mm (0.046")

Why SLT? The name of this product is an acronym for Stub Lead Tab Pack. Gennum has developed the SLT brand packaging for its miniature integrated circuit audio amplifiers to satisfy two distinct market needs.

The first need is driven by market demands to supply circuits in smaller packages to meet dimensional requirements of an industry that is producing products of continually decreasing size and increasing complexity, utilizing smaller real estate than chip/wire.

The second need is to supply a miniature packaged circuit which can be tested prior to assembly into a hybrid circuit using alumina substrates, epoxy printed circuit boards or flex circuit boards and offers "reworkability", (i.e. aid's "manufacturability").

The purpose of what follows is to provide assistance to design and production personnel in the assembly of SLT packaged devices onto miniature printed circuit boards or ceramic substrates. The technical details encompassed in this note are based on Gennum's findings.

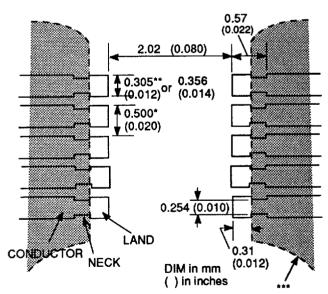

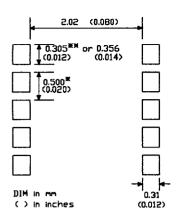

### SUGGESTED PAD GEOMETRY FOR SLT PACKAGED DEVICES

The lands to which SLT terminals are to be soldered should be located in accordance with the SLT terminal pattern shown in Figures 1 and 2 and should carefully be placed and sized. The dimensions of the lands and adjacent conductors must be properly determined so that the solder will not run onto the conductors and will hold the SLT devices firmly in place. The lands should ideally be 0.05 mm (0.002 inch) per side larger than the SLT lead width, causing a fillet to be formed at the contact edges. If any conductor is wider than 0.254 mm (0.010 inch), it should be necked to 0.254 mm (0.010"), as shown in Figure 2. The purpose of necking down the conductors is to prevent solder back flow (this rule is applicable when no solder resist is used). Although it is strongly recommended that solder resist be used where possible.

Note: It is very important to ensure that the coplanarity of the solder pads on the circuit board substrate be maintained to very tight tolerances.

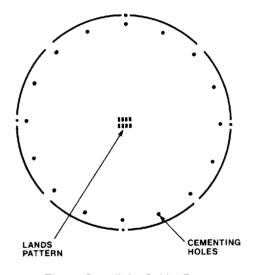

Because of the fine pitch of the SLT, it is recommended that metal stencil be used instead of screen stencil. The stencil or mask should be 0.1 mm (0.004") thick, with the pattern obtained by an etching process. It is important that the stencil be etched simultaneously from both sides to reduce undercutting of the pattern, and the amount of under cutting should be compensated for during the manufacture of the stencil.

A suggested solder mask pattern is shown in Figure 3. The solder paste should be applied to all the lands on the substrate in one stroke through the stencil as shown in Figure 5. The metal stencil is stretched tight and cemented to a fixture as shown in Figure 6.

The fixture is attached to a hinged platform, so that it can be raised to permit loading of the substrate onto a vacuum chuck located directly below. Exact positioning of the substrate on the vacuum pedestal can be best achieved by a series of locating pins. Vacuum hold-down is required to hold the substrate fixed when the stencil is raised for "snap-off" from the solder paste pattern.

Note: All other devices which are to be surface mounted, should have their solder paste screened on at the same time, (i.e. stencil should be designed as such).

For high volume production, the pattern can be step and repeated "N" number of times, to correspond with the "N" number of circuit board patterns being assembled. The accuracy and consistency of solder paste application in this instance should be taken into account in the stencil design.

# SCREEN PRINTING

To set up initially, the operator places the substrate on the vacuum chuck and lowers the stencil onto the substrate. Solder paste is applied using a teflon or polyurethane squeegee as shown in Fig. 7 (for high volume production, automated screen printers are usually available). This produces a uniform paste layer of a thickness equal to the metal stencil.

After the solder paste has been screened, the stencil must be raised vertically to provide a "snap-off". This motion is necessary to leave a well defined pattern on the substrate. Any horizontal movement will smear the pattern and increase the possibility of solder bridging of conductors on solder reflow.

The substrate is now ready for placement of surface mount components.

Document No. 520 - 10 - 1

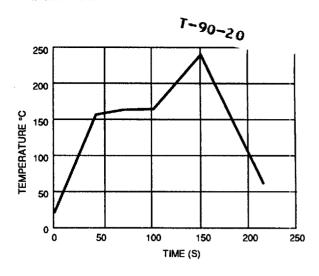

#### SOLDER REFLOW

The SLT can be easily soldered to the substrate using solder reflow techniques. Fig. 4 illustrates typically the solder temperature profile used to reflow SLTs.

For rigid substrates a 63 Sn/37 Pb solder cream (90% metal, -325 +500 mesh or type 3), containing the necessary flux is screened onto the land area. Kester Part #R-229-25 RMA or Alpha Part # RMA-390 DH3 performs well with no solder bridging evident. Excellent fillet formation at the land/device contact interface is apparent.

# RECOMMENDED STEPS IN ASSEMBLY

Note: No precleaning of SLT devices is required prior to use. STEP 1 SOLDER PASTE APPLICATION

Solder paste is screened onto the substrate using a squeegee as discussed under the heading "screen printing". Important variables:

- · age of solder paste

- time between solder paste application and reflow

- · accuracy and consistency in placing solder paste

## STEP 2 DEVICE PLACEMENT

The SLT is placed on the land area of the substrate with use of tweezers. A low power magnifier will assist the operator in easy, accurate location of the device over the circuit lands. It is best to bring the device above the application area, then descend vertically in one movement to avoid smearing the solder cream. It is important to precisely position the device over the contact lands.

For high volume production, the pick and place machine should have vision capability with two attributes:

- Board error correction and

- Component lead inspection (from under the device), or alternatively a dedicated pickup head with a recess shaped to the top section of SLT and vacuum for pickup can be used to center and square the device for placement.

The accurate placement of SLT devices is important in obtaining excellent soldering results, as the solder paste will not correct poor placement.

To prevent lead bending and maintain the pitch to pitch dimensions, the device should not be held or manipulated by the leads. Consistency and control of the placement force is also required.

#### STEP 3 SOLDER REFLOW

Heating the SLT and substrate for reflow soldering at 215°C (as measured at the lead/land interface) can be accompanied by any of the following techniques.

- A) Infra-red solder reflow oven.

- B) Vapor phase solder reflow.

Two versions are available:

B1 Batch type (immersion)

B2 Conveyor type

C) Conduction / convection - this method is not preferred as the process is difficult to control.

Since Gennum believes that these techniques are well known to users of our circuits, no discussion of them is included in this note.

#### STEP 4 CLEANING

Cleaning the completed hybrid circuit is the final step in this assembly process. Ultrasonic cleaning is preferred to remove the flux residue which could corrode the solder joint in time.

# STEP 5 INSPECTION/PROCESS MONITORING

The importance or process selection (for optimum yields) and control is very critical in the successful use of SLT devices. It is of utmost importance to ensure the any deviation from the "normally" expected soldering results, be analyzed and the cause be established, such that steps can be taken to bring the process back into control.

Fig. 1 Location of Conductor relative to Device Lead

- 4 spaces at 0.5 ±0.05 non-cumulative for 8 pin SLT 5 spaces at 0.5 +0.05 non-cumulative for 10 pin SLT

- \*\* Size should be established based on

- choice of interconnect medium

- assembly process capability

- \*\*\* Extent of solder resist, in which case "necking" will not be required. It is of utmost importance to have symmetrical pads only.

Fig. 2 SLT Solder Pad Pattern

- \* 4 spaces at 0.5 ±0.05 non-cumulative for 8 pin SLT 5 spaces at 0.5 ±0.05 non-cumulative for 10 pin SLT

- \*\* Choice of size should correspond with size selected in Fig. 2.

Fig. 3 Solder Mask Pattern for SLT

Fig. 5 Stencil for Solder Paste

Fig. 4 SLT Solder Reflow Temperature Profile

Fig. 6 Holding Plate for Stencil

Fig. 7 Screen Printing of Paste with Squeegee