# CoreUART v4.2 Handbook

#### **Actel Corporation, Mountain View, CA 94043**

© 2010 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 50200095-2 Release: October 2010

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### **Trademarks**

Actel, Actel Fusion, IGLOO, Libero, Pigeon Point, ProASIC, SmartFusion and the associated logos are trademarks or registered trademarks of Actel Corporation. All other trademarks and service marks are the property of their respective owners.

# **Table of Contents**

|   | Introduction General Description Core Versions Supported Families                                                                                         | 5<br>5                       |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 1 | Functional Block Description  Device Utilization and Performance  Programmable Options                                                                    | 8                            |

| 2 | Tool Flows Licensing SmartDesign Simulation Flows Synthesis in Libero IDE Place-and-Route in Libero IDE                                                   | . 11<br>. 11<br>. 12<br>. 13 |

| 3 | Core Interfaces                                                                                                                                           |                              |

| 4 | Timing Diagrams  Serial Transmit  Serial Receive  Parity Error  Overflow Error  Framing Error  Framing Error in Legacy Mode                               | . 17<br>. 18<br>. 18<br>. 19 |

| 5 | Ordering Information                                                                                                                                      |                              |

| Α | List of Document Changes                                                                                                                                  | 23                           |

| В | Product Support Customer Service Actel Customer Technical Support Center Actel Technical Support Website Contacting the Customer Technical Support Center | . 25<br>. 25<br>. 25<br>. 25 |

|   | Index                                                                                                                                                     | . 27                         |

## Introduction

## **General Description**

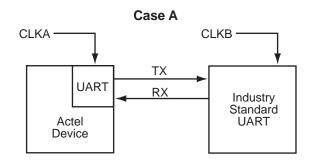

CoreUART is a serial communication controller with a flexible serial data interface that is intended primarily for embedded systems. CoreUART can be used to interface directly to industry standard UARTs. CoreUART is intentionally a subset of full UART capability to make the function cost-effective in a programmable device. Figure 1 illustrates the various usages of CoreUART.

Case A in Figure 1 represents the interface to an industry standard UART, such as an 8251 or a 16550. In Case B, CoreUART is transferring data from the 8051 to the system monitor through the RS-232 interface and vice versa.

Table 1 • System Block Diagram Depicting CoreUART Usage

## **Core Versions**

This handbook applies to CoreUART v4.2. The release notes provided with the core list known discrepancies between this handbook and the core release associated with the release notes.

## **Supported Families**

- IGLOO®

- IGLOOe

- IGLOO PLUS

- ProASIC<sup>®</sup>3

- ProASIC3E

- ProASIC3L

- ProASICPLUS

- SmartFusion™

- Fusion

- Axcelerator®

- RTAX-S

- SX-A

- RTSX-S

## 1 – Functional Block Description

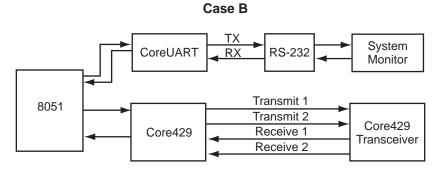

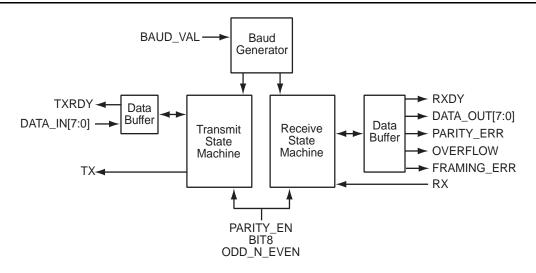

Figure 1-1 shows the block diagram of the CoreUART normal mode functionality. Figure 1-2 on page 8 shows the block diagram of CoreUART with FIFO mode functionality. The baud generator creates a divided down clock enable that correctly paces the transmit and receive state machines.

The function of the receive and transmit state machines is affected by the control inputs BIT8, PARITY\_EN, and ODD\_N\_EVEN. These signals indicate to the state machines how many bits should be transmitted. In addition, the signals suggest the type of parity and whether parity should be generated or checked. The activity of the state machines is paced by the outputs of the baud generator.

To transmit data, it is first loaded into the transmit data buffer in normal mode, and into the transmit FIFO in FIFO mode. Data can be loaded into the buffer until the TXRDY signal is driven inactive. The transmit state machine will immediately begin to transmit data and will continue transmission until the data buffer is empty in normal mode, and until the transmit FIFO is empty in FIFO mode. The state machine first transmits a START bit, followed by the data (LSB first), then the parity (optional), and finally the STOP bit. The data buffer is double-buffered in normal mode, so there is no loading latency.

The receive state machine monitors the activity of the RX signal. Once a START bit is detected, the receive state machine begins to store the data in the receive buffer in normal mode and the receive FIFO in FIFO mode. When the transaction is complete, the RXRDY signal indicates that valid data is available. Parity errors are reported on the PARITY\_ERR signal (if enabled), and data overrun conditions are reported on the OVERFLOW signal. Framing errors are reported on the FRAMING\_ERR signal. A framing error is defined as a missing stop bit detected by the UART receiver.

Figure 1-1 • Block Diagram of CoreUART Normal Functionality

Figure 1-2 • Block Diagram of CoreUART with FIFO Functionality

## **Device Utilization and Performance**

Utilization statistics for targeted devices are listed in Table 1-1 and Table 1-2 on page 9.

Table 1-1 • CoreUART Utilization in FIFO Mode

|                                    |            | Cells or Tiles | Memory | Utilization |           | Performance |     |

|------------------------------------|------------|----------------|--------|-------------|-----------|-------------|-----|

| Family                             | Sequential | Combinatorial  | Total  | Blocks      | Device    | Total       | MHz |

| IGLOO<br>IGLOOe<br>IGLOO PLUS      | 116        | 192            | 308    | 2           | AGL600V5  | 2%          | 71  |

| ProASIC3<br>ProASIC3E<br>ProASIC3L | 116        | 192            | 308    | 2           | A3P600    | 5%          | 128 |

| SmartFusion                        | 116        | 192            | 308    | 2           | A2F500M3F | 7%          | 118 |

| Fusion                             | 116        | 192            | 308    | 2           | AFS600    | 2%          | 127 |

| ProASIC <sup>PLUS</sup>            | 118        | 281            | 399    | 2           | APA600    | 13%         | 68  |

| Axcelerator                        | 171        | 215            | 386    | 2           | AX250     | 9%          | 194 |

| RTAX-S                             | 195        | 199            | 394    | 2           | RTAX250S  | 9%          | 153 |

| SX-A                               | 430        | 309            | 739    | 0           | A54SX16A  | 51%         | 96  |

| RTSX-S                             | 432        | 308            | 740    | 0           | RT54SX32S | 26%         | 62  |

#### Notes:

- 1. CoreUART supports all standard baud rates, including 110, 300, 1,200, 2,400, 4,800, 9,600, 19,200, 38,400, 57,600, 115,200, 230,400, 460,800, and 921,600 baud.

- 2. The depth of the FIFO for SX-A and RTSX-S is 16. For the other families, the depth of the FIFO is 256.

Table 1-2 • CoreUART Utilization in Normal Mode

|                                    | Cells or Tiles |               |       | Memory | Utilization |       | Performance |

|------------------------------------|----------------|---------------|-------|--------|-------------|-------|-------------|

| Family                             | Sequential     | Combinatorial | Total | Blocks | Device      | Total | MHz         |

| IGLOO<br>IGLOOe<br>IGLOO PLUS      | 84             | 167           | 251   | 0      | AGL600      | 2%    | 116         |

| ProASIC3<br>ProASIC3E<br>ProASIC3L | 84             | 167           | 251   | 0      | A3P600      | 4%    | 198         |

| SmartFusion                        | 84             | 167           | 251   | 0      | A2F500M3F   | 6%    | 200         |

| Fusion                             | 84             | 167           | 251   | 0      | AFS600      | 2%    | 197         |

| ProASIC <sup>PLUS</sup>            | 85             | 254           | 339   | 0      | APA600      | 11%   | 89          |

| Axcelerator                        | 86             | 108           | 194   | 0      | AX500       | 5%    | 185         |

| RTAX-S                             | 86             | 108           | 194   | 0      | RTAX250S    | 5%    | 138         |

| SX-A                               | 82             | 93            | 750   | 0      | A54SX16SA   | 12%   | 138         |

| RTSX-S                             | 80             | 92            | 172   | 0      | RT54SX32S   | 6%    | 87          |

Note: CoreUART supports all standard baud rates, including 110, 300, 1,200, 2,400, 4,800, 9,600, 19,200, 38,400, 57,600, 115,200, 230,400, 460,800, and 921,600 baud.

## **Programmable Options**

There are four programmable inputs to CoreUART: BAUD\_VAL (baud rate), BIT8 (number of data bits), PARITY\_EN (parity enable), and ODD\_N\_EVEN (odd or even parity).

#### **Number of Data Bits**

The input BIT8 is used to define the number of valid data bits in the serial bitstream. The most significant bit is a "don't care" for the seven-bit case.

### **Parity**

Parity is enabled/disabled with the input PARITY\_EN. When parity is enabled, the ODD\_N\_EVEN input defines the type of parity.

#### **Baud Rate**

This baud value is a function of the system clock and the desired baud rate. The value should be set according to EQ 1-1.

baud rate =

$$\frac{\text{clk}}{(\text{baudval} + 1) \times 16}$$

EQ 1-1

where

clk = the frequency of the system clock in hertz

baud rate = the desired baud rate

and

baudval =

$$\frac{\text{clk}}{16 \times \text{baudrate}} - 1$$

EQ 1-2

The term baudval must be rounded to the nearest integer. For example, a system with a 33 MHz system clock and a desired baud rate of 9,600 should have a baud\_value of 214 decimal or D6 hex. So, to get the desired baud rate, the user should assign 16#D6 to BAUD\_VAL input.

## 2 - Tool Flows

## Licensing

CoreUART is licensed in two ways. Depending on your license tool flow, functionality may be limited.

#### **Obfuscated**

Complete RTL code is provided for the core, allowing the core to be instantiated with SmartDesign. Simulation, Synthesis, and Layout can be performed within Libero<sup>®</sup> Integrated Design Environment (IDE). The RTL code for the core is obfuscated<sup>1</sup> and some of the testbench source files are not provided; they are precompiled into the compiled simulation library instead.

#### **RTL**

Complete RTL source code is provided for the core and testbenches.

## **SmartDesign**

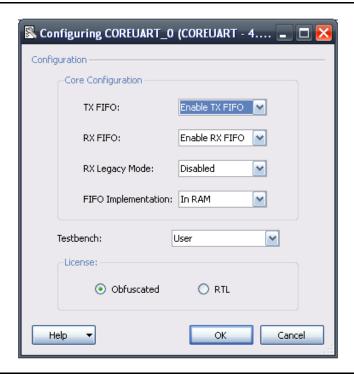

CoreUART is available for download in the SmartDesign IP deployment design environment. The core can be configured using the configuration GUI within SmartDesign, as shown in Figure 2-1.

For more information on using SmartDesign to instantiate and generate cores, refer to the *Using DirectCore in Libero IDE User's Guide*.

Figure 2-1 • SmartDesign CoreUART Configuration Window

1. Obfuscated means the RTL source files have had formatting and comments removed, and all instance and net names have been replaced with random character sequences.

### **Simulation Flows**

The user testbench for CoreUART is included in all releases.

To run simulations, select the user testbench flow within SmartDesign and click **Generate Design** under the SmartDesign menu. The user testbench is selected through the Core Testbench Configuration GUI.

When SmartDesign generates the Libero IDE project, it will install the user testbench files.

To run the user testbench, set the design root to the CoreUART instantiation in the Libero IDE Design Hierarchy pane and click the Simulation icon in the Libero IDE Design Flow window. This will invoke ModelSim® and automatically run the simulation.

#### **User Testbench**

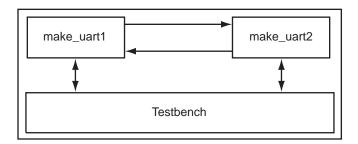

CoreUART is provided with a user testbench (Figure 2-1) to demonstrate sample UART operation. The testbenches are available in both Verilog and VHDL and contain two instances of CoreUART connected to each other. The source code is made available with Obfuscated and RTL licenses of the core.

Figure 2-2 • Verification Testbench

The testbench contains the tests listed in Table 2-1.

Table 2-1 • Verification Tests

| No. | Bit | Parity   | Parity Setting | Parity Error | Overflow Error | Framing Error | Procedure Call |

|-----|-----|----------|----------------|--------------|----------------|---------------|----------------|

| 1   | 8   | Enabled  | Even           | No           | No             | No            | txrxtest       |

| 2   | 8   | Enabled  | Odd            | No           | No             | No            | txrxtest       |

| 3   | 7   | Enabled  | Even           | No           | No             | No            | txrxtest       |

| 4   | 7   | Enabled  | Odd            | No           | No             | No            | txrxtest       |

| 5   | 8   | Disabled | N/A            | No           | No             | No            | txrxtest       |

| 6   | 8   | Disabled | N/A            | No           | No             | No            | txrxtest       |

| 7   | 7   | Disabled | N/A            | No           | No             | No            | txrxtest       |

| 8   | 7   | Disabled | N/A            | No           | No             | No            | txrxtest       |

| 9   | 8   | Enabled  | Even           | Yes          | No             | No            | paritytest     |

| 10  | 8   | Enabled  | Odd            | Yes          | No             | No            | paritytest     |

| 11  | 7   | Enabled  | Even           | Yes          | No             | No            | paritytest     |

| 12  | 7   | Enabled  | Odd            | Yes          | No             | No            | paritytest     |

| 13  | 8   | Enabled  | Odd            | No           | Yes            | No            | testoverflow   |

| 14  | 8   | Enabled  | Odd            | No           | No             | Yes           | N/A            |

CoreUART v4.2 Handbook

The procedure calls txrxtest, paritytest, and testoverflow are defined in the file tbpack.vhd. The top-level testbench, testbench.vhd, utilizes these procedures to perform the corresponding tests listed in Table 2-1.

Refer to the source directory on the release CD for source code for the testbench.

## **Synthesis in Libero IDE**

Click the **Synthesis** icon in Libero IDE. The Synthesis window appears, displaying the Synplify<sup>®</sup> project. Set Synplify to use the Verilog 2001 standard if Verilog is being used. To run Synthesis, select the **Run** icon.

### Place-and-Route in Libero IDE

Click the **Layout** icon in Libero IDE to invoke Designer. CoreUART requires no special place-and-route settings.

## 3 - Core Interfaces

Signal descriptions for CoreUART are given in Table 3-1.

Table 3-1 • CoreUART Signals

| Name <sup>1</sup> | Туре   | Description                                                                                                                                                                                                                                                                                       |

|-------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK               | Input  | Main system clock                                                                                                                                                                                                                                                                                 |

| RESET_N           | Input  | Active low asynchronous reset                                                                                                                                                                                                                                                                     |

| DATA_IN[7:0]      | Input  | Transmit write data bus                                                                                                                                                                                                                                                                           |

| DATA_OUT[7:0]     | Output | Receive read data bus                                                                                                                                                                                                                                                                             |

| WEN               | Input  | Active low write enable. This signal indicates that the data presented on the DATA_IN[7:0] bus should be registered by the transmit buffer/FIFO logic. This signal should only be active for a single clock cycle per transaction and should only be active when the TXRDY signal is active.      |

| OEN               | Input  | Active low read enable. This signal is used to indicate that the data on DATA_OUT[7:0] has been read and will reset the RXRDY bit and any error conditions (OVERFLOW or PARITY_ERR).                                                                                                              |

| CSN               | Input  | Active low chip select. The CSN signal qualifies both the WEN and OEN signals. For embedded applications, this signal should be tied to logic 0.                                                                                                                                                  |

| BIT8              | Input  | Control bit for data bit width for both receive and transmit functions. When BIT8 is logic 1, the data width is 8 bits; otherwise, the data width is 7 bits, data defined by DATA_IN[7] is ignored, and DATA_OUT[7] is "don't care."                                                              |

| PARITY_EN         | Input  | Control bit to enable parity for both receive and transmit functions. Parity is enabled when the bit is set to logic 1.                                                                                                                                                                           |

| ODD_N_EVEN        | Input  | Control bit to define odd or even parity for both receive and transmit functions. When the PARITY_EN control bit is set, a 1 on this bit indicates odd parity and a 0 indicates even parity.                                                                                                      |

| BAUD_VAL[12:0]    | Input  | 13-bit control bus used to define the baud rate                                                                                                                                                                                                                                                   |

| TXRDY             | Output | Status bit; when set to logic 0, indicates that the transmit data buffer/FIFO is not available for additional transmit data.                                                                                                                                                                      |

| RXRDY             | Output | Status bit; when set to logic 1, indicates that data is available in the receive data buffer/FIFO to be read by the system logic. The data buffer/FIFO controller must be notified of the receipt by simultaneous activation of the OEN and CSN signals to prevent erroneous overflow conditions. |

| PARITY_ERR        | Output | Status bit; when set to logic 1, indicates a parity error during a receive transaction. This bit is synchronously cleared by simultaneous activation of the OEN and CSN signals.                                                                                                                  |

| OVERFLOW          | Output | Status bit; when set to logic 1, indicates that a receive overflow has occurred. This bit is synchronously cleared by simultaneous activation of the OEN and CSN signals.                                                                                                                         |

| RX                | Input  | Serial receive data                                                                                                                                                                                                                                                                               |

#### Notes:

- 1. Active low signals are designated with a trailing uppercase N.

- 2. When RX\_FIFO is enabled, PARITY\_ERR is asserted when a parity error occurs, but deasserted before CoreUART receives the next byte. It is the user's responsibility to monitor the PARITY\_ERR signal (for example, treat it as an interrupt signal), as it is non-persistent when RX\_FIFO = 1. FRAMING\_ERR should be treated similarly, when RX\_FIFO = 1.

Table 3-1 • CoreUART Signals (continued)

| Name <sup>1</sup> | Туре   | Description                                                                                                                                                                               |

|-------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX                | Output | Serial transmit data                                                                                                                                                                      |

| FRAMING_ERR       | Output | Status bit; when set to logic 1, indicates that a framing error (missing stop bit) has occurred. This bit is synchronously cleared by simultaneous activation of the OEN and CSN signals. |

#### Notes:

- 1. Active low signals are designated with a trailing uppercase N.

- 2. When RX\_FIFO is enabled, PARITY\_ERR is asserted when a parity error occurs, but deasserted before CoreUART receives the next byte. It is the user's responsibility to monitor the PARITY\_ERR signal (for example, treat it as an interrupt signal), as it is non-persistent when RX\_FIFO = 1. FRAMING\_ERR should be treated similarly, when RX\_FIFO = 1.

### **Core Parameters**

### **CoreUART Configurable Options**

There are a number of configurable options that apply to CoreUART, as shown in Table 3-2. If a configuration other than the default is required, the user should use the configuration dialog box in CoreConsole to select appropriate values for the configurable options.

Table 3-2 • CoreUART Configurable Options

| <b>Configurable Options</b> | Default Setting | Description                                                                                                                                                                                                                             |

|-----------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_FIFO                     | Disabled        | Enables or disables transmit FIFO                                                                                                                                                                                                       |

| RX_FIFO                     | Disabled        | Enables or disables receive FIFO                                                                                                                                                                                                        |

| FAMILY                      | ProASIC3        | Selects target family. Must be set to match the supported FPGA family.                                                                                                                                                                  |

|                             |                 | 8 – SX-A                                                                                                                                                                                                                                |

|                             |                 | 9 – RTSXS<br>11 – Axcelerator                                                                                                                                                                                                           |

|                             |                 | 12 – RTAX-S                                                                                                                                                                                                                             |

|                             |                 | 1- 1111111                                                                                                                                                                                                                              |

|                             |                 | 14 – ProASIC <sup>PLUS</sup><br>15 – ProASIC3                                                                                                                                                                                           |

|                             |                 |                                                                                                                                                                                                                                         |

|                             |                 | 16 – ProASIC3E                                                                                                                                                                                                                          |

|                             |                 | 17 – Fusion                                                                                                                                                                                                                             |

|                             |                 | 18 – SmartFusion                                                                                                                                                                                                                        |

|                             |                 | 20 – IGLOO                                                                                                                                                                                                                              |

|                             |                 | 21 – IGLOOe                                                                                                                                                                                                                             |

|                             |                 | 22 – ProASIC3L                                                                                                                                                                                                                          |

|                             |                 | 23 – IGLOO PLUS                                                                                                                                                                                                                         |

| RX_LEGACY_MODE              | Disabled        | When disabled, the RXRDY signal is synchronized with the FRAMING_ERR output, which occurs after the stop bit. When enabled (Legacy mode), the RXRDY signal is asserted after all data bits have been received, but before the stop bit. |

| USE_SOFT_FIFO               | Disabled        | When disabled, the FIFO is implemented using a device-specific hard macro. When enabled, a 16-byte FIFO is implemented in FPGA logic instead. RTAX and RTSX-S devices use this soft FIFO by default.                                    |

## 4 - Timing Diagrams

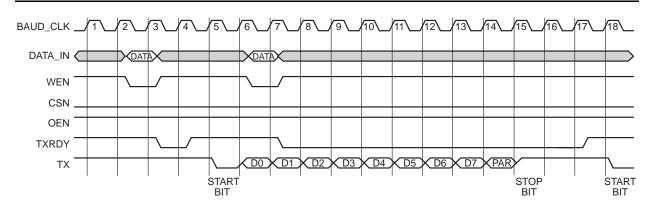

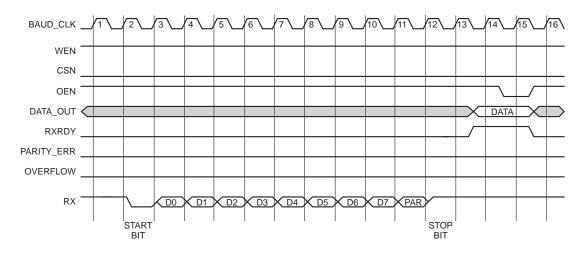

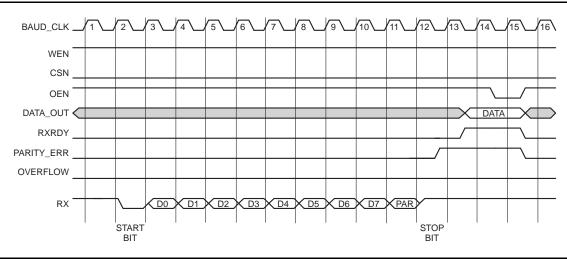

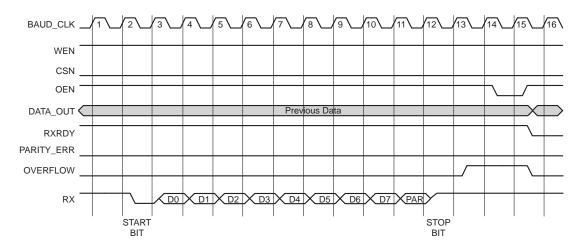

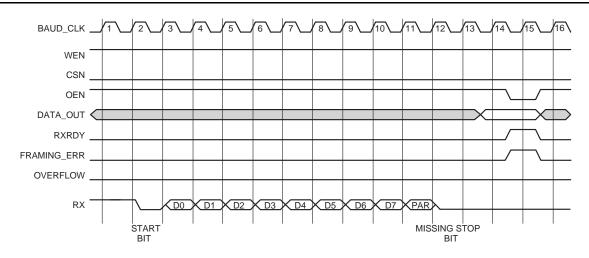

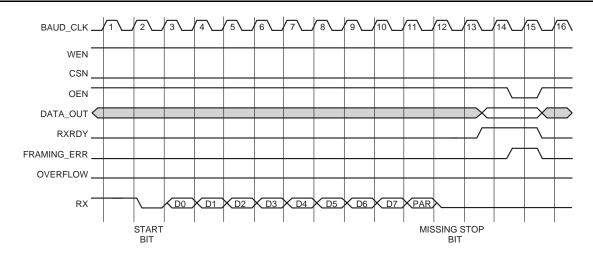

The UART waveforms can be broken down into a few basic functions: transmit data, receive data, and errors. Figure 4-1 shows serial transmit signals, and Figure 4-2 on page 18 shows serial receive signals. Figure 4-3 on page 18 and Figure 4-4 on page 19 show the parity and overflow error cycles, respectively. The number of clock cycles required is equal to the clock frequency divided by the baud rate. All waveforms assume that eight bits of data and parity are enabled. All waveforms, except "Framing Error" on page 19, assume Legacy mode is ENABLED.

### **Serial Transmit**

Figure 4-1 • Serial Transmit

#### Notes:

- A serial transmit is initiated by writing data into CoreUART. This is accomplished by providing valid data and asserting the WEN and CSN signals. The TXRDY signal will become inactive for one cycle while the data is being transferred from the transmit hold register to the transmit register that begins the serial transfer.

- 2. The transmission begins with a START bit, followed by data bits 0 through 6, the optional seventh bit, the optional parity bit, and finally the STOP bit.

- 3. Because the UART is double-buffered, data can be queued in the transmit hold register (cycle 7). The TXRDY line, when Low, indicates that no more data can be transferred to the UART.

- Once the previous serial transfer is complete, the data in the transmit hold register is passed to the transmit register, and the transfer begins. The TXRDY line is also asserted, indicating that the next data byte can be loaded.

### **Serial Receive**

Figure 4-2 • Serial Receive

#### Notes:

- 1. CoreUART continuously monitors the RX line, polling for a START bit. Once the START bit is detected, CoreUART registers the data stream. The optional parity bit is also registered and checked. A START bit is defined as logic 0-bit value on the RX line when the core is idle.

- 2. The data is then loaded into the receive hold buffer, and the RXRDY signal is asserted. The RXRDY signal will remain asserted until the data is read externally, indicated by the simultaneous assertion of CSN and OEN.

## **Parity Error**

Figure 4-3 • Parity Error

#### Notes:

- 1. When a parity error occurs, the PARITY\_ERR signal is asserted.

- 2. The error is cleared by the same method used to read the data, simultaneous assertion of CSN and OEN.

### **Overflow Error**

Figure 4-4 • Overflow Error

#### Notes:

- 1. When a data overflow error occurs, the OVERFLOW signal is asserted.

- 2. The previous data is held and the new data is lost. The error is cleared by the same method used to read the data, simultaneous assertion of CSN and OEN.

## **Framing Error**

Figure 4-5 • Framing Error

#### Notes:

- 1. Legacy mode is disabled in this timing diagram.

- 2. In Normal (non-legacy) mode, RXRDY and FRAMING\_ERR are synchronized. They are asserted in the same clock cycle. The error is cleared using a read operation simultaneous assertion of OEN and CSN.

## Framing Error in Legacy Mode

Figure 4-6 • Framing Error in Legacy Mode

#### Notes:

- 1. Legacy mode is enabled in this timing diagram.

- 2. In Legacy mode, RXRDY is asserted one cycle before FRAMING\_ERR is asserted. The error is cleared using a read operation: simultaneous assertion of OEN and CSN.

# 5 - Ordering Information

## **Ordering Codes**

CoreUART can be ordered through your local Actel sales representative. It should be ordered using the following number scheme: CoreUART-XX, where XX is listed in Table 5-1.

Table 5-1 • Ordering Codes

| XX | Description                                   |

|----|-----------------------------------------------|

| ОМ | RTL for Obfuscated RTL – multiple-use license |

| RM | RTL for RTL source – multiple-use license     |

Note: CoreUART-OM is included free with a Libero IDE license.

# A - List of Document Changes

The following table lists critical changes that were made in each revision of the document.

| Revision                      | Changes                                                                                                                                                                  | Page  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Revision 2<br>(October 2010)  | The core version was updated to v4.2.                                                                                                                                    | 6     |

|                               | SmartFusion and ProASIC3E were added to the "Supported Families" section.                                                                                                | 6     |

|                               | SmartFusion was added to Table 1-1 • CoreUART Utilization in FIFO Mode and Table 1-2 • CoreUART Utilization in Normal Mode.                                              | 8, 9  |

|                               | EQ 1-2 is new.                                                                                                                                                           | 10    |

|                               | The "Tool Flows" chapter was rewritten. The "Testbench Operation" chapter was deleted because its relevant content was incorporated into the "Tool Flows" chapter.       | 11    |

|                               | Signal names were made all upper case. The second note for Table 3-1 • CoreUART Signals was revised to add, "FRAMING_ERR should be treated similarly, when RX_FIFO = 1." | 15    |

|                               | SmartFusion was added to Table 3-2 • CoreUART Configurable Options.                                                                                                      | 16    |

| Revision 1<br>(February 2009) | Added framing error (FRAMING_ERR signal) support.                                                                                                                        | 7     |

|                               | Updated the "Tool Flows" chapter with SmartDesign flow.                                                                                                                  | 11    |

|                               | Updated Table 3-1 • CoreUART Signals to include FRAMING_ERR signal.                                                                                                      | 15    |

|                               | Updated Table 3-2 • CoreUART Configurable Options with new configurable options.                                                                                         | 16    |

|                               | Added Framing Error and Framing Error in Legacy Mode timing diagrams.                                                                                                    | 19–20 |

## **B** – Product Support

Actel backs its products with various support services including Customer Service, a Customer Technical Support Center, a web site, an FTP site, electronic mail, and worldwide sales offices. This appendix contains information about contacting Actel and using these support services.

#### **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From Northeast and North Central U.S.A., call 650.318.4480

From Southeast and Southwest U.S.A., call 650. 318.4480

From South Central U.S.A., call 650.318.4434

From Northwest U.S.A., call 650.318.4434

From Canada, call 650.318.4480

From Europe, call 650.318.4252 or +44 (0) 1276 401 500

From Japan, call 650.318.4743

From the rest of the world, call 650.318.4743

Fax, from anywhere in the world 650.318.8044

## **Actel Customer Technical Support Center**

Actel staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions. The Customer Technical Support Center spends a great deal of time creating application notes and answers to FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

## **Actel Technical Support**

Visit the Actel Customer Support website (www.actel.com/support/search/default.aspx) for more information and support. Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on the Actel web site.

### **Website**

You can browse a variety of technical and non-technical information on Actel's home page, at www.actel.com.

## **Contacting the Customer Technical Support Center**

Highly skilled engineers staff the Technical Support Center from 7:00 a.m. to 6:00 p.m., Pacific Time, Monday through Friday. Several ways of contacting the Center follow:

#### **Email**

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is tech@actel.com.

#### **Phone**

Our Technical Support Center answers all calls. The center retrieves information, such as your name, company name, phone number and your question, and then issues a case number. The Center then forwards the information to a queue where the first available application engineer receives the data and returns your call. The phone hours are from 7:00 a.m. to 6:00 p.m., Pacific Time, Monday through Friday. The Technical Support numbers are:

650.318.4460 800.262.1060

Customers needing assistance outside the US time zones can either contact technical support via email (tech@actel.com) or contact a local sales office. Sales office listings can be found on the website at www.actel.com/company/contact/default.aspx.

# Index

normal mode 7

| A                              | 0                               |  |  |

|--------------------------------|---------------------------------|--|--|

| Actel                          | ordering code 21                |  |  |

| electronic mail 25             | 3                               |  |  |

| telephone 26                   | P                               |  |  |

| web-based technical support 25 | parity                          |  |  |

| website 25                     | errors 7                        |  |  |

|                                | product support 26              |  |  |

| В                              | customer service 25             |  |  |

| baud generator 7               | electronic mail 25              |  |  |

| block diagram 7                | technical support 25            |  |  |

| FIFO mode 8                    | telephone 26                    |  |  |

| normal mode 7                  | website 25                      |  |  |

| buffers                        |                                 |  |  |

| receive 7                      | S                               |  |  |

| transmit 7                     | signals, I/O 15                 |  |  |

|                                | state machines                  |  |  |

| C                              | receive 7                       |  |  |

| configurable options 16        | transmit 7                      |  |  |

| contacting Actel               |                                 |  |  |

| customer service 25            | T                               |  |  |

| electronic mail 25             | technical support 25            |  |  |

| telephone 26                   | testbenches                     |  |  |

| web-based technical support 25 | verification 12                 |  |  |

| control inputs 7               | timing diagrams                 |  |  |

| core versions 5                | framing error 19                |  |  |

| customer service 25            | framing error in legacy mode 20 |  |  |

|                                | overflow error 19               |  |  |

| D                              | parity error 18                 |  |  |

| description, general 5         | serial receive 18               |  |  |

| device                         | serial transmit 17              |  |  |

| utilization and performance 8  |                                 |  |  |

| double-buffering 7             | U                               |  |  |

| · ·                            | use cases 5                     |  |  |

| F                              | 400 04000 0                     |  |  |

| FIFO mode 7                    | V                               |  |  |

| FIFOs                          | verification testbench 12       |  |  |

| receive 7                      |                                 |  |  |

| transmit 7                     | versions, core 5                |  |  |

|                                | W                               |  |  |

| G                              |                                 |  |  |

| general description 5          | web-based technical support 25  |  |  |

| general description o          |                                 |  |  |

| 1                              |                                 |  |  |

| I/O signals 15                 |                                 |  |  |

| 1/O signals 10                 |                                 |  |  |

|                                |                                 |  |  |

Actel is the leader in low power FPGAs and mixed signal FPGAs and offers the most comprehensive portfolio of system and power management solutions. Power Matters. Learn more at www.actel.com.

#### **Actel Corporation**

2061 Stierlin Court Mountain View, CA 94043-4655 USA **Phone** 650.318.4200 **Fax** 650.318.4600

#### Actel Europe Ltd.

River Court, Meadows Business Park Station Approach, Blackwater Camberley Surrey GU17 9AB United Kingdom

**Phone** +44 (0) 1276 609 300 **Fax** +44 (0) 1276 607 540

#### **Actel Japan**

EXOS Ebisu Buillding 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150 Japan **Phone** +81.03.3445.7671

Fax +81.03.3445.7668 http://jp.actel.com

### **Actel Hong Kong**

Room 2107, China Resources Building 26 Harbour Road Wanchai, Hong Kong **Phone** +852 2185 6460 **Fax** +852 2185 6488 www.actel.com.cn

© 2010 Actel Corporation. All rights reserved. Actel, Actel Fusion, IGLOO, Libero, Pigeon Point, ProASIC, SmartFusion and the associated logos are trademarks or registered trademarks of Actel Corporation. All other trademarks and service marks are the property of their respective owners.