| LTR                                                                        |                                                                                                                                                                                 | DESCRIPTION |         |         |                 |                    |              |         | D       | ATE     | (YR-MC  | )-DA)                 |         | APPR | OVED |      |      |      |        |    |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|---------|-----------------|--------------------|--------------|---------|---------|---------|---------|-----------------------|---------|------|------|------|------|------|--------|----|

| D                                                                          | Update boilerplate. Add device types 17 through 24. Add vendor CAGE 61772 as source of supply for device types 17 through 24. Add case outline T. Editorial changes throughout. |             |         |         |                 |                    | 9            | 4-09    | -06     |         | М       | i. A.                 | Fry     | e    |      |      |      |      |        |    |

| THE ORGI                                                                   | NAL I                                                                                                                                                                           | FIRST       | г РАС   | E OF    | THI             | S DR               | AWIN         | G НА:   | S BEI   | EN RE   | PLAC    | ED.                   |         |      |      |      |      |      |        |    |

| REV                                                                        |                                                                                                                                                                                 |             |         |         |                 | ļ                  | ļ            |         |         |         |         |                       |         |      |      |      |      |      |        |    |

| SHEET                                                                      |                                                                                                                                                                                 |             |         |         |                 |                    |              |         |         |         |         |                       |         |      |      |      |      |      |        |    |

| REV                                                                        | D<br>15                                                                                                                                                                         | 16          | D<br>17 | D<br>18 | D<br>19         | D 20               | D 24         | D 22    | D 27    | D       | D       | D                     | D 27    |      |      |      |      |      |        |    |

| SHEET REV STAT                                                             | L                                                                                                                                                                               | 16          | 1′      | RE      | L               | 20                 | 21<br>D      | 22<br>D | 23<br>D | 24<br>D | 25<br>D | 26<br>D               | 27<br>D | D    | D    | D    | D    | D    | D      | D  |

| OF SHEET                                                                   |                                                                                                                                                                                 |             |         | <b></b> | EET             |                    | 1            | 2       | 3       | 4       | 5       | 6                     | 7       | 8    | 9    | 10   | 11   | 12   | 13     | 14 |

| PMIC N/A                                                                   |                                                                                                                                                                                 |             |         |         | ARED E          |                    | Jamis        | on      | 1       | D       | EFEN:   |                       |         |      |      | PPLY |      | rer  | I      |    |

| STANDARD  CHECKED BY  Charkes Reusing                                      |                                                                                                                                                                                 |             |         |         |                 | DAYTON, OHIO 45444 |              |         |         |         |         |                       |         |      |      |      |      |      |        |    |

| DRAWING  APPROVED BY  THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS |                                                                                                                                                                                 |             |         | 2K      | X 8             | CM                 |              | STA     | ric     |         |         | EMORY,<br>DUAL PORT), |         |      |      |      |      |      |        |    |

| AND AGEN<br>DEPARTMEN                                                      | CIES C                                                                                                                                                                          | F THE       |         |         | ING AF<br>Janua |                    | L DATE<br>88 |         |         | SIZ     |         | r                     | E CO    |      |      | 59   | 962- | 8700 | <br>02 |    |

| AMSC N/A                                                                   | ı                                                                                                                                                                               |             |         | REVI    | SION E          | EVEL<br>D          |              |         |         | A       |         | 1                     | 5726    |      |      |      |      |      |        |    |

|                                                                            |                                                                                                                                                                                 |             |         |         |                 |                    |              |         |         | SH      | EET     | 1                     |         | OI   | •    | 27   |      |      |        |    |

REVISIONS

DESC FORM 193 JUL 94

$\underline{\textbf{DISTRIBUTION STATEMENT A}}. \ \textbf{Approved for public release; distribution is unlimited}.$

5962-E371-94

🖿 9004708 0003507 l42 🖿

- 1. SCOPE

- 1.1 <u>Scope</u>. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

- 1.2 Part or Identifying Number (PIN). The complete PIN shall be as shown in the following example:

1.2.1 Device type(s). The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | Circuit function                    | Access time |

|-------------|----------------|-------------------------------------|-------------|

| 01          | 7132SA         | 2K X 8 dual port static RAM, MASTER | 45 ns       |

| 02          | 7132SA         | 2K X 8 dual port static RAM, MASTER | 90 ns       |

| 03          | 7132SA         | 2K X 8 dual port static RAM, MASTER | 70 ns       |

| 04          | 7132SA         | 2K X 8 dual port static RAM, MASTER | 55 ns       |

| 05          | 7132LA         | 2K X 8 dual port static RAM, MASTER | 45 ns       |

| 06          | 7132LA         | 2K X 8 dual port static RAM, MASTER | 90 ns       |

| 07          | 7132LA         | 2K X 8 dual port static RAM, MASTER | 70 ns       |

| 08          | 7132LA         | 2K X 8 dual port static RAM, MASTER | 55 ns       |

| 09          | 7142SA         | 2K X 8 dual port static RAM, SLAVE  | 45 ns       |

| 10          | 7142SA         | 2K X 8 dual port static RAM, SLAVE  | 90 ns       |

| <b>1</b> 1  | 7142SA         | 2K X 8 dual port static RAM, SLAVE  | 70 ns       |

| 12          | 7142SA         | 2K X 8 dual port static RAM, SLAVE  | 55 ns       |

| 13          | 7142LA         | 2K X 8 dual port static RAM, SLAVE  | 45 ns       |

| 14          | 7142LA         | 2K X 8 dual port static RAM, SLAVE  | 90 ns       |

| 15          | 7142LA         | 2K X 8 dual port static RAM, SLAVE  | 70 ns       |

| 16          | 7142LA         | 2K X 8 dual port static RAM, SLAVE  | 55 ns       |

| 17          | 7132SA         | 2K X 8 dual port static RAM, MASTER | 35 ns       |

| 18          | 7132LA         | 2K X 8 dual port static RAM, MASTER | 35 ns       |

| 19          | 7132SA         | 2K X 8 dual port static RAM, MASTER | 25 ns       |

| 20          | 7132LA         | 2K X 8 dual port static RAM, MASTER | 25 ns       |

| 21          | 7142SA         | 2K X 8 dual port static RAM, SLAVE  | 35 ns       |

| 22          | 7142LA         | 2K X 8 dual port static RAM, SLAVE  | 35 ns       |

| 23          | 7142SA         | 2K X 8 dual port static RAM, SLAVE  | 25 ns       |

| 24          | 7142LA         | 2K X 8 dual port static RAM, SLAVE  | 25 ns       |

1.2.2 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style                |

|----------------|------------------------|------------------|------------------------------|

| x              | CQCC1-N52              | 52               | square leadless chip carrier |

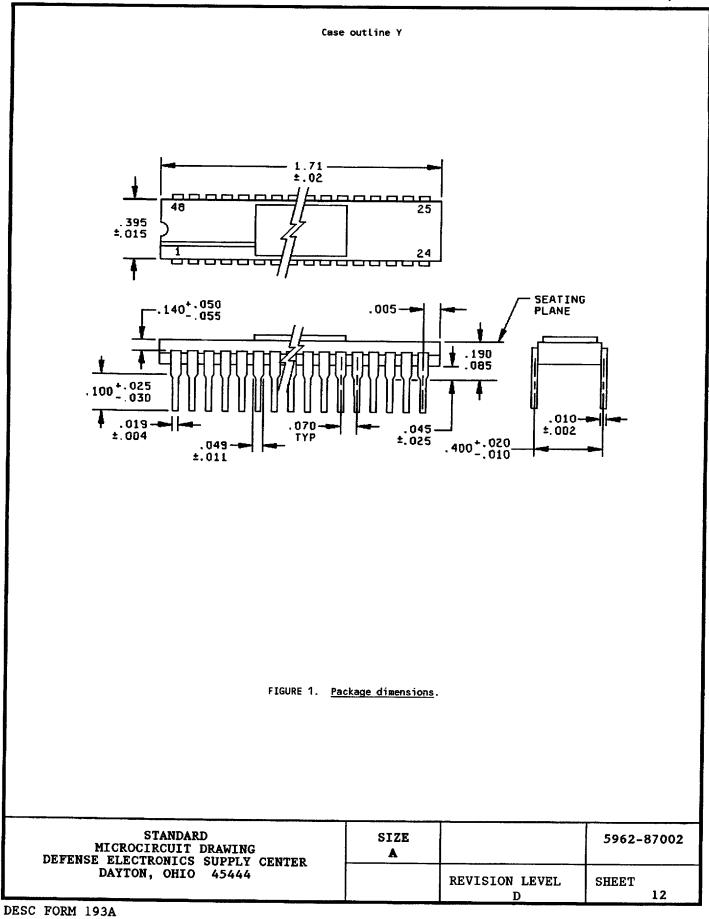

| Y              | See figure 1           | 48               | dual-in-line                 |

| Z              | GDIP1-T48 or CDIP2-T48 | 48               | dual-in-lin <del>e</del>     |

| U              | See figure 1           | 48               | square leadless chip carrier |

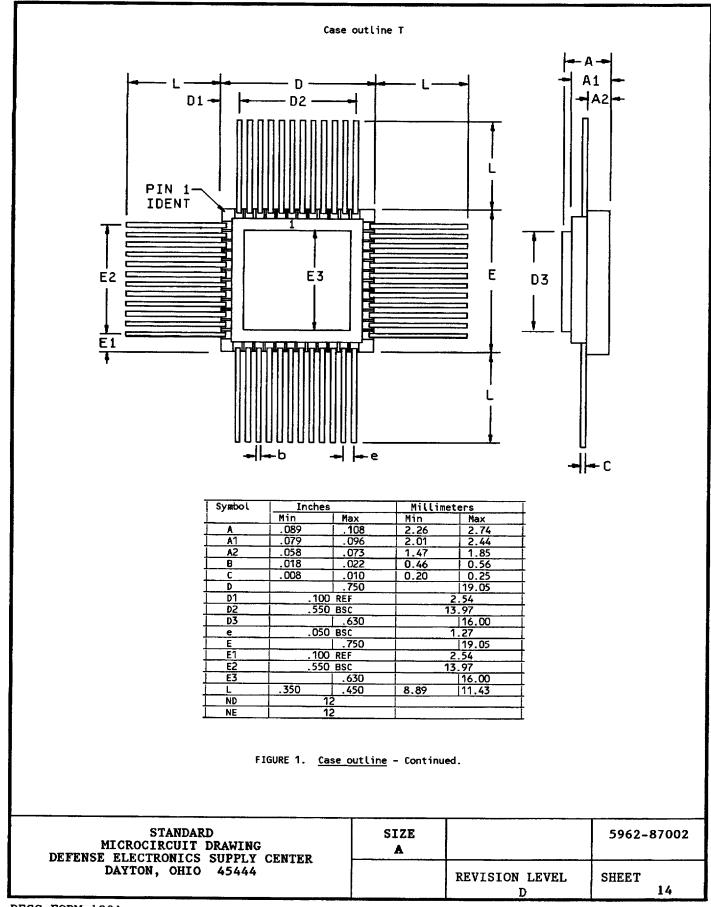

| T              | See figure 1           | 48               | flat pack                    |

1.2.3 <u>Lead finish</u>. The lead finish shall be as specified in MIL-STD-883 (see 3.1 herein). Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

### 1.3 Absolute maximum ratings.

$\overline{1/}$  Unless otherwise specified, all voltages are referenced to  $V_{SS}$ .

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>D | SHEET 2    |

DESC FORM 193A JUL 94

9004708 0003508 089 📟

|     | Power dissipation ( $P_D$ ) Lead temperature (soldering, 5 seconds) Maximum junction temperature ( $T_J$ ) $\underline{2}/$ Thermal resistance, junction-to-case ( $\theta_{JC}$ ): | 1 W<br>+270°C<br>+150°C                                                                                                          |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|     | Cases X and Z                                                                                                                                                                       | See MIL-STD-1835<br>23°C/W <u>3</u> /<br>24°C/W <u>3</u> /<br>20°C/W <u>3</u> /<br>50 mA                                         |

| 1.4 | Recommended operating conditions.                                                                                                                                                   |                                                                                                                                  |

|     | Case operating temperature range $(T_C)$                                                                                                                                            | -55°C to +125°C<br>-0.5 to +0.8 V dc <u>4/</u><br>+2.2 V to V <sub>CC</sub> +0.5 V dc <u>4/</u><br>+4.5 V to +5.5 V dc <u>4/</u> |

| ~   | ARRI TOARI E ROCUMENTO                                                                                                                                                              |                                                                                                                                  |

#### 2. APPLICABLE DOCUMENTS

2.1 Government specification, standards, and bulletin. Unless otherwise specified, the following specification, standards, and bulletin of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

SPECIFICATION

MILITARY

MIL-I-38535 - Integrated Circuits (Microcircuits) Manufacturing, General Specification for.

**STANDARDS**

MILITARY

MIL-STD-883 - Test Methods and Procedures for Microelectronics. MIL-STD-1835 Microcircuit Case Outlines.

BULLETIN

MIL TTARY

MIL-STD-103 - List of Standardized Military Drawings (SMD's).

(Copies of the specification, standards, and bulletin required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

#### 3. REQUIREMENTS

3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. Product built to this drawing that is produced by a Qualified Manufacturer Listing (QML) certified and qualified manufacturer or a manufacturer who has been granted transitional certification to MIL-I-38535 may be processed as QML product in accordance with the manufacturers approved program plan and qualifying activity approval in accordance with MIL-I-38535. This QML flow as documented in the Quality Management (QM) plan may make modifications to the requirements herein. These modifications shall not affect form, fit, or function of the device. These modifications shall not affect the PIN as described herein. A "Q" or "QML" certification mark in accordance with MIL-I-38535 is required to identify when the QML flow option is used.

Maximum junction temperature shall not be exceeded except for allowable short duration burn-in screening conditions in accordance with method 5004 of MIL-STD-883.

When a thermal resistance value for this case outline is included in MIL-STD-1835, that value shall supersede the value specified herein.

4/ Unless otherwise specified, all voltages are referenced to ground.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002 |

|-----------------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                                    |           | REVISION LEVEL<br>D | SHEET<br>3 |

DESC FORM 193A JUL 94

9004708 0003509 T15 📟

| Test                                                   | Symbol Conditions |                                                                                                |                                                                         | Group A   | Device                     | Limits                                           |                | <u> </u> Unit |

|--------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------|----------------------------|--------------------------------------------------|----------------|---------------|

| **************************************                 |                   | -55°C ≤ T<br> V <sub>SS</sub> = 0 V, 4.5<br>  unless otherw                                    | $c \le +125^{\circ}c$<br>$V \le V_{CC} \le 5.5$ Volume of the specified | subgroups | type                       | Min                                              | Max            | <br>          |

| Output high voltage<br>level                           | v <sub>OH</sub>   | V <sub>CC</sub> = 4.5 V, I <sub>O</sub><br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>I</sub> | 0H = -4.0 mA<br>N = V <sub>IL</sub>                                     | 1,2,3     | ALL                        | 2.4                                              | <br> <br> <br> | V             |

| Output low voltage<br>level                            | v <sub>OL</sub>   |                                                                                                | I <sub>OL</sub> = 6 mA                                                  | 1,2,3     | ALL                        |                                                  | 0.4            | ٧             |

|                                                        |                   | or VIN = VIL                                                                                   | I <sub>OL</sub> = 8 mA                                                  |           | <u> </u>                   |                                                  | 0.5            |               |

| Open drain <u>outp</u> ut low<br>voltage (BUSY output) | v <sub>oL1</sub>  | v <sub>cc</sub> = 4.5 v, I <sub>o</sub>                                                        | L = 16 mA                                                               | 1,2,3     | ALL                        |                                                  | 0.5            | V             |

| Input high voltage<br>level                            | V <sub>IH</sub>   |                                                                                                |                                                                         | 1,2,3     | ALL                        | 2.2                                              |                | ٧             |

| Input low voltage<br>level                             | v <sub>IL</sub>   |                                                                                                |                                                                         | 1,2,3     | All                        |                                                  | 0.8            | ٧             |

| Input leakage current                                  | IIH               | v <sub>cc</sub> = 5.5 v                                                                        | v <sub>IN</sub> = v <sub>CC</sub>                                       | 1,2,3     | ALL                        |                                                  | 10             | μΑ            |

|                                                        |                   |                                                                                                | VIN = O V                                                               | 1,2,3     | ALL                        | -10                                              |                |               |

| Dynamic operating                                      | T                 | CE = V <sub>II</sub> , outpu                                                                   | ts open                                                                 | 1,2,3     | 19,23<br>17,21             |                                                  | 300<br>290     | ļ             |

| current, both ports                                    | 1cc               | I TIL, backa                                                                                   | - VIL/ outputs open                                                     |           | 20,24                      | <u> </u>                                         | 240            | ‡             |

| active                                                 |                   |                                                                                                |                                                                         |           | 01,04,09,<br>12,18,22      |                                                  | 230            | mA            |

|                                                        |                   |                                                                                                |                                                                         | ĺ         | 03,11                      | <del>                                     </del> | 225            | Ì             |

|                                                        |                   |                                                                                                |                                                                         |           | 02,10                      | ļ                                                | 200            | Ļ             |

|                                                        |                   | ļ                                                                                              |                                                                         | 1         | 05,08,                     | ]                                                | 185            | ļ             |

|                                                        |                   |                                                                                                |                                                                         |           | 13,16<br>07,15             | 1                                                | 180            | †             |

|                                                        |                   | İ                                                                                              |                                                                         | i         | 06,14                      | 1                                                | 160            | Ī             |

|                                                        |                   |                                                                                                |                                                                         |           | 17,19,                     |                                                  | 80             |               |

| Standby current, both                                  | I <sub>SB1</sub>  | CE <sub>R</sub> and CE <sub>L</sub> ≥ V                                                        | IH                                                                      | 1,2,3     | 21,23                      | <u> </u>                                         | ļ              | Ļ             |

| ports inactive, TTL<br>level inputs                    | 1                 |                                                                                                |                                                                         |           | 01-04                      | 1                                                | 65             | mA            |

| tevet inputs                                           |                   |                                                                                                |                                                                         |           | 18,20,                     | <del>                                     </del> | 60             | 1             |

|                                                        | į                 |                                                                                                |                                                                         |           | 22,24                      |                                                  | <u> </u>       | Ĺ             |

|                                                        | ļ                 |                                                                                                |                                                                         | Į         | 05,07,08,                  | •                                                | 55             | !             |

|                                                        |                   |                                                                                                |                                                                         |           | <u>13,15,16</u><br>  06,14 | <u> </u>                                         | 45             | L             |

|                                                        | 1                 |                                                                                                |                                                                         |           | 19,23                      |                                                  | 195            |               |

| Standby current, one                                   | I <sub>SB2</sub>  | CE <sub>R</sub> or CE <sub>L</sub> ≥ V <sub>I</sub><br>Active port out                         | и                                                                       | 1,2,3     | 17,21                      |                                                  | 185            | Ī             |

| port active, TTL                                       | 1 302             | Active port out                                                                                | puts open                                                               |           | 20,24                      |                                                  | 160            | <u>[</u>      |

| level inputs                                           | - !               | !                                                                                              |                                                                         |           | 18,22                      |                                                  | 150            | ļ.            |

|                                                        |                   |                                                                                                |                                                                         |           | 01,03,04,<br>09,11,12      |                                                  | 135            | mA            |

|                                                        |                   | İ                                                                                              |                                                                         |           | 02,10                      | i                                                | 125            | Ì             |

|                                                        | į.                | !                                                                                              |                                                                         | 1         | 05,07,08,                  |                                                  | 110            |               |

|                                                        | 1                 | 1                                                                                              |                                                                         | 1         | 13,15,16                   | l                                                | l              | L             |

See footnotes at end of table.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-87002 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>4 |

DESC FORM 193A JUL 94

■ 9004708 0003510 737 **■**

TABLE I. <u>Electrical performance characteristics</u> - Continued. Unit Limits Test Symbol Conditions Group A Device  $| -55^{\circ}C \le T_{C} \le +125^{\circ}C$  $| v_{SS} = 0 \text{ v}, 4.5 \text{ v} \le v_{CC} \le 5.5 \text{ v}$ subgroups type Min Max unless otherwise specified  $|\overline{CE}_R|$  and  $|\overline{CE}_L| \ge V_{CC} -0.2 \text{ V}$   $|V_{IN}| \ge V_{CC} -0.2 \text{ V}$  or  $|V_{IN}| \le 0.2 \text{ V}$ Full standby current, 01-04, 30 mA 1,2,3 I<sub>SB3</sub> both ports inactive, 09-12, CMOS level inputs 17,19, 21,23 05-08, 13-16, 18,20, 10 22,24 19,23 185  $\overline{CE}_R$  or  $\overline{CE}_L \ge V_{CC} -0.2 \text{ V}$   $|V_{IN} \ge V_{CC} -0.2 \text{ V}$  or  $|V_{IN} \le 0.2 \text{ V}$ Full standby current, 175 1,2,3 17,21 I<sub>SB4</sub> 150 one port active, 20,24 CMOS level inputs 140 18,22 01,03,04, Active port outputs open mA 09,11,12 125 02,05,10, 110 06,07,08, 14,15,16 90 VOUT = 0 V or VOUT = VCC μА -10 10 Output leakage current ALL Ioz 1,2,3  $|V_{CC}| = 2.0 \text{ V}, \overline{CE} \ge V_{CC} - 0.2 \text{ V},$   $|V_{IN}| \ge V_{CC} - 0.2 \text{ V or}$   $|V_{IN}| \le 0.2 \text{ V}$ V<sub>CC</sub> for data 1,2,3 05-08, 2.0 ٧ VDR 13-16, retention 18,20, 22,24  $|v_{CC}| = 2.0 \text{ V}, \overline{CE} \ge v_{CC} -0.2 \text{ V}$   $|v_{IN}| \ge v_{CC} -0.2 \text{ V}$  or  $|v_{IN}| \le 0.2 \text{ V}$ Data retention current 05-08, 4000 μA 1,2,3  $^{\rm I}$ CCDR 13-16, 18,20, 22,24  $v_{CC} = 2.0 \text{ V}, \overline{CE} \ge v_{CC} -0.2 \text{ V}$   $v_{IN} \le v_{CC} -0.2 \text{ V}$  or  $v_{IN} \le 0.2 \text{ V}$ Chip deselect to data 9,10,11 05-08, O <sup>t</sup>cdr ns retention time 1/ 13-16, 18,20, 22,24  $v_{CC} = 2.0 \text{ v, } \overline{CE} \ge v_{CC} -0.2 \text{ v}$   $v_{IN} \ge v_{CC} -0.2 \text{ v or}$   $v_{IN} \le 0.2 \text{ v}$  1/ Operation recovery t<sub>R</sub> 9,10,11 05-08, tayav ns time 13-16, 18,20, 22,24 Functional tests See 4.3.1d 7,8A,8B ALL  $T_A = 25$ °C,  $V_{IN} = 0$  V, f = 1 MHz, see 4.3.1c CIN Input capacitance 4 ALL 11 рF |T<sub>A</sub> = 25°C, V<sub>OUT</sub> = 0 V, |f = 1 MHz, see 4.3.1c Output capacitance COUT 4 ALL 11

See footnotes at end of table.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>D | SHEET<br>5 |

DESC FORM 193A JUL 94

🖿 9004708 0003511 673 📟

TABLE I. <u>Electrical performance characteristics</u> - Continued. Test Symbol Conditions Group A Device Unit Limits  $-55^{\circ}C \le T_{C} \le +125^{\circ}C$   $|V_{SS} = 0 \text{ V, } 4.5 \text{ V} \le V_{CC} \le 5.5 \text{ V}$ unless otherwise specified subgroups type Min Max Read/write cycle time See figure 5 9,10,11 01,05,09, 45 <sup>t</sup>AVAV ns 02,06,10, 90 03,07,11, 70 04,08,12, 55 17,18,21, 35 19,20,23, 25 Address access time 9,10,11 01,05,09, <sup>t</sup>AVQV 45 ns 02,06,10, 90 03,07,11, 70 04,08,12, 55 16 17,18,21, 35 22 19,20,23, 25 Chip enable access <sup>t</sup>ELQV 9,10,11 01,05,09, 45 กร time 13 02,06,10, 90 03,07,11, 70 04,08,12, 55 16 17,18,21, 35 22 19,20,23, 25 Output enable access 9,10,11 02,03,06, <sup>t</sup>olqv 40 ns time 07,10,11, 04,08,12, 35 01,05,09, 30 17,18,21, 25 19,20,23, 12

See footnotes at end of table.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>D | SHEET<br>6 |

DESC FORM 193A JUL 94

■ 7004708 00035l2 50T ■

| Test                                           | Symbol            | Conditions                                                                                                                 | Group A<br>subgroups | Device                                 | Limits |     | Unit       |

|------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------|--------|-----|------------|

|                                                |                   | -55°C ≤ T <sub>C</sub> ≤ +125°C<br> V <sub>SS</sub> = 0 V, 4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V<br>  unless otherwise specified |                      | type                                   | Min    | Max | ļ<br>      |

| Output hold from address change                | <sup>t</sup> AVQX | See figure 5                                                                                                               | 9,10,11              | 02,06,10,                              | 10     |     | ns         |

| •                                              |                   |                                                                                                                            |                      | 01,03-05,<br>07-09,<br>11-13,<br>15-24 | 0      |     | †<br> <br> |

| Output low Z time 1/3/                         | toLQZ             | †<br>!<br>!                                                                                                                | 9,10,11              | 01-16,17,                              | 5      |     | ns         |

|                                                | -                 | <del> </del>                                                                                                               |                      | 19,20,23,<br> 24                       | 0      |     | <u> </u>   |

| Output high Z time<br>1/ 3/                    | <sup>t</sup> oHQZ |                                                                                                                            | 9,10,11              | 02,06,10,<br>14                        | !<br>! | 40  | ns         |

|                                                |                   |                                                                                                                            |                      | 03,07,11,                              |        | 35  | 1          |

|                                                |                   |                                                                                                                            |                      | 04,08,12,<br>16<br>01,05,09,           |        | 20  | <u> </u>   |

|                                                |                   |                                                                                                                            |                      | 13                                     |        | 15  | 1          |

|                                                |                   |                                                                                                                            |                      | 22<br>19,20,23,<br>24                  |        | 10  |            |

| Chip enable to power-up time 1/                | <sup>t</sup> ELPU |                                                                                                                            | 9,10,11              | ALL                                    | 0      |     | ns         |

| Chip disable to power-<br>down time <u>1</u> / | t <sub>EHPD</sub> |                                                                                                                            | 9,10,11              | ALL                                    |        | 50  | ns         |

| Write cycle time 4/                            | <sup>t</sup> avav | †<br>                                                                                                                      | 9,10,11              | 01,05,09,                              | 45     |     | ns         |

|                                                |                   |                                                                                                                            |                      | 02,06,10,                              | 90     |     | Ì<br>L     |

|                                                |                   |                                                                                                                            |                      | 03,07,11,<br>15                        | 70     |     | Ī          |

|                                                |                   |                                                                                                                            |                      | 04,08,12,<br>16<br>17,18,21,           | 55     |     |            |

|                                                |                   |                                                                                                                            |                      | 22                                     | 35     |     | ļ<br>Ī     |

|                                                |                   | 1                                                                                                                          |                      | 19,20,23,<br> 24                       | 25     | 1   | !          |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002 |

|-----------------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                                    |           | REVISION LEVEL<br>D | SHEET 7    |

DESC FORM 193A JUL 94

**9004708 0003513 446 📟**

| Test                          | Symbol            | Conditions                                                                                                              | Group A   | Device                 | Lim | its | i Unit   |

|-------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|-----|-----|----------|

|                               |                   | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>V <sub>SS</sub> = 0 V, 4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V<br>unless otherwise specified | subgroups | type                   | Min | Max |          |

| Chip enable to end of write   | t <sub>ELWH</sub> | See figure 5                                                                                                            | 9,10,11   | 01,05,09,              | 35  |     | ns       |

|                               |                   |                                                                                                                         | Ì         | 02,06,10,              | 85  |     | Ţ        |

|                               | İ                 |                                                                                                                         |           | 03,07,11,              | 50  |     | †        |

|                               | İ                 |                                                                                                                         |           | 04,08,12,              | 40  |     | †        |

|                               |                   |                                                                                                                         |           | 17,18,21,              | 30  |     | 1        |

|                               |                   |                                                                                                                         | <br>      | 19,20,23,<br> 24       | 20  |     | <u> </u> |

| Address valid to end of write | tavwh             |                                                                                                                         | 9,10,11   | 01,05,09,<br>13        | 35  |     | ns       |

|                               | į                 |                                                                                                                         |           | 02,06,10,              | 85  |     | †        |

|                               |                   |                                                                                                                         |           | 03,07,11,              | 50  |     | †        |

|                               |                   |                                                                                                                         |           | 04,08,12,              | 40  |     | †        |

|                               |                   |                                                                                                                         |           | 17,18,21,              | 30  |     | †        |

|                               |                   | <br>                                                                                                                    | <br>      | 22<br>19,20,23,<br> 24 | 20  |     | †<br>i   |

| Address setup time            | †AVWL             | <br> <br>                                                                                                               | 9,10,11   | ALL                    | 0   |     | ns       |

| rite pulse width 5/           | <sup>t</sup> wLWH |                                                                                                                         | 9,10,11   | 01,05,09,              | 35  |     | ns       |

|                               |                   |                                                                                                                         |           | 02,06,10,              | 55  |     | †        |

|                               |                   |                                                                                                                         |           | 03,07,11,              | 50  |     | †        |

|                               |                   |                                                                                                                         |           | 04,08,12,              | 40  |     | †        |

|                               |                   |                                                                                                                         |           | 16<br>17,18,21,        | 30  |     | †        |

|                               |                   |                                                                                                                         |           | 19,20,23,<br>124       | 20  |     | †        |

| rite recovery time            | t <sub>EHOL</sub> | <b>†</b>                                                                                                                | 9,10,11   | ALL                    | 0   |     | ns       |

See footnotes at end of table.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                     | 5962-87002 |

|------------------------------------------------------------------------------------|-----------|---------------------|------------|

|                                                                                    |           | REVISION LEVEL<br>D | SHEET<br>8 |

DESC FORM 193A JUL 94

# ■ 9004708 0003514 382 **■**

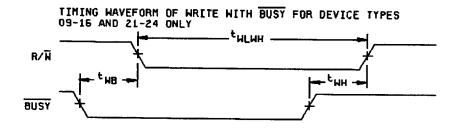

TABLE I. <u>Electrical performance characteristics</u> - Continued. Test Symbol Conditions Group A Device Limits Unit -55°C ≤ T<sub>C</sub> ≤ +125°C V<sub>SS</sub> = 0 V, 4.5 V ≤ V<sub>CC</sub> ≤ 5.5 V unless otherwise specified type subgroups Max Min Data valid to end 9,10,11 02,06,10, 40 ns <sup>t</sup>DVWH of write 03,07,11, 30 01,04,05, 08,09,12, 20 13,16-18, 21,22 19,20,23, 12 Output high Z time 9,10,11 02,06,10, 40 ns <sup>t</sup>ongz 1/ 3/ 03,07,11, 35 15 04,08,12, 30 01,05,09, 20 17,18,21, 15 19,20,23, 10 Data hold time 0 9,10,11 ALL ns <sup>t</sup>wHDX Write enabled to 9,10,11 02,06,10, 40 กร <sup>t</sup>wlqz output in high Z 1/ 3/ 03,07,11, 35 04,08,12, 30 16 01,05,**0**9, 20 13 17,18,21, 15 22 19,20,23, 10 Output active from end of write  $\underline{1}/\underline{3}/$ 9,10,11 <sup>t</sup>whqx All 0 ns Write to BUSY 6/ 9,10,11 09-16, ns <sup>t</sup>wB 21-24 Write to hold after 9,10,11 09-16,21, 20 ns twH 7/ 23,24 15

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                     | 5962-87002 |

|---------------------------------------------------------------------------------------------|-----------|---------------------|------------|

|                                                                                             |           | REVISION LEVEL<br>D | SHEET<br>9 |

DESC FORM 193A JUL 94

**=** 9004708 0003515 219 **=**

| Test                                    | Symbol           | Conditions $-55^{\circ}C \le T_{C} \le +125^{\circ}C$ $ V_{SS} = 0 \text{ V, } 4.5 \text{ V} \le V_{CC} \le 5.5 \text{ V}$ $ V_{SS} = 0 \text{ unless otherwise specified}$ | Group A<br>subgroups | Device          | Limits |          | ⊥ Unit       |

|-----------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|--------|----------|--------------|

|                                         |                  |                                                                                                                                                                             |                      | type            | Min    | Max      |              |

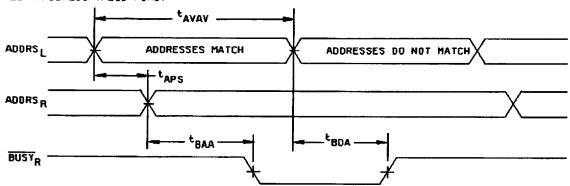

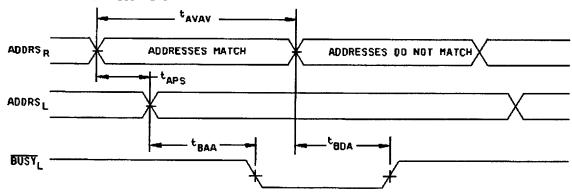

| BUSY access time<br>to address          | <sup>t</sup> BAA | See figure 5                                                                                                                                                                | 9,10,11              | 01,05,<br>17,18 |        | 35       | ns           |

|                                         |                  |                                                                                                                                                                             |                      | 02,03,04,       |        | 45       |              |

|                                         |                  | †                                                                                                                                                                           |                      | 19,20           |        | 25       | <del> </del> |

| BUSY disable time<br>to address         | <sup>t</sup> BDA |                                                                                                                                                                             | 9,10,11              | 01,05           | ļ      | 35       | ns           |

|                                         |                  |                                                                                                                                                                             |                      | 03,04,<br>07,08 |        | 40       | Ī            |

|                                         |                  |                                                                                                                                                                             | İ                    | 17,18<br>19,20  |        | 30       | Ţ            |

| BUSY access time<br>to chip enable      | tBAC             |                                                                                                                                                                             | 9,10,11              | 01,05,          | ļ      | 30       | ns           |

|                                         |                  |                                                                                                                                                                             |                      | 02,06           |        | 45<br>35 | Į            |

|                                         |                  |                                                                                                                                                                             |                      | 03,04,<br>07,08 |        |          | 1            |

|                                         |                  | +                                                                                                                                                                           |                      | 19,20           |        | 20       | <u> </u>     |

| BUSY disable time<br>to chip enable     | <sup>t</sup> BDC |                                                                                                                                                                             | 9,10,11              | 01,05,<br>17,18 | <br>   | 25       | ns           |

|                                         | ļ                |                                                                                                                                                                             |                      | 02,06           |        | 45       | Į            |

|                                         |                  |                                                                                                                                                                             |                      | 03,04,          |        | 30       | ļ            |

| <del></del>                             |                  | †                                                                                                                                                                           |                      | 19,20           |        | 20       |              |

| Write pulse to data<br>delay <u>8</u> / | <sup>t</sup> wDD |                                                                                                                                                                             | 9,10,11              | 01,05,<br>09,13 |        | 70       | ns           |

|                                         |                  |                                                                                                                                                                             |                      | 02,06,<br>10,14 |        | 100      | Ĺ            |

|                                         |                  |                                                                                                                                                                             |                      | 03,07,<br>11,15 |        | 90       | Ĺ            |

|                                         |                  |                                                                                                                                                                             |                      | 04,08,<br>12,16 |        | 80       | j<br>I       |

|                                         | ļ                |                                                                                                                                                                             |                      | 17,18           |        | 60       | Ĺ            |

|                                         | <u></u>          | <u> </u>                                                                                                                                                                    |                      | 19,20           |        | 50       | L            |

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE 5962-87002

REVISION LEVEL SHEET

D 10

DESC FORM 193A JUL 94

**-** 9004708 0003516 155 **-**

STANDARD

# TABLE I. <u>Electrical performance characteristics</u> - Continued.

| Test                                           | Symbol           | Conditions                                                                                                                                                                                              | Group A   | Device<br>type  | Limits   |            | _ Unit    |

|------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|----------|------------|-----------|

|                                                |                  | $   V_{SS} = 0 \text{ V, } 4.5 \text{ V} \leq V_{CC} \leq 5.5 \text{ V} $ $   U_{SS} = 0 \text{ v, } 4.5 \text{ V} \leq V_{CC} \leq 5.5 \text{ V} $ $   U_{SS} = 0 \text{ unless otherwise specified} $ | subgroups |                 | Min      | Max        | <br> <br> |

| Write data valid to read data delay <u>8</u> / | t <sub>DDD</sub> | <br>  See figure 5<br>                                                                                                                                                                                  | 9,10,11   | 01,05,          |          | 45         | ns        |

|                                                |                  |                                                                                                                                                                                                         |           | 02,06,          |          | 90         | Ī         |

|                                                | i                |                                                                                                                                                                                                         | j         | 03,07,          | 1        | 70         | †         |

|                                                | 1                |                                                                                                                                                                                                         | İ         | 11,15           | <u> </u> | 70         | Ĺ         |

|                                                |                  |                                                                                                                                                                                                         |           | 04,08,          |          |            | [         |

|                                                | ļ                |                                                                                                                                                                                                         | !         | 12,16           | ļ        | 55         | Ţ         |

|                                                | <del></del>      | +                                                                                                                                                                                                       |           | 17-20           | -        | 35         |           |

| BUSY disable to valid data 9/                  | t <sub>BDD</sub> |                                                                                                                                                                                                         | 9,10,11   | 01-08,<br>17-20 |          | <u>6</u> / | ns        |

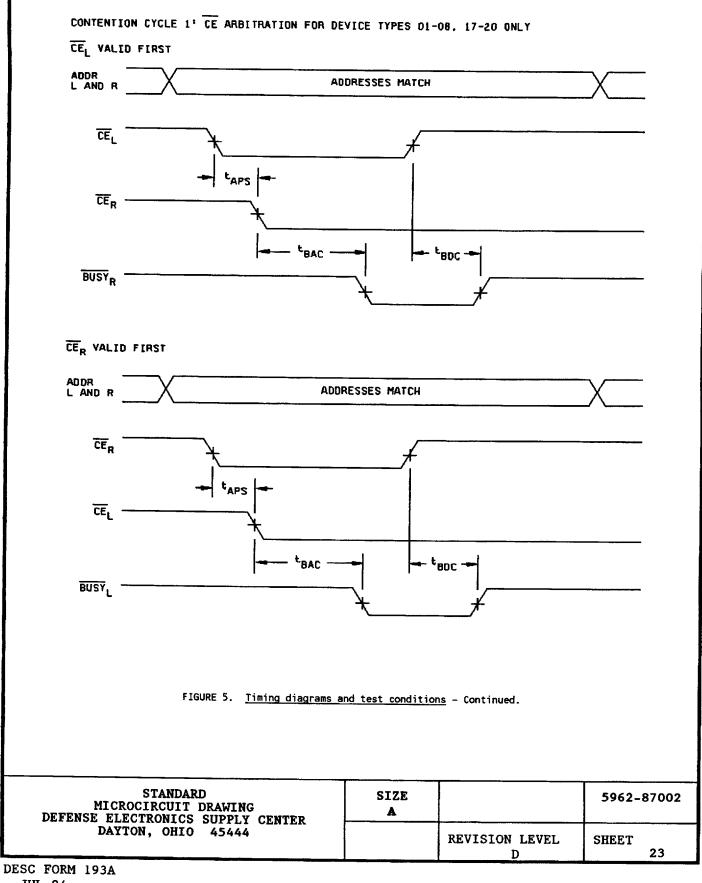

| Arbitration priority setup time 10/            | t<br>APS         | †                                                                                                                                                                                                       | 9,10,11   | 01-08,          | 5        |            | ns        |

This parameter not required to be tested but shall be guaranteed to the limits specified in table I.

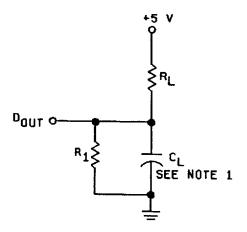

$t_{RC}$  = Read Cycle Time =  $t_{AVAV}$ . Transition is measured  $\pm 500$  mV from low or high impedance voltage with load.  $R_1$  = 1250 ohms,  $c_L$  = 5 picofarads.

4/ For master/slave combination, t<sub>AVAV</sub> = t<sub>BAA</sub> + t<sub>WLWH</sub>.

Specified for OE at high.

For slave device only. To ensure that the write cycle is completed after contention.

To ensure that a write cycle is completed after contention.

Port-to-port delay through RAM cells from writing port to reading port.  $\frac{9}{10}$  is a calculated parameter and is the greater of 0,  $t_{WDD} - t_{WLWH}$  (actual) or  $t_{DDD} - t_{DVWH}$  (actual). To ensure that the earlier of the two ports wins.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>D | SHEET<br>11 |

DESC FORM 193A JUL 94

9004708 0003517 091 📟

JUL 94

🖿 9004708 0003518 T28 🗯

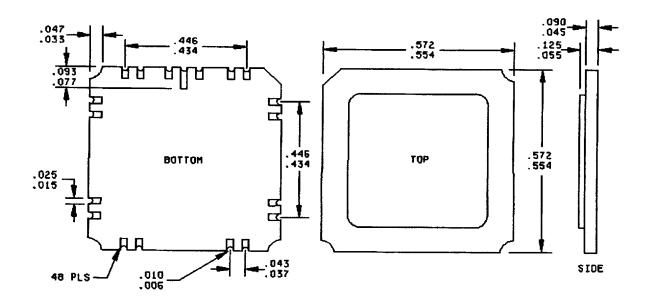

### Case outline U

| Inches | mm   | Inches | mm    |

|--------|------|--------|-------|

| .006   | 0.15 | .055   | 1.40  |

| .010   | 0.25 | .077   | 1.96  |

| .015   | 0.38 | .090   | 2.29  |

| .025   | 0.64 | .093   | 2.36  |

| .033   | 0.84 | .125   | 3.18  |

| .037   | 0.94 | .434   | 11.02 |

| .043   | 1.09 | .446   | 11.33 |

| .045   | 1.14 | .554   | 14.07 |

| .047   | 1.19 | .572   | 15.53 |

#### NOTES:

- Dimensions are in inches.

Metric equivalents are given for general information only.

Unless otherwise specified, tolerance is ±.005 (0.13 mm).

FIGURE 1. Package dimensions - Continued.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>D | SHEET 13   |

DESC FORM 193A JUL 94

9004708 0003519 964 📟

DESC FORM 193A JUL 94

💶 9004708 0003520 **686 📟**

| Device             | 1                        |                   |           | T                 |                   |

|--------------------|--------------------------|-------------------|-----------|-------------------|-------------------|

| !                  |                          |                   | Device    | 1                 |                   |

| types              | ^                        | ll                | types     | ^                 | l l               |

| Case               | Y, Z,                    | T                 | Case      | Y, Z,             | 1                 |

| outlines           | U, and T                 | j x               | outlines  | U, and T          | x                 |

|                    | <u> </u>                 |                   | <u> </u>  |                   | <u> </u>          |

| Terminal<br>number |                          |                   | Terminal  | !                 |                   |

| number             | Terminal                 | symbol            | number    | Terminal          | symbol            |

|                    |                          | 1                 | <u> </u>  | 1                 | 1                 |

| į 1                | CE                       | CEL               | 27        | 1/0 <sub>2R</sub> | I/O <sub>OR</sub> |

| ļ                  | ĺ                        | _                 | į         |                   | l                 |

| 2                  | R/W <sub>L</sub>         | R/W <sub>L</sub>  | 28        | 1/0 <sub>3R</sub> | 1/0 <sub>1R</sub> |

| ! _                |                          | [ <del></del>     |           |                   |                   |

| 3                  | BUSYL                    | BUSY              | 29        | 1/0 <sub>4R</sub> | 1/0 <sub>2R</sub> |

| 4                  | A10L                     | NC                | 30        | 1/0 <sub>5R</sub> | 1/03R             |

| 5                  | ŌĒL                      | i<br>I a          | 31        |                   |                   |

|                    | J-L                      | A <sub>10L</sub>  | 3'        | 1/0 <sub>6R</sub> | 1/0 <sub>4R</sub> |

| 6                  | AOL                      | 0E <sub>L</sub>   | 32        | 1/0 <sub>7R</sub> | 1/0 <sub>5R</sub> |

| 7                  | A <sub>1L</sub>          | AOL               | 33        | A <sub>9R</sub>   | 1/06R             |

| j 8                | A <sub>2</sub> L         | A1L               | 34        | ASR               | 1/0 <sub>7R</sub> |

| 9                  | A <sub>3L</sub>          | A <sub>2</sub> L  | 35        | A7R               | NC R              |

| 10                 | AZI                      | ואלו              | 36        | A <sub>6R</sub>   | A <sub>9R</sub>   |

| 11                 | A5L                      | A <sub>4L</sub>   | 37        | A <sub>5R</sub>   | ASR               |

| 12                 | 761                      | 751               | 38        | A4R               | A7R               |

| 13                 | A7L                      | י מאי             | 39        | A <sub>3R</sub>   | A <sub>6R</sub>   |

| 14                 | ^ <b>2</b> I             | ולף ו             | 40        | A 2B              | A50               |

| 15                 | A <sub>9L</sub>          | 1 <b>^</b> 81     | 41        | ! ^1R             | ^4R               |

| 16                 | A9L<br>I/O <sub>DL</sub> | A <sub>9</sub> L  | 42        | AOR               | A3R               |

| 47                 |                          |                   | ļ <u></u> |                   | i                 |

| 17<br>18           | 1/0 <sub>1L</sub>        | I/O <sub>OL</sub> | 43        | oe <sub>R</sub>   | A <sub>2R</sub>   |

| 10                 | 1/0 <sub>2L</sub>        | I/O1L             | 44        | A <sub>10R</sub>  | A1R               |

| 19                 | 1/0 <sub>3L</sub>        | 1/0 <sub>2L</sub> | 45        | BUSYR             |                   |

| i '' i             | 1/ °3L                   | 1,02L             | 45        | 7                 | A <sub>OR</sub>   |

| 20                 | 1/0 <sub>4L</sub>        | 1/0 <sub>3L</sub> | 46        | R/W <sub>R</sub>  | ŌE <sub>R</sub>   |

| i i                |                          |                   |           | ł .               | R                 |

| 21                 | 1/0 <sub>5L</sub>        | 1/0 <sub>4L</sub> | 47        | CER               | A10R              |

| 22                 | 1/06L                    | 1/0 <sub>5L</sub> | 48        | Vcc               | NC                |

|                    |                          |                   |           | "                 |                   |

| 23                 | 1/0 <sub>7L</sub>        | 1/0 <sub>6L</sub> | 49        |                   | BUSYR             |

| <br>  24           | GND                      |                   | l<br>1 50 | !                 | 0.0               |

| Z <del>-4</del>    | GND                      | 1/0 <sub>7L</sub> | טכ ן      |                   | R∕₩ <sub>R</sub>  |

| 25                 | I/O <sub>OR</sub>        | NC                | l<br>l 51 |                   | CER               |

| 26                 | 1/0 <sub>1R</sub>        | GND               | 52        | i                 | V <sub>CC</sub>   |

|                    | i K                      |                   |           | i                 | CC                |

FIGURE 2. Terminal connections.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>D | SHEET<br>15 |

DESC FORM 193A JUL 94

**■** 9004708 0003521 512 **■**

### Noncontention read/write control

| Left or right port (see note 1) |    |    |                  | Function                                                                         |

|---------------------------------|----|----|------------------|----------------------------------------------------------------------------------|

| R/W                             | CE | ŌĒ | D <sub>0-7</sub> |                                                                                  |

| x                               | н  | x  | Z                | Port disabled and in power-down mode  ISB2 or ISB4                               |

| X                               | H  | х  | 2                | $\overline{CE}_R = \overline{CE}_L = H$ , power-down mode $I_{SB1}$ or $I_{SB3}$ |

| L                               | L  | x  | Data in          | Data on port written into memory 2/                                              |

| Н                               | L  | L  | Data out         | Data in memory output on port 3/                                                 |

| Н                               | L  | н  | Z                | High impedance outputs                                                           |

H = High, L = Low, X = Don't care, Z = High impedance.

## NOTES:

- 1.  $A_{QL} = A_{10L} \neq A_{OR} = A_{10R}$ 2. If BUSY = L, data is not written. 3. If BUSY = L, data may not be valid. See  $t_{WDD}$  and  $t_{DDD}$  timing.

FIGURE 3. Truth tables.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-87002  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>16 |

DESC FORM 193A JUL 94

9004708 0003522 459

### Bus arbitration (see notes)

| Left port |                                      |         | Right port                           | ort Fla     |         |                                  |

|-----------|--------------------------------------|---------|--------------------------------------|-------------|---------|----------------------------------|

| CEL       | ≠ A <sub>OL</sub> - A <sub>1OL</sub> | CER     | ≠ A <sub>OR</sub> - A <sub>1OR</sub> | BUSY        | BUSYR   | Function                         |

| н         | x                                    | н       | x                                    | н           | Н       | No contention                    |

| L         | Any                                  | н       | x                                    | н           | н       | No contention                    |

| н         | x                                    | L       | Any                                  | н           | н       | No contention                    |

| L         | ≠ A <sub>OR</sub> - A <sub>10R</sub> | L       | ≠ A <sub>OL</sub> - A <sub>1OL</sub> | <br>  H<br> | н       | No contention                    |

| Addre     | ss arbitration with                  | CE Low  | before address mate                  | ch          |         |                                  |

| L         | LV5R                                 | L       | LV5R                                 | н           | L       | Left-port wins                   |

| L         | RV5L                                 | L       | RV5L                                 | L           | Н       | Right-port wins                  |

| L         | Same                                 | L       | Same                                 | н           | L       | Arbitration resolved             |

| L         | Same                                 | L       | Same                                 | L           | н       | Arbitration resolved             |

| CE ar     | bitration with addre                 | ess mat | ch before CE                         | I           | 1       |                                  |

| LL5R      | = A <sub>OR</sub> - A <sub>1OR</sub> | LL5R    | = A <sub>OL</sub> - A <sub>1OL</sub> | н           | <br>  L | Left-port wins                   |

| RL5L      | = A <sub>OR</sub> - A <sub>1OR</sub> | RL5L    | = A <sub>OL</sub> - A <sub>10L</sub> | L           | н       | Right-port wins                  |

| LW5R      | = A <sub>OR</sub> - A <sub>1OR</sub> | LW5R    | = A <sub>OL</sub> - A <sub>1OL</sub> | н           | L       | Arbitration resolved             |

| LW5R      | = A <sub>OR</sub> - A <sub>1OR</sub> | LW5R    | = A <sub>OL</sub> - A <sub>1OL</sub> | L           | <br>  H | <br>  Arbitration resolved  <br> |

## NOTES:

- X = Don't care, L = Low, H = High.

LV5R = Left address valid ≥ 5 ns before right address.

- 3. RV5L = Right address valid  $\geq$  5 ns before left address.

- Same = Left and right addresses match within 5 ns of each other.

LL5R = Left CE = Low ≥ 5 ns before right CE.

RL5L = Right CE = Low ≥ 5 ns before left CE.

- 7. LW5R = Left and right CE = Low within 5 ns of each other.

## FIGURE 3. <u>Truth tables</u> - Continued.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>D | SHEET 17   |

DESC FORM 193A JUL 94

**9**004708 0003523 395

NOTE: For device types 01-08, 17-20: BUSY is open drain and requires pull-up resistor. For device types 09-16, 21-24: BUSY is input.

Pin names

| Left port                            | Right port                           | Names             |

|--------------------------------------|--------------------------------------|-------------------|

| CE <sub>L</sub>                      | CE <sub>R</sub>                      | Chip enable       |

| R/W <sub>L</sub>                     | R∕W <sub>R</sub>                     | Read/write enable |

| <br>  <del>OE</del> L                | ŌE <sub>R</sub>                      | Output enable     |

| BUSY                                 | BUSŸR                                | Busy flag         |

| A <sub>OL</sub> - A <sub>1OL</sub>   | A <sub>OR</sub> - A <sub>1OR</sub>   | Address           |

| 1/0 <sub>0L</sub> -1/0 <sub>7L</sub> | 1/0 <sub>OR</sub> -1/0 <sub>7R</sub> | Data input/output |

|                                      | V <sub>CC</sub>                      | Power             |

|                                      | GND                                  | Ground            |

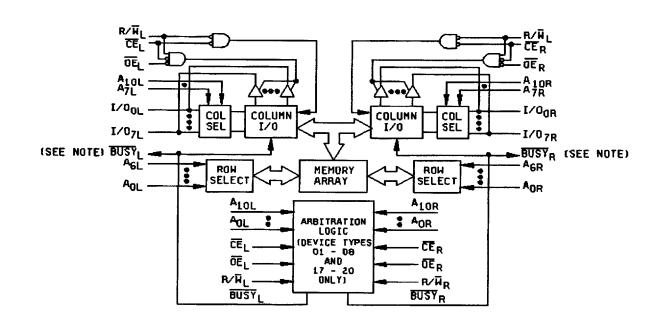

FIGURE 4. Functional block diagram.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>D | SHEET<br>18 |

DESC FORM 193A JUL 94

🖿 9004708 0003524 22l 📟

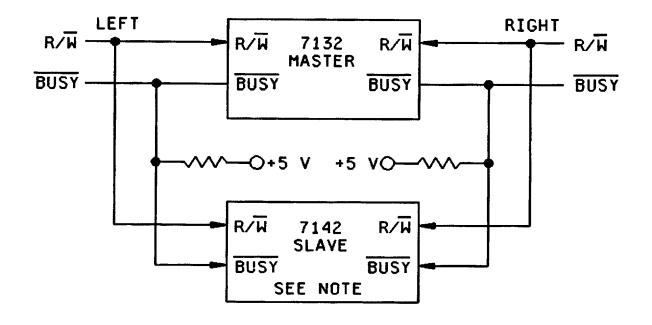

NOTE: No arbitration in 7142 (slave). BUSY-in inhibits write in 7142 (slave).

FIGURE 4. <u>Functional block diagram</u> - Continued.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>D | SHEET<br>19 |

DESC FORM 193A JUL 94

**9004708 0003525 168 📟**

**9**004708 0003526 0T4 🗪

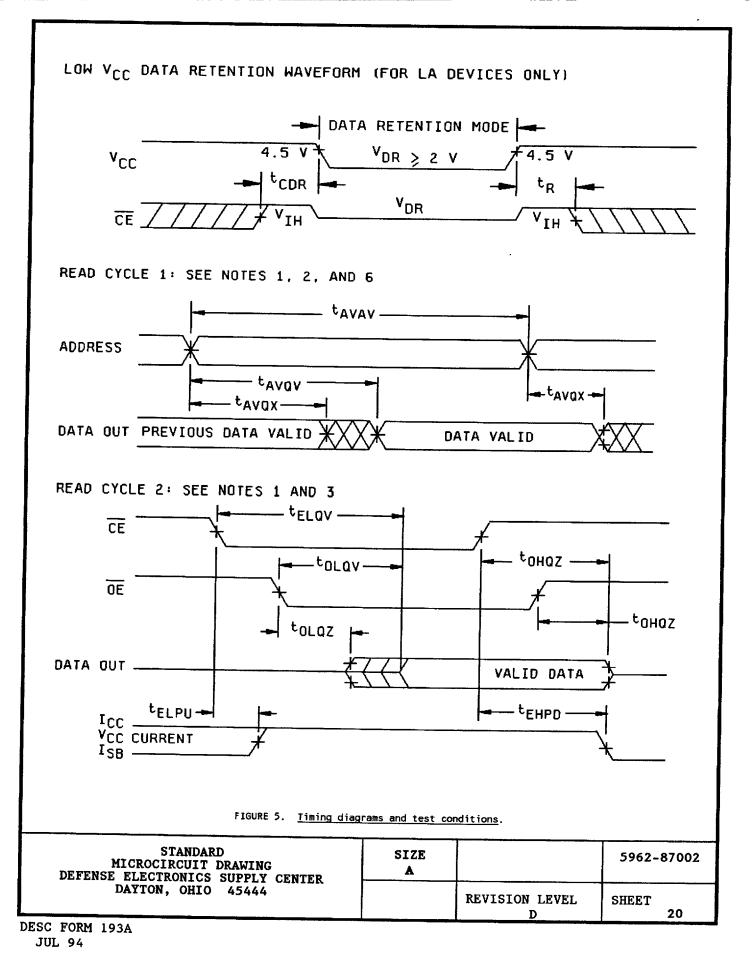

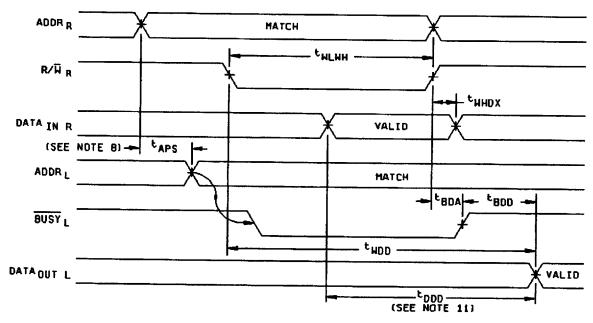

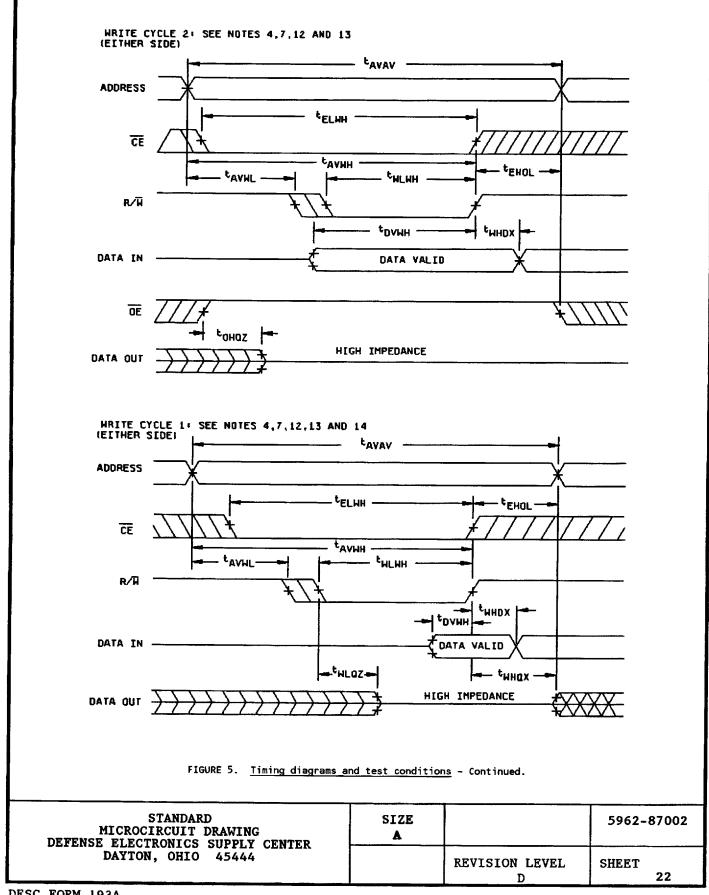

FIGURE 5. <u>Timing diagrams and test conditions</u> - Continued.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-87002 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 21   |

DESC FORM 193A JUL 94

■ 9004708 0003527 T30 ■

DESC FORM 193A JUL 94

**9**004708 0003528 977 🗯

JUL 94

9004708 0003529 803 📟

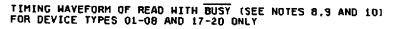

# CONTENTION CYCLE 2: ADDRESS VALID ARBITRATION FOR DEVICE TYPES 01-8 AND 17-20 SEE NOTE 5

LEFT ADDRESS VALID FIRST:

RIGHT ADDRESS VALID FIRST:

#### NOTES:

- $R/\overline{W}$  is high for read cycles.

- Device is continuously enabled,  $\overline{CE} = V_{IL}$ .

Addresses valid prior to or coincident with  $\overline{CE}$  transition low.

If the  $\overline{CE}$  low transition occurs simultaneously with or after the  $R/\overline{W}$  low transition, the outputs remain in the high impedance state.

- 6.

- CEL = CER = VIL.

OE = VIL.

R/W = VIH during address transition.

To ensure that the earlier of the two ports wins. 8.

- Write cycle parameters should be adhered to in order to ensure proper writing.

- 10. Device is continuously enabled for both ports.

- OE at low for the reading port.

- 12. A write occurs during the overlap ( $t_{ELWH}$  or  $t_{WLWH}$ ) of a low  $\overline{CE}$  and a low  $R/\overline{W}$ .

- $t_{EHOL}$  is measured from the earlier of  $\overline{\text{CE}}$  or  $R/\overline{W}$  going high to the end of the write cycle.

- 14. If  $\overline{OE}$  is low during a R/W controlled write cycle, the write pulse width must be the larger of twelve or (twelve to the larger)  $t_{\text{DVWH}}$ ) to allow the I/O drivers to turn off and data to be placed on the bus for the required  $t_{\text{DVWH}}$ . If  $\overline{\text{OE}}$  is high during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified t<sub>WLWH</sub>.

15. During this period, the I/O pins are in the output state and input signals must not be applied.

FIGURE 5. <u>Timing diagrams and test conditions</u> - Continued.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-87002 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>D | SHEET 24   |

DESC FORM 193A JUL 94

## 9004708 0003530 525

### NOTES:

- Includes jig and probe capacitance.

See output load legend.

OUTPUT LOAD SEE NOTE 2

#### Output load legend

| Row | Devices/conditions                                                                       | cL     | RL    | R <sub>1</sub> |

|-----|------------------------------------------------------------------------------------------|--------|-------|----------------|

| 1   | 02-04, 06-08, 10-12, and 14-16;<br>for all ac parameters except as<br>indicated in row 3 | 100 pF | 1250Ω | 775Ω           |

| 2   | 01, 05, 09, 13, and 17-24; for all ac parameters except as indicated in row 3            | 30 pF  | 1250Ω | 775Ω           |