# ·WYUNDAI

# HY524800 Series

512K x 8-bit CMOS DRAM

#### DESCRIPTION

The HY524800 is the new generation and fast dynamic RAM organized 524,288 x 8-bits. The HY524800 utilizes Hyundai's CMOS silicon gate process technology as well as advanced circuit techniques to provide wide operating margins to the users. Multiplexed address inputs permit the HY524800 to be packaged in a 350 mil 28 pin plastic SOJ.

The package size provides high system bit densities and is compatible with widely available automated-test equipments. System oriented-feature includes single power supply of 5V± 10% tolerence and direct interfacing capability with high performance logic families such as Schottky TTL.

# **FEATURES**

Low power dissipation Max. CMOS standby 5.5mW Max. TTL standby 11.0mW Max. operating

| Speed | Power   |

|-------|---------|

| 70    | 742.5mW |

| 80    | 632.5mW |

- Single power supply of 5V± 10%

- · TTL compatible inputs and outputs

- · Fast access time

| Speed | TRAC | tCAC | tPC  |

|-------|------|------|------|

| 70    | 70ns | 20ns | 45ns |

| 80    | 80ns | 20ns | 50ns |

- · Fast page mode operation

- 350 mil 28 pin SOJ

- · Read-Modify-Write capability

- CAS-before-RAS, RAS-only refresh

- 1024 refresh cycles / 16ms

### PIN CONNECTION

| VCC 0 10<br>D000 2<br>D010 2<br>D010 5<br>D020 4<br>D030 5<br>NC0 5<br>WE 0 7<br>RASO 8<br>A90 10<br>A10 11<br>A20 12<br>A30 13<br>VCC 14 | SQJ | 28<br>27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16<br>15 | DVSS<br>DDOO<br>DDOO<br>DDOO<br>DDOO<br>DDOO<br>DDOO<br>DDOO |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------|--------------------------------------------------------------|

|                                                                                                                                           |     |                                                                                  |                                                              |

#### PIN DESCRIPTION

|         | 28 F 25 48 W          |

|---------|-----------------------|

| RAS     | Row Address Strobe    |

| CAS     | Column Address Strobe |

| WE      | Write Enable          |

| ŌĒ      | Output Enable         |

| A0-A9*  | Address Input         |

| DQ0-DQ7 | Data Input/Output     |

| Vcc     | Power (+ 5V)          |

| Vss     | Ground                |

<sup>\*</sup>A9 is applied to Row address input only.

This document is a general product description and is subject to change without notice. Hyundai electronics does not assume any responsibility for use of circuits described. No patent licences are implied.

1AC03-20-MAY94

# **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL    | PARAMETER                          | RATING      | UNIT    |

|-----------|------------------------------------|-------------|---------|

| TA        | Ambient Temperature                | 0 to 70     | ·c      |

| TSTG      | Storage Temperature                | -55 to 150  | .c      |

| VIN, VOUT | Voltage on Any Pin Relative to Vss | -1.0 to 7.0 | V       |

| Vcc       | Voltage on Vcc Relative to Vss     | -1.0 to 7.0 | V       |

| los       | Short Circuit Output Current       | 50          | mA      |

| Po        | Power Dissipation                  | 1.0         |         |

| TSOLDER   | Soldering Temperature• Time        | 260• 10     | 'C• sec |

NOTE: Operation at or above Absolute Maximum Ratings can adversely affect device reliability.

# RECOMMENDED DC OPERATING CONDITIONS

(TA= 0°C to 70°C)

| SYMBOL | PARAMETER          | MIN. | TYP. | MAX.     | UNIT |

|--------|--------------------|------|------|----------|------|

| Vcc    | Supply Voltage     | 4.5  | 5.0  | 5.5      | V    |

| VIH    | Input High Voltage | 2.4  | -    | Vcc+ 1.0 | ٧    |

| VIL    | Input Low Voltage  | -1.0 | -    | 0.8      | ٧    |

NOTE: All voltages are referenced to Vss.

# DC CHARACTERISTICS

(TA= 0°C to 70°C, VCC= 5V± 10%, VsS= 0V, unless otherwise noted.)

| SYMBOL | PARAMETER                                        | TEST CONDITIONS                                       | SPEED    | MIN. | MAX.       | UNIT | NOTE  |

|--------|--------------------------------------------------|-------------------------------------------------------|----------|------|------------|------|-------|

| ILI    | Input Leakage Current<br>(Any Input Pins)        | Vss≤ Vin≤ 6.0V,<br>All other pins not under test= Vss |          | -10  | 10         | μА   |       |

| LO     | Output Leakage Current<br>(High Impedance State) | Vss≤ Vout≤ 5.5V,<br>RAS & CAS at ViH                  |          | -10  | 10         | μА   |       |

| ICC1   | Vcc Supply Current,<br>Operating                 | tRC= tRC (min.)                                       | 70<br>80 | -    | 135<br>115 | mA   | 1,2,3 |

| ICC2   | Vcc Supply Current,<br>TTL Standby               | RAS & CAS at VIH,                                     |          | -    | 2          | mA   |       |

| ICC3   | Vcc Supply Current,<br>RAS-only refresh          | tRC= tRC (min.)                                       | 70<br>80 | -    | 135<br>115 | mA   | 1,3   |

| ICC4   | Vcc Supply Current,<br>Fast Page mode            | tPC= tPC (min.)                                       | 70<br>80 | -    | 65<br>55   | mA   | 1,2,3 |

| ICC5   | Vcc Supply Current,<br>CMOS Standby              | RAS & CAS≤ Vcc-0.2V                                   |          | -    | 1          | mA   |       |

| ICC6   | Vcc Supply Current,<br>CAS-before-RAS refresh    | tRC= tRC (min.)                                       | 70<br>80 | -    | 135<br>115 | mA   | 1,3   |

| VOL    | Output Low Voltage                               | IOL= 4.2mA                                            |          | -    | 0.4        | ٧    |       |

| Voн    | Output High Voltage                              | IOH= -5mA                                             |          | 2.4  | •          | ٧    |       |

#### NOTE:

- ICC1, ICC3, ICC4, and ICC6 depend on cycle rate.

ICC1 and ICC4 depend on output loading. Specified values are obtained with the output open.

- 3. It depends on user whether column address is changed or not at least once while RAS= VIL and CAS= VIH.

# **AC CHARACTERISTICS**

(TA= 0°C to 70°C, Vcc= 5V± 10%, Vss= 0V, unless otherwise noted.) NOTE: 1, 2, 3

|    | OVMOC  | PARAMETER                                   |     |            | 4800J | ~    |      |        |

|----|--------|---------------------------------------------|-----|------------|-------|------|------|--------|

| #  | SYMBOL | PAHAMETER                                   |     | 70<br>MAX. |       | MAX. | UNIT | NOTE   |

| 1  | tRC    | Random Read or Write Cycle Time             |     | 128K       | 150   | 128K | ns   | 1,2    |

| 2  | tRWC   | Read-Modify-Write Cycle Time                | 180 | 128K       | 205   | 128K | ns   | 1,2,10 |

| 3  | tPC    | Fast Page Mode Cycle Time                   | 45  | -          | 50    | -    | ns   | 2      |

| 4  | tPRWC  | Fast Page Mode Read-Modify-Write            | 90  | -          | 100   | -    | ns   | 2,12   |

|    |        | Cycle Time                                  |     | <u> </u>   |       |      |      |        |

| 5  | trac   | Access Time from FAS                        |     | 70         |       | 80   | ns   | 3,4,5  |

| 6  | tCAC   | Access Time from CAS                        | -   | 25         | -     | 20   | ns   | 3,4,5  |

| 7  | taa    | Access Time from Column Address             | -   | 35         | -     | 40   | ns   | 4,5    |

| 8  | tCPA   | Access Time from CAS Precharge              |     | -          | 40    | _    | 45   | ns5    |

| 9  | tcLZ   | CAS to Output Low Impedance                 | 0   | -          | 0     | -    | ns   |        |

| 10 | tOFF   | Output Buffer Turn-off Delay                | 0   | 15         | 0     | 15   | ns   | 7      |

| 11 | tτ     | Transition Time (Rise and Fall)             | 3   | 50         | 3     | 50   | ns   |        |

| 12 | tRP    | RAS Precharge Time                          | 50  | -          | 60    | -    | ns   |        |

| 13 | tras   | RAS Pulse Width                             | 70  | 16K        | 80    | 16K  | ns   | 1,2    |

| 14 | trasp  | RAS Pulse Width (Fast Page Mode)            | 120 | 16K        | 135   | 16K  | ns   | 1,2,10 |

| 15 | trsh   | RAS Hold Time                               | 20  | -          | 20    | -    | ns   |        |

| 16 | tcsh   | CAS Hold Time                               | 70  | -          | 80    |      | ns   |        |

| 17 | tCAS   | CAS Pulse Width                             | 20  | 10K        | 8     | 10K  | ns   |        |

| 18 | tRCD   | RAS to CAS Delay                            | 20  | 50         | 20    | 60   | ns   | 3      |

| 19 | tRAD   | RAS to Column Address Delay Time            | 15  | -          | 15    | •    | ns   | 6      |

| 20 | tCRP   | CAS to RAS Precharge Time                   | 10  | ,          | 10    | ,    | ns   |        |

| 21 | tCP    | CAS Precharge Time                          | 10  | 1          | 10    | •    | ns   | 9      |

| 22 | tasr   | Row Address Set-up Time                     | 0   | -          | 0     | -    | ns   |        |

| 23 | trah   | Row Address Hold Time                       | 10  | -          | 10    | -    | ns   |        |

| 24 | tasc   | Column Address Set-up Time                  | 0   | -          | 0     | - 1  | ns   |        |

| 25 | tCAH   | Column Address Hold Time                    | 15  | ·-         | 15    | -    | ns   |        |

| 26 | tAR    | Column Address Hold Time from RAS           | 50  | -          | 55    | -    | ns   |        |

| 27 | tral   | Column Address to RAS Lead Time             | 35  | -          | 40    | -    | ns   |        |

| 28 | tRCS   | Read Command Set-up Time                    | 0   | -          | 0     | -    | ns   |        |

| 29 | tRCH   | Read Command Hold Time<br>Referenced to CAS | 0   | -          | 0     | -    | ns   |        |

| 30 | trrh   | Read Command Hold Time<br>Referenced to RAS | 0   | -          | 0     | -    | ns   |        |

| 31 | twch   | Write Command Hold Time                     | 15  | -          | 15    | -    | กร   |        |

| 32 | twcn   | Write Command Hold Time from RAS            | 55  | -          | 60    | -    | ns   |        |

| 33 | tWP    | Write Command Pulse Width                   | 15  | -          | 15    | -    | ns   |        |

| 34 | trw.   | Write Command to RAS Lead Time              | 20  | - 1        | 20    | -    | ns   |        |

| 35 | tcwL   | Write Command to CAS Lead Time              | 20  | -          | 20    |      | ns   |        |

| 36 | tDS    | Data-In Set-up Time                         | 0   | -          | 0     |      | ns   | 8      |

| 37 | tDH    | Data-In Hold Time                           | 15  |            | 15    | -    | ns   | 8      |

| 38 | tDHR   | Data-In Hold Time Referenced to RAS         | 55  | -          | 60    | -    | ns   |        |

| 39 | tREF   | Refresh Period (1024 cycles)                | -   | 16         | -     | 16   | ms   |        |

| 40 | twcs   | Write Command Set-up Time                   | 0   | - 1        | 0     | 1    | ns   |        |

# AC CHARACTERISTICS

(continued)

| /D<br>/D<br>R | PARAMETER  CAS to WE Delay Time  RAS to WE Delay Time  Column Address to WE Delay Time  CAS Set-up Time (CBR Cycle)  CAS Hold Time (CBR Cycle) | MIN.<br>45<br>95<br>60<br>10                                                   | 70<br>  MAX.<br>  -                                                                | MIN.<br>50<br>110<br>70                                                                 | MAX.                                                                                        | ns<br>ns<br>ns                                                                             | 10<br>10<br>10                                                                                          |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| /D<br>/D<br>R | RAS to WE Delay Time Column Address to WE Delay Time CAS Set-up Time (CBR Cycle) CAS Hold Time (CBR Cycle)                                     | 45<br>95<br>60<br>10                                                           | -                                                                                  | 50<br>110<br>70                                                                         | -                                                                                           | ns                                                                                         | 10                                                                                                      |

| /D<br>/D<br>R | RAS to WE Delay Time Column Address to WE Delay Time CAS Set-up Time (CBR Cycle) CAS Hold Time (CBR Cycle)                                     | 95<br>60<br>10                                                                 | <del> </del>                                                                       | 110<br>70                                                                               | -                                                                                           | ns                                                                                         | 10                                                                                                      |

| /D<br>R<br>R  | Column Address to WE Delay Time CAS Set-up Time (CBR Cycle) CAS Hold Time (CBR Cycle)                                                          | 60<br>10                                                                       | <del> </del>                                                                       | 70                                                                                      | -                                                                                           |                                                                                            | 10                                                                                                      |

| R             | CAS Set-up Time (CBR Cycle) CAS Hold Time (CBR Cycle)                                                                                          | 60<br>10                                                                       | <del> </del>                                                                       | 70                                                                                      | -                                                                                           |                                                                                            |                                                                                                         |

| R             | CAS Set-up Time (CBR Cycle) CAS Hold Time (CBR Cycle)                                                                                          | 10                                                                             | <del> </del>                                                                       |                                                                                         | <del>                                     </del>                                            | ( IIS                                                                                      | 10                                                                                                      |

| R             | CAS Hold Time (CBR Cycle)                                                                                                                      |                                                                                |                                                                                    | 10                                                                                      |                                                                                             | ·                                                                                          |                                                                                                         |

|               | ario riola fillo (ODITO)Cle)                                                                                                                   |                                                                                |                                                                                    |                                                                                         |                                                                                             | ns                                                                                         | 9                                                                                                       |

| C I           | RAS to CAS Precharge Time                                                                                                                      | 15                                                                             |                                                                                    | 20                                                                                      | -                                                                                           | ns                                                                                         |                                                                                                         |

| <del>  </del> | TAG to CAG Frecharge Time                                                                                                                      |                                                                                | -                                                                                  | 0                                                                                       | -                                                                                           | ns                                                                                         |                                                                                                         |

|               | OE Command Hold Time                                                                                                                           | 15                                                                             | -                                                                                  | 15                                                                                      |                                                                                             | ns                                                                                         |                                                                                                         |

| Н             | RAS Hold Time Reference to OE                                                                                                                  | 10                                                                             |                                                                                    | 10                                                                                      | <del>                                     </del>                                            | +                                                                                          |                                                                                                         |

| A   i         | OE Access Time                                                                                                                                 |                                                                                |                                                                                    |                                                                                         |                                                                                             | ns                                                                                         |                                                                                                         |

|               | OE to Data Delay                                                                                                                               |                                                                                | 20                                                                                 |                                                                                         | 20                                                                                          | ns                                                                                         | 4,5                                                                                                     |

| 2 (           | Output Dotte T OF D                                                                                                                            | 15                                                                             |                                                                                    | 15                                                                                      | - 1                                                                                         | ns                                                                                         |                                                                                                         |

|               | Output Buffer furn Off Delay Time from OE                                                                                                      | -                                                                              | 15                                                                                 | -                                                                                       | 15                                                                                          | ns                                                                                         | 7                                                                                                       |

| P   1         | WE to RAS Precharge Time (CBR Cycle)                                                                                                           | 5                                                                              |                                                                                    | 5                                                                                       |                                                                                             | <del></del>                                                                                | 9                                                                                                       |

|               | WE to RAS Hold Time (CBR Cycle)                                                                                                                |                                                                                |                                                                                    |                                                                                         |                                                                                             |                                                                                            | 9                                                                                                       |

| 2             |                                                                                                                                                | Output Buffer Turn Off Delay Time from OE WE to RAS Precharge Time (CBR Cycle) | Output Buffer Turn Off Delay Time from OE  WE to RAS Precharge Time (CBR Cycle)  5 | Output Buffer Turn Off Delay Time from OE - 15 WE to RAS Precharge Time (CBR Cycle) 5 - | Output Buffer Turn Off Delay Time from OE - 15 - WE to RAS Precharge Time (CBR Cycle) 5 - 5 | Output Buffer Turn Off Delay Time from OE - 15 - 15 WE to RAS Precharge Time (CBR Cycle) 5 | Output Buffer Turn Off Delay Time from OE - 15 - 15 ns  WE to RAS Precharge Time (CBR Cycle) 5 - 5 - ns |

NOTE:

- 1. 1024 refreshes are required every 16ms. A burst of eight consecutive refreshes are allowed to keep tras= 16µs average. A maximum of 128µs between refreshes is allowed, however 16ms retention must be

- 2. All AC timings assume tr(max.)= 5ns. If the actual tr is greater than tr(max.), then the cycle times need to be greater than that specified by the amount each transition exceeds tr(max.). HY524800 will support a tr up to 50ns. The transition time is defined between the VIH and VIL. All timings are referenced to a VIL or

- 3. tRCD(max.) is specified as a reference point only. If tRCD> tRCD(max), then this parameter increased by the amount tRCD exceeds tRCD(max.)

- 4. tRAC, tCAC, tAA and tOEA must be satisfied to guarantee access. Please check that all parameters are met for your application.

- 5. Access assumes a load equivalent to 100pF.

- 6. trad is specified as a reference point only. If trad> trac-taa, then the access is increased by the difference.

- 7. This parameter defines the time at which the output achieves the open circuit and is not referenced to the output voltage levels.

- 8. Data in set-up and holds are measured from the later of falling signal CAS or WE.

- 9. tcp, tcsp, twpp, twph all need to be valid for CBR users.

- 10. A 5ns delta is used between data reaching high impedance and having valid data in for these numbers.

# CAPACITANCE

EVIL 100/ Vice- OV f- 1Mile unless athenuise nated \

|        | VCC= 5V± 10%, Vss= 0V, f= 1MHz, unless otherwise n | TYP. | MAX. | UNIT     |

|--------|----------------------------------------------------|------|------|----------|

| SYMBOL | PARAMETER                                          | -    | 5    | pF       |

| CIN1   | Input Capacitance (A0-A9, D)                       |      | 5    | pF       |

|        | Input Capacitance (RAS, CAS, WE, OE)               |      | R    | ρF       |

| COUT   | Output Capacitance (Q)                             |      | . ب  | <u> </u> |

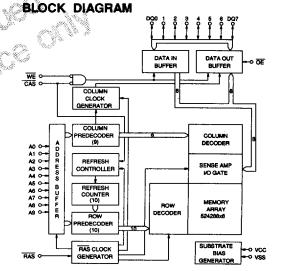

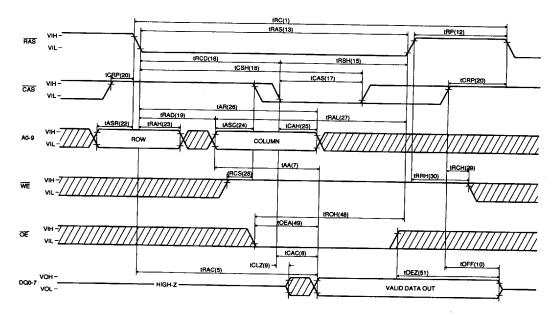

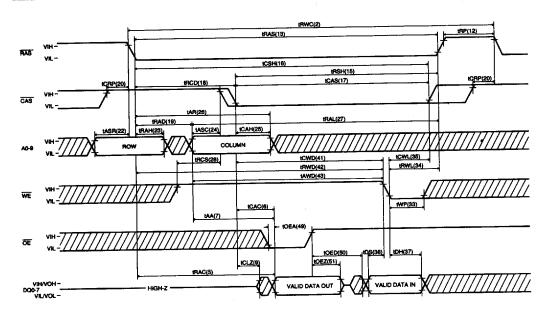

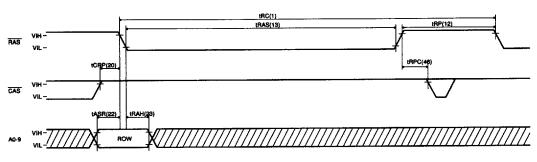

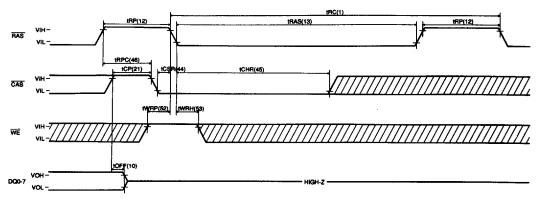

# TIMING DIAGRAM

## READ CYCLE

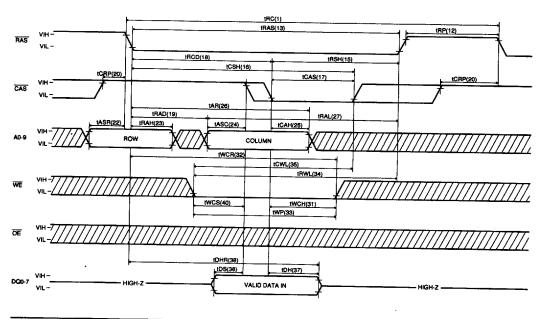

## EARLY WRITE CYCLE

# WRITE CYCLE (OE CONTROLLED WRITE)

# READ-MODIFY-WRITE CYCLE

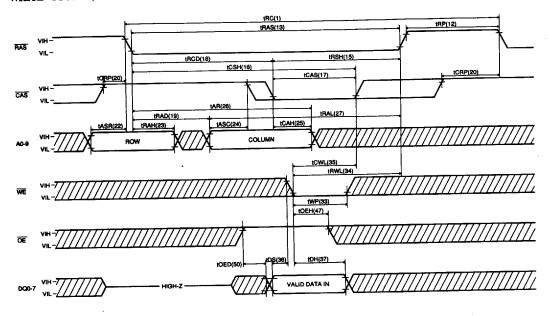

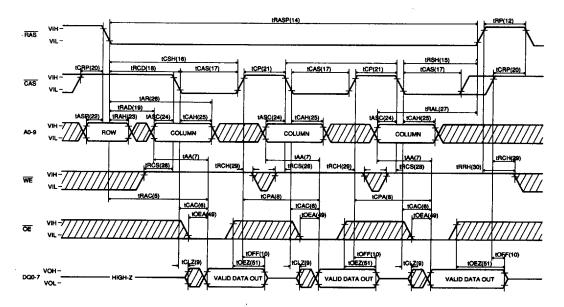

#### FAST PAGE MODE READ CYCLE

#### FAST PAGE MODE EARLY WRITE CYCLE

🕶 4675088 0002620 7TT 🔤

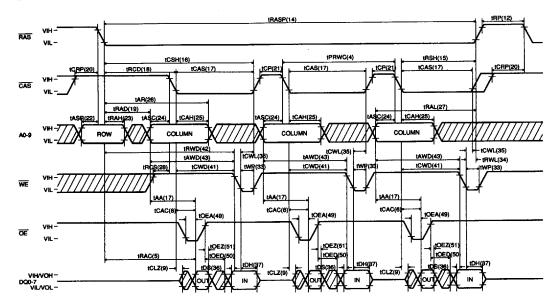

# FAST PAGE MODE READ-MODIFY-WRITE CYCLE

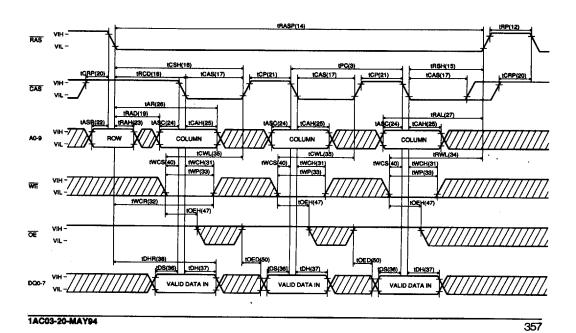

#### RAS-ONLY REFRESH CYCLE

NOTE : OE and WE = "H" or "L"

# CAS-BEFORE-RAS REFRESH CYCLE

NOTE : A0-9 and OE = "H" or "L"

# **DEVICE OPERATION**

#### POWER ON, INITIALIZATION, POWER OFF

After Vcc stabilizes, a pause of at least 500 microseconds is required before initialization begin. During this interval, RAS must be inactive(ViH). A minimum of 8 cycles are required to initialized the device, these must be either RAS-only or CAS-before-RAS refresh cycles, whose tRP must be greater than 70ns. After the initialization cycles, the device is ready for normal-use.

#### PAGE MODE OPERATION

The standard page mode for CAS-before-RAS and RAS-only refresh, early and late-write, read and Read-Modity-Write cycles are supported.

#### ADDRESS CONTROL

The row address is trapped with the falling edge of RAS, which is common for all modes of operation. This selects the word line to be used during the RAS cycle. The W/L selected cannot be changed without RAS going inactive. The column address(A0-A8) is trapped with the falling edge of CAS, for both the Read and Write operations. Each falling CAS allows a new Read or Write operation to occur on a selected new bit address on the same W/L. CAS cycles may continue with new random addresses trapped each time CAS falls, up to the limit of the RAS active time-thas. The CAS pulse must rise past the VIH value and remain at a high level for a specified time. Only one Write operation can occur while CAS is low. The device's access is impacted by active RAS, active CAS, active OE, as well as valid address and inactive CAS. All conditions must be met in order to have a valid access. Therefore the set-up time for column address may impact the device's access.

#### READ/WRITE CONTROL

The state of the WE pin at CAS falling time determines the type of cycle the device will start. If WE is low when CAS falls, an early write operation is initiated. Because the device knows that a write operation has been initiated, the off-chip drivers will remain in high impedance for the entire CAS cycle and only allows one write operation for each CAS cycle. If WE is high when CAS falls, a Read operation is performed, and the OE pin will control the OCD impedance. The OE pin is independent of CAS, but does have an access requirement. CAS and WE must not change state until data out is read. If WE does fall while CAS is still low, a Read-Modify-Write or Late-Write cycle will be initiated. In this case, the OE pin will control the OCD impedance. When WE falls, it will trap Data-In information for the Write operation. The OE pin must be used for this cycle to guarantee correct "hand shaking" on the DQ pin for Data-Out and Data-In control. Until Data-Out is read and Data-In is set up, Write must not go low. In this case, the Data In will be written on the same Column address which was trapped when CAS fall. CAS must remain low for a specified time after WE is low, and can not start another cycle until after a traww cycle time has passed. The customer can mix the above cycle types as long as all other timings are obeyed.

#### DATA IN CONTROL

Input data are is trapped when the write cycle is initiated. For an early write operation, CAS will be the trapping signal. During a late write or Read-Modify-Write operation, WE will be the trapping signal.

1AC03-20-MAY94

#### IMPEDANCE CONTROL

The following signals are used to control the impedance of the OCDs; OE pin, WE pin, RAS pin, and CAS pin. All pins must be in there proper state in order to drive Data Out. With the OE pin high, the OCDs are turned off and will maintain hi-impedance. Thus Data Out can be turned "off" by returning the OE pin to hi-level. OE pin going to low will allow the output driver to be turned "on", but only if the device is doing a Read operation (WE pin high) and both the CAS and RAS pins are still low. If CAS never falls(RAS-Only Refresh), the device will also maintain hi-impedance. Data-Out can be turned "off" by returning the CAS pin to hi-level. If WE is low when CAS falls, the device will maintain hi-impedance. Data-Out will not be turned "off" by returning the RAS pin to a hi-level, but when RAS falls to start another cycle, the device will return to a hi-impedance even if CAS had remained low. Thus Hidden-Refresh is not supported.

#### REFRESH CYCLE

Because 512K x 8 bits are a dynamic memory cells (data is represented by charge stored on a capacitor), each cell must be refreshed periodically to replace leakage. Refreshing the entire chip requires sequence through all 1024 row addresses. This must be done within each 16ms refresh interval. Two refresh methods are provided. A RAS-Only Refresh used a RAS select with CAS high. The selected row address (A0-A9) must be provided to the device. A CAS-Before-RAS Refresh capability is also provided. If CAS is low, RAS is pulled low to initiate the Refresh, an on-chip Row Address Counter(RAC) will provide the next row address for the Refresh. No external addresses are used.

#### NOTE:

- 1.Refresh occurs whenever RAS is selected; eg, read or write.

- 2. If both CAS & WE are low when RAS becomes active(low), the device will be forced into a test mode. Since some test modes may cause physical damage to the device, the above sequence is not allowed. Test modes are cleared by RAS-only and CAS-before-RAS refresh cycles.

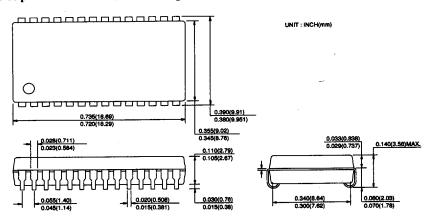

## PACKAGE INFORMATION

350 mil 28 pin Small Outline J-form Package (J)

# ORDERING INFORMATION

| PART NO   | SPEED | POWER | PACKAGE |

|-----------|-------|-------|---------|

| HY524800J | 70/80 |       | SOJ     |