# COP440/COP441/COP442 and COP340/COP341/COP342 Single-Chip N-Channel Microcontrollers

# **General Description**

The COP440, COP441, COP442, COP340, COP341, and COP342 Single-Chip N-Channel Microcontrollers are members of the COPSTM microcontrollers family, fabricated using N-channel, silicon gate MOS technology. These are complete microcontrollers with all system timing, internal logic, ROM, RAM, and I/O necessary to implement dedicated control functions in a variety of applications. Features include single supply operation, various output configuration options, and an instruction set, internal architecture, and I/O scheme designed to facilitate keyboard input, display output, and data manipulation. The COP440 is a 40-pin chip and the COP441 is a 28-pin version of the same circuit (12 I/O lines removed). The COP442 is a 24-pin version (4 more input lines removed). The COP340, COP341, COP342 are functional equivalents of the above devices respectively, but operate with an extended temperature range (-40°C to +85°C). Standard test procedures and reliable high-density fabrication techniques provide the medium to large volume customers with a customized controller oriented processor at a low end-product cost.

## **Features**

- Enhanced, more powerful instruction set

- 2k x 8 ROM, 160 x 4 RAM

- 35 I/O lines (COP440)

- Zero-crossing detect circuitry with hysteresis

- True multi-vectored interrupt from 4 selectable sources (plus restart)

- Four-level subroutine stack (in RAM)

- 4 µs cycle time

- Single supply operation (4.5V-6.3V)

- Programmable time-base counter

- Internal binary counter/register with MICROWIRE™ compatible serial I/O

- General purpose and TRI-STATE® outputs

- TTL/CMOS compatible in and out

- LED drive capability

- MICROBUS™ compatible

- Software/hardware compatible with other members of the COP400 family

- Extended temperature range devices COP340, COP341, COP342 (-40°C to +85°C)

- Compatible dual CPU device available (COP2440 series)

# COP440/COP441/COP442 **Absolute Maximum Ratings**

if Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Voltage at Zero-Crossing Detect Pin

Relative to GND

-1.2V to +15V

Voltage at Any Other Pin

Relative to GND **Ambient Operating Temperature**

-0.5V to +7V 0°C to +70°C -65°C to +150°C

**Ambient Storage Temperature**

Power Dissipation

Lead Temperature (Soldering, 10 sec.)

300°C 0.75W at 25°C

0.4W at 70°C

**Total Source Current**

150 mA 75 mA

Total Sink Current

Note: Absolute maximum ratings indicate limits beyond

which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

# DC Electrical Characteristics 0°C ≤ T<sub>A</sub> ≤ +70°C, 4.5V ≤ V<sub>CC</sub> ≤ 6.3V unless otherwise noted

| Parameter                            | Conditions                    | Min                 | Max   | Unita |  |

|--------------------------------------|-------------------------------|---------------------|-------|-------|--|

| Operating Voltage (V <sub>CC</sub> ) | (Note 3)                      | 4.5                 | 6.3   | V     |  |

| Power Supply Ripple                  | (Peak to Peak)                |                     | 0.4   | V     |  |

| Operating Supply Current             | (All Inputs and Outputs Open) |                     |       |       |  |

|                                      | T <sub>A</sub> = 0°C          |                     | 44    | mA    |  |

|                                      | T <sub>A</sub> = 25°C         |                     | 35    | mA.   |  |

|                                      | T <sub>A</sub> = 70°C         |                     | 27    | mA.   |  |

| Input Voltage Levels                 |                               |                     |       |       |  |

| CKI input Levels                     |                               |                     |       |       |  |

| Crystal Input ( $\div$ 16, $\div$ 8) |                               |                     |       |       |  |

| Logic High (V <sub>IH</sub> )        | V <sub>CC</sub> = Max         | 3.0                 |       | l v   |  |

| Logic High (V <sub>IH</sub> )        | $V_{CC} = 5V \pm 5\%$         | 2.0                 |       | V     |  |

| Logic Low (V <sub>IL</sub> )         |                               | -0.3                | 0.4   | V     |  |

| Schmitt Trigger Input (÷4)           |                               |                     |       |       |  |

| Logic High (V <sub>IH</sub> )        |                               | 0.7 V <sub>CC</sub> |       | V     |  |

| Logic Low (V <sub>IL</sub> )         |                               | -0.3                | 0.6   | V     |  |

| RESET Input Levels                   | (Schmitt Trigger Input)       |                     |       |       |  |

| Logic High                           |                               | 0.7 V <sub>CC</sub> |       | V     |  |

| Logic Low                            |                               | -0.3                | 0.6   | V     |  |

| Zero-Crossing Detect Input           | See <i>Figure 7</i>           |                     |       |       |  |

| Trip Point                           |                               | -0.15               | 0.15  | V     |  |

| Logic High (VIH) Limit               |                               |                     | 12    | V     |  |

| Logic Low (V <sub>IL</sub> ) Limit   |                               | -0.8                | -     | V     |  |

| SO Input Level (Test Mode)           | (Note 5)                      | 2.0                 | 2.5   | V     |  |

| All Other Inputs                     |                               |                     |       |       |  |

| Logic High                           | V <sub>CC</sub> = Max         | 3.0                 |       | V     |  |

| Logic High                           | $V_{CC} = 5V \pm 5\%$         | 2.0                 | İ     | V     |  |

| Logic Low                            |                               | -0.3                | 0.8   | V     |  |

| Input Levels High Trip Option        |                               |                     |       | İ     |  |

| Logic High                           |                               | 3.6                 | ļ     | V     |  |

| Logic Low                            |                               | -0.3                | 1.2   | V     |  |

| Input Capacitance                    |                               |                     | 7.0   | pF    |  |

| Hi-Z Input Leakage                   |                               | -1.0                | + 1.0 | μΑ    |  |

Note 1: Duty Cycle =  $t_{WI}/(t_{WI} + t_{WO})$ .

Note 2: See Figure for additional I/O Characteristics.

Note 3: V<sub>CC</sub> voltage change must be less than 0.5V in a 1 ms period to maintain proper operation.

Note 4: Exercise great care not to exceed maximum device power dissipation limits when direct-driving LEDs (or sourcing similar loads) at high temperature.

Note 5: SO output "0" level must be less than 0.8V for normal operation.

# COP440/COP441/COP442

**DC Electrical Characteristics**  $0^{\circ}C \le T_{A} \le +70^{\circ}C$ ,  $4.5V \le V_{CC} \le 6.3V$  unless otherwise noted (Continued)

| Parameter                              | Conditions                     | Min                   | Max  | Units |  |

|----------------------------------------|--------------------------------|-----------------------|------|-------|--|

| Output Voltage Levels                  |                                |                       |      |       |  |

| Standard Output                        |                                |                       | 1    |       |  |

| TTL Operation                          |                                |                       |      |       |  |

| Logic High (V <sub>OH</sub> )          | $I_{OH} = -100  \mu A$         | 2.4                   |      | V     |  |

| Logic Low (VOL)                        | i <sub>OL</sub> = 1.6 mA       |                       | 0.4  | V     |  |

| CMOS Operation (Note 1)                |                                |                       |      |       |  |

| Logic High (V <sub>OH</sub> )          | $I_{OH} = -10 \mu\text{A}$     | V <sub>CC</sub> - 0.4 |      | V     |  |

| Logic Low (VOL)                        | I <sub>OL</sub> = 10 μA        |                       | 0.2  | V     |  |

| Output Current Levels                  |                                |                       |      |       |  |

| Standard Output Source Current         | $V_{CC} = 4.5V, V_{OH} = 2.4V$ | -100                  | -650 | μΑ    |  |

| LED Direct Drive Output                | $V_{CC} = 6V, V_{OH} = 2V$     |                       |      |       |  |

| Logic High (I <sub>OH</sub> )          |                                | -2.5                  | -17  | mA.   |  |

| TRI-STATE Output Leakage Current       |                                | -2.5                  | +2.5 | μΑ    |  |

| CKO Output                             |                                |                       |      |       |  |

| Oscillator Output Option               |                                |                       |      |       |  |

| Logic High                             | $V_{OH} = 2V$                  | -0.2                  |      | mA    |  |

| Logic Low                              | $V_{OL} = 0.4V$                | 0.4                   |      | mA.   |  |

| V <sub>R</sub> RAM Power Supply Option |                                |                       |      |       |  |

| Supply Current                         | $V_{R} = 3.3V$                 |                       | 3.0  | mA    |  |

| CKI Sink Current (RC Option)           | $V_{HH} = 3.5V, V_{CC} = 4.5V$ | 2.0                   |      | mA    |  |

| Input Current Levels                   |                                |                       |      | }     |  |

| Zero-Crossing Detect Input             |                                |                       |      |       |  |

| Resistance                             | $V_{IH} = 1.0V$                | 0.9                   | 4.6  | kΩ    |  |

| Input Load Source Current              | $V_{IH} = 2.0V, V_{CC} = 4.5V$ | 14                    | 230  | μΑ    |  |

| Total Sink Current Allowed             |                                |                       |      |       |  |

| All I/O Combined                       |                                |                       | 75   | mA    |  |

| Each L, R Port                         |                                |                       | 20   | mA    |  |

| Each D, G, H Port                      |                                |                       | 10   | mA    |  |

| SO, SK                                 |                                |                       | 2.5  | mA    |  |

| Total Source Current Allowed           |                                |                       |      |       |  |

| All I/O Combined                       |                                |                       | 150  | mA    |  |

| L Port                                 |                                |                       | 120  | mA    |  |

| L7-L4                                  |                                |                       | 70   | mA    |  |

| L3-L0                                  |                                |                       | 70   | mA    |  |

| Each L Pin                             |                                |                       | 23   | mA    |  |

| All Other Output Pins                  |                                | i                     | 1.6  | mA    |  |

# COP340/COP341/COP342 Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Voltage at Zero-Crossing Detect Pin

Relative to GND

-1.2V to +15V

Voltage at Any Other Pin Relative to GND

Relative to GND

Ambient Operating Temperature

-0.5V to +7V -40°C to +85°C

Ambient Storage Temperature -65°C to +150°C

Lead Temperature (Soldering, 10 sec.)

Power Dissipation

300°C

0.75W at 25°C 0.25W at 85°C

**Total Source Current**

150 mA

Total Sink Current

75 mA

Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

DC Electrical Characteristics  $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$ ,  $4.5\text{V} \le \text{V}_{CC} \le 5.5\text{V}$  unless otherwise noted

| Parameter                            | Conditions                    | Min                 | Max  | Unite |

|--------------------------------------|-------------------------------|---------------------|------|-------|

| Operating Voltage (V <sub>CC</sub> ) | (Note 3)                      | 4.5                 | 5.5  | V     |

| Power Supply Ripple                  | (Peak to Peak)                |                     | 0.4  | ٧     |

| Operating Supply Current             | (All Inputs and Outputs Open) |                     |      |       |

|                                      | $T_A = -40^{\circ}C$          |                     | 54   | mA.   |

|                                      | T <sub>A</sub> = 25°C         |                     | 35   | mA    |

|                                      | T <sub>A</sub> = 85°C         |                     | 25   | mA    |

| Input Voltage Levels                 |                               |                     |      |       |

| CKI Input Levels                     |                               |                     |      |       |

| Crystal Input (÷16, ÷8)              | V <sub>CC</sub> = Max         | 3.0                 |      | V     |

| Logic High (VIH)                     |                               | 2.2                 |      | V     |

| Logic Low (VIL)                      | •                             | -0.3                | 0.3  | ٧     |

| Schmitt Trigger Input (÷4)           |                               |                     |      |       |

| Logic High (VIH)                     |                               | 0.7 V <sub>CC</sub> |      | V     |

| Logic Low (VII.)                     |                               | -0.3                | 0.4  | V     |

| RESET Input Levels                   | (Schmitt Trigger Input)       |                     |      |       |

| Logic High                           | ,                             | 0.7 V <sub>CC</sub> |      | V     |

| Logic Low                            |                               | -0.3                | 0.4  | ٧     |

| Zero-Crossing Detect Input           | See Figure 7                  |                     |      | -     |

| Trip Point                           |                               | -0.15               | 0.15 | V     |

| Logic High (VIH) Limit               |                               |                     | 12   | V     |

| Logic Low (VIL) Limit                |                               | -0.8                |      | V     |

| SO Input Level (Test Mode)           | (Note 5)                      | 2.2                 | 2.4  | V     |

| All Other Inputs                     | V <sub>CC</sub> = Max         | 3.0                 |      | V     |

| Logic High                           |                               | 2.2                 |      | ٧     |

| Logic Low                            |                               | -0.3                | 0.6  | V     |

| Input Levels High Trip Option        |                               |                     |      |       |

| Logic High                           |                               | 3.6                 |      | v     |

| Logic Low                            |                               | -0.3                | 1.2  | V     |

| Input Capacitance                    |                               |                     | 7.0  | pF    |

| Hi-Z Input Leakage                   |                               | -2.0                | +2.0 | μА    |

Note 1: Duty Cycle = twi/(twi + two).

Note 2: See Figure for additional I/O Characteristics.

Note 3: V<sub>CC</sub> voltage change must be less than 0.5V in a 1 ms period to maintain proper operation.

Note 4: Exercise great care not to exceed maximum device power dissipation limits when direct-driving LEDs (or sourcing similar loads) at high temperature.

Note 5: SO output "0" level must be less than 0.6V for normal operation.

# COP340/COP341/COP342

# **DC Electrical Characteristics**

$-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$ ,  $4.5\text{V} \le \text{V}_{\text{CC}} \le 5.5\text{V}$  unless otherwise noted (Continued)

| Parameter                              | Conditions                     | Min                   | Max  | Unite |

|----------------------------------------|--------------------------------|-----------------------|------|-------|

| Output Voltage Levels                  |                                |                       |      |       |

| Standard Output                        |                                |                       |      |       |

| TTL Operation                          |                                |                       |      |       |

| Logic High (V <sub>OH</sub> )          | $I_{OH} = -100 \mu A$          | 2.4                   |      | l v   |

| Logic Low (VOL)                        | I <sub>OL</sub> = 1.6 mA       |                       | 0.4  | l v   |

| CMOS Operation (Note 1)                | -                              |                       |      |       |

| Logic High (V <sub>OH</sub> )          | $I_{OH} = -10 \mu A$           | V <sub>CC</sub> - 0.5 |      | v     |

| Logic Low (V <sub>OL</sub> )           | $I_{OL} = 10 \mu A$            |                       | 0.2  | ٧     |

| Output Current Levels                  |                                |                       |      |       |

| Standard Output Source Current         | $V_{CC} = 4.5V, V_{OH} = 2.4V$ | -100                  | 800  | μA    |

| LED Direct Drive Output                | V <sub>CC</sub> = 5V (Note 4)  |                       |      |       |

| Logic High (I <sub>OH</sub> )          | $V_{OH} = 2V$                  | -1.5                  | -15  | mA.   |

| TRI-STATE Output Leakage Current       |                                | -5.0                  | +5.0 | μΑ    |

| CKO Output                             |                                |                       |      |       |

| Oscillator Output Option               |                                |                       |      |       |

| Logic High                             | $V_{OH} = 2V$                  | -0.2                  |      | mA    |

| Logic Low                              | $V_{OL} = 0.4V$                | 0.4                   |      | mA    |

| V <sub>R</sub> RAM Power Supply Option |                                |                       |      |       |

| Supply Current                         | $V_R = 3.3V$                   |                       | 4.0  | mA    |

| CKI Sink Current (RC Option)           | $V_{CC} = 4.5V, V_{IH} = 3.5V$ | 2.0                   |      | mA    |

| Input Current Levels                   |                                |                       |      |       |

| Zero-Crossing Detect Input             |                                |                       |      |       |

| Resistance                             | V <sub>IH</sub> = 1.0V         | 0.9                   | 4.6  | kΩ    |

| Input Load Source Current              | $V_{IH} = 2.0V, V_{CC} = 4.5V$ | 14                    | 280  | μΑ    |

| Total Sink Current Allowed             |                                | !                     |      |       |

| All I/O Combined                       |                                |                       | 75   | mA    |

| Each L, R Port                         |                                |                       | 20   | mA    |

| Each D, G, H Port                      |                                | 1                     | 10   | mA    |

| SO, SK                                 |                                |                       | 2.5  | mA    |

| Total Source Current Allowed           |                                |                       |      |       |

| All I/O Combined                       |                                |                       | 150  | mA    |

| L Port                                 |                                |                       | 120  | mA    |

| L7-L4                                  |                                |                       | 70   | mA    |

| L3-L0                                  |                                |                       | 70   | mA    |

| Each L Pin                             |                                |                       | 23   | mA    |

| All Other Output Pins                  |                                |                       | 1.6  | mA    |

Note 1: TRI-STATE and LED configurations are excluded.

# **AC Electrical Characteristics**

COP440/COP441/COP442: 0°C  $\leq$  T<sub>A</sub>  $\leq$   $+70^{\circ}$ C, 4.5V  $\leq$  V<sub>CC</sub>  $\leq$  6.3V unless otherwise noted COP340/COP341/COP342: - 40°C  $\leq$  T<sub>A</sub>  $\leq$   $+85^{\circ}$ C, 4.5V  $\leq$  V<sub>CC</sub>  $\leq$  5.5V unless otherwise noted

| Parameter                                |                  | Conditions                                    | Min          | Max        | Units    |

|------------------------------------------|------------------|-----------------------------------------------|--------------|------------|----------|

| Instruction Cycle Time-t <sub>E</sub>    |                  |                                               | 4.0          | 10         | μs       |

| CKI Frequency                            |                  | ÷ 16 Mode                                     | 1.6          | 4.0        | MHz      |

| <b>,</b>                                 |                  | ÷ 8 Mode                                      | 0.8          | 2.0        | MHz      |

|                                          |                  | ÷ 4 Mode                                      | 0.4          | 1.0        | MHz      |

| Duty Ovala (Nata 1)                      |                  | f <sub>I</sub> = 4 MHz                        | 30           | 60         | %        |

| Duty Cycle (Note 1)                      |                  |                                               | ] 30         |            | 1        |

| Rise Time                                |                  | f <sub>I</sub> = 4 MHz External Clock         |              | 60         | ns       |

| Fall Time                                |                  | f <sub>I</sub> = 4 MHz External Clock         |              | 40         | ns       |

| CKI Using RC (Figure 9c)                 |                  | ÷ 4 Mode                                      |              | İ          |          |

| Frequency                                |                  | $R = 15 k\Omega \pm 5\%, C = 100 pF \pm 10\%$ | 0.5          | 1.0        | MHz      |

| Instruction Execution Time               | 8−t <sub>F</sub> |                                               | 4.0          | 8.0        | μs       |

| (Note 1)                                 |                  |                                               |              |            | ,        |

| INPUTS: (Figure 4)                       |                  |                                               |              |            |          |

| SI                                       |                  |                                               |              |            |          |

| <sup>t</sup> SETUP                       |                  |                                               | 0.3          |            | μs       |

| tHOLD                                    |                  |                                               | 300          |            | ns ns    |

| All Other Inputs                         |                  |                                               |              |            |          |

| •                                        |                  |                                               | 1.7          |            | μs       |

| <sup>t</sup> SETUP                       |                  |                                               |              |            |          |

| thold                                    |                  |                                               | 300          |            | ns       |

| OUTPUT PROPAGATION DEL                   | _AY              | Test Condition:                               |              |            |          |

|                                          |                  | $C_{L} = 50 \text{ pF, } V_{OUT} = 1.5V$      | I            |            | l        |

| СКО                                      |                  |                                               | 1            |            | l        |

| t <sub>pd1</sub> , t <sub>pd0</sub>      |                  | Crystal Input                                 |              | 0.17       | μs       |

|                                          |                  | Schmitt Trigger Input                         | 1            | 0.3        | μS       |

| t <sub>pd1</sub> , t <sub>pd0</sub>      |                  | Schille Higger Input                          |              | 0.5        | μs       |

| SO, SK                                   |                  | B 0440                                        | I            | 1          | 1        |

| t <sub>pd1</sub> , t <sub>pd0</sub>      |                  | $R_L = 2.4 k\Omega$                           |              | 1.0        | μs       |

| All Other Outputs                        |                  | $R_L = 5.0 \text{ k}\Omega$                   |              | 1.4        | μs       |

| MICROBUS TIMING                          |                  | $C_L = 100 \text{ pF}, V_{CC} = 5V \pm 5\%$   |              |            |          |

| Read Operation (Figure 2a)               |                  | TRI-STATE Outputs                             | I            | 1          | 1        |

| Chip Select Stable Before                | RD-to            |                                               | 65           |            | ns       |

| Chip Select Hold Time for                |                  |                                               | 20           |            | ns       |

| RD Pulse Width-t <sub>RR</sub>           | 7                |                                               | 400          |            | ns       |

| Data Delay from RD-t <sub>RD</sub>       |                  |                                               | 1            | 375        | ns       |

| RD to Data Floating-to-                  |                  |                                               | I            | 250        | ns       |

| Write Operation (Figure 2b)              |                  | !                                             | ŀ            | -50        | "        |

|                                          | WB 4             |                                               | 65           |            |          |

| Chip Select Stable Before                |                  |                                               | 1            |            | ns       |

| Chip Select Hold Time for                | WH-U             |                                               | 20           |            | ns       |

| WR Pulse Width-tww                       |                  |                                               | 400          |            | ns       |

| Data Set-Up Time for WR-                 |                  |                                               | 320          |            | ns       |

| Data Hold Time for WR-ty                 |                  |                                               | 100          |            | ns       |

| INTR Transition Time from                |                  |                                               | 1            | 700        | ns       |

| lote 1: Variation due to the device incl | luded.           |                                               | •            |            | <u> </u> |

| (IN <sub>2</sub> )                       | cs ~             |                                               |              |            |          |

| (IMZ)                                    | -                | → tacs →                                      | 1            |            |          |

| (tNg)                                    | AD _             | <del></del> \                                 |              |            |          |

| (IND)                                    |                  | + ICSR IRD IDF                                |              |            |          |

|                                          | D= C-            | - con - inu                                   |              |            |          |

| (L7-L0)                                  | 07-08 -          |                                               |              | TL/DD/6926 | -2       |

|                                          |                  | URE 2a. MICROBUS Read Operation Timing        |              |            |          |

|                                          |                  |                                               |              |            |          |

|                                          |                  |                                               | .l           |            |          |

|                                          |                  |                                               | <b></b>      |            |          |

| (IN <sub>2</sub> )                       | CS -             |                                               | <b>/</b>     |            |          |

| (IN <sub>2</sub> )                       | _                | - CSW - NWCS - NWCS -                         | <b>/</b>     |            |          |

|                                          | CS WA            | TOW -                                         | <b>/</b>     |            |          |

| (IN <sub>2</sub> )                       | _                |                                               | <b>}</b>     |            |          |

| (IN <sub>2</sub> )                       | _                | TOW -                                         | <b> </b>     |            |          |

| (IN <sub>2</sub> )<br>(IN <sub>3</sub> ) | WR -             | TOW -                                         | <del> </del> |            |          |

| (IN <sub>2</sub> )                       | WR -             | WO                                            | <u></u>      | TL/DD/6926 |          |

#### **Connection Diagrams** Duai-In-Line Package VCC **Dual-in-Line Package** 39 12 l A **Dual-In-Line Package** 91 38 13 50 37 IM2 GND SK 36 1841 CKO 27 ING L4 35 CKI **D**1 CKO 23 26 **n**2 IK3 L5 RESET **D**3 CIO 22 . B2 25 BO 33 16 RESET L7 63 21 24 Gi 32 L7 LS 23 R2 63 COP449/ COP340 COP442/ COP342 COP441/ COP341 G2 10 31 RG L5 22 B1 19 16 **a**3 11 30 21 R1 Ł4 21 nn. 15 18 HO 12 29 R2 IN 1 IN3 60 14 H1 13 28 R3 IN2 10 SK INO 19 VCC -Н2 14 27 84 11 . 8K 10 S.O. VCC . L3 15 НЗ 15 26 R5 L3 12 - 80 17 11 12 -03 16 25 RE 12 13 21 12 13 D2 17 24 87 LI 14 D1 18 23 RESET TL/DD/6926-6 DO 19 22 CK TL/DD/8926-5 Top View 20 21 CKO **Top View** Order Number COP442-XXX/D or TL/DD/6926-4 Order Number COP441-XXX/D or COP342-XXX/D **Top View** COP341-XXX/D See NS Hermetic Package Number See NS Hermetic Package Number Order Number COP440-XXX/D or **D24C D28C** COP340-XXX/D Order Number COP442-XXX/N or Order Number COP441-XXX/N or See NS Hermetic Package Number COP342-XXX/N COP341-XXX/N See NS Molded Package Number D40C See NS Molded Package Number Order Number COP440-XXX/N or N24A N28B COP340-XXX/N See NS Molded Package Number N40A FIGURE 3 Pin Descriptions Description Pin Description Lz-Lo 8-bit Bidirectional I/O Port with TRI-STATE CKI System Oscillator Input System Oscillator Output (or General Purpose In-G<sub>3</sub>-G<sub>0</sub> 4-bit Bidirectional I/O Port CKO put or RAM Power Supply) D<sub>3</sub>-D<sub>0</sub> 4-bit General Purpose Output Port RESET System Reset Input IN3-IN0 4-bit General Purpose Input Port (Not Available on COP442/COP342) **Power Supply** Vcc GND SI Serial Input Ground SO Serial Output (or General Purpose Output) H3-H0 4-bit Bidirectional I/O Port (COP440/COP340 Only) SK Logic-Controlled Clock (or General Purpose Output) $R_7 - R_0$ 8-Bit Bidirectional I/O Port with TRI-STATE (COP440/COP340 Only) Timing Diagram SK AS A CLOCK SETUP ISETUP teros o ALL OTHER OUTPUTS TL/DD/6926-7 FIGURE 4. Input/Output Timing Diagrams (Divide by 16 Mode)

# **Functional Description**

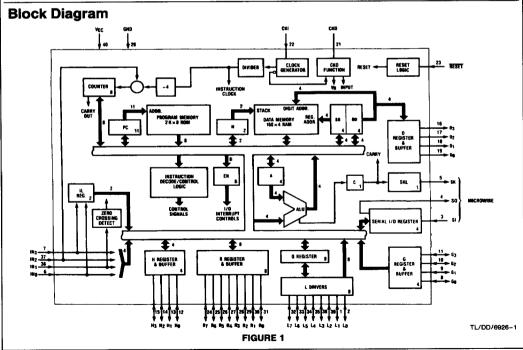

The block diagram of the COP440 is shown in Figure 1. Data paths are illustrated in simplified form to depict how the various logic elements communicate with each other in implementing the instruction set of the device. Positive logic is used. When a bit is set, it is a logic "1" (greater than 2.0V). When a bit is reset, it is a logic "0" (less than 0.8V).

#### **PROGRAM MEMORY**

Program Memory consists of a 2,048 byte ROM. As can be seen by an examination of the COP440 instruction set, these words may be program instructions, constants, or ROM addressing data. Because of the special characteristics associated with the JP, JSRP, JID, LQID, and LID instructions, ROM must often be thought of as being organized into 32 pages of 64 words each.

ROM addressing is accomplished by an 11-bit PC register. Its binary value selects one of the 2,048 8-bit words contained in ROM. A new address is loaded into the PC register during each instruction cycle. Unless the instruction is a transfer of control instruction, the PC register is loaded with the next sequential 11-bit binary count value.

ROM instruction words are fetched, decoded and executed by the Instruction Decode, Control and Skip Logic circuitry.

## DATA MEMORY

Data memory consists of a 640-bit RAM, organized as 10 data registers of 16 4-bit digits. RAM addressing is implemented by an 8-bit B register whose upper 4 bits (Br) select 1 of 10 (0-9) data registers and lower 4 bits (Bd) select 1 of 16 4-bit digits in the selected data register. While the 4-bit contents of the selected RAM digit (M) is usually loaded into, or from, or exchanged with the A register (accumulator), it may also be loaded into or from the Q latches, L port, R port, EN register, and T counter (internal time base counter). RAM may also be loaded from 4 bits of a ROM word. RAM addressing may also be performed directly to the lower 8 registers by the LDD and XAD instructions based upon the 7-bit contents of the operand field of these instructions. The Bd register also serves as a source register for 4-bit data sent directly to the D outputs. RAM register 8 (Br = 8) also serves as a subroutine stack. Note that it is possible. but not recommended, to alter the contents of the stack by normal data memory access commands.

### INTERNAL LOGIC

The 4-bit A register (accumulator) is the source and destination register for most I/O arithmetic, logic, and data memory access operations. It can also be used to load the Br and Bd portions of the B register, N register, to load and input 4 bits of the 8-bit Q latch, EN register, or T counter, to input 4 bits of a ROM word, L or R I/O port data, to input 4-bit G, H, or IN ports, and to perform data exchanges with the SIO register. The accumulator is cleared upon reset.

A 4-bit adder performs the arithmetic and logic functions of the COP440, storing its results in A. It also outputs a carry bit to the 1-bit C register, most often employed to indicate arithmetic overflow. The C register, in conjunction with the XAS instruction and the EN register, also serves to control the SK output. C can be outputted directly to SK or can enable SK to be a sync clock each instruction cycle time. (See XAS instruction and EN register description, below).

The 8-bit T counter is a binary up counter which can be loaded to and from M and A. The input to this counter is software selectable from two sources: the first coming from a divide-by-four prescaler (from instruction cycle frequency) thus providing a 10-bit time base counter; the second coming from IN2 input, changing the T counter into an 8-bit external event counter (see EN register below). In this mode, a low-going pulse ("1" to "0") of at least 2 instruction cycles wide will increment the counter. When the counter overflows, an overflow flag will be sent (see SKT instruction below) and an interrupt signal will be sent to processor X. The T counter is cleared on reset.

Four general-purpose inputs,  $IN_3-IN_0$ , are provided;  $IN_1$ ,  $IN_2$  and  $IN_3$  may be selected, by a mask-programmable option, as Read Strobe, Chip Select, and Write Strobe inputs, respectively, for use in MICROBUS applications;  $IN_1$ , by another mask-programmable option, can be selected as a true zero-crossing detector with the output triggering an interrupt or being interrogated by an instruction. These two mask-programmable options are mutually exclusive.

The D register provides 4 general-purpose outputs and is used as the destination register for the 4-bit contents of Bd. The G register contents are outputs to a 4-bit general-pur-

pose bidirectional I/O port. G<sub>0</sub> may be mask-programmed as an output for MICROBUS applications.

The H register contents are outputs to a 4-bit general-purpose bidirectional I/O port.

The Q register is an internal, latched, 8-bit register, used to hold data loaded to or from M and A, as well as 8-bit data from ROM. Its contents are outputted to the L I/O ports when the L drivers are enabled under program control. With the MICROBUS option selected, Q can also be loaded with the 8-bit contents of the L I/O ports upon the occurrence of a write strobe from the host CPU. Note that unlike most other COPS controllers, Q is cleared on reset.

The 8 L drivers, when enabled, output the contents of latched Q data to the L I/O ports. Also, the contents of L may be read directly into A and M. As explained above, the MICROBUS option allows L I/O port data to be latched into the Q register. The L I/O port can be directly connected to the segments of a multiplexed LED display (using the LED Direct Drive output configuration option) with Q data being outputted to the Sa-Sg and decimal point segments of the display.

The R register, when enabled, outputs to an 8-bit general-purpose, bidirectional, I/O port.

The SIO register functions as a 4-bit serial-in/serial-out shift register for MICROWIRE I/O and COPS peripherals, or as a binary counter (depending on the contents of the EN register; see EN register description, below). Its contents can be exchanged with A, allowing it to input or output a continuous serial data stream.

The XAS instruction copies the C flag into the SKL latch. In the counter mode, SK is the output of SKL; in the shift register mode, SK outputs SKL ANDed with the instruction cycle clock.

The 2-bit N register is a stack pointer to the data memory register 8 where the subroutine return address is located. It points to the next location where the address may be stored

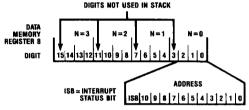

and increments by 1 after each push of the stack, and decrements by 1 before each pop. The N register can be accessed by exchanging its value with A and is cleared on reset. The stack is 4 addresses deep, 12 bits wide, and does not check for overflow or empty conditions. The RAM digit locations where the addresses are stored are shown in Figure 5. The LSBs of the addresses are at digits 0, 4, 8, and 12. The MSBs of digits 2, 6, 10, and 14 contain an interrupt status bit (see Interrupt description, below). The four unused digits (3, 7, 11, and 15) can be used as general data storage. When a subroutine call or interrupt occurs, an 11-bit return address and an interrupt status bit are stored in the stack. The N register is then incremented. When a RET or RETSK instruction is executed, the N register is decremented and then the return address is fetched and loaded into the program counter. The address and interrupt status bits remain in the stack, but will be overwritten when the next subroutine call or interrupt occurs.

TL/DD/6926-8

# FIGURE 5. Subroutine Return Address Stack Organization

The EN register in an internal 8-bit register loaded under program control by the LEI instruction (lower 4 bits) or by the CAME instruction. The state of each bit of this register selects or deselects the particular feature associated with each bit of the EN register.

0. The least significant bit of the enable register, EN<sub>0</sub>, selects the SIO register as either a 4-bit shift register or a 4-bit binary counter. With EN<sub>0</sub> set, SIO is an asynchronous binary counter, decrementing its value by one upon each low-going pulse ("1" to "0") occurring on the SI input. Each pulse must be at least two instruction cycles wide. SK outputs the value of SKL. The SO output is equal to the value of EN<sub>3</sub>. With EN<sub>0</sub> reset, SIO is a serial shift register left shifting 1 bit each instruction cycle time. The data present at SI goes into the least significant bit of SIO. SO can be enabled to output the most significant bit of SIO each cycle time. The SK output becomes a logic-controlled clock.

- With EN<sub>1</sub> set, interrupt is enabled with EN<sub>4</sub> and EN<sub>5</sub> selecting the interrupt source. Immediately following an interrupt, EN<sub>1</sub> is reset to disable further interrupts.

- 2. With EN<sub>2</sub> set, the L drivers are enabled to output the data in Q to the L I/O port. Resetting EN<sub>2</sub> disables the L drivers, placing the L I/O port in a high-impedance input state. A special feature of the COP440 and COP441 is that the MICROBUS option will change the function of this bit to disable any writing into G<sub>0</sub> when EN<sub>2</sub> is set.

- 3. EN<sub>3</sub>, in conjunction with EN<sub>0</sub>, affects the SO output. With EN<sub>0</sub> set (binary counter option selected) SO will output the value loaded into EN<sub>3</sub>. With EN<sub>0</sub> reset (serial shift register option selected), setting EN<sub>3</sub> enables SO as the output of the SIO shift register, outputting serial shifted data each instruction time. Resetting EN<sub>3</sub> with the serial shift register option selected disables SO as the shift register output; data continues to be shifted through SIO and can be exchanged with A via an XAS instruction but SO remains set to "0". Table I below provides a summary of the modes associated with EN<sub>3</sub> and EN<sub>0</sub>.

- 4. EN5 and EN4 select the source of the interrupt signal.

- 5. The possible sources are as follows:

| EN <sub>5</sub> | EN <sub>4</sub> | Interrupt Source                                    |  |  |  |

|-----------------|-----------------|-----------------------------------------------------|--|--|--|

| 0               | 0               | IN <sub>1</sub> (low-going pulse)                   |  |  |  |

| 0               | 1               | CKO input (if mask-programmed as an input)          |  |  |  |

| 1               | 0               | Zero-crossing (or IN <sub>1</sub> level transition) |  |  |  |

| 1               | 1               | T counter overflows                                 |  |  |  |

EN₄ determines the interrupt routine location.

- With EN<sub>6</sub> set, the internal 8-bit T counter will use IN<sub>2</sub> as its input. With EN<sub>6</sub> reset, the input to the T counter is the output of a divide by four prescaler (from instruction cycle frequency), thus providing a 10-bit time-base counter.

- 7. With EN $_7$  set, the R outputs are enabled; if EN $_7=0$ , the R outputs are disabled.

## INTERRUPT

The following features are associated with the interrupt procedure and protocol and must be considered by the programmer when utilizing interrupts.

a. The interrupt, once acknowledged as explained below, pushes the next sequential program counter address (PC+1) together with an interrupt status bit, onto the program counter stack residing in data memory. Any previous contents at the bottom of the stack are lost. The program counter is set to hex address 0FF (the last word of page 3) and EN<sub>1</sub> is reset. If EN<sub>4</sub> is reset, the next program address is hex 100; if EN<sub>4</sub> is set, the next program address is hex 300; thus providing a different interrupt location for different interrupt sources.

| TABLE I. Enable Register Modes — Bits EN <sub>3</sub> and EN | 40 |

|--------------------------------------------------------------|----|

|--------------------------------------------------------------|----|

| EN <sub>3</sub> | EN <sub>0</sub> | SIO            | SI                      | so         | SK                                           |

|-----------------|-----------------|----------------|-------------------------|------------|----------------------------------------------|

| 0               | 0               | Shift Register | Input to Shift Register | 0          | If SKL = 1, SK = Clock If SKL = 0, SK = 0    |

| 1               | 0               | Shift Register | Input to Shift Register | Serial Out | If SKL = 1, SK = Clock<br>If SKL = 0, SK = 0 |

| 0               | 1               | Binary Counter | Input to Binary Counter | 0          | If SKL = 1, SK = 1<br>If SKL = 0, SK = 0     |

| 1               | 1               | Binary Counter | Input to Binary Counter | 1          | If SKL = 1, SK = 1<br>If SKL = 0, SK = 0     |

- An interrupt will be acknowledged only after the following conditions are met:

- 1. EN<sub>1</sub> has been set.

- For an external interrupt input, the signal pulse must be at least two instruction cycles wide.

- 3. A currently executing instruction has been completed.

- 4. All successive transfer of control instructions and successive LBIs have been completed (e.g., if the main program is executing a JP instruction which transfers program control to another JP instruction, the interrupt will not be acknowledged until the second JP instruction has been executed.

- c. The instruction at hex address 0FF must be a NOP.

- d. A CAME or LEI instruction may be put immediately before the RET instruction to re-enable interrupts.

- e. If the interrupt signal source is being changed, the interrupt must be disabled prior to, or at, the same time with the change to avoid false interrupts. An interrupt may be enabled only if the interrupt source is not changing. A sample code for changing the interrupt source and enabling the interrupt is as follows:

CAME ; disable interrupt & alter interrupt source

SMB 1 ; set interrupt enable bit

CAME ; enable interrupt

f. An interrupt status bit is stored together with the return address in the stack. The status bit is set if an interrupt occurs at a point in the program where the next instruction is to be skipped; upon returning from the interrupt routine, this set status bit will cause the next instruction to be skipped. Subroutine and interrupt nesting inside interrupt routines are allowed. Note that this differs from the COP420/420C/420L/444L series.

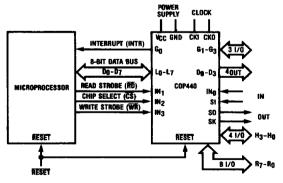

### MICROBUS INTERFACE (not available in COP442, COP342)

#### (not available in COP442, COP342

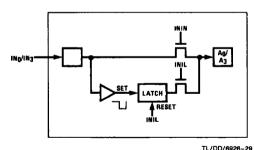

The COP440 series has an option which allows them to be used as peripheral microprocessor devices, inputting and outputting data from and to a host microprocessor ( $\mu$ P). IN<sub>1</sub>, IN<sub>2</sub> and IN<sub>3</sub> general purpose inputs become MICROBUS-compatible read-strobe, chip-select, and write-strobe lines, respectively. IN<sub>1</sub> becomes  $\overline{RD}$ —a logic "0" on this input

will cause Q latch data to be enabled to the L ports for input to the  $\mu P.$  IN $_2$  becomes  $\overline{CS}-a$  logic "0" on this line selects the COPS processor as the  $\mu P$  peripheral device by enabling the operation of the  $\overline{RD}$  and  $\overline{WR}$  lines and allows for the selection of one of several peripheral components. IN $_3$  becomes  $\overline{WR}-a$  logic "0" on this line will write bus data from the L ports to the Q latches for input to the COPS processor.  $G_0$  becomes INTR, a "ready" output, reset by a write pulse from the  $\mu P$  on the  $\overline{WR}$  line, providing the "handshaking" capability necessary for asynchronous data transfer between the host CPU and the COPS processor.  $G_0$  output can be separated from other G outputs by the EN $_2$  bit (see EN description above).

This option has been designed for compatibility with National's MICROBUS—a standard interconnect system for 8-bit parallel data transfer between MOS/LSI CPUs and interfacing devices. (See MICROBUS National Publication.) The functional and timing relationships between the COPS processor signal lines affected by this option are as specified for the MICROBUS interface, and are given in the AC electrical characteristics and shown in the timing diagrams (Figure 2). Connection of the COP440 to the MICROBUS is shown in Figure 6.

Note: TRI-STATE outputs must be used on L port.

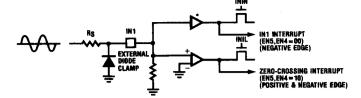

# ZERO-CROSSING DETECTION (not available on the COP442, COP342)

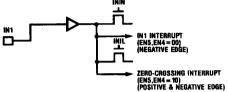

The following features are associated with the IN $_1$  pin: ININ and INIL instructions input the state of IN $_1$  to A $_1$ ; IN $_1$  interrupt generates an interrupt pulse when a low-going transition ("1" to "0") occurs on IN $_1$ ; zero-crossing interrupt generates an interrupt pulse when an IN $_1$  transition occurs (both "1" to "0" and "0" to "1").

If the zero-crossing detector is mask-programmed in (see Figure 7a), the INIL instruction and zero-crossing interrupt will input the state of IN $_1$  through the true zero-crossing detector ("1" if input > 0V, "0" if input < 0V). The ININ instruction and IN $_1$  interrupt will then have unique logic HIGH and LOW levels depending on the IN port input level chosen. If normal (TTL) level is chosen, logic HIGH level is 3.0V (3.3V for COP340/341) and logic LOW level is 0.8V

**FIGURE 6. MICROBUS Option Interconnect**

TL/DD/6926-9

TL/DD/6926-10

TL/DD/6926-12

\*Note: This input has a different set of logic HIGH and LOW levels; see above description.

a. Zero-Crossing Detect Logic Option

TL/DD/6926-11

b. IN, without Zero-Crossing Detect Logic FIGURE 7. IN, Mask-Programmable Options

(0.6V for COP340/341); if high trip level is chosen, logic HIGH level is 5.4V and logic LOW level is 1.2V. If the zero-crossing detector is not mask-programmed in (see Figure 7b), IN<sub>1</sub> will have logic HIGH and LOW levels that are defined for the IN port (see option list).

The zero-crossing detector input contains a small hysteresis (50 mV typical) to eliminate signal noise, and is not a high impedance input but contains a resistive load to ground. Since this input can withstand a voltage range of  $-0.8 \mathrm{V}$  to  $+12 \mathrm{V}$ , an external clamping diode is needed for most input signals, as shown in Figure~7a, to limit the voltage below ground. An external resistor,  $\mathrm{R}_\mathrm{S}$  may be needed for the following two cases:

- a. Input signal exceeds 12V; R<sub>S</sub> and the internal resistor act as a voltage divider to reduce the voltage at the input pin to below 12V.

- b. Signal comes from a low impedance source; when the voltage at the pin is clamped to -0.7V by the forward bias voltage of an external diode, R<sub>S</sub> limits the current going through the diode.

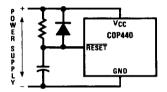

The RESET pin is configured as a Schmitt trigger input. If

### INITIALIZATION

not used, it should be connected to V<sub>CC</sub>. Initialization will occur whenever a logic "O" is applied to the RESET input, provided it stays low for at least three instruction cycle times. The user must provide an external RC network and diode to the RESET pin as in Figure 8. The external POR (Power-on-Reset) delay must be greater than the internal POR. The internal POR delay is 2600 internal clock cycles. Upon initialization, the PC register is cleared to 0 (ROM address 0) and the A, B, C, D, EN, G, H, IL, L, N, Q, R, and T registers are cleared. The SK output is enabled as a SYNC output by setting the SKL latch, thus providing a clock. RAM (data memory and stack) is not cleared. The first instruction at address 0 must be a CLRA.

RC ≥ 5 × power supply rise time

FIGURE 8. Power-Up Clear Circuit

## OSCILLATOR

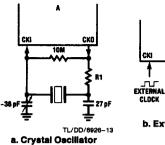

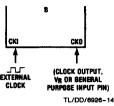

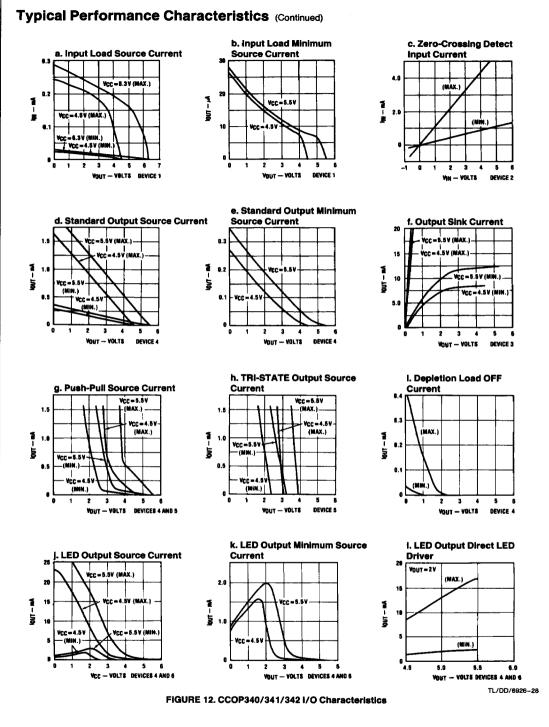

There are three basic clock oscillator configurations available, as shown by Figure 9.

- a. Crystal Controlled Oscillator. CKI and CKO are connected to an external crystal. The cycle frequency equals the crystal frequency divided by 16 (optional by 8). Thus a 4 MHz crystal with the divide-by-16 option selected will give a 250 kHz cycle frequency (4 μs instruction cycle time).

- b. External Oscillator. CKI is an external clock input signal. The external frequency is divided by 16 (optional by 8 or 4) to give the cycle frequency. If the divide-by-4 option is selected, the CKI input level is the Schmitt-trigger level. CKO is now available to be used as the RAM power supply (V<sub>R</sub>) or as a general purpose input.

- c. RC Controlled Oscillator. CKI is configured as a single pin RC controlled Schmitt trigger oscillator. The cycle frequency equals the oscillation frequency divided by 4. CKO is available for non-timing functions.

#### **CKO PIN OPTIONS**

As an option, CKO can be an oscillator output. In a crystal controlled oscillator system, this signal is used as an output to the crystal network. As another option, CKO can be an interrupt input or a general purpose input, reading into bit 2 of A (accumulator) through the INIL instruction. As another option, CKO can be a RAM power supply pin ( $V_{\rm R}$ ), allowing

c. RC Controlled Oscillator

## **Crystal Oscillator**

| Crystal Value | R <sub>1</sub> |

|---------------|----------------|

| 4 MHz         | 1k             |

| 3.58 MHz      | 1k             |

| 2.10 MHz      | 2k             |

## RC Controlled Oscillator

|               |        | Instruction |

|---------------|--------|-------------|

| <b>R</b> (kΩ) | C (pF) | Execution   |

|               |        | Time (μs)   |

| 13            | 100    | 5.0 ± 20%   |

| 6.8           | 220    | 5.3 ±23%    |

| 8.2           | 300    | 8.0 ±22%    |

| 22            | 100    | 8.2 ±17%    |

Note: 5 kΩ < B < 50 kΩ 50 pF ≤ C ≤ 360 pF

### FIGURE 9. COP440/441/442 Oscillators

its connection to a standby/backup power supply to maintain the data integrity of RAM registers 0-3 with minimum power drain when the main supply is inoperative or shut down to conserve power. Using either of the two latter options is appropriate in applications where the system configuration does not require use of the CKO pin for timing func-

## **RAM KEEP-ALIVE OPTION**

Selecting CKO as the RAM power supply (Vp) allows the user to shut off the chip power supply (V<sub>CC</sub>) and maintain data in the lower 4 registers of the RAM. To insure that RAM data integrity is maintained, the following conditions must be

- 1. RESET must go low before V<sub>CC</sub> goes below spec during power-off; VCC must be within spec before RESET goes high on power-up.

- 2. When V<sub>CC</sub> is on, V<sub>B</sub> must be within the operating voltage range of the chip, and within 1V of VCC.

- 3.  $V_R$  must be  $\geq$  3.3V with  $V_{CC}$  off.

#### I/O OPTIONS

COP440 inputs have the following optional configurations, illustrated in Figure 10.

- a. An on-chip depletion load device to V<sub>CC</sub>.

- b. A Hi-Z input which must be driven to a "1" or "0" by external components.

- c. A resistive load to GND for the zero-crossing input option (IN1 only).

COP440 outputs have the following optional configurations:

- d. Standard-an enhancement mode device to ground in conjunction with a depletion-mode device to V<sub>CC1</sub> compatible with TTL and CMOS input requirements. Available on SO, SK, D, G, and H outputs.

- e. Open-Drain-an enhancement-mode device to ground only, allowing external pull-up as required by the user's application. Available on SO, SK, D, G, L, H, and R outputs.

- f. Push-Pull-an enhancement-mode device to ground in conjunction with a depletion-mode device paralleled by an enhancement-mode device to V<sub>CC</sub>. This configuration has been provided to allow for fast rise and fall times when driving capacitive loads. Available on SO and SK outputs only.

- g. Standard L,R-same as d., but may be disabled. Available on L and R outputs only (disabled on reset).

- h. LED Direct Drive-an enhancement-mode device to ground and V<sub>CC</sub> together with a depletion device to V<sub>CC</sub> meeting the typical current sourcing requirements of the segments of an LED display. The sourcing devices are clamped to limit current flow. These devices may be turned off under program control (see Functional Description, EN Register), placing the output in a high-impedance state to provide required LED segment blanking for a multiplexed display. Available on L outputs only.

- Note 1: When the driver is disabled, the depletion device may cause the output to settle down to an intermediate level between Voc and GND. This voltage cannot be relied upon as a "1" level when reading the L inputs. The external signal must drive it to a "1" level.

- Note 2: Much power is dissipated by this driver in driving an LED. Care must be taken to limit the power dissipation of the chip to within the absolute maximum ratings specified.

- I. TRI-STATE Push-Pull—an enhancement-mode device to ground and VCC. These outputs are TRI-STATE outputs, allowing for connection of these outputs to a data bus shared by other bus drivers. Available on L and R outputs only (in TRI-STATE mode on reset).

- i. Push-Pull R-same as f., but may be disabled. Available on R outputs only.

- k. Additional depletion pull-up—a depletion load to VCC with the same current sourcing capability as the input load a., in addition to the output drive chosen. Available on L and R outputs only. This device cannot be disabled; therefore, open-drain outputs with "1" output and TRI-STATE outputs do not show high-impedance characteristics. This device is useful in applications where a pull-up with low source current is desired, e.g., reading keyboards and switches.

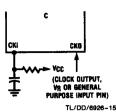

The above input and output configurations share common enhancement-mode and depletion-mode devices. Specifically, all configurations use one or more of six devices (numbered 1-6 respectively). Minimum and maximum current (IOUT and VOUT) curves are given in Figures 11 and 12 for each of these devices to allow the designer to effectively use these I/O configurations in designing a COP440 system.

# Functional Description (Continued) INPUT X TL/DD/6926-17 TL/DD/6926-20 TL/DD/6926-16 b. Hi-Z Input Open-Drain T) /DD/6926\_19 a. Input with Load TL/DD/6926-18 d. Standard Output c. Zero-Crossing Output Input DISABLE TL/DD/6926-21 TL/DD/6926-23 TL/DD/6926-22 f. Push-Pull Output i. TRI-STATE Push-Pull g. Standard L, R Outputs (L, R) Outputs L.R OUTPUT TL/DD/6926-26 #3

TL/DD/6926~24 (A is depletion device)

TI /DD/6926-25 j. Push-Pull R Outputs

h. LED (L) Outputs

FIGURE 10. Input/Output Configurations

#### L-BUS CONSIDERATIONS

START:

False states may be generated on L<sub>0</sub>-L<sub>7</sub> during the execution of the CAMQ instruction. The L-Ports should not be used as clocks for edge sensitive devices such as flip-flops, counters, shift registers, etc. The following short program illustrates this situation.

# **Glitch Test Program**

|       | CLRA |      | ENABLE THE Q        |

|-------|------|------|---------------------|

|       | LEI  | 4    | REGISTER TO L LINES |

|       | LBI  | TEST |                     |

|       | STII | 3    |                     |

|       | AISC | 12   |                     |

| LOOP: |      |      |                     |

|       | LBI  | TEST | LOAD Q WITH X'C3    |

|       | CAMQ |      |                     |

|       | JP   | L00P |                     |

In this program the internal Q register is enabled onto the L lines and a steady bit pattern of logic highs is output on Lo, L<sub>1</sub>, L<sub>6</sub>, L<sub>7</sub>, and logic lows on L<sub>2</sub>-L<sub>5</sub> via the two-byte CAMQ instruction. Timing constraints on the device are such that the Q register may be temporarily loaded with the second byte of the CAMQ opcode (X'3C) prior to receiving the valid data pattern. If this occurs, the opcode will ripple onto the L lines and cause negative-going glitches on L0, L1, L6, L7, and positive glitches on L2-L5. Glitch durations are under 2 µs, although the exact value may vary due to data patterns, processing parameters, and L line loading. These false states are peculiar only to the CAMQ instruction and the L lines.

#### **Typical Performance Characteristics** b. Input Load Minimum Source c. Zero-Crossing Detect Input Current Current a. Input Load Source Current VCC = 6.3V (MAX.) VCC = 6.3 V Ę VCC = 4. 2 \_1 3 4 VOUT - VOLTS DEVICE 1 YOUT - YOLTS DEVICE 1 d. Standard Output e. Standard Output Minimum **Source Current** Source Current f. Output Sink Current VCC = 6.3 V (MAX.) VCC = 4.5V (MAX VCC=6.3V (MAX.) 10 VCC 0.1 3 4 2 3 5 VOUT - VOLTS VOUT - VOLTS DEVICE 4 VOUT - VOLTS DEVICE 3 h. TRI-STATE Output Source i. Depletion Load OFF Current g. Push-Pull Source Current Current VCC = 6.31 0.3 VCC = 6.3 (MAX.) (MAX.) VCC = 6.3 V VCC = 6.3Y 1 1 0.2 MAX 喜 0.1 VCC = 4.5 (MAX ) VCC = 4.5 (MIN.) (MIN.) 3 2 3 5 3 VOUT - VOLTS DEVICE 5 VOUT - VOLTS DEVICES 4 AND 5 - VOL78 DEVICE 4 k. LED Output Minimum Source I. LED Output Direct LED Drive Current j. LED Output Source Current V0UT = 2 V CC=6.3V (MAX.) 2.0 15 (MAX.) 15 į (MAX.) 10 Vcc = 4.5 3 5.5 VOUT - VOLTS DEVICES 4 AND 6 YOUT - YOUTS DEVICES 4 AND 6 - VOLTS DEVICES 4 AND 6 TL/DD/6926-27 FIGURE 11, COP440/441/442 I/O Characteristics

# **Power Dissipation**

In order not to damage the device by exceeding the absolute maximum power dissipation rating, the amount of power dissipated inside the chip must be carefully controlled. As an example, an application uses a COP440 in room temperature (25°C) environment with a  $V_{\rm CC}$  power supply of 6V; IN and SI inputs have internal loads; G and D ports drive loads that may sink up to 2 mA into the chip; H port with standard output option reads switches; L port with the LED option drives a multiplexed seven-segment display; R, SO and SK drive MOS inputs that do not source or sink any current.

- a. At 25°C, maximum power dissipation allowed = 750 mW

- b. Power dissipation by chip except

$$I/O = I_{CC} \times V_{CC} = 35 \text{ mA} \times 6V = 210 \text{ mW}$$

c. Maximum power dissipation by IN,

$$SI = 5 \times 0.3 \,\text{mA} \times 6V = 9 \,\text{mW}$$

d. G and D ports are sinking current from external loads; maximum output voltage with 2 mA sink current is less than 0.4V. Power dissipation by G and D ports =

$$2 \text{ mA} \times 0.4 \text{V} \times 8 = 6.4 \text{ mW}$$

e. Maximum power dissipation by H port =

$$4 \times 1.5 \text{ mA} \times 6V = 36 \text{ mW}$$

f. When the seven segments of the LED are turned on, the output voltage is about 2V, so that the segment current is 17 mA. Power dissipation by L port =

$$7 \times 17 \text{ mA} \times (6V - 2V) = 476 \text{ mW}$$

This power dissipation caused by driving LEDs is usually the highest among the various sources.

g. R, SO, and SK do not dissipate any significant amount of power because they do not need to source or sink any current. Total power dissipation (TPD) inside the device is the sum of items b through g above.

$$TPD = 210 + 9 + 6 + 36 + 476 \,\text{mW} = 737 \,\text{mW}$$

This is within the 750 mW limit at room temperature. If this application has to operate at 70°C, then the power dissipation must be reduced to meet the limit at that temperature. Some ways to achieve this would be to limit the LED current or to use an external LED driver.

At 70°C the absolute maximum power dissipation rating drops to 400 mW. The user must be careful not to exceed this value.

#### **COP440 SERIES DEVICES**

If the COP440 is bonded as a 28- or 24-pin device, it becomes the COP441 or COP442, respectively, as illustrated in Figure 3. Note that the COP441 and COP442 does not include H and R ports. In addition, the COP442 does not include IN inputs; use of this option precludes the use of the IN options, the interrupt feature with IN as input, the zerocrossing detect option, IN<sub>2</sub> external event counter input, and the MICROBUS option. All other options are available. COP340, COP341, and COP342 are extended temperature versions of the COP440, COP441, and COP442, respectively.

# **COP440 Series Instruction Set**

Table II is a symbol table providing internal architecture, instruction operand and operation symbols used in the instruction set table.

Table III provides the mnemonic, operand, machine code, data flow, skip conditions and description associated with each instruction in the COP440 series instruction set.

#### **TABLE II. COP440 Series Instruction Set Symbols**

| Symbo                                                              | Definition                                                                                                                                                                                                                                                                                                                                                                                    | Symbo                                                              | Definition                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTER                                                              | NAL ARCHITECTURE SYMBOLS                                                                                                                                                                                                                                                                                                                                                                      | INSTR                                                              | UCTION OPERAND SYMBOLS                                                                                                                                                                                                                                                                                                                           |

| A<br>B<br>Br<br>Bd<br>C<br>D<br>EN<br>G<br>H                       | 4-bit Accumulator 8-bit RAM Address Register Upper 4 bits of B (register address) Lower 4 bits of B (digit address) 1-bit Carry Register 4-bit Data Output Port 8-bit Enable Register 4-bit Register to latch data for G I/O Port 4-bit Register to latch data for H I/O Port Two 1-bit Latches associated with the IN <sub>3</sub> or IN <sub>0</sub> Inputs                                 | RAMN                                                               | 4-bit Operand Field, 0-15 binary (RAM Digit Select) 4-bit Operand Field, 0-9 binary (RAM Register Select) 11-bit Operand Field, 0-2047 binary (ROM Address) 4-bit Operand Field, 0-15 binary (Immediate Data) Content of RAM location addressed by s Content of RAM location addressed by stack pointer N Content of ROM location addressed by t |

| IN                                                                 | 4-bit Input Port                                                                                                                                                                                                                                                                                                                                                                              | OPER                                                               | ATIONAL SYMBOLS                                                                                                                                                                                                                                                                                                                                  |

| IN <sub>1</sub> Z<br>L<br>M<br>N<br>PC<br>Q<br>R<br>SIO<br>SK<br>T | Zero-Crossing Input 8-bit TRI-STATE I/O Port 4-bit contents of RAM Memory pointed to by B Register 2-bit subroutine return address stack pointer 11-bit ROM Address Register (program counter) 8-bit Register to latch data for L I/O Port 8-bit Register to latch data for R TRI-STATE I/O Port 4-bit Shift Register and Counter Logic-Controlled Clock Output 8-bit Binary Counter Register | +<br>-<br>-<br>-<br>-<br>-<br>-<br>A<br>+<br>-<br>-<br>-<br>-<br>V | Plus Minus Replaces Is exchanged with Is equal to The one's complement of A Exclusive-OR Range of values OR                                                                                                                                                                                                                                      |

# Instruction Set

**TABLE III. COP440 Series Instruction Set**

| Mnemonic | Operand    | Hex<br>Code | Machine<br>Language Code<br>(Binary)           | Data Flow                                                                                                                                                 | Skip Conditions       | Description                                  |

|----------|------------|-------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------|

| ARITHMET | IC/LOGIC I | NSTRU       |                                                | <u> </u>                                                                                                                                                  |                       |                                              |

| ASC      |            | 30          | 0011 0000                                      | $A + C + RAM(B) \rightarrow A$<br>Carry $\rightarrow$ C                                                                                                   | Carry                 | Add with Carry, Skip on<br>Carry             |

| ADD      |            | 31          | 0011 0001                                      | A + RAM(B) → A                                                                                                                                            | None                  | Add RAM to A                                 |

| ADT      |            | 4A          | 0100   1010                                    | $A + 10_{10} \rightarrow A$                                                                                                                               | None                  | Add Ten to A                                 |

| AISC     | у          | 5-          | 0101 y                                         | $A + y \rightarrow A$                                                                                                                                     | Carry                 | Add immediate, Skip on Carry (y $\neq$ 0)    |

| CASC     |            | 10          | 0001   0000                                    | $\overline{A} + RAM(B) + C \rightarrow A$<br>Carry $\rightarrow C$                                                                                        | Carry                 | Complement and Add with Carry, Skip on Carry |

| CLRA     |            | 00          | 0000 0000                                      | 0 → A                                                                                                                                                     | None                  | Clear A                                      |

| COMP     |            | 40          | 0100 0000                                      | $\overline{A} \rightarrow A$                                                                                                                              | None                  | One's complement of A to                     |

| NOP      |            | 44          | 0100   0100                                    | None                                                                                                                                                      | None                  | No Operation                                 |

| OR       |            | 33<br>1A    | 0011 0011                                      | $A \lor M \rightarrow A$                                                                                                                                  | None                  | OR RAM with A                                |

| RC       |            | 32          | 0011 0010                                      | "o" → C                                                                                                                                                   | None                  | Reset C                                      |

| SC       |            | 22          | 0010 0010                                      | "1" → C                                                                                                                                                   | None                  | Set C                                        |

| XOR      |            | 02          | 0000   0010                                    | A⊕RAM(B) → A                                                                                                                                              | None                  | Exclusive-OR RAM with A                      |

| TRANSFER | OF CONTE   | ROL INS     | STRUCTIONS                                     |                                                                                                                                                           |                       |                                              |

| JID      |            | FF          | [1111   1111                                   | ROM (PC <sub>10:8</sub> , A,M) → PC <sub>7:0</sub>                                                                                                        | None                  | Jump Indirect (Note 3)                       |

| JMP      | а          | 6-<br>      | 0110 0 a <sub>10:8</sub>                       | a → PC                                                                                                                                                    | None                  | Jump                                         |

| JP       | а          |             | 1 <u>a<sub>6:0</sub></u><br>(pages 2,3 only)   | a → PC <sub>6:0</sub>                                                                                                                                     | None                  | Jump within Page<br>(Note 4)                 |