### Dual Decade Counter

#### Preliminary

| Device Parameter                  | High Speed (74HCT) | Standard (74SC) | Military (54HCT) |

|-----------------------------------|--------------------|-----------------|------------------|

| Dual Decade Counter               | 74HCT390           | 74SC390         | 54HCT390         |

| Operating temperature range (°C)  | -40 to +85         | -40 to +85      | -55 to +125      |

| Recommended operating voltage (V) | 4.75 to 5.25       | 4.75 to 5.25    | 4.50 to 5.50     |

| Typical fmax MHz                  | _                  | 20              | _                |

#### **Features**

- ☐ Pin and function compatible to 54/74LS equivalent circuits

- ☐ Typical DC operating supply current: 10µA

- ☐ MIL STD 883B Screening/Leadless chip carrier available

- ☐ Fast propagation delay times

- ☐ Fan out of 30 LSTTL loads

- ☐ Fully TTL and CMOS compatible

- ☐ -40°C to +85°C operating temperature range

- ☐ Capable of operating over 3-volt to 6-volt range

- ☐ High speed silicon-gate CMOS technology

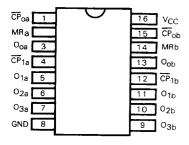

# **Pin Configuration**

### **General Description**

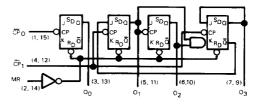

The '390 is a dual 4-bit decade ripple counter divided into four separately clocked sections. The counter has two divide-by-two sections and two divide-by-five sections. These sections are normally used in a BCD decade or a bi-quinary configuration, since they share a common Master Reset input. If the two Master Resets can be used to simultaneously clear all 8 bits of the counter, a number of counting configurations are possible within one package. The separate clocks of each section allow ripple counter or frequency division applications of divide-by-2, 4, 5, 10, 20, 25, 50 or 100.

Each section is triggered by the HIGH-to-LOW transition of the Clock ( $\overline{CP}$ ) inputs. For BCD decade operation, the Q<sub>0</sub> output is connected to the  $\overline{CP}_1$  input of the divide-by-five section. For bi-quinary decade operation (50% duty cycle output), the Q<sub>3</sub> output is connected to the CP<sub>0</sub> input, and Q<sub>0</sub> becomes the decade output.

The Master Resets ( $MR_a$  and  $MR_b$ ) are active HIGH asynchronous inputs to each decade counter which operate on the portion of the counter identified by the "a" and "b" suffixes in the Pin Configuration. A HIGH level on the MR input overrides the clocks and sets the four outputs LOW.

# **Function Block Diagram**

V<sub>CC</sub> = Pin 16 GND = Pin 8 ( ) = Pin numbers