|                                       |                       |        |    | <del></del> |         |          |          | RF   | EVISI          | ONS  |        |       |       |      |        |       |      | <del>- 11. 11.</del> |      |    |

|---------------------------------------|-----------------------|--------|----|-------------|---------|----------|----------|------|----------------|------|--------|-------|-------|------|--------|-------|------|----------------------|------|----|

| LTR                                   |                       |        |    |             |         | ESCRI    | IPTIC    |      | VATOT          | .UNS |        |       | D     | ATE  | (YR-MO | -DA)  |      | APPR                 | OVED |    |

|                                       |                       |        |    |             |         | 100      |          |      |                |      |        |       |       |      | •      |       |      |                      |      |    |

| •<br>·                                |                       |        |    |             |         |          |          |      |                |      |        | •     |       |      |        |       | •    |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                | × .  |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

| i<br>I                                |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

|                                       |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

| REV                                   |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

| SHEET                                 |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

| REV                                   |                       |        |    |             |         |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

| SHEET                                 | 15                    | 16     | 17 | 18          | 19      | 20       | 21       | 22   | 23             | 24   | 25     | 26    |       |      |        |       |      |                      |      |    |

| REV STATE                             |                       |        |    | RE          | .v      |          |          |      |                |      |        |       |       |      |        |       |      |                      |      |    |

| OF SHEETS                             | 3                     |        |    | SH          | IEET    |          | 1        | 2    | 3              | 4    | 5      | 6     | 7     | 8    | 9      | 10    | 11   | 12                   | 13   | 14 |

| PMIC N/A                              |                       |        |    | PREP        | ARED B  | JY       | -<br>- / | 1    | ,              | DI   | FFENS  | SE EL | ECTR  | ONIC | s su   | ррг,ү | CENT | rer                  |      |    |

| -                                     |                       |        |    |             | L       | in G     | PK       | and  | _              | ~-   | 31 aa. |       | OTYAC |      |        |       |      |                      |      |    |

| STAND.<br>MIL                         | AKDI<br>I <b>TA</b> R |        |    | CHEC        | KED BY  | <b>,</b> | 14.      | // . |                |      |        |       |       |      |        |       |      |                      |      |    |

| DRA                                   | AMIN(                 | G      |    | 1           | ROWED B |          | m./      | 7    |                | 1    |        | IRCU  |       |      |        |       |      |                      |      |    |

| THIS DRAWIN                           |                       |        |    | No          | men i   |          | Koc      | 0/   | \\ \frac{1}{2} | 1    |        | NG I  |       |      |        | CES   | sor, |                      |      |    |

| FOR USE BY A<br>AND AGEN<br>DEPARTMEN | CIES O                | OF THE |    | DRAW        | ING AF  | PROVAL   | _ DATE   |      | <del>}</del>   | 1101 | 1011   | 1111  |       |      |        |       |      | ·                    |      |    |

| VEFARITIEN                            | lUrv                  | EFENSE | -  |             | 92-08   | 3-03     |          |      |                | SIZ  | E      |       | E CO  |      |        | 59    | 962- | 8946                 | 53   |    |

| AMSC N/A                              |                       |        | İ  | REVI        | SION L  | .EVEL    |          |      |                | A    |        | 6     | 5726  | 8    |        |       |      |                      |      |    |

|                                       |                       |        | ;  |             |         |          |          |      |                | SHE  | EET    |       |       |      |        |       |      |                      |      | 1  |

DESC FORM 193

## 1 SCOPE

1.1 Scope. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

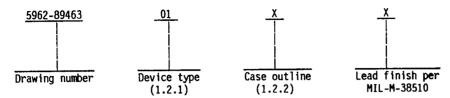

1.2 Part or Identifying Number (PIN). The complete PIN shall be as shown in the following example:

1.2.1 Device type(s). The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>          |

|-------------|----------------|----------------------------------|

| 01          | 68882-16       | HCMOS floating point coprocessor |

| 02          | 68882-20       | HCMOS floating point coprocessor |

| 03          | 68882-25       | HCMOS floating point coprocessor |

| 04          | 68882-33       | HCMOS floating point coprocessor |

1.2.4 Case outline(s). The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style               |

|----------------|------------------------|------------------|-----------------------------|

| X              | CMGA2-PN               | 68               | Pin grid array package      |

| V              | See figure 1           | 68               | Leaded chip carrier package |

1.3 Absolute maximum ratings.

| Supply voltage range $(V_{CC})$                                          | -0.3 V dc to +7.0 V dc |

|--------------------------------------------------------------------------|------------------------|

| Supply voltage range $(V_{CC})$ Storage temperature range $(T_{CC})$     | -65°C to +150°C        |

| Case operating temperature range $(T_C)$                                 | -55°C to +125°C        |

| Maximum power dissipation $(P_0)$ Lead temperature (soldering 5 seconds) | U./5 W                 |

| Lead temperature (soldering 5 seconds)                                   | 270 °C                 |

| Junction temperature $(T_1)$                                             | 150 °C                 |

| Thermal resistance, junction to case (01c):                              |                        |

| Case X                                                                   | See MIL-STD-1835       |

| Case Y                                                                   | 10°C/W                 |

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-89463 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 2    |

| Supply voltage (V <sub>CC</sub> )                     | 2.0 V dc to V <sub>CC</sub> |

|-------------------------------------------------------|-----------------------------|

| ow level input voltage (logic inputs)( $V_{II}^{1}$ ) | GND -0.3 V to 0.8 V         |

| inimum high level output voltage (V <sub>OH</sub> )   | 2.4 V dc                    |

| Maximum low level output Voltage $(V_{01})$           | 0.5 V dc                    |

| requency of operation:                                |                             |

| Device type 01                                        | 12.5 to 16.67 MHz           |

| Device type 02                                        | 12.5 to 20.0 MHz            |

| Device type 03                                        | 12.5 to 25 MHz              |

| Device type 04                                        |                             |

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standard, and bulletin</u>. Unless otherwise specified, the following specification, standard, and bulletin of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

MILITARY

MIL-M-38510

- Microcircuits, General Specification for.

STANDARD

MILITARY

MIL-STD-883 MIL-STD-1835 Test Methods and Procedures for Microelectronics.

- Microcircuit Case Outlines.

BULLETIN

MILITARY

MIL-BUL-103

- List of Standardized Military Drawings (SMD's).

(Copies of the specification, standard, and bulletin required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

- 2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

- 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- $3.2~\underline{\text{Design, construction, and physical dimensions}}$ . The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89463 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 3    |

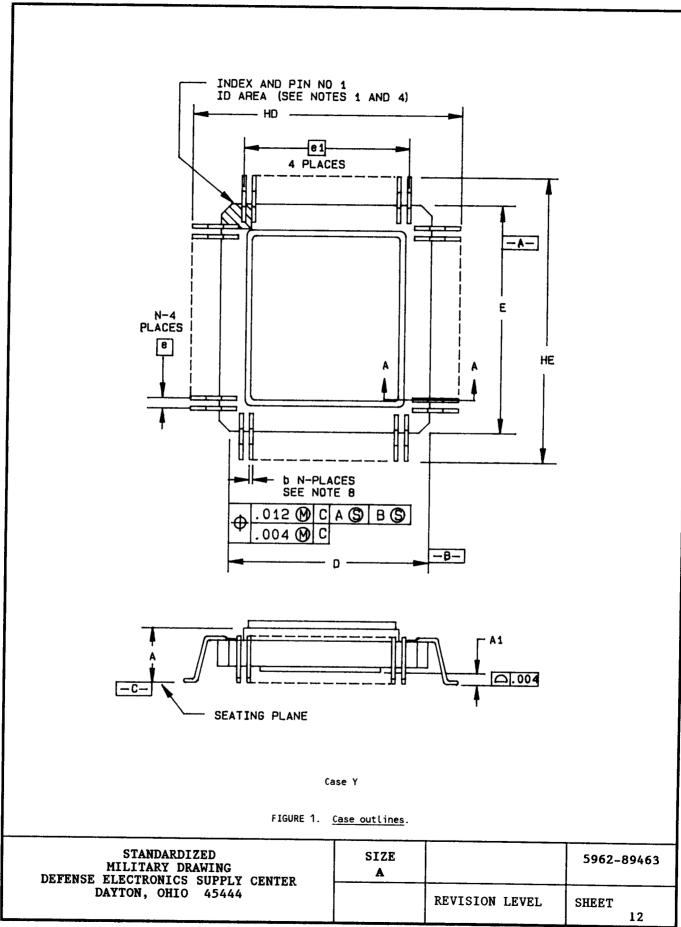

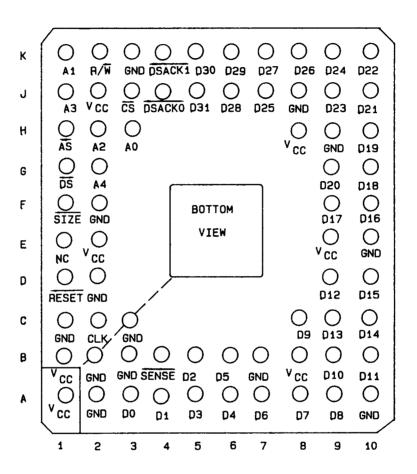

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.2 herein and figure 1.

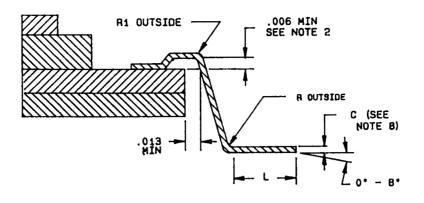

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

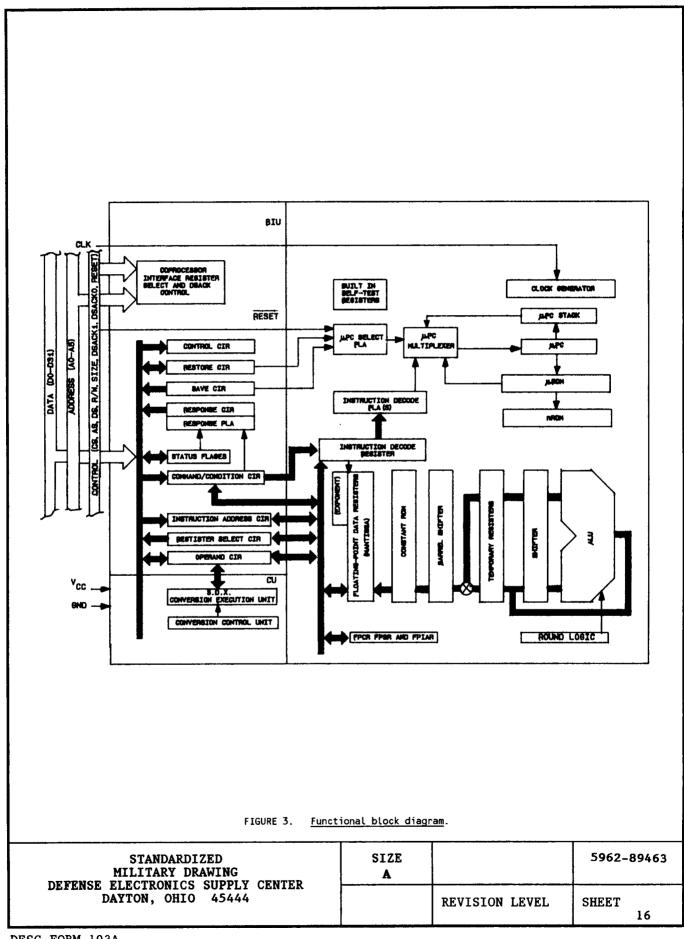

- 3.2.3 <u>Functional block diagram</u>. The functional block diagram shall be as specified on figure 3.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103 (see 6.7 herein).

- 3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7 herein). The certificate of compliance submitted to DESC-ECC prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change. Notification of change to DESC-ECC shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.9 <u>Verification and review</u>. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- Test condition A or D using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89463 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 4    |

| Test                                                                 | Symbol              | Conditions 1/                                                                                                                                               | Group A              | Device               | Limi                          | ts                            | Unit       |

|----------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-------------------------------|-------------------------------|------------|

|                                                                      |                     | $-55^{\circ}\text{C} \le T_{\text{C}} \le +125^{\circ}\text{C}$<br>$4.5 \text{ V} \le \text{V}_{\text{CC}} \le 5.5 \text{ V}$<br>unless otherwise specified | subgroups            | type                 | Min                           | Max                           |            |

| Input high voltage                                                   | N <sup>IH</sup>     |                                                                                                                                                             | 1, 2, 3              | A11                  | 2.0                           | v <sub>cc</sub>               | v          |

| Input low voltage                                                    | VIL                 |                                                                                                                                                             |                      |                      | -0.3                          | 0.8                           |            |

| Input leakage current<br>CLK, RESET, R/W, A0-A4,<br>CS, DS, AS, SIZE | IIN                 | V <sub>CC</sub> = 5.5 V                                                                                                                                     |                      |                      | -                             | 10                            | μΑ         |

| High-impedance(off-state)<br>DSACKO, DSACK1, DO - D31                | I <sub>TSI</sub>    | V <sub>IN</sub> = 2.4 V / 0.4 V                                                                                                                             |                      |                      | -                             | 20                            |            |

| Supply current <u>2</u> /                                            | 1 <sub>CC</sub>     | V <sub>CC</sub> = 5.5 V                                                                                                                                     |                      |                      | -                             | 150                           | mA .       |

| Output low current 3/<br>(V <sub>OL</sub> = GND) SENSE               | I <sub>OL</sub>     |                                                                                                                                                             |                      |                      | -                             | 500                           | μΑ         |

| High-level output voltage<br>DSACKO, DSACK1, DO - D31                | v <sub>OH</sub><br> | I <sub>OH</sub> = -400 μA                                                                                                                                   |                      |                      | 2.4                           | -                             | V          |

| Low-level output voltage<br>DSACKO, DSACK1, DO - D31                 | v <sub>OL</sub>     | I <sub>OL</sub> = 5.3 mA                                                                                                                                    | -<br> <br> <br> <br> |                      | -                             | 0.5                           |            |

| Input capacitance                                                    | CIN                 | V <sub>IN</sub> = 0.0 V<br>f = 1MHz, see 4.3.1c                                                                                                             | 4                    |                      | -                             | 20                            | pF         |

| Functional testing                                                   |                     | See 4.3.1d, V <sub>CC</sub> = 4.5 V                                                                                                                         | 7, 8                 | A11                  |                               |                               |            |

| Frequency of operation <u>4</u> /                                    | f <sub>MAX</sub>    | GND = 0.0 V                                                                                                                                                 |                      | 01<br>02<br>03<br>04 | 12.5<br>12.5<br>12.5<br>16.67 | 16.7<br>20.0<br>25.0<br>33.33 | MHz        |

| Cycle time                                                           | 1                   | See figure 4                                                                                                                                                | 9, 10, 11            | 01<br>02<br>03<br>04 | 60<br>50<br>40<br>30          | 125<br>80<br>80<br>60         | ns         |

| Clock pulse width<br>(Measured from 1.5 V to<br>1.5 V for 33 MHz)    | 2, 3                |                                                                                                                                                             |                      | 01<br>02<br>03<br>04 | 24<br>20<br>15<br>14          | 95<br>54<br>59<br>42          |            |

| See footnotes at end of ta                                           | ble.                | <del></del>                                                                                                                                                 | <u> </u>             |                      | -1                            |                               |            |

| STANDARDIZED<br>MILITARY DRAWING                                     |                     | WING                                                                                                                                                        | SIZE<br>A            |                      |                               |                               | 5962-89463 |

| DEFENSE ELECTRO<br>DAYTON,                                           |                     |                                                                                                                                                             |                      | REVIS                | ION LEV                       | EL                            | SHEET 5    |

TABLE I. <u>Electrical performance characteristics</u> - continued.

| Test                                               | Symbol     | Conditions <u>1</u> /<br>  -55°C ≤ T <sub>C</sub> ≤ +125°C                                                                                                                | Group A<br>subgroups | Device<br>type       | Lir                  | nits                 | _ Unit                    |

|----------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|---------------------------|

|                                                    |            | $-55^{\circ}\text{C} \le \text{T}_{\text{C}} \le +125^{\circ}\text{C}$<br>$4.5 \text{ V} \le \text{V}_{\text{CC}} \le 5.5 \text{ V}$<br><u>unless otherwise specified</u> | <b>3</b>             |                      | Min                  | Max                  |                           |

| Clock fall time                                    | 4          | See figure 4                                                                                                                                                              | 9, 10, 11            | 01<br>02<br>03<br>04 |                      | 5<br>5<br>4<br>3     | ns                        |

| Clock rise time                                    | 5          |                                                                                                                                                                           |                      | 01<br>02<br>03<br>04 |                      | 5<br>5<br>4<br>3     |                           |

| Address valid to AS asserted <u>5</u> /            | 6          |                                                                                                                                                                           |                      | 01<br>02<br>03<br>04 | 15<br>10<br>5<br>5   | Peter and the second |                           |

| Address valid to DS<br>asserted (read) <u>5</u> /  | 6A         |                                                                                                                                                                           |                      | 01<br>02<br>03<br>04 | 15<br>10<br>5<br>5   |                      |                           |

| Address valid to DS<br>asserted (write) <u>5</u> / | 6B         |                                                                                                                                                                           |                      | 01<br>02<br>03<br>04 | 50<br>50<br>35<br>26 |                      |                           |

| AS negated to address invalid <u>6</u> /           | 7          |                                                                                                                                                                           |                      | 01<br>02<br>03<br>04 | 10<br>10<br>5<br>5   |                      | - <br> <br> <br> <br>     |

| DS negated to address invalid <u>6</u> /           | 7 <b>A</b> |                                                                                                                                                                           |                      | 01<br>02<br>03<br>04 | 10<br>10<br>5<br>5   |                      | -<br> <br> <br> <br> <br> |

| CS negated to AS asserted 7/                       | 8          |                                                                                                                                                                           |                      | 01<br>02<br>03<br>04 | 0 0                  |                      | -                         |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 59626-89463 |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>6  |

TABLE I. <u>Electrical performance characteristics</u> - continued.

| Test                                                                    | Symbol | Conditions 1/                                                                                                                                                      | Group A   | Device               | Limi                       | ts                                      | Unit         |

|-------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|----------------------------|-----------------------------------------|--------------|

|                                                                         |        | $-55^{\circ}\text{C} \le \text{T}_{\text{C}} \le +125^{\circ}\text{C}$<br>$4.5 \text{ V} \le \text{V}_{\text{CC}} \le 5.5 \text{ V}$<br>unless otherwise specified | subgroups | type                 | Min                        | Max                                     | <u> </u><br> |

| CS negated to DS asserted (read) 7/                                     | 8A     | See figure 4                                                                                                                                                       | 9, 10, 11 | 01<br>02<br>03<br>04 | 0 0                        |                                         | ns           |

| CS asserted to DS asserted (write)                                      | 8B     |                                                                                                                                                                    |           | 01<br>02<br>03<br>04 | 30<br>  25<br>  20<br>  15 |                                         |              |

| AS negated to CS<br>negated                                             | 9      |                                                                                                                                                                    |           | 01<br>02<br>03<br>04 | 10<br>10<br>5<br>5         |                                         |              |

| DS negated to CS<br>negated                                             | 9A     |                                                                                                                                                                    |           | 01<br>02<br>03<br>04 | 10<br>10<br>5<br>5         |                                         |              |

| R/W high to AS<br>asserted (read)                                       | 10     |                                                                                                                                                                    |           | 01<br>02<br>03<br>04 | 15<br>10<br>5<br>5         |                                         |              |

| R/W high to DS<br>asserted (read)                                       | 10A    |                                                                                                                                                                    |           | 01<br>02<br>03<br>04 | 15<br>10<br>5<br>5         |                                         |              |

| R/W low to DS<br>asserted (write)                                       | 10B    |                                                                                                                                                                    |           | 01<br>02<br>03<br>04 | 35<br>30<br>25<br>25       |                                         |              |

| AS negated to R/W<br>low (read) or<br>AS negated to R/W<br>high (write) | 11     |                                                                                                                                                                    |           | 01<br>02<br>03<br>04 | 10<br>10<br>5<br>5         | *************************************** |              |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-89463 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 7    |

TABLE I. <u>Electrical performance characteristics</u> - continued.

| Test                                                                    | Symbol | Conditions <u>1</u> /                                                                                                                                        | Group A subgroups | Device<br>type       | Limi                 | ts                   | Unit |

|-------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------|----------------------|----------------------|------|

|                                                                         |        | $-55^{\circ}\text{C} \le T_{\text{C}} \le +125^{\circ}\text{C}$<br>$4.5 \text{ V} \le \text{V}_{\text{CC}} \le 5.5 \text{ V}$<br> unless otherwise specified | Jaby, caps        | Сурс                 | Min                  | Max                  |      |

| DS negated to R/W<br>low (read) or<br>DS negated to R/W<br>high (write) | 11A    | See figure 4                                                                                                                                                 | 9, 10, 11         | 01<br>02<br>03<br>04 | 10<br>10<br>5<br>5   |                      | ns   |

| DS width asserted<br>(write)                                            | 12     |                                                                                                                                                              |                   | 01<br>02<br>03<br>04 | 40<br>38<br>30<br>23 |                      |      |

| DS width negated 3/                                                     | 13     |                                                                                                                                                              |                   | 01<br>02<br>03<br>04 | 40<br>38<br>30<br>23 |                      |      |

| DS negated to AS asserted <u>3</u> / <u>8</u> /                         | 13A    |                                                                                                                                                              |                   | 01<br>02<br>03<br>04 | 30<br>30<br>25<br>18 |                      |      |

| CS, DS asserted to data out valid (read) <u>9</u> /                     | 14     |                                                                                                                                                              |                   | 01<br>02<br>03<br>04 |                      | 80<br>45<br>45<br>30 |      |

| DS negated to data<br>out invalid (read)                                | 15     |                                                                                                                                                              |                   | 01<br>02<br>03<br>04 | 0 0 0                |                      |      |

| DS negated to data out high impedance (read) <u>3</u> /                 | 16     |                                                                                                                                                              |                   | 01<br>02<br>03<br>04 |                      | 50<br>30<br>30<br>30 |      |

| Data in valid to DS<br>asserted (write)                                 | 17     | <br> <br>                                                                                                                                                    |                   | 01<br>02<br>03<br>04 | 15<br>10<br>5<br>5   |                      |      |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-89463 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 8    |

TABLE I. <u>Electrical performance characteristics</u> - continued.

| Test                                                                         | Symbol | Conditions 1/                                                                                                                                               | Group A   | Device               | Li                          | mits                  | Unit |

|------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|-----------------------------|-----------------------|------|

|                                                                              |        | $-55^{\circ}\text{C} \le T_{\text{C}} \le +125^{\circ}\text{C}$<br>$4.5 \text{ V} \le \text{V}_{\text{CC}} \le 5.5 \text{ V}$<br>unless otherwise specified | subgroups | type                 | Min                         | Max                   |      |

| DS negated to data<br>in invalid<br>(write)                                  | 18     | See figure 4                                                                                                                                                | 9, 10, 11 | 01<br>02<br>03<br>04 | 15<br>10<br>5<br>5          |                       | ns   |

| START true to DSACKO<br>and DSACK1 asserted<br><u>9</u> /                    | 19     |                                                                                                                                                             |           | 01<br>02<br>03<br>04 |                             | 50<br>35<br>25<br>20  |      |

| DSACKO asserted to<br>DSACKI asserted<br>(skew) <u>10</u> /                  | 19A    |                                                                                                                                                             |           | 01<br>02<br>03<br>04 | <br>  -15<br>  -10<br>  -10 | 15<br>10<br>10<br>5   |      |

| DSACKO or DSACK1<br>asserted to data<br>out valid                            | 20     |                                                                                                                                                             |           | 01<br>02<br>03<br>04 |                             | 50<br>43<br>32<br>17  |      |

| START false to DSACKO<br>and DSACK1 negated<br><u>11</u> /                   | 21     |                                                                                                                                                             |           | 01<br>02<br>03<br>04 |                             | 50<br>40<br>30<br>30  |      |

| START false to DSACKO<br>and DSACK1 high<br>impedance <u>3</u> / <u>11</u> / | 22     |                                                                                                                                                             |           | 01<br>02<br>03<br>04 |                             | 70<br>55<br>55<br>40  |      |

| START true to clock<br>high (synchronous<br>read) <u>11/ 12</u> /            | 23     |                                                                                                                                                             |           | 01<br>02<br>03<br>04 | 0 0                         |                       |      |

| Clock low to data out valid (synchronous read) <u>12</u> /                   | 24     |                                                                                                                                                             |           | 01<br>02<br>03<br>04 |                             | 105<br>80<br>60<br>45 |      |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-89463 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 9    |

TABLE I. <u>Electrical performance characteristics</u> - continued.

| Test                                                           | Symbol | Conditions $1/$ $-55^{\circ}C \le T_C \le +125^{\circ}C$ $4.5 \ V \le V_{CC} \le 5.5 \ V$ Unless otherwise specified | Group A<br>subgroups | Device<br>type       |     | mits                 | Unit       |

|----------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-----|----------------------|------------|

|                                                                |        | unless otherwise specified                                                                                           |                      |                      | Min | Max                  | 1          |

| START true to data out valid                                   | 25     |                                                                                                                      | 9, 10, 11            | 01                   | 1.5 | 105+<br>2.5          | ns         |

| (synchronous read)<br>11/ 12/ 13/                              |        |                                                                                                                      |                      | 02                   | 1.5 | 80+<br>2.5           | ns<br>clks |

|                                                                |        |                                                                                                                      |                      | 03                   | 1.5 | 60+<br>2.5           | ns<br>clks |

|                                                                |        |                                                                                                                      |                      | 04                   | 1.5 | 45+<br>2.5           | ns<br>clks |

| Clock low to DSACKO and DSACK1 asserted (synchronous read) 12/ | 26     |                                                                                                                      |                      | 01<br>02<br>03<br>04 |     | 75<br>55<br>45<br>30 | ns         |

| START true to DSACKO<br>and DSACK1 asserted                    | 27     |                                                                                                                      |                      | 01                   | 1.5 | 75+<br>2.5           | ns         |

| (synchronous read)<br>11/ 12/ 13/                              |        | į<br>į                                                                                                               |                      | 02                   | 1.5 | 55+<br>2.5           | ns<br>clks |

| سے سے سے                                                       |        | İ                                                                                                                    |                      | 03                   | 1.5 | 45+<br>2.5           | ns<br>clks |

|                                                                |        |                                                                                                                      |                      | 04                   | 1.5 | 30+<br>2.5           | ns         |

- The following pins are active low: AS, CS, DS, DSACKO, DSACKI, RESET, W of R/W, SENSE, SIZE. Unless otherwise specified, test conditions shall be at worst case condition.

- $\underline{2}$ / All outputs unloaded except for load capacitance. Clock at  $f_{Max}$ . Part in reset.

- $\underline{\mathbf{3}}'$  Tested initially and at process and design changes. Thereafter guaranteed, if not tested, to the limits specified in table I.

- 4/ -55°C ≤ TC ≤ +125°C in a power-off condition under thermal soak for 4 minutes minimum or until thermal equilibrium. Electrical parameters are tested instant on 100 ms after power is applied.

- 5/ If the SIZE pin is not strapped to either  $V_{CC}$  or GND, it must have same setup times as do address.

- $\underline{6}$ / If the SIZE pin is not strapped to either  $V_{CC}$  or GND, it must have same hold times as do address.

- 7/ If a subsequent access is not a FPCP access, CS must be negated before the assertion of AS and or DS on the non-FPCP

- 8/ This specification only applies to systems in which back-to-back accesses (read-write or write-write) of the coprocessor interface operand can occur. When the device is used as a coprocessor to the main processor, this can occur when the addressing mode is immediate.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-89463 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 10   |

- 9/ These specifications only apply if the device had completed all operations initiated by the termination of the previous bus cycle when DS was negated. Bus cycles which initiate operations in this manner are: Write to coprocessor interface control register LSB.

- Write to coprocessor interface restore register LSB.

- Last write to coprocessor interface operand register LSB during restore with "busy" state size.

- First read to coprocessor interface operand register LSB during save "idle" or "busy" state size.

Following one of these bus cycles, all operations are completed within four clocks after DS is negated. If an asynchronous read/write bus cycle is attempted prior to the completion of these operations, the new bus cycle is postponed by DSACKO-DSACK1 (and data for reads) being withheld. DSACKO-DSACK1 (and data for reads) are also withheld on asynchronous reads/writes of the coprocessor interface operand register and register selector register when the MPU overturns the device. Since the device clock may be much slower than the MPU's clock, these registers cold be empty/full when the MPU attempts to read/write.

- 10/ This number can be reduced to 5 ns if DSACKO and DSACKI have equal loads.

- 11/ START is not an external signal, rather it is logical condition that indicates the start of an access. The logical equation for this condition is: START = CS+AS + (R/W.DS).

- $\underline{12}$ / Synchronous reads occur only when the coprocessor interface save register or response register locations are read.

- 13/ Value depends on actual clock input waveform used and not clock input specifications.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89463 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 11   |

SECTION A-A

|        | Case Y |          |          |         |  |  |

|--------|--------|----------|----------|---------|--|--|

| Symbol | I      | nches    | Mill     | imeters |  |  |

|        | Min    | Max      | Min      | Max     |  |  |

| A      |        | .125     |          | 3.18    |  |  |

| A1     | .018   | .035     | 0.16     | 0.89    |  |  |

| b      | .018   | .030     | 0.16     | 0.76    |  |  |

| С      | .005   | .010     | 0.13     | 0.25    |  |  |

| D/E    | .940   | .960     | 23.88    | 24.38   |  |  |

| е      | .0     | 50 BSC   | 1.28 BSC |         |  |  |

| e1     | .80    | .800 BSC |          | 32 BSC  |  |  |

| HD/HE  | 1.133  | 1.147    | 28.78    | 29.13   |  |  |

| L      | .024   | .040     | 0.61     | 1.02    |  |  |

| N      | 68     |          | 6        | 58      |  |  |

| R      | .011   | .034     | 0.28     | 0.87    |  |  |

| R1     | .009   |          | 0.23     |         |  |  |

## NOTES:

- 1. A terminal 1 identification mark shall be located at the index corner in the shaded area shown. Terminal 1 is located immediately adjacent to and counterclockwise from the index corner. Terminal numbers increase in a counterclockwise direction when viewed as shown.

- 2. Generic lead attach dogleg depiction.

- 3. Dimension N: Number of terminals.

- 4. Corner shapes (square, notch, radius, etc.) may vary from that shown on the drawing. The index corner shall be clearly unique.

- 5. Metric equivalents are given for general information only.6. Controlling dimension: Inch.

- 7. Datums X and Y to be determined where center leads exit the body.

- 8. Dimension b and c include lead finish

FIGURE 1. <u>Case outlines</u> - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89463 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 13   |

#### All device types

Case X

# Bottom view

FIGURE 2. <u>Terminal connections</u>.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89463 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET      |

# All device types Case Y NC GND GND GND D0 D1 D2 D2 D3 D5 D5 D6 D5 D6 D7 51 VCC ⊏ \_\_\_ D9 CLKIN = D10 GND F D11 RESET = D12 NC E D13 V CC = D14 V CC = TOP D15 SIZE = V CC VIEW GND C ⊐ ∨ ლ CASE DS c **GND** AS C D16 A4 C D17 A3 E D18 ¥5 = D19 A1 = D20 A0 = D21 V CC \_\_\_\_\_ □ GND 35 DSACKO DSACK1 D31 D29 D28 D27 D26 D25 D25 D27 CCC D22 NC = No connection FIGURE 2. Terminal connections - Continued. **STANDARDIZED** SIZE 5962-89463 MILITARY DRAWING A DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 SHEET REVISION LEVEL

15

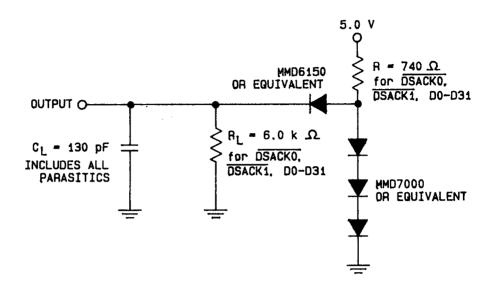

## Test circuit

NOTE: Equivalent loading may be simulated by the tester.

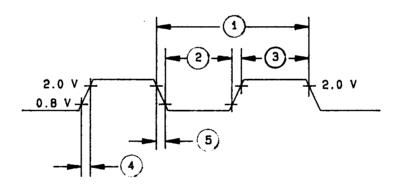

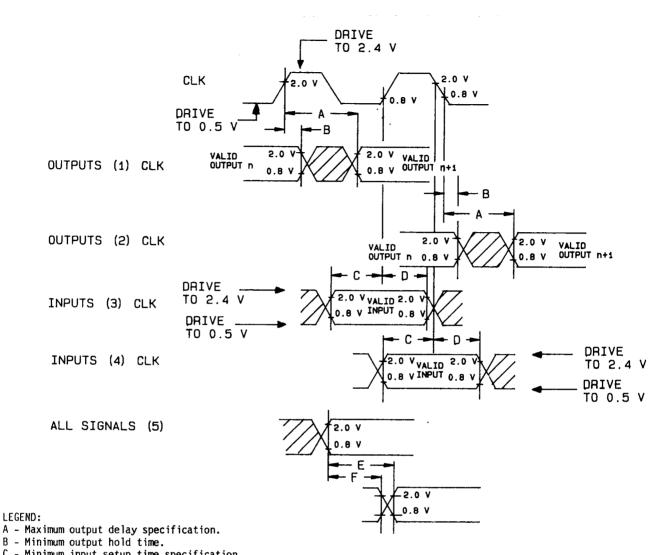

Clock input AC timing diagram

NOTE: Timing measurements are referenced to and from a low voltage of 0.8 volt and a high voltage of 2.0 volts, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise and fall will be linear between 0.8 and 2.0 volts.

FIGURE 4. Switching waveforms and test circuit

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89463 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 17   |

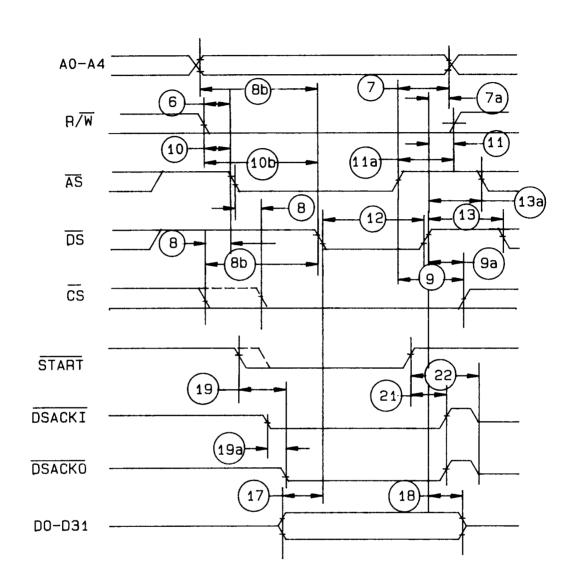

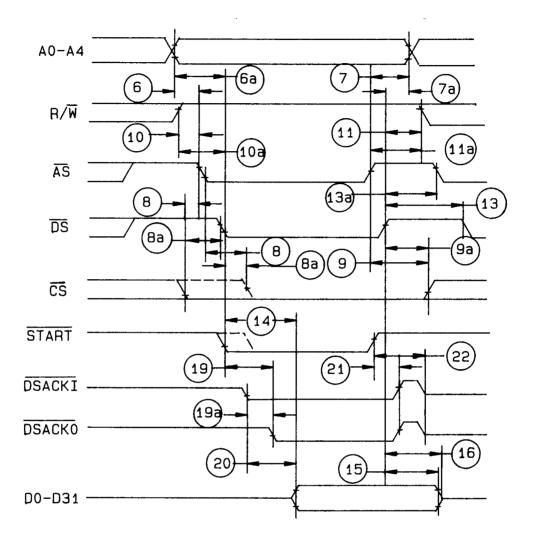

ASYNCHRONOUS WRITE CYCLE TIMING DIAGRAM

FIGURE 4. <u>Switching waveforms and test circuit</u> - Continued.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89463  |

|-----------------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                                    |           | REVISION LEVEL | SHEET<br>18 |

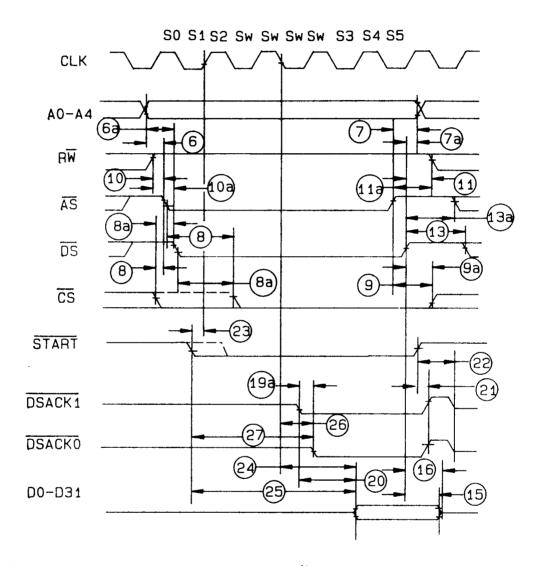

ASYNCHRONOUS READ CYCLE TIMING DIAGRAM

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89463  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>19 |

SYNCHRONOUS READ CYCLE TIMING DIAGRAM

FIGURE 4. <u>Switching waveforms and test circuit</u> - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89463  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>20 |

- C Minimum input setup time specification.

- D Minimum input hold time specification.

- E Signal valid to signal valid specification (maximum or minimum).

- F Signal valid to signal invalid specification (maximum or minimum).

## DRIVE LEVELS AND TEST POINTS FOR AC SPECIFICATION

#### NOTES:

- This output timing is applicable to all parameters specified relative to the rising edge of the clock.

This output timing is applicable to all parameters specified relative to the falling edge of the clock.

- 3. This input timing is applicable to all parameters specified relative to the rising edge of the clock.

- 4. This input timing is applicable to all parameters specified relative to the falling edge of the clock.5. This timing is applicable to all parameters specified relative to the assertion/negation of another signal.

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89463 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 21   |

| 8 - BIT  |

|----------|

|          |

| 16 - BIT |

| 32 - BIT |

|          |

## SYSTEM BUS SIZE CONFIGURATIONS

| DATA BUS | A4 | DSACK1' | DSACKO' | COMMENTS                                      |

|----------|----|---------|---------|-----------------------------------------------|

| 32 - BIT | 1  | LOW     | LOW     | VALID DATA ON D31-D0                          |

| 32 - BIT | 0  | LOW     | HIGH    | VALID DATA ON D31-D16                         |

| 16 - BIT | х  | LOW     | HIGH    | VALID DATA ON D31-D16 OR D15-D0               |

| 8 - BIT  | Х  | HIGH    | LOW     | VALID DATA ON D31-D24, D23-D16, D15-D8, D7-D0 |

| ALL      | x  | HIGH    | HIGH    | INSERT WAIT STATES IN CURRENT<br>BUS CYCLE    |

## DSACK ASSERTIONS

NOTE: ' = Asserted LOW

# SYSTEM BUS SIZE CONFIGURATIONS AND DSACK ASSERTIONS

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARDIZED MILITARY DRAWING DEFENCE ELECTRONICS SIDDLY CENTER | SIZE<br>A |                | 5962-89463 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444            |           | REVISION LEVEL | SHEET 22   |

TABLE II. Electrical test requirements.

| MIL-STD-883 test requirements                                | Subgroups<br>(per method<br>5005, table I) |

|--------------------------------------------------------------|--------------------------------------------|

| Interim electrical parameters<br>  (method 5004)             | 1,7,9                                      |

| <br>  Final electrical test parameters<br>  (method 5004)    | 1*,2,3,7*,<br>8a,9,10,11                   |

| <br>  Group A test requirements<br>  (method 5005)           | 1,2,3,4,7,<br>8a,9,10,11                   |

| Groups C and D end-point electrical parameters (method 5005) | 2,7,8a,<br>9,10                            |

<sup>\*</sup> PDA applies to subgroup 1 and 7.

4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

#### 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 ( $C_{IN}$  measurement) shall be measured only for the initial test and after process or design changes which may affect input capacitance. A minimum sample size of 5 devices with zero rejects shall be required.

- d. Subgroups 7 and 8 shall include verification of the instruction set. The instruction set forms a part of the vendors test tape and shall be maintained and available from the approved sources of supply.

## 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- Test condition A or D using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125$ °C, minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-89463 |

|---------------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                             |           | REVISION LEVEL | SHEET 23   |

- 5. PACKAGING

- 5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

- 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-481 using DD Form 1693, Engineering Change Proposal (Short Form).

- 6.4 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a <u>system application</u> requires configuration control and the applicable SMD. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronics devices (FSC 5962) should contact DESC-ECC, telephone (513) 296-6022.

- 6.5 Comments. Comments on this drawing should be directed to DESC-ECC, Dayton, Ohio 45444, or telephone (513) 296-8525.

- 6.6 Symbols, definitions, and functional descriptions.

#### A0 - A4 (Address bus)

These active-high address line inputs are used by the main processor to select the coprocessor interface register locations located in the CPU address space. When the device is configured to operate over an 8-bit system data bus, the AO pin is used as an address lead for byte accesses of the coprocessor interface registers. When the device configured to operate over a 16- or 32-bit system data bus, both the AO and  $\overline{\text{SIZE}}$  pins are strapped high and/or low as listed in Table 1A.

## DO - D31 (Data bus)

This 32-bit, bidirectional, three-state bus serves as the general-purpose data path between the main processor and the device. Regardless of whether the device is operated as a coprocessor or a peripheral processor, all interprocessor transfers of instruction information, operand data, status information, and requests for service occur as standard similar family bus cycles. The device may be configured to operate over an  $8-, \underline{16-}$ , or 32-bit system data bus. Depending upon the system data bus configuration, both the AO and  $\overline{\text{SIZE}}$  pins are configured specifically for the applicable bus configuration. (Refer to address bus (AO through A5) and  $\overline{\text{SIZE}}$  for further information.

### ST7F

This active low input signal is used in conjunction with the AO pin to configure the device for operation over an 8-, 16-, or 32-bit system data bus. When the device is configured to operate over a 16-, or 32-bit system data bus, both the  $\overline{\text{SIZE}}$  and AO pins are strapped high and/or low as listed at the end of figure 4.

| STANDARDIZED  MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-89463 |

|-------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                     |           | REVISION LEVEL | SHEET 24   |

### 6.6 Symbols, definitions, and functional descriptions - Continued.

## AS (Address strobe)

This active low input signal indicates that there is a valid address on the bus, and both the chip select  $\overline{CS}$  and Read/Write  $(R/\overline{W})$  signal lines are valid.

### CS (Chip select)

This active low input signal enables the main processor access to the device coprocessor interface registers. When operating the device as a peripheral processor the Chip Select decode is system dependent (i.e., like the Chip Select on any peripheral). The  $(\overline{CS})$  signal must be valid as  $(\overline{AS})$  is asserted.

## R/W (Read/Write)

This active low input signal indicates the direction of a bus transaction (read/write) by the main processor. A logic high (1) indicates a read from device and a low (0) indicates a write to the device. The  $R/\overline{W}$  signal must be valid when  $\overline{AS}$  is asserted.

### DS (Data strobe)

This active low input signal indicates that there is a valid data on the data bus during a write bus cycle.

### RESET

This active-low input signal causes the device to initialize the floating-point data registers to nonsignaling not-a-numbers (NANs) and clears the floating-point control, status, and instruction address registers. When performing a power-up reset, the external circuitry should keep the RESET line asserted for a minimum of four clock cycles after  $V_{CC}$  is within tolerance. This assures correct initialization of the device when power is applied. For compatibility with all family devices, 100ms should be used at the minimum. When performing a reset after the device  $V_{CC}$  has been within tolerance for more than the initial power-up time, the RESET line must have an asserted pulse width which is greater than two clock cycles. For compatibility with all similar family devices, 10-clock cycles should be used as the minimum.

### CLK (Clock)

The device clock input is a TTL-compatible signal that is internally buffered for development of the internal clock signals. The clock input must be a constant frequency square wave.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89463 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 25   |

## 6.6 Symbols, definitions, and functional descriptions - continued.

DSACKO, DSACK1 (Data transfer and size acknowledge)

These active-low, three-state output signals indicate the <u>completion of bus cycle</u> to the main processor. The device assert either one or both of the (DSACKO) and (DSACKI) <u>signals</u> upon <u>receipt</u> of a CS assertion. If the bus cycle is a main processor read, the device asserts DSACKO and DSACKI signals to indicate that the information on the data bus is valid. (Both the DSACK signals may be asserted in advance of the valid data being placed on the bus.) If the bus cycle is a main processor write to the device, DSACKO and DSACKI are used to acknowledge acceptance of the data by the device.

The device also uses DSACKO and DSACKI signals to dynamically indicate to the main processor to "port" size (system data bus width) on a cycle-by cycle basis. Depending upon which of the two DSACK pins are asserted in a given busccle, the main processor will assume data has been transferred to/from an 8-, 16-, or 32-bit wide data port. Table 1 lists the DSACK assertions that are used by the device for the various bus cycles over the various system data bus configurations. Figure 4 indicates that all accesses where A4 equals zero are to be 16-bit registers. The device implements all 16-bit coprocessor interface registers on data lines D16-D31; the main processor expects 16-bit registers that are located in a 32-bit port at odd word addresses (A1=1) to be implemented on data lines D0-D15. For accesses to these registers when configured for 32-bit bus operation, the device generates DSACK signals as listed in Table 1 to inform the main processor of valid data on D16-D31 instead of D0-D15. An external holding register is required to maintain both DSACKO and DSACKI high between bus cycles. The DSACKO and DSACKI lines are actively pulled up (negated) by the device following the rising edge of the AS and both DSACK lines are then three-stated (high-impedance state) to avoid interference with the next bus cycle.

#### SENSE

This pin may optionally be used as an additional GND pin, or as an indicator to external hardware that the device is present in the system. This signal is internally connected to the GND of the die, but it is not necessary to connect it to the external ground for correct device operation. If a pull-up resistor is connected to this pin, external hardware may sense the presense of the device in a system. If the pin floats high, the coprocessor is not installed; while the pin will be pulled low if the device is installed in the system.

V<sub>CC</sub> and GND (Power and ground)

These pins provide the supply voltage and system reference level for the internal circuitry of the device. Care should be taken to reduce the noise level on these pins with appropriate capacitive decoupling.

6.7 <u>Approved sources of supply</u>. Approved sources of supply are listed in MIL-BUL-103. The vendors listed in MIL-BUL-103 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DESC-ECC.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-89463 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 26   |

DESC FORM 193A JUL 91