### TDA8045

#### **FEATURES**

- Different modulation schemes: 4, 16, 32 and 64-QAM

- Digital demodulator and Square-Root Raised-Cosine Nyquist filter with roll-off of 20%

- High performance adaptive equalizer (no training sequence needed)

- · Digital detectors for generation of required control voltages for carrier recovery, clock recovery and AGC

- · Digital-to-Analog Converters (DACs) and operational amplifiers allowing high flexibility for selection of the (PLL) loop time constants

- High maximum symbol frequency: 7 Msymbols/s

- · Input format: straight binary or twos complement (up to 9 bits, TTL compatible)

- Output format: 7-bit wide bus (CMOS compatible)

- I2C-bus interface to initialize and monitor the demodulator. When no I2C usage: 64-QAM in default mode, soft or hard decision output for FEC (pin SHND)

- 5 V supply voltage

- Boundary Scan Test.

#### **APPLICATION**

Demodulation for digital cable TV.

#### QUICK REFERENCE DATA

| SYMBOL              | PARAMETER                              | CONDITIONS             | MIN. | TYP. | MAX. | UNIT       |

|---------------------|----------------------------------------|------------------------|------|------|------|------------|

| $V_{DD}$            | supply voltage                         | _                      | 4.75 | 5.00 | 5.25 | V          |

| I <sub>DD</sub>     | total supply current at 7 Msymbols/s   | $V_{DD} = 5 \text{ V}$ | -    | 260  | _    | mA         |

| f <sub>sym</sub>    | symbol frequency                       | _                      | -    | _    | 7    | Msymbols/s |

| 1L                  | implementation loss                    | notes 1 and 2          | -    | _    | 1    | dB         |

| α                   | Nyquist roll-off                       | _                      | ]-   | 20   |      | %          |

| SNR <sub>lock</sub> | SNR for locking a 64-QAM constellation | _                      | 21   | _    | _    | dB         |

### **Notes**

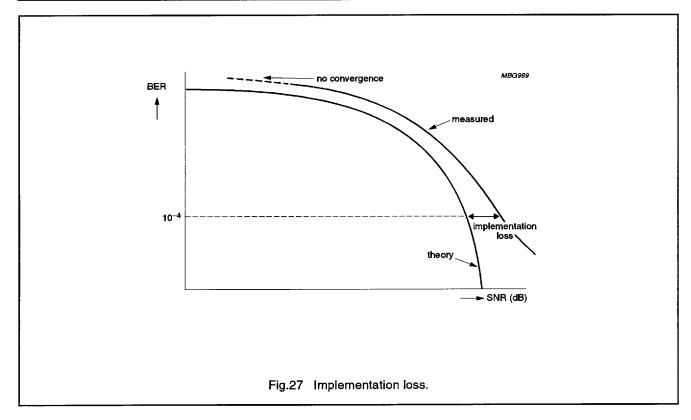

- The implementation loss, IL, of the demodulator is defined as the distance between the measured and theoretical BER curve as function of S/N at a BER = 10<sup>-6</sup> for a back-to-back measurement at the IF frequency. Of course, this performance depends on the chosen loop parameters (see "Application Note AN95088").

- 2. The demodulator should be able to acquire lock for a BER  $\geq 2 \times 10^{-3}$ , because the FEC can still handle this input error rate (see Fig.27).

#### ORDERING INFORMATION

| TYPE     |       | PACKAGE                                                                                      |          |  |  |  |

|----------|-------|----------------------------------------------------------------------------------------------|----------|--|--|--|

| NUMBER   | NAME  | DESCRIPTION                                                                                  | VERSION  |  |  |  |

| TDA8045H | QFP64 | plastic quad flat package; 64 leads (lead length 1.95 mm); body $14 \times 20 \times 2.8$ mm | SOT319-2 |  |  |  |

**TDA8045**

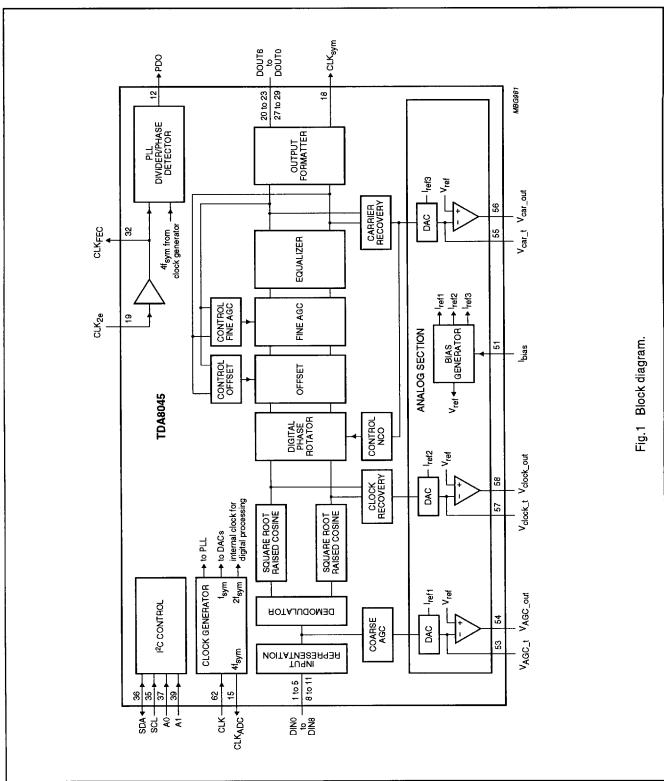

### **BLOCK DIAGRAM**

**TDA8045**

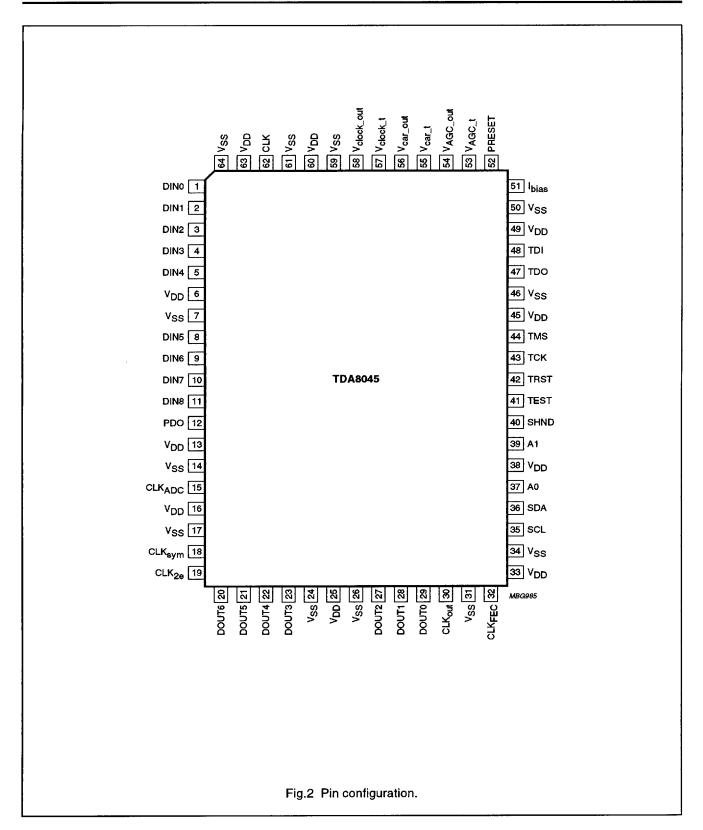

### **PINNING**

| SYMBOL             | PIN | 1/0    | DESCRIPTION                                                          |

|--------------------|-----|--------|----------------------------------------------------------------------|

| DIN0               | 1   | 1      | digital input bit 0 (LSB)                                            |

| DIN1               | 2   | I      | digital input bit 1                                                  |

| DIN2               | 3   | I      | digital input bit 2                                                  |

| DIN3               | 4   | 1      | digital input bit 3                                                  |

| DIN4               | 5   | ı      | digital input bit 4                                                  |

| V <sub>DD</sub>    | 6   | supply | positive supply voltage                                              |

| V <sub>SS</sub>    | 7   | supply | negative supply voltage                                              |

| DIN5               | 8   | 1      | digital input bit 5                                                  |

| DIN6               | 9   |        | digital input bit 6                                                  |

| DIN7               | 10  | ı      | digital input bit 7                                                  |

| DIN8               | 11  | 1      | digital input bit 8 (MSB)                                            |

| PDO                | 12  | 0      | PLL phase detector output                                            |

| $V_{DD}$           | 13  | supply | positive supply voltage                                              |

| V <sub>SS</sub>    | 14  | supply | negative supply voltage                                              |

| CLK <sub>ADC</sub> | 15  | 0      | clock output to Analog-to-Digital Converter (ADC); 4f <sub>sym</sub> |

| $V_{DD}$           | 16  | supply | positive supply voltage                                              |

| V <sub>SS</sub>    | 17  | supply | negative supply voltage                                              |

| CLK <sub>sym</sub> | 18  | 0      | symbol clock output (f <sub>sym</sub> )                              |

| CLK <sub>2e</sub>  | 19  | 1      | clock input for CLK <sub>FEC</sub> PLL and for test purposes         |

| DOUT6              | 20  | 0      | parallel data output (bit 6)                                         |

| DOUT5              | 21  | 0      | parallel data output (bit 5)                                         |

| DOUT4              | 22  | 0      | parallel data output (bit 4)                                         |

| DOUT3              | 23  | 0      | parallel data output (bit 3)                                         |

| Vss                | 24  | supply | negative supply voltage                                              |

| $V_{DD}$           | 25  | supply | positive supply voltage                                              |

| Vss                | 26  | supply | negative supply voltage                                              |

| DOUT2              | 27  | 0      | parallel data output (bit 2)                                         |

| DOUT1              | 28  | 0      | parallel data output (bit 1)                                         |

| DOUT0              | 29  | 0      | parallel data output (bit 0)                                         |

| CLKout             | 30  | 0      | clock output to FEC (2f <sub>sym</sub> )                             |

| V <sub>SS</sub>    | 31  | supply | negative supply voltage                                              |

| CLK <sub>FEC</sub> | 32  | 0      | clock output to FEC (16/3f <sub>sym</sub> )                          |

| $V_{DD}$           | 33  | supply | positive supply voltage                                              |

| V <sub>SS</sub>    | 34  | supply | negative supply voltage                                              |

| SCL                | 35  | 1      | serial clock of I <sup>2</sup> C-bus                                 |

| SDA                | 36  | I/O    | serial data of I <sup>2</sup> C-bus                                  |

| <b>A</b> 0         | 37  | ı      | I <sup>2</sup> C hardware address                                    |

| $V_{DD}$           | 38  | supply | positive supply voltage                                              |

| A1                 | 39  | I      | I <sup>2</sup> C hardware address                                    |

| SHND               | 40  | 1      | soft hard not decision (sets output mode)                            |

| SYMBOL                 | PIN | 1/0    | DESCRIPTION                               |  |

|------------------------|-----|--------|-------------------------------------------|--|

| TEST                   | 41  | ı      | test pin (normally connected to ground)   |  |

| TRST                   | 42  | l      | optional asynchronous reset               |  |

| TCK                    | 43  | l      | dedicated test clock                      |  |

| TMS                    | 44  | 1      | input control signal                      |  |

| $V_{DD}$               | 45  | supply | positive supply voltage                   |  |

| Vss                    | 46  | supply | negative supply voltage                   |  |

| TDO                    | 47  | 0      | serial test data out                      |  |

| TDI                    | 48  | l      | serial test data in                       |  |

| $V_{DD}$               | 49  | supply | positive supply voltage                   |  |

| Vss                    | 50  | supply | negative supply voltage                   |  |

| I <sub>bias</sub>      | 51  | I      | bias current for DAC                      |  |

| PRESET                 | 52  | ı      | set device into default mode              |  |

| $V_{AGC_t}$            | 53  | 0      | AGC time constant connection              |  |

| $V_{AGC\_out}$         | 54  | 0      | analog output for AGC                     |  |

| V <sub>car_t</sub>     | 55  | 0      | carrier recovery time constant connection |  |

| V <sub>car_out</sub>   | 56  | 0      | analog output for carrier recovery        |  |

| $V_{clock\_t}$         | 57  | 0      | clock recovery time constant connection   |  |

| V <sub>clock_out</sub> | 58  | 0      | analog output for clock recovery          |  |

| V <sub>SS</sub>        | 59  | supply | negative supply voltage                   |  |

| $V_{DD}$               | 60  | supply | positive supply voltage                   |  |

| V <sub>SS</sub>        | 61  | supply | negative supply voltage                   |  |

| CLK                    | 62  | 1      | clock (4f <sub>sym</sub> ) input          |  |

| $V_{DD}$               | 63  | supply | positive supply voltage                   |  |

| V <sub>SS</sub>        | 64  | supply | negative supply voltage                   |  |

TDA8045

#### **FUNCTIONAL DESCRIPTION**

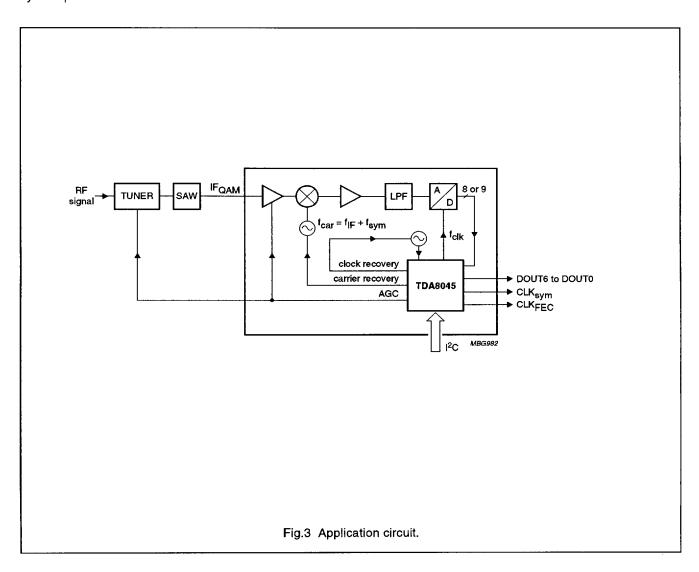

Figure 3 shows the application of the TDA8045 QAM demodulator. The frequency of the IF signal, IF $_{QAM}$ , is down converted to the symbol frequency  $f_{sym}$  by a mixer which is driven from a local oscillator with a frequency of  $f_{car} = f_{IF} + f_{sym}$ . After low pass filtering this baseband signal is applied to an external 8 or 9-bit ADC. Under normal operating conditions, it is sufficient to use an 8-bit ADC. To avoid additional performance degradation due to adjacent interferences, a 9-bit ADC can be used.

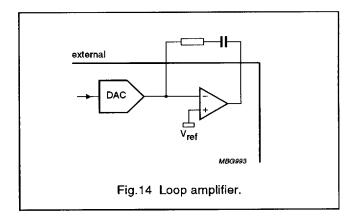

The QAM demodulator generates in a digital way the control values for AGC, Carrier Recovery, and Clock Recovery. The on-chip DACs translate these digital values to analog control currents which are integrated afterwards by a loop filter.

To perform this loop filtering, after each DAC an operational amplifier is integrated.

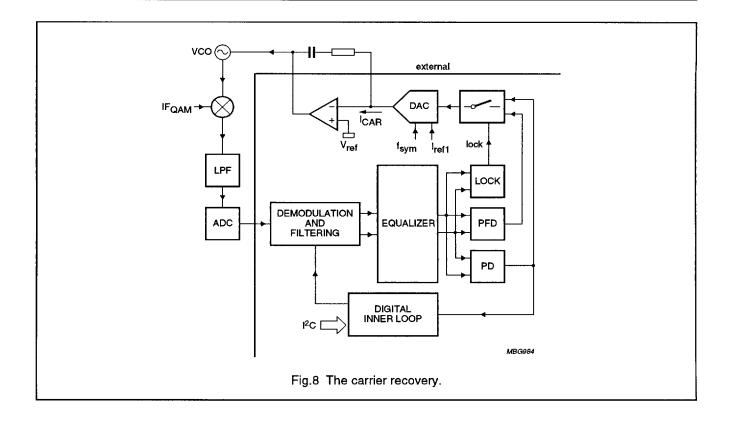

The carrier recovery consists of a two loop system. The outer loop is shown in the diagram of Fig.3 and controls both phase and frequency at a low speed. The inner loop controls the carrier phase at a high speed (wide loop bandwidth).

Also the AGC consists of two loops; one outer loop called the coarse AGC and one inner loop called the fine AGC.

The recovered symbols are converted into bits according to a demapping scheme and represented at the output in a 7-bit parallel output format. The demodulator can be initialized and monitored by the I<sup>2</sup>C-bus interface.

#### Functional description of the individual blocks

The functional block diagram of the QAM demodulator is shown in Fig. 1. In this section the individual blocks in the demodulator are described. After adaptation for the used input format (twos complement or binary), the input signal is demodulated in the I and Q baseband signals which are applied to the inputs of the Half Nyquist filter (Square-Root Raised-Cosine). To avoid overloading of the ADC, an AGC detector is placed after the adaptation for the input format. After Half Nyquist filtering, the control value for the clock recovery is generated. In the equalizer, the echos created in the cable network are reduced significantly.

After the equalizer, a 'clean' constellation diagram is present from which the information for carrier recovery is derived. This constellation is also applied to the output formatter which demaps the transmitted symbols in corresponding bits. The Carrier Recovery and Lock Detection function are based on the equalizer output. The output of the equalizer is applied to an output formatter, which translates the symbol bits to a FEC input format. The digital outputs of the Clock Recovery, AGC, and Carrier Recovery section are converted into currents which are integrated by the loop filters. To make these

active loop filters, operational amplifiers are integrated on the chip.

The TDA8045 can handle four different digital modulation schemes; 4, 16, 32 and 64-QAM. These schemes are selectable by the I<sup>2</sup>C interface.

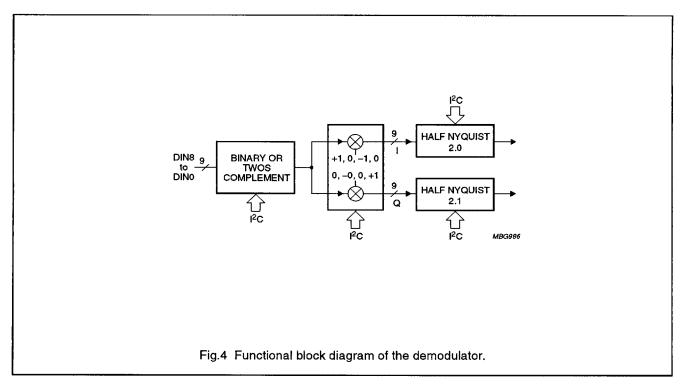

#### **DEMODULATOR AND HALF NYQUIST FILTER**

After selection of the appropriate input format by the I<sup>2</sup>C-bus, demodulation is accomplished. The in-phase and quadrature components are both applied to a Half Nyquist filter. Under normal operation this filter gives a 20% roll-off Half Nyquist shaping. The basic schematic of the demodulator followed by the Half Nyquist filter is shown in Fig.4. The signs of the multiplication factors in the Q branch can be inverted. This can be done by using I<sup>2</sup>C.

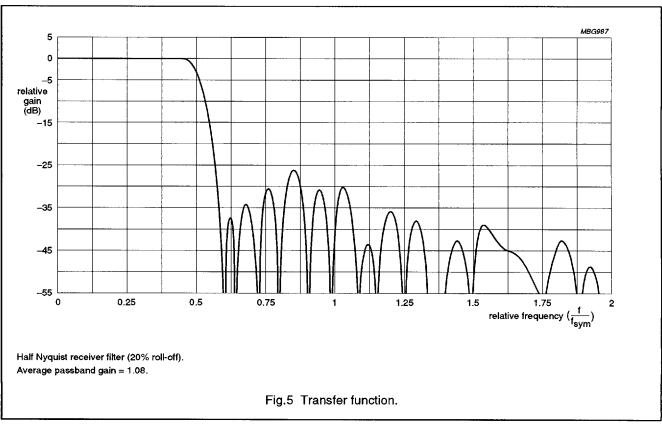

When using an 8-bit ADC the LSB of the 9-bit input word should be connected to the supply. This is to ensure a symmetrical twos complement representation which can be multiplied by -1 in a correct (twos complement) way. The characteristics of the demodulator and the Half Nyquist filter are listed in Table 1. The overall transfer function of the Square-Root Raised-Cosine filter is shown in Fig.5.

| Table 1 Demodulator and Half Nyquist filter characteris | stics |

|---------------------------------------------------------|-------|

|---------------------------------------------------------|-------|

| SYMBOL               | PARAMETER                      | CONDITIONS              | MIN.     | TYP.       | MAX. | UNIT |

|----------------------|--------------------------------|-------------------------|----------|------------|------|------|

| Half Nyquist         | filter                         |                         |          |            |      |      |

| α                    | roll-off                       |                         | -        | 20         | _    | %    |

| PBR                  | passband ripple                | f ≤ 0.4f <sub>sym</sub> | <u> </u> | 0.05       | -    | dB   |

| SBR                  | stopband ripple                | f ≤ 0.6f <sub>sym</sub> | see Fig  | .5         |      |      |

| ISI <sub>power</sub> | power intersymbol interference | note 1                  | <u> </u> | <b>-44</b> | -    | dB   |

#### Note

1. Definition of peak intersymbol interference:

$$|SI_{power}(dB)| = 10 \log \left[ \frac{2 \times \sum_{k=1}^{(N_{conv}-1)/2} |C_{conv}(4k)|^2}{\left|C_{conv}(0)\right|^2} \right]$$

- a) where  $N_{conv}$  is the number of coefficients  $C_{conv}$ .  $C_{conv(k)}$  represents the coefficient resulting from the convolution of the transmission and reception filters (k indicates the  $k^{th}$  coefficient).

- b) the power ISI specified in Table 1 has been calculated on a filter resulting from the convolution of the TDA8045 filter and a truncated Half Nyquist filter with 41 T/4 taps.

1996 Feb 02 8

TDA8045

#### **EQUALIZER**

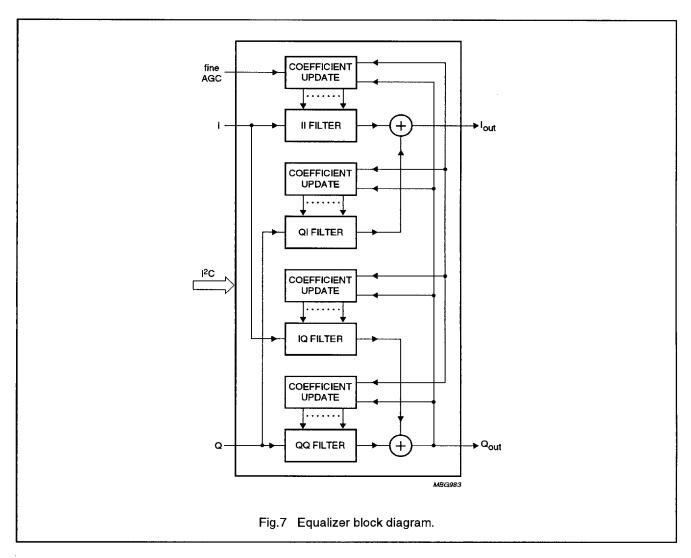

The equalizer function is realized with four 'T' spaced adaptive filters based on Zero-Forcing algorithm; no training sequence is required. The block schematic of the total equalizer is shown in Fig.7. The main tap of the II and QQ filter is adjustable for fine AGC function (6 dB AGC range). By means of the I<sup>2</sup>C bus, one can read the settings of the equalizer taps. Only one set of tap values is needed for the two direct filters and one set for the two cross filters.

Besides reading the equalizer tap values, the main tap of the direct filters in the equalizer can also be programmed. After setting the main tap, the other coefficients can be set to zero. Furthermore in the equalizer one can freeze the equalizer settings also by I<sup>2</sup>C.

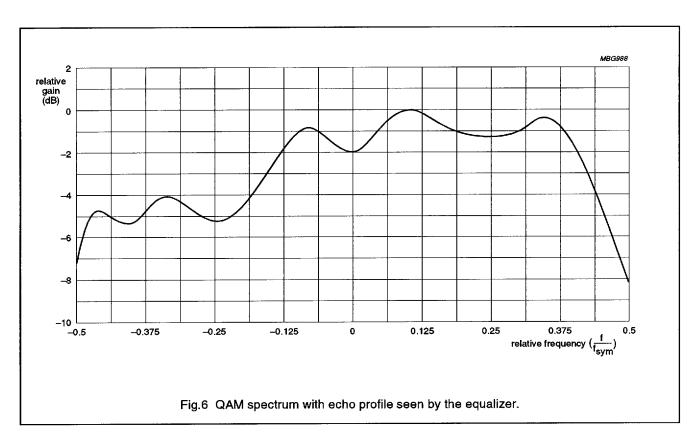

The equalizer has been simulated with the echo profile as given in Table 2. From the total system simulations it is concluded that all loops (including equalizer) converges at a SNR of 21 dB for a 64-QAM modulation format.

Table 2 Channel Echo Profile

| DELAY                                          | AMPLITUDE | PHASE |

|------------------------------------------------|-----------|-------|

| <sup>3</sup> ∕ <sub>8</sub> T <sub>sym</sub>   | 0.08      | 130°  |

| 1½T <sub>sym</sub>                             | 0.20      | 60°   |

| 2T <sub>sym</sub>                              | 0.05      | 310°  |

| 4 <sup>5</sup> / <sub>8</sub> T <sub>sym</sub> | 0.10      | 200°  |

| 6 <sup>7</sup> / <sub>8</sub> T <sub>sym</sub> | 0.03      | 200°  |

Figure 6 represents the QAM spectrum seen by the equalizer. It corresponds (in the frequency domain) to the multiplication of a full Nyquist spectrum by the impulse response of the channel specified by Table 2.

TDA8045

#### LOCK DETECTOR

The lock detector indicates whether all algorithms in the demodulator are converged or not. For a symbol error rate (at the input of the demodulator) smaller than  $2\times 10^{-2}$ , the detector will give the indication 'LOCK'; I²C bit LK = 1. For larger symbol error rates, the detector will generate the 'UNLOCK' signal; I²C bit LK = 0. Note that this 'UNLOCK' signal is generated before any other part of the

demodulator loses lock. The lock detector is part of the carrier recovery loop, see Fig.8. The Lock Detector Threshold (LDT) can be changed with the help of I<sup>2</sup>C. The nominal LDT values for given S/N ratios are given in Table 3. The estimation algorithm used in the lock detector provides also information about the SER ratio which can be read out by the I<sup>2</sup>C-bus interface.

TDA8045

Table 3 Lock detector characteristics

| SYMBOL              | PARAMETER    | CONSTELLATION FORMAT | MIN. | TYP. | MAX. | UNIT |

|---------------------|--------------|----------------------|------|------|------|------|

| SNR <sub>lock</sub> | SNR for lock | 4-QAM                | 8    | _    | -    | dB   |

|                     |              | 16-QAM               | 15   | _    | _    | dB   |

|                     |              | 32-QAM               | 18   | -    | _    | dB   |

|                     |              | 64-QAM               | 21   | _    |      | dB   |

#### CARRIER RECOVERY

The carrier recovery detector consists of a Phase-Frequency Detector (PFD) and Phase Detector (PD). Depending on the mode of operation, the carrier recovery is switched either between the phase-frequency detector (no lock) or the phase detector (lock). The carrier recovery consists of the following two loops:

- The outer loop; this loop is controlling the phase and frequency of the incoming QAM signal at the IF frequency in such a way that the constellation is optimally positioned for detection.

- The inner loop; the bandwidth of this loop can be large (up to 50 kHz) and can therefore reduce the influence of large bandwidth phase noise.

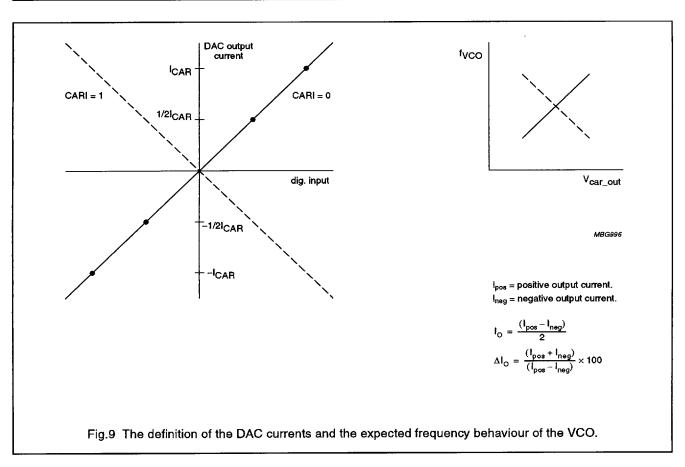

Four different maximum DAC output currents can be selected with the I<sup>2</sup>C-bus. The characteristics of the carrier recovery detector are listed in Table 4. The output currents of the DAC are defined in such a way that a VCO with a behaviour as shown in Fig.8 can be connected directly to the output of the integrated operational amplifier. In case the VCO slope is negative the sign of the current can be inverted by I<sup>2</sup>C. Figure 9 defines also the DAC output currents.

**Table 4** Characteristics of the carrier recovery detector Bias current for DACs is set to 37.5 μA.

| SYMBOL                     | PARAMETER                               | CONDITIONS                              | MIN.       | TYP.                                         | MAX.                 | UNIT             |

|----------------------------|-----------------------------------------|-----------------------------------------|------------|----------------------------------------------|----------------------|------------------|

| Carrier recov              | ery                                     |                                         |            |                                              |                      |                  |

| K <sub>d</sub>             | detector constant                       | SNR = 21 dB for<br>64-QAM constellation | _          | <sup>6</sup> ∕ <sub>2</sub> l <sub>CAR</sub> | _                    | μ <b>A</b> /rad  |

| $\Delta f_{car}$           | frequency range                         |                                         | 0.017      |                                              | _                    | f <sub>sym</sub> |

| f <sub>n in</sub>          | loop bandwidth of inner loop            |                                         | 10         | -                                            | 50                   | kHz              |

| f <sub>n out</sub>         | loop bandwidth of outer loop            |                                         | _          | _                                            | 0.3f <sub>n in</sub> | kHz              |

| Iz                         | zero current of DAC                     |                                         | -25        | _                                            | +25                  | nA               |

| I <sub>CAR</sub>           | DAC output current range (programmable) |                                         | 50         | _                                            | 200                  | μА               |

| f <sub>DAC</sub>           | DAC sampling rate                       |                                         | _          | f <sub>sym</sub>                             | _                    | MHz              |

| Carrier recov              | ery DAC output currents during l        | ock                                     |            |                                              |                      |                  |

| I <sub>O-car-lock</sub>    | mean output current                     |                                         | _          | ½lcar                                        | _                    | μА               |

| ΔI <sub>O-car-lock</sub>   | matching of output currents             |                                         | <b>-</b> 5 | _                                            | +5                   | %                |

| Carrier recov              | ery DAC output currents during u        | ınlock                                  |            |                                              |                      |                  |

| I <sub>O-car-unlock</sub>  | mean output current                     |                                         |            | I <sub>CAR</sub>                             | <u> </u>             | μΑ               |

| ΔI <sub>O-car-unlock</sub> | matching of output current              |                                         | <b>-</b> 5 | -                                            | +5                   | %                |

### CLOCK RECOVERY

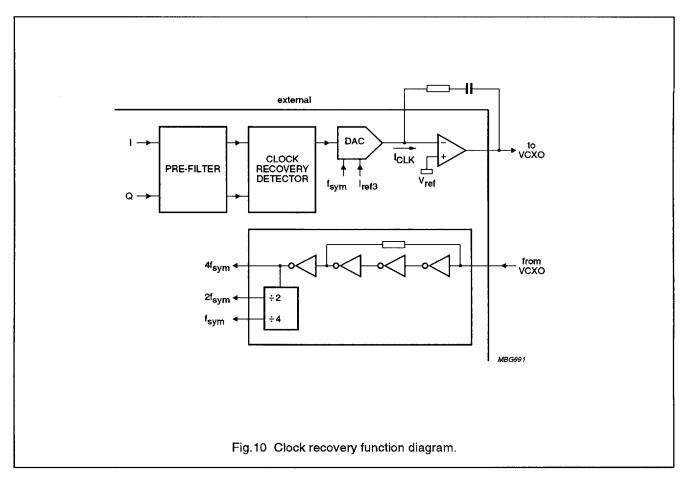

The clock recovery function uses the unequalized I and Q signals, i.e. the Half Nyquist filter outputs; see Fig.2. The clock recovery section generates a control value each symbol period. As this algorithm is based on the energy maximization, both main and mid symbols are required at the input. So, the input data rate is twice the symbol rate  $(2/T_{\text{sym}})$ . To reduce the data jitter, a prefilter, IIR, in front of the clock recovery detector is included. The functional schematic of this detector is shown in Fig.10.

The clock generator generates from the VCXO clock signal at  $4f_{\text{sym}}$  the required internal clocks. The input stage amplifier of this generator enables the designer to supply a low amplitude oscillator signal to the TDA8045. The DAC output current range,  $I_{\text{CLK}}$ , can be varied by means of the  $I^2\text{C}$ -bus. Also here the sign of the output current can be inverted to adjust for the proper sign of the VCXO slope.

The characteristics of the clock recovery detector are listed in Table 5.

**Table 5** Characteristics of the clock recovery detector Bias current for DACs is set to 37.5  $\mu$ A.

| SYMBOL                   | PARAMETER                               | CONDITIONS                                 | MIN.       | TYP.                | MAX.     | UNIT            |

|--------------------------|-----------------------------------------|--------------------------------------------|------------|---------------------|----------|-----------------|

| K <sub>d</sub>           | detector constant                       | SNR = 21 dB for<br>64-QAM<br>constellation | -          | 0.4I <sub>CLK</sub> | _        | μ <b>A</b> /rad |

| Δf <sub>CLK</sub>        | frequency range                         |                                            | ±100       | <b>[</b> -          | <b>-</b> | ppm             |

| f <sub>n</sub>           | natural frequency                       |                                            | Ī-         | 400                 | -        | Hz              |

| I <sub>CLK</sub>         | DAC output current range (programmable) |                                            | 50         | _                   | 200      | μΑ              |

| f <sub>DAC</sub>         | DAC sample rate                         |                                            | _          | f <sub>sym</sub>    | _        | MHz             |

| Clock recover            | y DAC output currents                   |                                            |            |                     |          |                 |

| I <sub>O-clk-lock</sub>  | mean output current                     |                                            | -          | I <sub>CLK</sub>    | -        | μА              |

| Δl <sub>O-clk-lock</sub> | matching of output currents             |                                            | <b>-</b> 5 | <u> </u>            | +5       | %               |

TDA8045

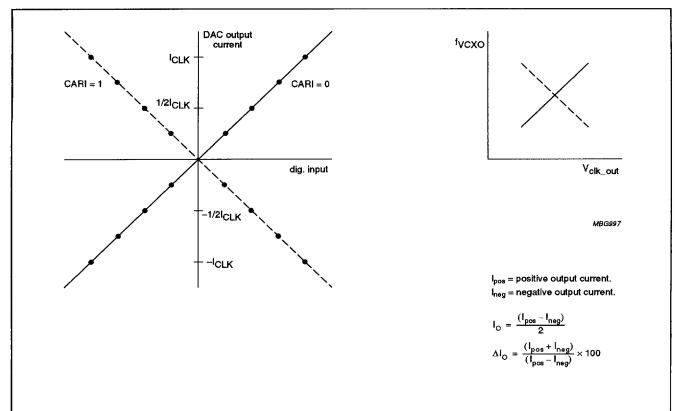

Fig.11 The definition of the DAC currents and the expected frequency behaviour of the VCXO for clock recovery.

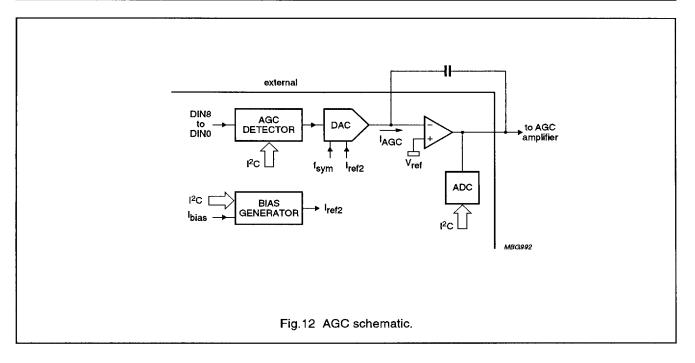

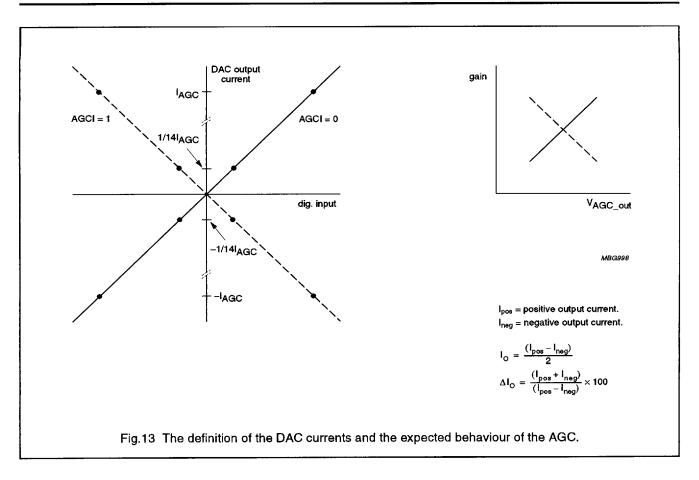

#### AGC

The AGC estimates the mean power based on the digital input signal and relates this to a peak value for a given constellation. To avoid overloading of the ADC, this estimation of the peak signals is used to control the AGC loop. The implemented AGC covers a range of ±20 dB in gain variance.

In case the SAW filter has not sufficient adjacent channel attenuation, the AGC threshold can be varied to avoid clipping of the ADC. To do this, the threshold is made programmable by the I<sup>2</sup>C-bus (byte ATH).

Table 6 shows that for each mode, a new ATH value (on address 08) must be set with the help of I<sup>2</sup>C. The I<sup>2</sup>C data on address 08 is a factor 16 smaller than the used AGC threshold ATH.

The DAC output current range can be varied with the I<sup>2</sup>C-bus interface (bits AGCA and AGCB) and sign of the current can be inverted (bit AGCI). The output of the AGC amplifier can be monitored and read by the I<sup>2</sup>C-bus interface (I<sup>2</sup>C bits AGO).

Table 6 AGC Threshold values

| MODE   | ATH (AGC THRESHOLD) | I <sup>2</sup> C DATA FOR ADDRESS 08 |

|--------|---------------------|--------------------------------------|

| 4-QAM  | 496                 | 1F                                   |

| 16-QAM | 992                 | 3E                                   |

| 32-QAM | 1408                | 58                                   |

| 64-QAM | 1984                | 7C                                   |

**TDA8045**

# QAM demodulator

**Table 7** Characteristics of the AGC detector Bias current for DACs set to 37.5  $\mu$ A.

| SYMBOL              | PARAMETER                                | MIN.       | TYP.             | MAX. | UNIT |

|---------------------|------------------------------------------|------------|------------------|------|------|

| $\Delta R_{AGC}$    | AGC range of detector                    | ±20        | -                | -    | dB   |

| I <sub>Z</sub>      | zero current                             | -25        | _                | +25  | nA   |

| I <sub>AGC</sub>    | DACs output current range (programmable) | 50         | _                | 200  | μΑ   |

| f <sub>DAC</sub>    | DACs sample rate                         | _          | f <sub>sym</sub> | _    | MHz  |

| AGC DAC out         | put currents                             | -          |                  |      |      |

| I <sub>O-AGC</sub>  | mean output current (in lock)            | _          | 1/14lagc         | _    | μΑ   |

|                     | mean output current (unlock)             | _          | I <sub>AGC</sub> | 1-   | μΑ   |

| Δl <sub>O-AGC</sub> | matching of output current               | <b>-</b> 5 | _                | +5   | %    |

#### OFFSET CONTROL

To compensate offsets in the I and Q branch due to spurious signals at the symbol frequency at the ADC input, an offset compensation loop in each of the I and Q branches is included. This loop forces the constellation to be symmetrically distributed over its four quadrants. This function can be switched **off** by I<sup>2</sup>C (bit OFFS; see Table 14).

#### LOOP AMPLIFIERS

The characteristics of the loop amplifiers to enable loop filtering in the loops are listed in Table 8.

Table 8 Characteristics of integrated loop amplifiers

| SYMBOL             | PARAMETER              | MIN.               | TYP. | MAX.               | UNIT |

|--------------------|------------------------|--------------------|------|--------------------|------|

| G <sub>o</sub>     | open loop gain         | _                  | 60   | _                  | dB   |

| G <sub>BW</sub>    | gain bandwidth product |                    | 1    | _                  | MHz  |

| V <sub>ref</sub>   | reference voltage      | _                  | 2.5  |                    | V    |

| V <sub>out</sub>   | output voltage range   | 0.1V <sub>DD</sub> | T-   | 0.9V <sub>DD</sub> | V    |

| R <sub>L VSS</sub> | load to ground         | 5                  | -    | -                  | kΩ   |

| R <sub>L VDD</sub> | load to supply         | 6.5                | _    | _                  | kΩ   |

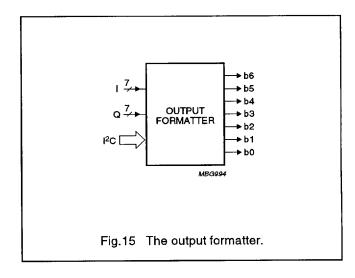

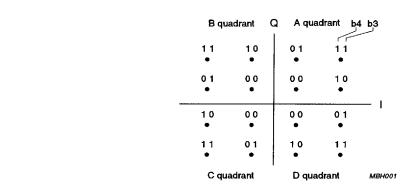

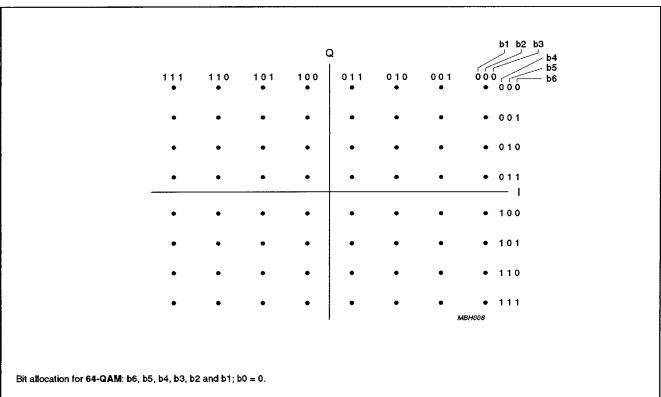

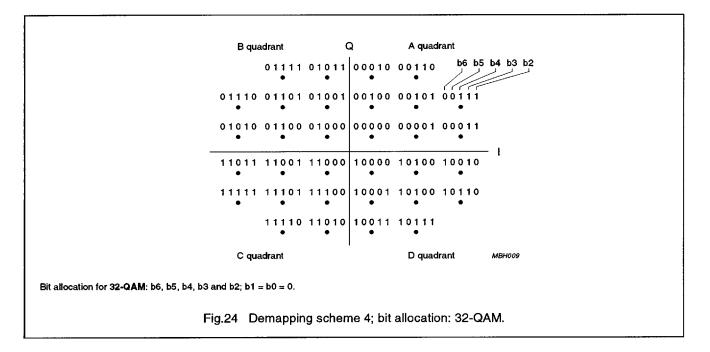

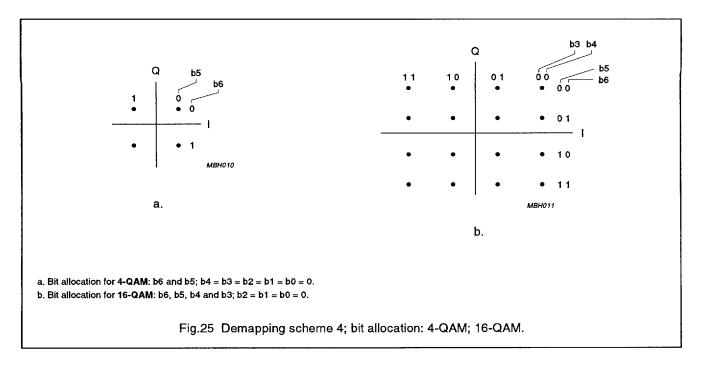

#### OUTPUT FORMATTER

The output formatter transforms the detected I and Q values into bits according to the selected mapping. The TDA8045 has four possible mapping formats which can be selected by the I<sup>2</sup>C-bus interface (OUTA and OUTB). The demapping procedure and the corresponding bits are defined in Fig.15.

After demapping the bits are allocated to the output. Output format is controlled by I<sup>2</sup>C-bus interface (TSEL2, TSEL1 and TSEL0). Two main modes are used: 7-bit parallel detected symbol or 7-bit I and Q value (twos complement). The output allocation for the detected symbols corresponds to one of the selected demapping schemes.

The implemented demapping formats and output bit allocation are listed below.

**TDA8045**

### Demapping scheme 1; differential decoding

|      | B qua | adrant | (    | a<br>a | A quad | Irant | b4 b:<br>ند اد | 3 b2 b1 |

|------|-------|--------|------|--------|--------|-------|----------------|---------|

| 1010 | 1011  | 1001   | 1000 | 0010   | 0110   | 1110  | 1010           |         |

| 1110 | 1111  | 1101   | 1100 | 0011   | 0111   | 1111  | 1011           |         |

| 0110 | 0111  | 0101   | 0100 | 0001   | 0101   | 1101  | 1001           |         |

| 0010 | 0011  | 0001   | 0000 | 0000   | 0100   | 1100  | 1000           |         |

| 1000 | 1100  | 0100   | 0000 | 0000   | 0001   | 0011  | 0010           | I       |

| 1001 | 1101  | 0101   | 0001 | 0100   | 0101   | 0111  | 0110           |         |

| 1011 | 1111  | 0111   | 0011 | 1100   | 1101   | 1111  | 1110           |         |

| 1010 | 1110  | 0110   | 0010 | 1000   | 1001   | 1011  | 1010           |         |

|      | C qua | adrant |      | I      | D quad | rant  | МВ             | G999    |

Bit allocation for 4-QAM: b4 = b3 = b2 = b1 = b0 = 0; b6 and b5 differentially decoded (see Table 9). Bit allocation for 64-QAM: b4, b3, b2 and b1; b0 = 0; b6 and b5 differentially decoded (see Table 9).

Fig.16 Demapping scheme 1; bit allocation: 4-QAM; 64-QAM.

Bit allocation for 16-QAM: b4 and b3; b2 = b1 = b0 = 0; b6 and b5 differentially decoded (see Table 9). Bit allocation for 32-QAM: not implemented.

Fig.17 Demapping scheme 1; bit allocation: 16-QAM; 32-QAM.

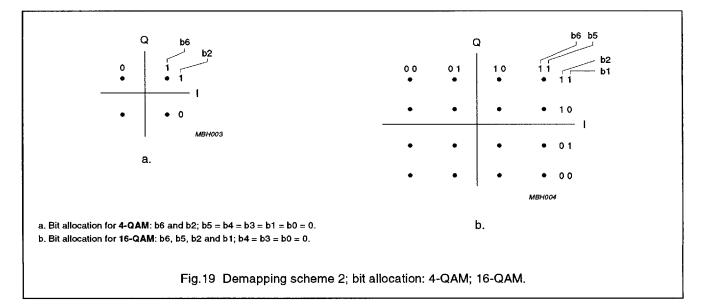

### Demapping scheme 2; direct translation

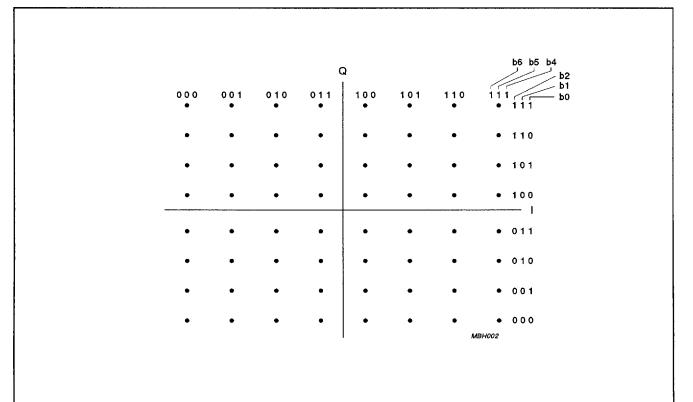

Bit allocation for 64-QAM: 66, 65, 64, 62, 61, 60; 63 = 60. Bit allocation for 64-QAM: not implemented.

Fig.18 Demapping scheme 2; bit allocation: 64-QAM; 32-QAM.

**TDA8045**

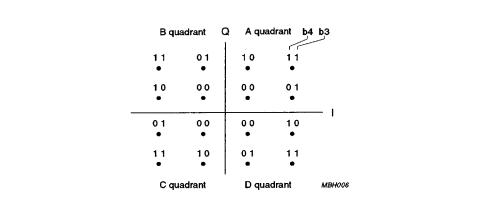

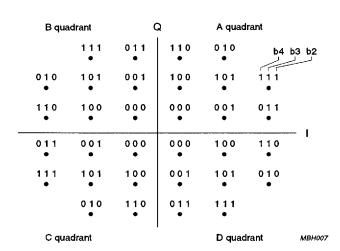

Demapping scheme 3; differential decoding: Draft prETS 429: 1994

| 1100 1110 0110 0100 1000 1001 1101 110                                                                                                                                                                                               |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1001 1011 0011 0001 0010 0011 0111 0110                                                                                                                                                                                              |      |

| 1000 1010 0010 0000 0001 0101 0100                                                                                                                                                                                                   |      |

| · · · · · ·                                                                                                                                                                                                                          |      |

| 0100 0101 0001 0000 0000 0010 1010 1000                                                                                                                                                                                              |      |

|                                                                                                                                                                                                                                      | ı    |

| 0110 0111 0011 0010 0001 0011 1011 1001                                                                                                                                                                                              |      |

| 1110 1111 1011 1010 0101 0111 1111 1101                                                                                                                                                                                              |      |

| 1100 1101 1001 1000 0100 0110 1110 1100                                                                                                                                                                                              |      |

| С quadrant D quadrant мвн                                                                                                                                                                                                            | 1005 |

| cation for <b>4-QAM</b> : $b4 = b3 = b2 = b1 = b0 = 0$ ; $b6$ and $b5$ differentially decoded (see Table 9). cation for <b>64-QAM</b> : $b4$ , $b3$ , $b2$ and $b1$ ; $b0 = 0$ ; $b6$ and $b5$ differentially decoded (see Table 9). |      |

Bit allocation for 16-QAM: b4 and b3; b2 = b1 = b0 = 0; b6 and b5 differentially decoded (see Table 9).

Fig.21 Demapping scheme 3; bit allocation: 16-QAM.

Bit allocation for 32-QAM: b4, b3 and b2; b1 = b0 = 0; b6 and b5 differentially decoded (see Table 9).

Fig.22 Demapping scheme 3; bit allocation: 32-QAM.

**TDA8045**

Demapping scheme 4; direct translation: HP8782B/K03

Fig.23 Demapping scheme 4; bit allocation: 64-QAM.

TDA8045

Table 9 Definition of two MSBs in modulation schemes 1 and 3

| QUADRANT OF     | QUADRANT OF     | PHASE     | CUF  | RENT O     | UTPUT E  | зітѕ       |

|-----------------|-----------------|-----------|------|------------|----------|------------|

| CURRENTLY       | PREVIOUSLY      | CHANGE    | SCHE | ME 1       | SCHEME 3 |            |

| RECEIVED SYMBOL | RECEIVED SYMBOL | (DEGREES) | b6   | <b>b</b> 5 | b6       | <b>b</b> 5 |

| Α               | Α               | 0         | 0    | 0          | 0        | 0          |

| Α               | В               | 270       | 1    | 0          | 0        | 1          |

| Α               | С               | 180       | 1    | 1          | 1        | 1          |

| Α               | D               | 90        | 0    | 1          | 1        | 0          |

| В               | Α               | 90        | 0    | 1          | 1        | 0          |

| В               | В               | 0         | 0    | 0          | 0        | 0          |

| В               | С               | 270       | 1    | 0          | 0        | 1          |

| В               | D               | 180       | 1    | 1          | 1        | 1          |

| С               | Α               | 180       | 1    | 1          | 1        | 1          |

| С               | В               | 90        | 0    | 1          | 1        | 0          |

| С               | С               | 0         | 0    | 0          | 0        | 0          |

| С               | D               | 270       | 1    | 0          | 0        | 1          |

| D               | Α               | 270       | 1    | 0          | 0        | 1          |

| D               | В               | 180       | 1    | 1          | 1        | 1          |

| D               | С               | 90        | 0    | 1          | 1        | 0          |

| D               | D               | 0         | 0    | 0          | 0        | 0          |

25

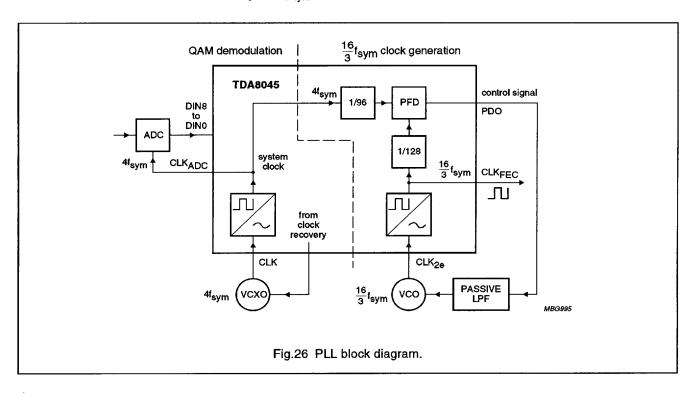

### PLL DIVIDER AND PHASE DETECTOR

A phase detector with two dividers is included in order to generate a control signal for an external VCO which has to be phase locked on the symbol frequency.

An extra VCO and a passive low pass filter are placed outside the TDA8045. The VCO is running at  $^{16}$ /3f<sub>sym</sub>.

The LPF is fed by a phase frequency detector which is implemented on chip. It is comparing the ' $^4$ / $_96$ f $_{sym}$  signal' and the 'squared and by 128 divided  $^{16}$ / $_3$ f $_{sym}$  signal'. An additional  $^{16}$ / $_3$ f $_{sym}$  output buffer is available to provide a digital clock signal to the FEC IC.

### I<sup>2</sup>C-BUS INTERFACE

The TDA8045 is controlled by an I<sup>2</sup>C-bus. For programming, there is one 7-bit module address and the R/W bit for selecting READ or WRITE mode. Note that the TDA8045 starts up according to the settings as defined in Tables 11, 12 and 13.

Table 10 Slave address

| <b>A</b> 6 | <b>A</b> 5 | <b>A</b> 4 | <b>A</b> 3 | A2 | A1         | <b>A</b> 0 | R/W |

|------------|------------|------------|------------|----|------------|------------|-----|

| 0          | 0          | 0          | 1          | 1  | <b>A</b> 1 | <b>A</b> 0 | Х   |

**Table 11** WRITE  $(R/\overline{W} = 0)$

| FUNCTION                | ADD | D7   | D6   | D5   | D4   | D3   | D2    | D1    | DO     |

|-------------------------|-----|------|------|------|------|------|-------|-------|--------|

| General                 | 00  | _    | _    | _    | _    | OFFS | NYQ   | DPHR  | RST    |

| Demodulator             | 01  | INP  | -    | OUTB | OUTA | DEM  | _     | CONB  | CONA   |

| DAC select              | 02  | -    | _    | AGCB | AGCA | CLKB | CLKA  | CARB  | CARA   |

| DAC current inversion   | 03  |      | -    | -    | _    | -    | AGCI  | CLKI  | CARI   |

| Digital test mode       | 04  | -    | _    | _    | -    | -    | TSEL2 | TSEL1 | TSEL0  |

| Carrier recovery BW     | 05  | DCA7 | DCA6 | DCA5 | DCA4 | DCA3 | DCA2  | DCA1  | DCA0   |

| Carrier recovery BW     | 06  | FSOL | DCB2 | DCB1 | DCB0 | -    | -     | _     | DCA8   |

| Lock detector threshold | 07  | LDT7 | LDT6 | LDT5 | LDT4 | LDT3 | LDT2  | LDT1  | LDT0   |

| AGC detector threshold  | 80  | ATH7 | ATH6 | ATH5 | ATH4 | ATH3 | ATH2  | ATH1  | ATH0   |

| Equalizer mode          | 09  | -    |      | EAR  | _    | EFCR | EFDI  | EFC   | PRESET |

| Equalizer tap TDC       | 0A  | TDC7 | TDC6 | TDC5 | TDC4 | TDC3 | TDC2  | TDC1  | TDC0   |

Table 12 Default settings after reset

| FUNCTION                   | ADD | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----------------------------|-----|----|----|----|----|----|----|----|----|

| General                    | 00  | _  | _  | _  |    | 1  | 1  | 1  | 0  |

| Demodulator                | 01  | 1  | -  | 0  | 1  | 0  | _  | 1  | 1  |

| DAC select                 | 02  | _  | _  | 0  | 1  | 0  | 0  | 0  | 1  |

| DAC current inversion      | 03  | _  | _  | -  | _  | _  | 0  | 1  | 0  |

| Digital test mode          | 04  | -  | -  | -  | -  |    | 0  | 0  | 0  |

| Carrier recovery BW        | 05  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0  |

| Carrier recovery BW        | 06  | 1  | 0  | 1  | 1  | _  | _  | _  | 0  |

| Lock detector<br>threshold | 07  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 1  |

| AGC detector threshold     | 08  | 0  | 1  | 1  | 1  | 1  | 1  | 0  | 0  |

| Equalizer mode             | 09  | _  | _  | 1  | _  | 0  | 0  | 0  | 0  |

| Equalizer tap TDC          | 0A  | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 1  |

**TDA8045**

Table 13 READ  $(R/\overline{W} = 1)$

| FUNCTION                        | ADD | D7  | D6  | D5  | D4   | D3   | D2   | D1   | D0   |

|---------------------------------|-----|-----|-----|-----|------|------|------|------|------|

| V <sub>car_out</sub> (4 bits)   | 00  |     | _   | _   |      | CR03 | CR02 | CR01 | CR00 |

| V <sub>clock_out</sub> (4 bits) | 01  | _   | _   | _   | _    | CL03 | CL02 | CL01 | CL00 |

| V <sub>AGC_out</sub> (4 bits)   | 02  | _ ′ | _   | _   |      | AG03 | AG02 | AG01 | AG00 |

| Lock detector                   | 03  | _   | _   | _   | ALEQ | _    | _    | _    | LK   |

| SER estimation                  | 04  | LE7 | LE6 | LE5 | LE4  | LE3  | LE2  | LE1  | LE0  |

### I<sup>2</sup>C WRITE PARAMETERS

Table 14 I<sup>2</sup>C write parameters; 1-bit values

| PARAMETER             | BIT                                      | VALUE | DESCRIPTION                                       |

|-----------------------|------------------------------------------|-------|---------------------------------------------------|

| Input format          | INP                                      | 0     | twos complement                                   |

|                       |                                          | 1     | straight binary                                   |

| Inversion demodulator | DEM                                      | 0     | Q-branch = 0,-1, 0, +1                            |

|                       |                                          | 1     | Q-branch = 0,+1, 0, -1                            |

| Half Nyquist filter   | NYQ                                      | 0     | filter in bypass mode (only for test purposes)    |

|                       |                                          | 1     | Half Nyquist filter                               |

| Digital phase rotator | DPHR                                     | 1     | on                                                |

|                       |                                          | 0     | off                                               |

| Digital filter select | FSOL                                     | 0     | first order loop (test mode)                      |

|                       |                                          | 1     | second order loop (normal mode)                   |

| General reset         | RST                                      | 0     | normal operation                                  |

|                       |                                          | 1     | reset (with automatic return to normal operation) |

| Offset                | OFFS                                     | 0     | switch off                                        |

|                       |                                          | 1     | switch <b>on</b>                                  |

| DAC current inversion | CARI                                     | 0     | no inversion                                      |

|                       |                                          | 1     | inversion                                         |

|                       | CLKI                                     | 0     | no inversion                                      |

|                       |                                          | 1     | inversion                                         |

|                       | AGCI                                     | 0     | no inversion                                      |

|                       |                                          | 1     | inversion                                         |

| Equalizer             | PRESET                                   | 0     | normal operation                                  |

| ·                     |                                          | 1     | coefficient to zero (main tap to '01110111')      |

|                       | EFCR                                     | 0     | normal operation                                  |

|                       | (Equalizer Freeze Cross) FIR             | 1     | freeze coefficients                               |

|                       | EFDI                                     | 0     | normal operation                                  |

|                       | (Equalizer Freeze Direct FIR)            | 1     | freeze coefficients                               |

|                       | EFC                                      | 0     | normal operation                                  |

|                       | (Fine AGC (Equalizer Freeze Center tap)) | 1     | freeze center tap, no fine AGC                    |

|                       | EAR                                      | 0     | off                                               |

|                       | (Equalizer Auto Reset)                   | 1     | on                                                |

TDA8045

Table 15 I<sup>2</sup>C write parameter: constellation; 2-bit values

| В    | BITS |             |  |  |  |  |

|------|------|-------------|--|--|--|--|

| CONB | CONA | DESCRIPTION |  |  |  |  |

| 0    | 0    | 4-QAM       |  |  |  |  |

| 0    | 1    | 16-QAM      |  |  |  |  |

| 1    | 0    | 32-QAM      |  |  |  |  |

| 1    | 1    | 64-QAM      |  |  |  |  |

| BI.  | BITS |             |  |  |  |  |

|------|------|-------------|--|--|--|--|

| OUTB | OUTA | DESCRIPTION |  |  |  |  |

| 0    | 0    | scheme 1    |  |  |  |  |

| 0    | 1    | scheme 2    |  |  |  |  |

| 1    | 0    | scheme 3    |  |  |  |  |

| 1    | 1    | scheme 4    |  |  |  |  |

Table 16 I<sup>2</sup>C write parameter: output format; 2-bit values

**Table 17** I<sup>2</sup>C write parameter: DAC carrier recovery (maximum current); 2-bit values

| В    | BITS |             |  |  |  |  |

|------|------|-------------|--|--|--|--|

| CARB | CARA | DESCRIPTION |  |  |  |  |

| 0    | 0    | 50 μΑ       |  |  |  |  |

| 0    | 1    | 100 μΑ      |  |  |  |  |

| 1    | 0    | 150 μΑ      |  |  |  |  |

| 1    | 1    | 200 μΑ      |  |  |  |  |

**Table 18** I<sup>2</sup>C write parameter: DAC clock recovery (maximum current); 2-bit values

| BI   | DESCRIPTION |             |  |

|------|-------------|-------------|--|

| CLKB | CLKA        | DESCRIPTION |  |

| 0    | 0           | 50 μΑ       |  |

| 0    | 1           | 100 μΑ      |  |

| 1    | 0           | 150 μΑ      |  |

| 1    | 1           | 200 μΑ      |  |

**Table 19** I<sup>2</sup>C write parameter: DAC AGC (maximum current); 2-bit values

| Bi   | DESCRIPTION |             |  |

|------|-------------|-------------|--|

| AGCB | AGCA        | DESCRIPTION |  |

| 0    | 0           | 50 μΑ       |  |

| 0    | 1           | 100 μΑ      |  |

| 1    | 0           | 150 μΑ      |  |

| 1    | . 1         | 200 μΑ      |  |

Table 20 12C write parameters; 3-bit values

| DADAMETED       |          | BITS  |             |                           |  |  |

|-----------------|----------|-------|-------------|---------------------------|--|--|

| PARAMETER       | TSEL2    | TSEL1 | TSEL0       | DOUT6 TO DOUT0            |  |  |

| Functional Test | 0        | 0     | 0           | default mode              |  |  |

|                 |          |       |             | SHND = 0: scheme 1 to 4   |  |  |

|                 |          | į     |             | SHND = 1: multiplexed I/Q |  |  |

|                 | 0        | 0     | 1           | scheme 1 to 4             |  |  |

|                 | 0        | 1     | 0           | multiplexed I/Q           |  |  |

|                 | 0        | 1     | 1           | test mode 1               |  |  |

|                 | 1        | 0     | 0           | test mode 2               |  |  |

| 1 0 1           |          | 1     | test mode 3 |                           |  |  |

|                 | 1 1 0 te |       | 0           | test mode 4               |  |  |

|                 | 1        | 1     | 1           | test mode 5               |  |  |

**TDA8045**

### I<sup>2</sup>C READ PARAMETERS

Table 21 I<sup>2</sup>C read parameters; 1-bit values

| PARAMETER       | BIT  | VALUE | DESCRIPTION                    |  |

|-----------------|------|-------|--------------------------------|--|

| Lock detect     | LK   | 0     | no lock                        |  |

| i               |      | 1     | lock                           |  |

| Alarm equalizer | ALEQ | 0     | normal operation (alarm off)   |  |

|                 |      | 1     | divergence detected (alarm on) |  |

## Table 22 I<sup>2</sup>C read parameter: ADC carrier recovery; 4-bit values

|      | ВІТ                 | s  |      | DESCRIPTION                                                                     |

|------|---------------------|----|------|---------------------------------------------------------------------------------|

| CR03 | CR03 CR02 CR01 CR00 |    | CR00 | DESCRIPTION                                                                     |

| b3   | b2                  | b1 | b0   | Carrier recovery: $V_{car_out} = 0.25 + \frac{VDD}{16}(8b3 + 4b2 + 2b1 + b0) V$ |

### Table 23 I2C read parameter: ADC clock recovery; 4-bit values

| BITS |                     |    |    | DESCRIPTION                                                                      |  |  |  |

|------|---------------------|----|----|----------------------------------------------------------------------------------|--|--|--|

| CL03 | CL03 CL02 CL01 CL00 |    |    |                                                                                  |  |  |  |

| b3   | b2                  | b1 | b0 | Clock recovery: $V_{clock\_out} = 0.25 + \frac{VDD}{16}(8b3 + 4b2 + 2b1 + b0) V$ |  |  |  |

### Table 24 I<sup>2</sup>C read parameter: ADC AGC; 4-bit values

|      | BITS |      |      | DESCRIPTION                                                        |

|------|------|------|------|--------------------------------------------------------------------|

| AG03 | AG02 | AG01 | AG00 | DESCRIPTION                                                        |

| b3   | b2   | b1   | b0   | AGC: $V_{AGC_out} = 0.25 + \frac{VDD}{16}(8b3 + 4b2 + 2b1 + b0) V$ |

### Table 25 I2C read parameter; 8-bit values

| PARAMETER          | BITS <sup>(1)</sup> |    |     |     |                    |    |     | DESCRIPTION |                                         |

|--------------------|---------------------|----|-----|-----|--------------------|----|-----|-------------|-----------------------------------------|

| PARAMETER          | LE7 LE6 L           |    | LE5 | LE4 | LE4 LE3 LE2 LE1 LE |    | LE0 | DESCRIPTION |                                         |

| SER <sup>(2)</sup> | b7                  | b6 | b5  | b4  | b3                 | b2 | b1  | b0          | SER = f(b7, b6, b5, b4, b3, b2, b1, b0) |

### Notes

- 1. The bits LE7 to LE0 give the number of symbols falling inside the lock detector active areas. The count is made during an observation period (256 to 2048 symbols).

- 2. To get more details about the SER estimation, refer to the "Application Note AN95088".

TDA8045

### **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL           | PARAMETER                     | CONDITIONS               | MIN. | MAX.            | UNIT |

|------------------|-------------------------------|--------------------------|------|-----------------|------|

| $V_{DD}$         | supply voltage                |                          | -0.3 | 6.0             | V    |

| $V_{\text{max}}$ | maximum voltage on all pins   |                          | 0    | V <sub>DD</sub> | V    |

| P <sub>tot</sub> | total power dissipation       | T <sub>amb</sub> = 70 °C | -    | 1.5             | W    |

|                  |                               | T <sub>amb</sub> = 60 °C | -    | 1.8             | W    |

|                  |                               | T <sub>amb</sub> = 50 °C | -    | 2.0             | W    |

| T <sub>stg</sub> | storage temperature           |                          | -55  | +150            | °C   |

| T <sub>amb</sub> | operating ambient temperature |                          | 0    | +70             | °C   |

### THERMAL CHARACTERISTICS

| SYMBOL              | PARAMETER                                               | VALUE | UNIT |

|---------------------|---------------------------------------------------------|-------|------|

| R <sub>th j-a</sub> | thermal resistance from junction to ambient in free air | 45    | K/W  |

### **HANDLING**

Inputs and outputs are protected against electrostatic discharges in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling integrated circuits.

### **ELECTRICAL CHARACTERISTICS OF DIGITAL INPUTS AND OUTPUTS**

$V_{DD} = 5 \text{ V}$ ;  $T_{amb} = 25 \text{ °C}$ ; unless otherwise specified.

| SYMBOL               | PARAMETER                 | CONDITIONS          | MIN.               | TYP.     | MAX.               | UNIT |

|----------------------|---------------------------|---------------------|--------------------|----------|--------------------|------|

| Digital outputs:     | DOUT6 to DOUT0            |                     |                    | •        | •                  | •    |

| V <sub>OL</sub>      | LOW level output voltage  |                     | 0                  | <u> </u> | 0.1V <sub>DD</sub> | V    |

| V <sub>OH</sub>      | HIGH level output voltage |                     | 0.9V <sub>DD</sub> |          | V <sub>DD</sub>    | V    |

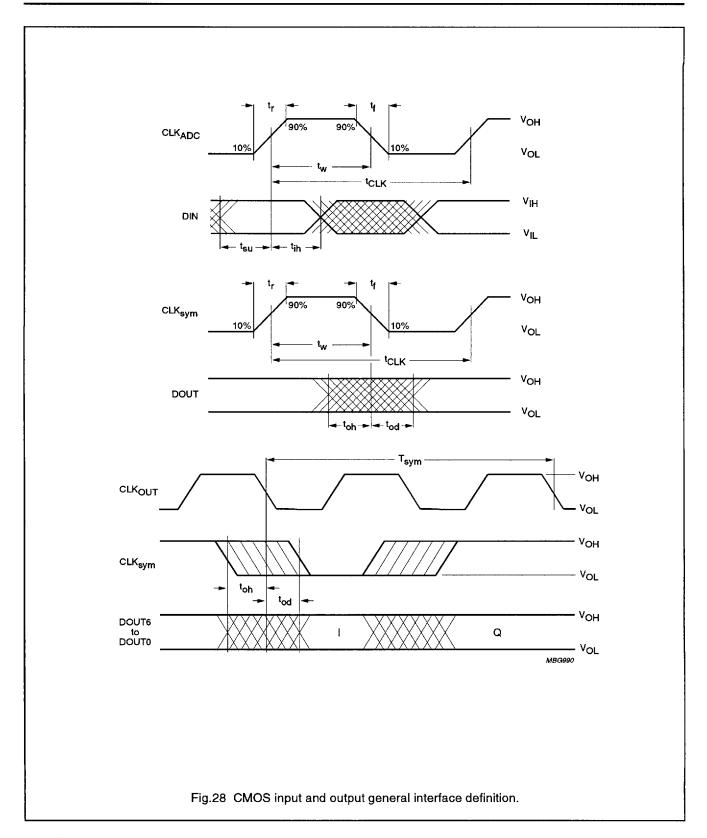

| t <sub>od</sub>      | delay time                |                     | _                  | _        | 22                 | ns   |

| t <sub>oh</sub>      | hold time                 |                     | _                  | _        | 22                 | ns   |

| C <sub>L</sub>       | load capacitance          |                     | -                  |          | 30                 | pF   |

| Digital inputs: [    | DIN8 to DINO              |                     |                    |          |                    |      |

| V <sub>IL</sub>      | LOW level input voltage   |                     | 0                  | Ī-       | 0.8                | V    |

| V <sub>IH</sub>      | HIGH level input voltage  |                     | 2                  | _        | V <sub>DD</sub>    | V    |

| t <sub>su</sub>      | set-up time               |                     | -                  | _        | 15                 | ns   |

| t <sub>ih</sub>      | hold time                 |                     | _                  | _        | 0                  | ns   |

| Ci                   | input capacitance         |                     | -                  | _        | 10                 | pF   |

| Clock inputs: C      | LK and CLK <sub>2e</sub>  |                     | <del>-</del>       | -        | -                  | _    |

| V <sub>in(rms)</sub> | input level               | sine wave           | 100                | -        | _                  | mV   |

| T <sub>cy</sub>      | cycle time                |                     | 35                 | _        | _                  | ns   |

| tw                   | pulse width               | 40 : 60 duty factor | 14                 |          | _                  | ns   |

| R <sub>source</sub>  | source resistance         |                     | -                  |          | 50                 | Ω    |

| SYMBOL          | PARAMETER                                 | CONDITIONS             | MIN.               | TYP. | MAX.               | UNIT |

|-----------------|-------------------------------------------|------------------------|--------------------|------|--------------------|------|

| Clock outputs:  | CLK <sub>ADC</sub> and CLK <sub>FEC</sub> |                        |                    |      |                    | -    |

| V <sub>OL</sub> | LOW level output voltage                  |                        | 0                  |      | 0.1V <sub>DD</sub> | V    |

| V <sub>OH</sub> | HIGH level output voltage                 |                        | 0.9V <sub>DD</sub> | -    | V <sub>DD</sub>    | V    |

| T <sub>cy</sub> | cycle time                                |                        | 35                 | Ī-   | -                  | ns   |

| t <sub>w</sub>  | pulse width                               | 40:60 duty factor      | 14                 | _    | _                  | ns   |

| t <sub>r</sub>  | rise time                                 | C <sub>L</sub> = 30 pF | -                  | _    | 6                  | ns   |

| t <sub>f</sub>  | fall time                                 | C <sub>L</sub> = 30 pF | _                  | _    | 6                  | ns   |

| $R_L$           | load                                      |                        | 1                  | _    | _                  | kΩ   |

| Clock outputs:  | CLK <sub>sym</sub> and CLK <sub>out</sub> | ·                      |                    | -    |                    |      |

| V <sub>OL</sub> | LOW level output voltage                  |                        | 0                  | _    | 0.1V <sub>DD</sub> | V    |

| V <sub>OH</sub> | HIGH level output voltage                 |                        | 0.9V <sub>DD</sub> | _    | $V_{DD}$           | V    |

| t <sub>r</sub>  | rise time                                 | C <sub>L</sub> = 30 pF | _                  | _    | 6                  | ns   |

| t <sub>f</sub>  | fall time                                 | C <sub>L</sub> = 30 pF |                    | _    | 6                  | ns   |

| Loop amplifiers |                                           |                        |                    |      |                    |      |

| Vo              | output range                              |                        | 0.1V <sub>DD</sub> | _    | 0.9V <sub>DD</sub> | V    |

| G <sub>o</sub>  | DC voltage gain (open loop)               |                        | _                  | 60   | _                  | dB   |

| G <sub>B</sub>  | gain bandwidth product                    |                        | _                  | 1    | _                  | MHz  |

| $R_L$           | load resistance                           |                        | 5                  | _    | _                  | kΩ   |

**TDA8045**

### **PACKAGE OUTLINES**

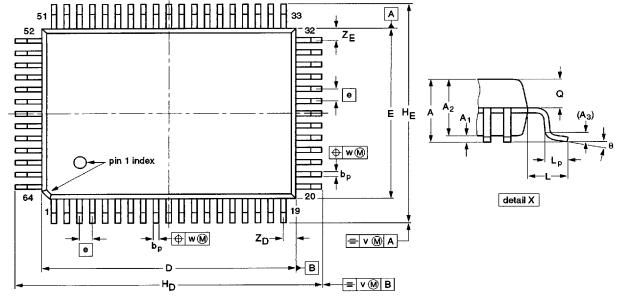

QFP64: plastic quad flat package; 64 leads (lead length 1.95 mm); body 14 x 20 x 2.8 mm

SOT319-2

### **DIMENSIONS (mm are the original dimensions)**

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bp           | C            | D <sup>(1)</sup> | E <sup>(1)</sup> | е | HD           | HE           | L    | Lp         | σ          | v   | w   | у   | Z <sub>D</sub> <sup>(1)</sup> | ZE <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|------|--------------|--------------|------------------|------------------|---|--------------|--------------|------|------------|------------|-----|-----|-----|-------------------------------|-------------------|----------|

| mm   | 3.20      | 0.25<br>0.05   | 2.90<br>2.65   | 0.25 | 0.50<br>0.35 | 0.25<br>0.14 | 20.1<br>19.9     | 14.1<br>13.9     | 1 | 24.2<br>23.6 | 18.2<br>17.6 | 1.95 | 1.0<br>0.6 | 1.4<br>1.2 | 0.2 | 0.2 | 0.1 | 1.2<br>0.8                    | 1.2<br>0.8        | 7°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER | EUROPEAN | ISSUE DATE |            |                                 |  |

|----------|-----|-------|----------|------------|------------|---------------------------------|--|

| VERSION  | IEC | JEDEC | EIAJ     |            | PROJECTION | SOUL DATE                       |  |

| SOT319-2 |     |       |          |            |            | <del>92-11-17</del><br>95-02-04 |  |

#### SOLDERING

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

#### Reflow soldering

Reflow soldering techniques are suitable for all QFP packages.

The choice of heating method may be influenced by larger plastic QFP packages (44 leads, or more). If infrared or vapour phase heating is used and the large packages are not absolutely dry (less than 0.1% moisture content by weight), vaporization of the small amount of moisture in them can cause cracking of the plastic body. For more information, refer to the Drypack chapter in our "Quality Reference Handbook" (order code 9398 510 63011).

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary between 50 and 300 seconds depending on heating method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 minutes at 45 °C.

#### Wave soldering

Wave soldering is **not** recommended for QFP packages. This is because of the likelihood of solder bridging due to closely-spaced leads and the possibility of incomplete solder penetration in multi-lead devices.

If wave soldering cannot be avoided, the following conditions must be observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The footprint must be at an angle of 45° to the board direction and must incorporate solder thieves downstream and at the side corners.

Even with these conditions, do not consider wave soldering the following packages: QFP52 (SOT379-1), QFP100 (SOT317-1), QFP100 (SOT317-2), QFP100 (SOT382-1) or QFP160 (SOT322-1).

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150 °C within 6 seconds. Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### Repairing soldered joints

Fix the component by first soldering two diagonally-opposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C. When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.