# **MOS INTEGRATED CIRCUIT** μ**PD70433**

## V55PI™ **16-BIT MICROPROCESSOR**

#### DESCRIPTION

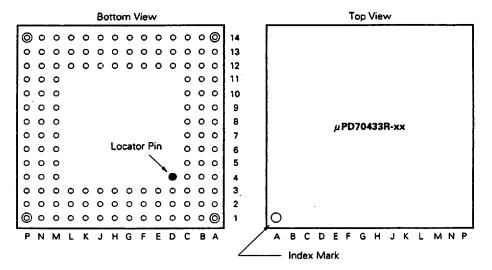

The µPD70433 (V55PI) is a microprocessor in which a 16-bit CPU, RAM, serial interface, parallel interface, A/D converter, timers; DMA controller, interrupt controller, etc., are integrated in a single chip.

The V55PI is software-compatible with the μPD70320 and 70330 (V25™ and V35™) single-chip microcontrollers. The V55Pl provides a migration path from the V25. It offers higher-level functions and higher performance, and is particularly suitable for control of data processing systems associated with mechanical control, including printer and facsimile.

Detailed functions are described in the following user's manuals, which should be read when carrying out design work.

| <ul> <li>V55PI User's Manual Hardware</li> </ul>           | : IEU-1418 |

|------------------------------------------------------------|------------|

| <ul> <li>V55SC, V55PI User's Manual Instruction</li> </ul> | : IEU-1416 |

#### **FEATURES**

- Internal 16-bit architecture, selectable external data bus width (16/8 bits)

- Software compatible with V20<sup>™</sup> and V30<sup>™</sup> (native mode) and V25 and V35 (includes additional instructions)

- Minimum instruction cycle: 160 ns/12.5 MHz (external 25 MHz)

- 125 ns/16 MHz (external 32 MHz)

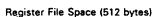

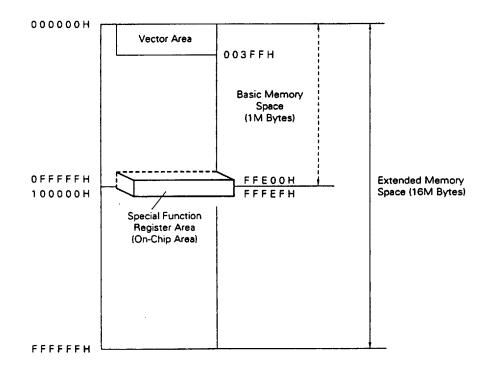

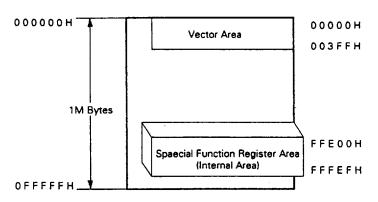

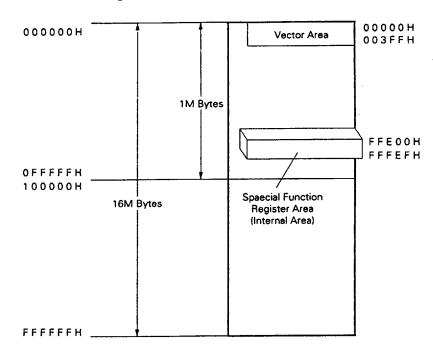

- 1-Mbyte basic memory space

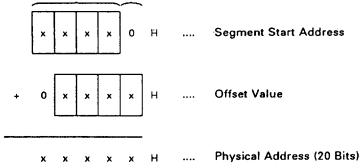

- 16-Mbyte extended memory space

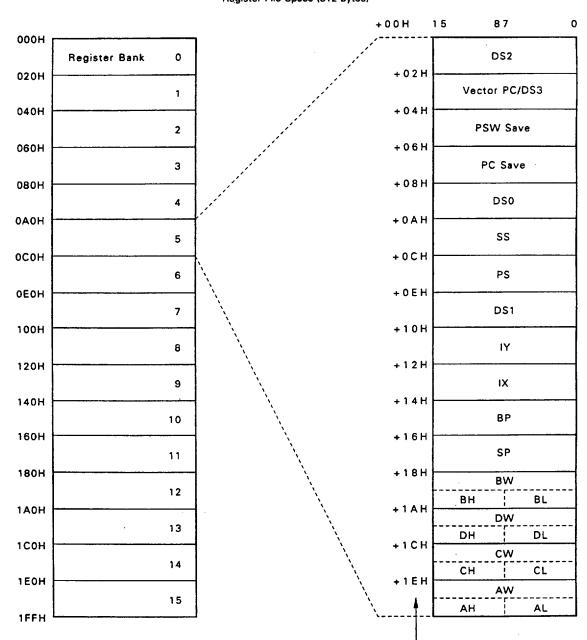

- Register file space (in on-chip RAM) : 512 bytes/16 register banks

- I/O space : 64K bytes

• Address space: 16M bytes:-

- Automatic wait control with memory space divided in variable sizes (max, 6 blocks)

- I/O line (input ports: 11 bits, input/output ports: 42 bits)

- DMA controller (DMAC): Max. 4-channel configuration possible

- Four DMA transfer modes (single transfer, demand release, single step, burst)

- Intelligent DMA modes 1 and 2

- Serial interface: 2 channels

- Asynchronous mode (UART) or clocked mode (CSI) selectable

- Parallel interface: 8 bits

- · Centronics data input/output and general-purpose data input/output

- A/D converter (8 bits): 4 channels

- Real-time output port: 4 bits × 2 channels or 8 bits × 1 channel

- PMW (Pulse Width Modulation) output function : 8 bits

The information in this document is subject to change without notice.

Document No. IC-3670 (O.D.No. IC-82578) Date Published June 1995 P © NEC Corporation 1995 Printed in Japan

6427525 0063107 744 📟

- interrupt controller

- Programmable priority (4 levels)

- Three interrupt servicing methods

- Vectored interrupt function, register bank switching function, macro service function

- 16-bit timer: 4 channels

- Watchdog timer function

- Software interval timer (16 bits)

- Address field wait insertion function and RAS/CAS switchover timing generation function

- DRAM and pseudo-SRAM refresh functions

- Standby functions (STOP mode, HALT mode)

- On-chip clock generator

#### APPLICATIONS

• Control of data processing systems using serial or parallel communication (Data processing terminals, printer, G3 facsimile, etc.)

#### **ORDERING INFORMATION**

| Part Number       | Package                          | Maximum Operating<br>Frequency (MHz) |  |

|-------------------|----------------------------------|--------------------------------------|--|

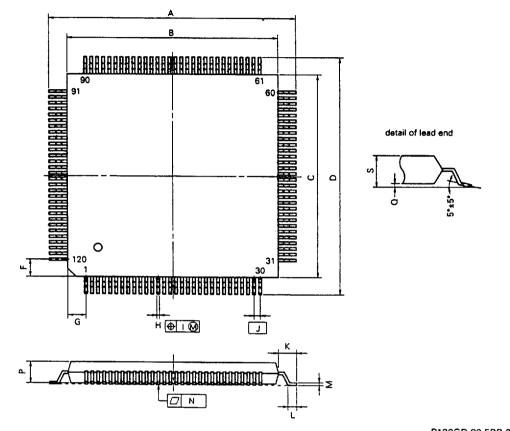

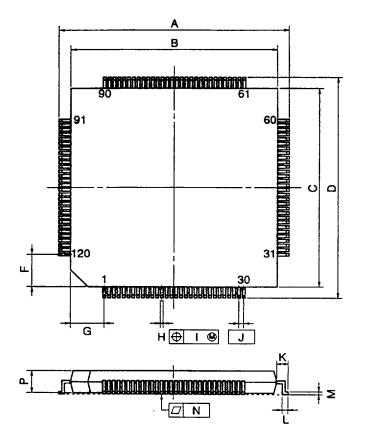

| μPD70433GD-5BB    | 120-pin plastic QFP (28 x 28 mm) | 12.5                                 |  |

| μPD70433GD-12-5BB | 120-pin plastic QFP (28 x 28 mm) | 12.5                                 |  |

| μPD70433GD-16-5BB | 120-pin plastic QFP (28 x 28 mm) | 16                                   |  |

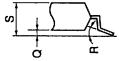

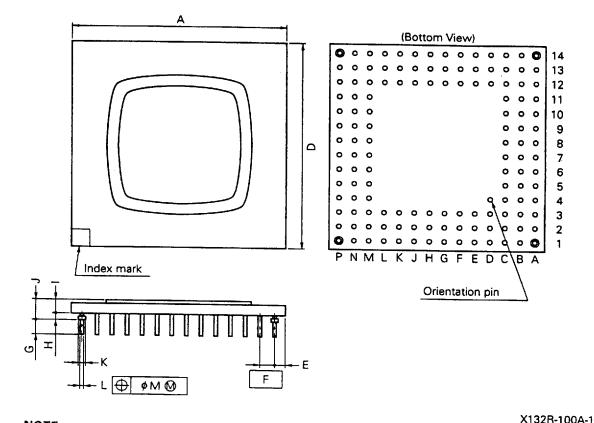

| μPD70433R-12      | 132-pin ceramic PGA              | 12.5                                 |  |

| μPD70433R-16      | 132-pin ceramic PGA              | 16                                   |  |

| μPD70433GJ-12-3EB | 120-pin plastic QFP (20 x 20 mm) | 12.5                                 |  |

| μPD70433GJ-16-3EB | 120-pin plastic QFP (20 x 20 mm) | 16                                   |  |

## 🖿 6427525 OO631O8 68O 📟

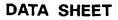

#### **PIN CONFIGURATION (TOP VIEW)**

(1) 120-Pin Plastic QFP (28 x 28 mm), 120-pin plastic QFP (fine pitch) (20 x 20 mm)

Remark IC: Internally Connected

- Notes 1. The IC (H) pin should be connected to Vod with an external resistor (1 to 10 k $\Omega$ ).

- 2. The IC (L) pin should be connected to GND with an external resistor (1 to 10 k $\Omega$ ).

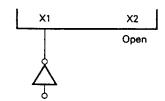

3. No connection should be made to the OPEN pin.

#### 🔳 6427525 0063109 517 🔳

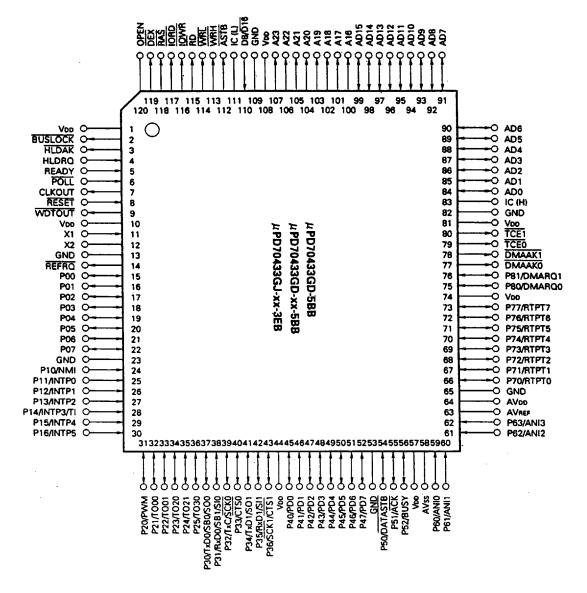

#### (2) 132-Pin Ceramic PGA

| Remark | The locator pin is not included in the pin co | unt. |

|--------|-----------------------------------------------|------|

|--------|-----------------------------------------------|------|

| No.        | Signal Nane  | Port | No.             | Signal Name  | Port            | No. | Signal Name | Port |

|------------|--------------|------|-----------------|--------------|-----------------|-----|-------------|------|

| A1         | ANI1         | P61  | B5              | PD7          | P47             | C9  | CTSO        | P33  |

| A2         | AVss         | -    | B6              | PD5          | P45             | C10 | TO30        | P25  |

| A3         | ACK          | P51  | B7              | PD2          | P42             | C11 | TO00        | P21  |

| A4         | DATASTB      | P50  | B8              | PD0          | P40             | C12 | NC          | -    |

| A5         | PD6          | P46  | <b>B</b> 9      | RxD1/SI1     | <del>P</del> 35 | C13 | INTP4       | P15  |

| A6         | PD4          | P44  | B10             | RxD0/SB1/SI0 | P31             | C14 | INTP0       | P11  |

| A7         | PD1          | P41  | B11             | TO21         | P24             | D1  | RTPT2       | P72  |

| <b>A</b> 8 | NC           | 1    | B12             | TO01         | P22             | D2  | GND         | -    |

| A9         | SCK1/CTS1    | P36  | B13             | NC           | —               | D3  | ANI3        | P63  |

| A10        | TxD1/SO1     | P34  | _B14            | INTP3/TI     | P14             | D12 | INTP5       | P16  |

| A11        | TxC/SCK0     | P32  | C1              | RTPT1        | P71             | D13 | INTP2       | P13  |

| A12        | TxD0/SB0/SO0 | P30  | C2              | AVref        | -               | D14 | NMI         | P10  |

| A13        | TO20         | P23  | СЗ              | NC           | -               | E1  | RTPT5       | P75  |

| A14        | PWM          | P20  | C4              | NC           | -               | E2  | RTPT3       | P73  |

| B1         | AVDO         | _    | C5              | Voo          | —               | E3  | RTPT0       | P70  |

| B2         | ANI2         | P62  | C6 <sup>`</sup> | GND          | _               | E12 | INTP1       | P12  |

| 83         | ANIO         | P60  | C7              | PD3          | P43             | E13 | GND         | -    |

| B4         | BUSY         | P52  | C8              | Vod          | -               | E14 | _           | P06  |

- 4

🖬 6427525 0063110 239 🎟

| No. | Signal Nane | Port | No. | Signal Name | Port | No.            | Signal Name | Port |

|-----|-------------|------|-----|-------------|------|----------------|-------------|------|

| F1  | RTPT7       | P77  | КЗ  | AD2         |      | N3             | AD9         |      |

| F2  | RTPT6       | P76  | K12 | POLL        |      | N4             | AD11        | —    |

| F3  | RTPT4       | P74  | K13 | WDTOUT      | —    | N5             | AD14        | _    |

| F12 |             | P07  | K14 | X1 ·        |      | N6             | A18         |      |

| F13 |             | P05  | L1  | AD0         |      | N7             | A21         | —    |

| F14 |             | P04  | L2  | AD3         |      | N8             | A23         |      |

| G1  | NC          | —    | L3  | AD6         | —    | N9             | D8/D16      |      |

| G2  | DMARQO      | P80  | L12 | BUSLOCK     | —    | N10            | ASTB        | _    |

| G3  | Vod         | —    | L13 | READY       |      | N11            | IOWR        |      |

| G12 | —           | P03  | L14 | RESET       |      | N12            | DEX         | —    |

| G13 |             | P02  | M1  | AD1         |      | N13            | Voo         | _    |

| G14 |             | P01  | M2  | AD5         |      | N14            | HLDRQ       |      |

| H1  | DMARQ1      | P81  | М3  | NC          |      | P1             | AD7         | —    |

| H2  | DMAAKO      | —    | M4  | AD8         |      | P2             | AD10        | —    |

| НЗ  | DMAAK1      | —    | M5  | AD12        | —    | P3             | AD13        | —    |

| H12 | REFRO       | —    | M6  | A16         | —    | P4             | AD15        |      |

| H13 |             | P00  | M7  | A20         |      | P5             | A17         | -    |

| H14 | NC          | —    | M8  | Voo         |      | P6             | A19         | —    |

| J1  | TCEO        |      | M9  | WRH         |      | <del>P</del> 7 | NC          |      |

| J2  | TCE1        |      | M10 | IORD        | _    | P8             | A22         |      |

| J3  | GND         |      | М11 | NC          |      | P9             | GND         |      |

| J12 | Voo         |      | M12 | NC          |      | P10            | IC (L)      | _    |

| J13 | X2          |      | М13 | HLDAK       | -    | P11            | WRL         |      |

| J14 | GND         |      | M14 | CLKOUT      | —    | P12            | RD          | —    |

| К1  | Voo         |      | N1  | AD4         |      | P13            | RAS         | _    |

| К2  | IC (H)      |      | N2  | NC          |      | P14            | OPEN        | _    |

Remark IC: Internally Connected NC: Non-Connection

- 2. The IC (L) pin should be connected to GND with an external resistor (1 to 10 k $\Omega$ ).

- 3. No connection should be made to the OPEN pin.

🎟 6427525 0063lll 175 🎟

Notes 1. The IC (H) pin should be connected to Vop with an external resistor (1 to 10 k $\Omega$ ).

## CONTENTS

| 1.1       LIST OF PIN FUNCTION       10         1.1.1       Port Pins       10         1.1.2       Non-Port Pins       11         2.       BLOCK CONFIGURATION       14         2.1       BUS CONTROL UNIT (BCU)       14         2.2       EXECUTION UNIT (BCU)       14         2.3       INTERRUPT CONTROLLER (INTC)       14         2.4       DMA CONTROLLER (INTC)       14         2.5       UART/CLOCKED SERIAL INTERFACE (UART/CSI)       14         2.6       PARALLEL INTERACE UNIT (PUI)       14         2.7       A/D CONVERTER UNIT (8-BIT A/D)       14         2.8       TIMER/COUNTER UNIT (TCU)       14         2.9       PUW (PULSE WIDT MODULATION) UNIT (PWM)       14         2.10       WATCHDOG TIMER (WOT)       14         2.11       PORTS (PORT)       14         2.12       CLOCK GENERATOR (CG)       15         2.13       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.1       FEATURES       16         3.1       FEATURES       16         3.1       FEATURES       16         3.2.1       Registers (SP, BP) end Index Registers                                                                                         | 1. | PIN I | FUNCTIONS                              | 10 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|----------------------------------------|----|

| 1.1.2       Non-Port Pins       11         2.       BLOCK CONFIGURATION       14         2.1       BUS CONTROL UNIT (BCU)       14         2.2       EXECUTION UNIT (ECU)       14         2.3       INTERRUPT CONTROLLER (INTC)       14         2.4       DMA CONTROLLER (INTC)       14         2.5       UART/CLOCKED SERIAL INTERFACE (UART/CSI)       14         2.6       PARALLEL INTERFACE (UART/CSI)       14         2.7       A/D CONVERTER UNIT (8-BIT A/D)       14         2.8       PARALLEL INTERFACE UNIT (PUI)       14         2.7       A/D CONVERTER UNIT (8-BIT A/D)       14         2.8       PM (PULSE WIDTH MODULATION) UNIT (PWM)       14         2.9       PWM (PULSE WIDTH MODULATION) UNIT (PWM)       14         2.10       WATCHDOG TIMER (WDT)       14         2.11       PORTS (PORT)       14         2.12       PORTS (WIDT MODULATION)       14         2.13       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       14         2.13       CLOCK GENERATOR (CG)       15         3.2       POINTEROL (FUNCTIONS       16         3.1       FEATURES       16 <t< th=""><th></th><th>1.1</th><th>LIST OF PIN FUNCTION</th><th></th></t<> |    | 1.1   | LIST OF PIN FUNCTION                   |    |

| 2. BLOCK CONFIGURATION       14         2.1 BUS CONTROL UNIT (BCU)       14         2.2 EXECUTION UNIT (EXU)       14         2.3 INTERRUPT CONTROLLER (INTC)       14         2.4 DMA CONTROLLER (INTC)       14         2.5 UART/CLOCKED SERIAL INTERFACE (UART/CSI)       14         2.6 PARALLEL INTERFACE UNIT (PUU)       14         2.7 A/D CONVERTE UNIT (FILI)       14         2.8 TIMER/COUNTRE UNIT (FILI)       14         2.10 WATCHDOG TIMER (WDT)       14         2.11 PORTS (FORT)       14         2.12 REAL-TIME OUTPUT PORT (RTOP)       14         2.13 CLOCK GENERATOR (CG)       15         2.14 SOFTWARE INTERVAL TIMER (SIT)       15         3.1 FEATURES       16         3.1 FEATURES       16         3.1 FEATURES       16         3.2 REGISTERS       17         3.2.3 Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4 Segment Registers (DS2, DS1)       20         3.2.5 Extended Segment Registers (IX, ER)       21         3.2.6 Special Function Registers (ISR)       22                                 |    |       | 1.1.1 Port Pins                        | 10 |

| 2.1       BUS CONTROL UNIT (BCU)       14         2.2       EXECUTION UNIT (EXU)       14         2.3       INTERRUPT CONTROLLER (INTC)       14         2.4       DMA CONTROLLER (IMTC)       14         2.5       UART/CLOCKED SERIAL INTERFACE (UART/CSI)       14         2.6       PARALLEL INTERFACE UNIT (PU)       14         2.7       A/D CONVERTER UNIT (B-BIT A/D)       14         2.8       TIMER/COUNTER UNIT (B-BIT A/D)       14         2.9       PWM (PULSE WIDTH MOULLATION) UNIT (PWM)       14         2.9       PWM (PULSE WIDTH MOULLATION) UNIT (PWM)       14         2.10       WATCHDOG TIMER (WDT)       14         2.11       PORTS (PORT)       14         2.12       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.1       FEATURES       16         3.1       FEATURES       16         3.2       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.1       Registers (SP, S, DSO, DS1)       20         3.2.2       Signert Registers (SF, S)       20         3.2.4       Segment Registers (SF, BP)       21         3.2.5       Extended Segment Registers                                              |    |       | 1.1.2 Non-Port Pins                    | 11 |

| 2.1       BUS CONTROL UNIT (BCU)       14         2.2       EXECUTION UNIT (EXU)       14         2.3       INTERRUPT CONTROLLER (INTC)       14         2.4       DMA CONTROLLER (IMTC)       14         2.5       UART/CLOCKED SERIAL INTERFACE (UART/CSI)       14         2.6       PARALLEL INTERFACE UNIT (PU)       14         2.7       A/D CONVERTER UNIT (B-BIT A/D)       14         2.8       TIMER/COUNTER UNIT (B-BIT A/D)       14         2.9       PWM (PULSE WIDTH MOULLATION) UNIT (PWM)       14         2.9       PWM (PULSE WIDTH MOULLATION) UNIT (PWM)       14         2.10       WATCHDOG TIMER (WDT)       14         2.11       PORTS (PORT)       14         2.12       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.1       FEATURES       16         3.1       FEATURES       16         3.2       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.1       Registers (SP, S, DSO, DS1)       20         3.2.2       Signert Registers (SF, S)       20         3.2.4       Segment Registers (SF, BP)       21         3.2.5       Extended Segment Registers                                              | 2. | BLO   | CK CONFIGURATION                       | 14 |

| 2.2       EXECUTION UNIT (EXU)       14         2.3       INTERRUPT CONTROLLER (INTC)       14         2.4       DMA CONTROLLER (INTC)       14         2.5       UART/CLOCKED SERIAL INTERFACE (UART/CSI)       14         2.6       PARALLEL INTERFACE UNIT (PU)       14         2.7       A/D CONVERTER UNIT (BIT A/D)       14         2.8       TIMER/COUNTER UNIT (TCU)       14         2.8       TIMER/COUNTER UNIT (TCU)       14         2.9       PWM (PULSE WIDT H MODULATION) UNIT (PWM)       14         2.10       WATCHOOG TIMER (WDT)       14         2.11       PORTS (PORT)       14         2.12       REALTIME OUTPUT PORT (RTOP)       14         2.13       CLOCK GENERATOR (CG)       15         3.1       CPU FUNCTIONS       15         3.2       REGISTERS       17         3.2.1       REGISTERS       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (DS2, DS3)       21         3.2.5       Extended Segment Registers (IX, IY)       20         3.2.4       Special Function Registers (SFR) <td></td> <td></td> <td></td> <td></td>        |    |       |                                        |    |

| 2.3       INTERRUPT CONTROLLER (INTC)       14         2.4       DMA CONTROLLER (IMAC)       14         2.5       UART/CLOCKED SERIAL INTERFACE (UART/CSI)       14         2.6       PARALLEL INTERFACE UNIT (PIU)       14         2.7       A/D CONVERTER UNIT (BUT A/D)       14         2.8       TIMER/COUNTER UNIT (FU)       14         2.8       TIMER/COUNTER UNIT (FU)       14         2.9       PWM (PULSE WIDTH MODULATION) UNIT (PWM)       14         2.10       WATCHOOG TIMER (WDT)       14         2.11       PORTS (PORT)       14         2.12       REAL-TIME OUTPUT PORT (RTOP)       14         2.13       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.       CPU FUNCTIONS       16         3.1       FEATURES       16         3.1       FEATURES       16         3.2       Register Banks       17         3.2.3       Pointers (SF, PP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (PS, SS, DS, DS, DS1)       20         3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Register (SSR)                                                      |    | 2.2   |                                        |    |

| 2.4       DMA CONTROLLER (DMAC)       14         2.5       UART/CLOCKED SERIAL INTERFACE (UART/CSI)       14         2.6       PARALLEL INTERFACE (UART/CSI)       14         2.6       PARALLEL INTERFACE (UART/CSI)       14         2.7       A/D CONVERTER UNIT (PU)       14         2.7       A/D CONVERTER UNIT (BU)       14         2.8       TIMER/COUNTER UNIT (CU)       14         2.9       PWM (PULSE WIDTH MODULATION) UNIT (PWM)       14         2.10       WATCHDOG TIMER (WDT)       14         2.11       PORTS (PORT)       14         2.12       REAL-TIME OUTPUT PORT (RTOP)       14         2.13       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.       CPU FUNCTIONS       16         3.1       FEATURES       16         3.2       Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SF, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (DS2, DS3)       21         3.2.5       Extended Segmert Registers (IX, IY)       20         3.2.4       Segment Registers (DS2, DS3)       21         3.2.5       Extended Segmert Regis                                             |    | 2.3   |                                        |    |

| 2.5       UART/CLOCKED SERIAL INTERFACE (UART/CSI)       14         2.6       PARALLEL INTERFACE UNIT (PU)       14         2.7       A/D CONVERTER UNIT (AD)       14         2.8       TIMER/COUNTER UNIT (TCU)       14         2.9       PWM (PULSE WIDTH MODULATION) UNIT (PWM)       14         2.10       WATCHDOG TIMER (WDT)       14         2.11       PORTS (PORT)       14         2.12       REAL-TIME OUTPUT PORT (RTOP)       14         2.13       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.1       FEATURES       16         3.1       FEATURES       16         3.2.1       Register Banks       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (DS2, DS3)       21         3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.2.7       Special Function Registers (SFR)       22         3.2.8       Special Function Registers (SFR)       23         3.4       P                                             |    |       |                                        |    |

| 2.6       PARALLEL INTERFACE UNIT (PIU)       14         2.7       A/D CONVERTER UNIT (FBIT A/D)       14         2.8       TIMER/COUNTER UNIT (CU)       14         2.9       PWM (PULSE WIDTH MODULATION) UNIT (PWM)       14         2.10       WATCHDOG TIMER (WDT)       14         2.11       PORTS (PORT)       14         2.12       REAL-TIME OUTPUT PORT (RTOP)       14         2.13       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.       CPU FUNCTIONS       16         3.1       FEATURES       16         3.2       REGISTERS       17         3.2.1       REGISTERS       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (DS2, DS3)       21         3.2.5       Extended Segment Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (FSW)       22         3.5.1       Besic Memory Space       24         3.5.4       Vector Table Area       36                                                                                     |    | 2.5   |                                        |    |

| 2.7       A/D CONVERTER UNIT (8-BIT A/D)       14         2.8       TIMER/COUNTER UNIT (TCU)       14         2.9       PWM (PULSE WIDTH MODULATION) UNIT (PWM)       14         2.10       WATCHDOG TIMER (WDT)       14         2.11       PORTS (PORT)       14         2.12       REAL-TIME OUTPUT PORT (RTOP)       14         2.13       SOFTWARE INTERVAL TIMER (SIT)       15         3.       CPU FUNCTIONS       16         3.1       FEATURES       16         3.1       FEATURES       16         3.2       REGISTERS       16         3.2       REGISTERS       17         3.2.1       Register Banks       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (DS2, DS3)       21         3.2.5       Steil Function Registers (DS2, DS3)       21         3.2.6       Special Function Registers (DS2, DS3)       21         3.2.6       Special Function Registers (DS2, DS3)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       22                                                                     |    |       |                                        |    |

| 2.8       TIMER/COUNTER UNIT (TCU)       14         2.9       PWM (PULSE WIDTH MODULATION) UNIT (PWM)       14         2.10       WATCHDOG TIMER (WDT)       14         2.11       PORTS (PORT)       14         2.12       REAL-TIME OUTPUT PORT (RTOP)       14         2.13       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.       CPU FUNCTIONS       16         3.1       FEATURES       16         3.1       FEATURES       16         3.2.1       Register Banks       17         3.2.2       General Registers (PS, SD, DSO, DS1)       20         3.2.4       Segment Registers (DS2, DS3)       21         3.2.5       Extended Segment Registers (SFR)       22         3.2.6       Special Function Registers (SFR)       23         3.4       PROGRAM COUNTER (PC)       23         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       24         3.5.3       Special Function Register Area       36         3.5.4       Vector Table Area       36         3.5.7       Extended Memory Space       24         3.5.8 <td></td> <td>2.7</td> <td></td> <td></td>                                         |    | 2.7   |                                        |    |

| 2.9       PWM (PULSE WIDTH MODULATION) UNIT (PWM)       14         2.10       WATCHDOG TIMER (WDT)       14         2.11       PORTS (PORT)       14         2.12       REAL-TIME OUTPUT PORT (RTOP)       14         2.13       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.       CPU FUNCTIONS       16         3.1       FEATURES       16         3.1       FEATURES       16         3.2       REGISTERS       16         3.2.1       Register Banks       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (DS2, DS3)       21         3.2.5       Extended Segment Registers (ISR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       26         3.5.2       Extended Memory Space       26         3.5.3       Special Function Register Area       36         3.5.4                                                                                           |    | 2.8   |                                        |    |

| 2.11       PORTS (PORT)       14         2.12       REAL-TIME OUTPUT PORT (RTOP)       14         2.13       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.       CPU FUNCTIONS       16         3.1       FEATURES       16         3.1       FEATURES       16         3.2       REGISTERS       17         3.2.1       Register Banks       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       25         3.5.3       Special Function Register Area       36         3.5.4       Vector Table Area       36         3.5.1       Basic Memory Space       36         3.5.3                                                                                                |    | 2.9   |                                        |    |

| 2.11       PORTS (PORT)       14         2.12       REAL-TIME OUTPUT PORT (RTOP)       14         2.13       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.       CPU FUNCTIONS       16         3.1       FEATURES       16         3.1       FEATURES       16         3.2       REGISTERS       17         3.2.1       Register Banks       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       25         3.5.3       Special Function Register Area       36         3.5.4       Vector Table Area       36         3.5.1       Basic Memory Space       36         3.5.3                                                                                                |    | 2.10  |                                        |    |

| 2.12       REAL-TIME OUTPUT PORT (RTOP)       14         2.13       CLOCK GENERATOR (CG)       15         2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.       CPU FUNCTIONS       16         3.1       FEATURES       16         3.2       REGISTERS       17         3.2.1       Register Banks       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (DS, DS, DS1)       20         3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       26         3.5.4       Vector Table Area       36         3.5.1       Basic Memory Space       36         3.5.2       Extended Memory Space       36         3.5.4       Vector Table Area       36         3.5.7<                                                                                |    | 2.11  | PORTS (PORT)                           |    |

| 2.14       SOFTWARE INTERVAL TIMER (SIT)       15         3.       CPU FUNCTIONS       16         3.1       FEATURES       16         3.2       REGISTERS       17         3.2.1       Register Banks       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (DS2, DS3)       21         3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       25         3.5.3       Special Function Register Area       36         3.5.4       Vector Table Area       36         3.5.4       Vector Table Area       36         3.5.4       Vector Table Area       36         3.5       MUCTION       35         4.       BUS CONTROL FUNCTIONS       32         4.                                                                                      |    | 2.12  | REAL-TIME OUTPUT PORT (RTOP)           | 14 |

| 3. CPU FUNCTIONS       16         3.1 FEATURES       16         3.2 REGISTERS       17         3.2.1 Register Banks       17         3.2.2 General Registers (AW, BW, CW, DW)       19         3.2.3 Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4 Segment Registers (PS, SS, DSO, DS1)       20         3.2.5 Extended Segment Registers (DS2, DS3)       21         3.2.6 Special Function Registers (DS2, DS3)       21         3.2.6 Special Function Registers (SFR)       22         3.3 PROGRAM COUNTER (PC)       23         3.4 PROGRAM STATUS WORDS (PSW)       23         3.5 MEMORY SPACE       24         3.5.1 Basic Memory Space       24         3.5.2 Extended Memory Space       26         3.5.4 Vector Table Area       36         3.5.4 Vector Table Area       36         3.5.4 Vector Table Area       36         3.5.1 WAIT FUNCTIONS       35         3.5.4 Vector Table Area       36         3.5.4 Vector Table Area                               |    | 2.13  | CLOCK GENERATOR (CG)                   | 15 |

| 3.1       FEATURES       16         3.2       REGISTERS       17         3.2.1       Register Banks       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (PS, SS, DS0, DS1)       20         3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       26         3.5.4       Vector Table Area       36         3.5       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36                                                                                                        |    | 2.14  | SOFTWARE INTERVAL TIMER (SIT)          | 15 |

| 3.1       FEATURES       16         3.2       REGISTERS       17         3.2.1       Register Banks       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (PS, SS, DS0, DS1)       20         3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       26         3.5.4       Vector Table Area       36         3.5       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36                                                                                                        |    |       |                                        |    |

| 3.2       REGISTERS       17         3.2.1       Register Banks       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (PS, SS, DS0, DS1)       20         3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       24         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         3.7       I/O SPACE       36         4.1       WAIT FUNCTION       35         4.2       REFRESH FUNCTION       35         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                          | 3. | CPU   |                                        | -  |

| 3.2.1       Register Banks       17         3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (PS, SS, DS0, DS1)       20         3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       25         3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         3.7       I/O SPACE       36         4.1       WAIT FUNCTIONS       33         4.2       REFRESH FUNCTION       34         4.2       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                    |    | 3.1   |                                        |    |

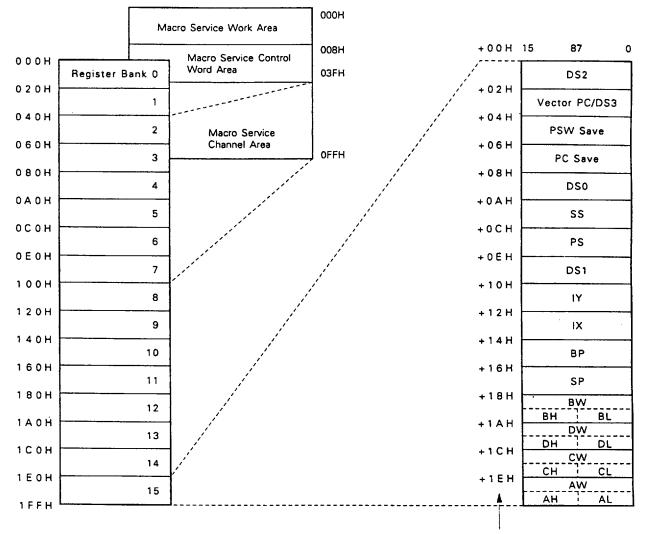

| 3.2.2       General Registers (AW, BW, CW, DW)       19         3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (PS, SS, DS0, DS1)       20         3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       25         3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         4.1       WAIT FUNCTIONS       35         4.2       REFRESH FUNCTION       36         4.2       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                     |    | 3.2   | REGISTERS                              | 17 |

| 3.2.3       Pointers (SP, BP) and Index Registers (IX, IY)       20         3.2.4       Segment Registers (PS, SS, DS0, DS1)       20         3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       25         3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       38         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       39         4.2       Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                   |    |       | -                                      |    |

| 3.2.4       Segment Registers (PS, SS, DS), DS1)       20         3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       24         3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       38         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       39         4.2       Refresh Mode Register (RFM)       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                         |    |       | •                                      |    |

| 3.2.5       Extended Segment Registers (DS2, DS3)       21         3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       25         3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       38         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       39         4.2       Refresh Mode Register (RFM)       41         4.2.1       Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                    |    |       | -                                      |    |

| 3.2.6       Special Function Registers (SFR)       22         3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       25         3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       38         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |       |                                        |    |

| 3.3       PROGRAM COUNTER (PC)       23         3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       25         3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       |                                        |    |

| 3.4       PROGRAM STATUS WORDS (PSW)       23         3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       25         3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       | 3.2.6 Special Function Registers (SFR) |    |

| 3.5       MEMORY SPACE       24         3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       25         3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       38         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       |                                        |    |

| 3.5.1       Basic Memory Space       24         3.5.2       Extended Memory Space       25         3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |       |                                        |    |

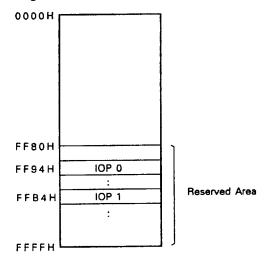

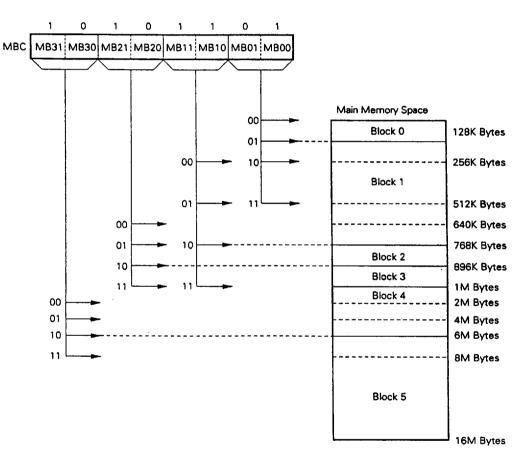

| 3.5.2       Extended Memory Space       25         3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       36         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 3.5   |                                        |    |

| 3.5.3       Special Function Register Area       26         3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       38         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |       |                                        |    |

| 3.5.4       Vector Table Area       34         3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       38         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |                                        |    |

| 3.6       REGISTER FILE SPACE       36         3.7       I/O SPACE       38         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |       | • • •                                  |    |

| 3.7       I/O SPACE       38         4.       BUS CONTROL FUNCTIONS       39         4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |                                        |    |

| 4. BUS CONTROL FUNCTIONS       39         4.1 WAIT FUNCTION       39         4.2 REFRESH FUNCTION       41         4.2.1 Refresh Mode Register (RFM)       41         4.2.2 Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |       |                                        |    |

| 4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 3.7   | I/O SPACE                              | 38 |

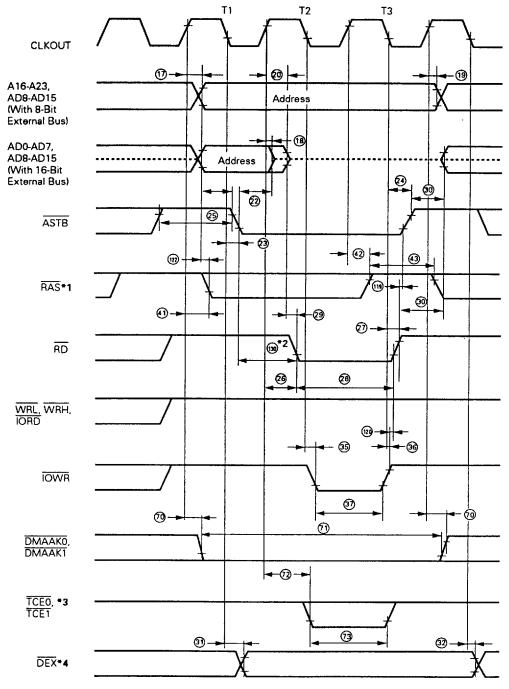

| 4.1       WAIT FUNCTION       39         4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4. | BUS   | CONTROL FUNCTIONS                      | 39 |

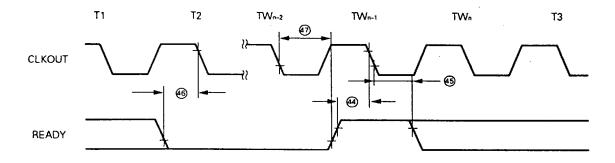

| 4.2       REFRESH FUNCTION       41         4.2.1       Refresh Mode Register (RFM)       41         4.2.2       Wait Control in Refresh Cycle       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |       |                                        |    |

| 4.2.2 Wait Control in Refresh Cycle41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 4.2   |                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |       | 4.2.1 Refresh Mode Register (RFM)      | 41 |

| 4.2.3 Refresh Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |       | 4.2.3 Refresh Address                  | 41 |

🔲 6427525 0063113 T48 📖

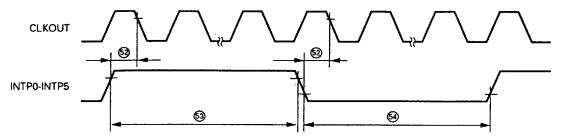

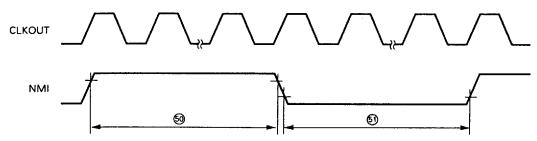

| 5.  | INTE          | RRUPT FUNCTIONS                                  | 42        |

|-----|---------------|--------------------------------------------------|-----------|

|     | 5.1           | FEATURES                                         | 42        |

|     | 5.2           | INTERRUPT RESPONSE METHODS                       |           |

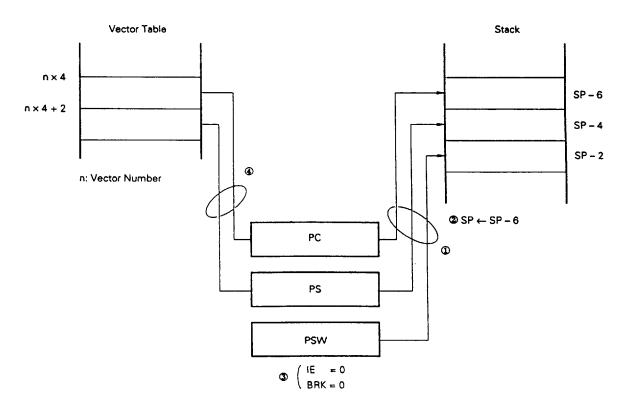

|     |               | 5.2.1 Vectored Interrupts                        | 45        |

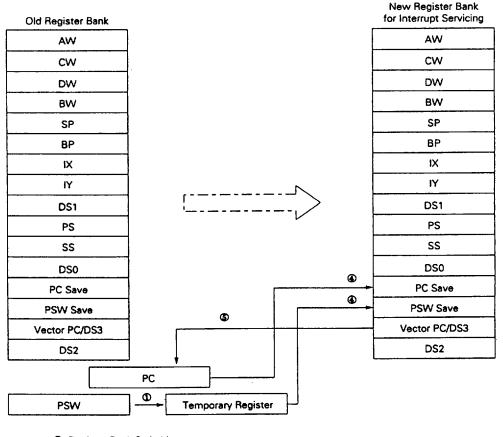

|     |               | 5.2.2 Register Bank Switching Function           | 46        |

|     |               | 5.2.3 Macro Service Function                     | 47        |

|     |               |                                                  |           |

| 6.  | DMA           | FUNCTION (DMA CONTROLLER)                        | 48        |

|     | 6.1           | FEATURES                                         | 48        |

| -   | 050           | AL INTERFACE FUNCTIONS                           | 50        |

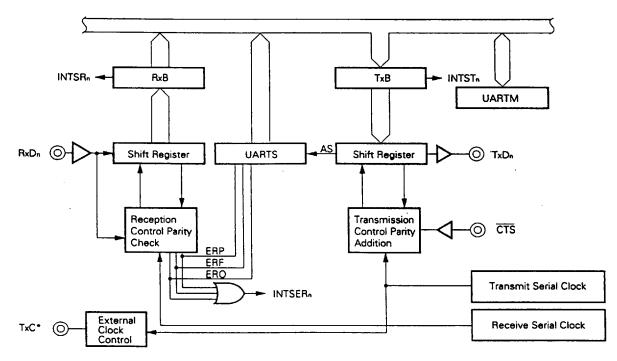

| 7.  |               | FEATURES                                         |           |

|     | 7.1           | PROTOCOLS                                        |           |

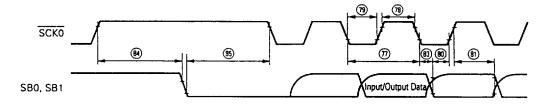

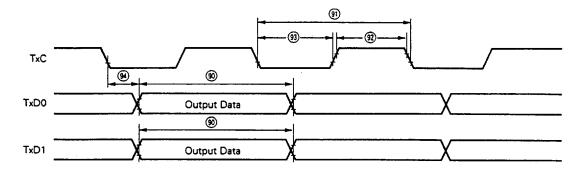

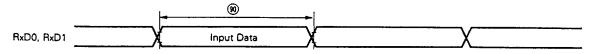

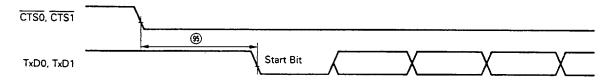

|     | 7.2           |                                                  |           |

|     | 7.3           | UART                                             |           |

|     |               | 7.3.1 Features<br>CLOCKED SERIAL INTERFACE (CSI) |           |

|     | 7.4           |                                                  |           |

|     |               | 7.4.1 Features                                   | 5Z        |

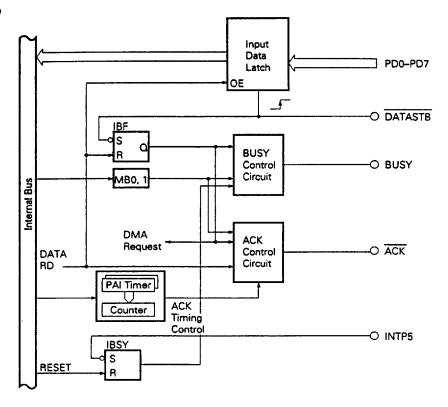

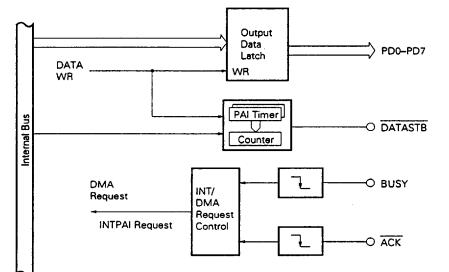

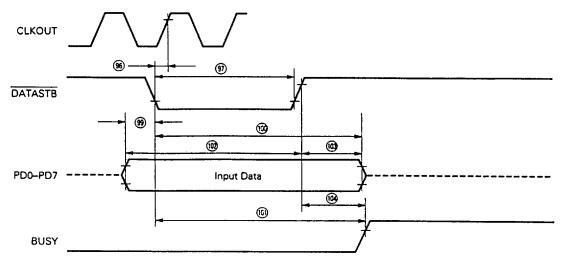

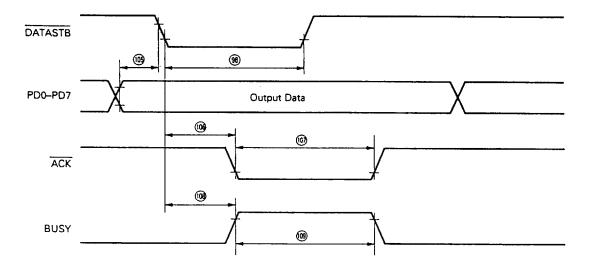

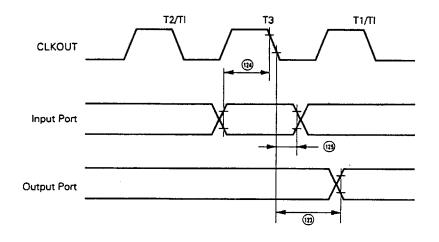

| 8.  | PAR           | ALLEL INTERFACE FUNCTIONS                        | 53        |

|     | 8.1           | FEATURES                                         |           |

|     | 0.1           |                                                  |           |

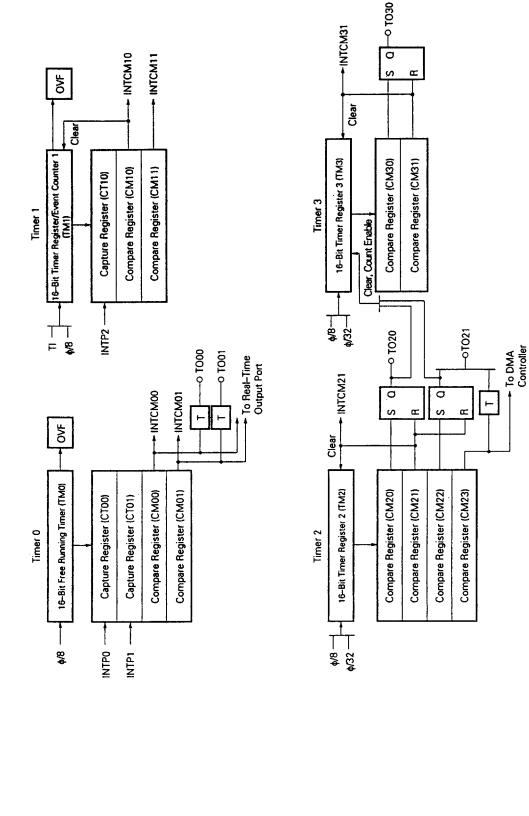

| 9.  | TIM           | R FUNCTION                                       | 55        |

|     | 9.1           | FEATURES                                         | 55        |

|     | 9.2           | TIMER UNIT CONFIGURATION                         |           |

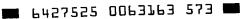

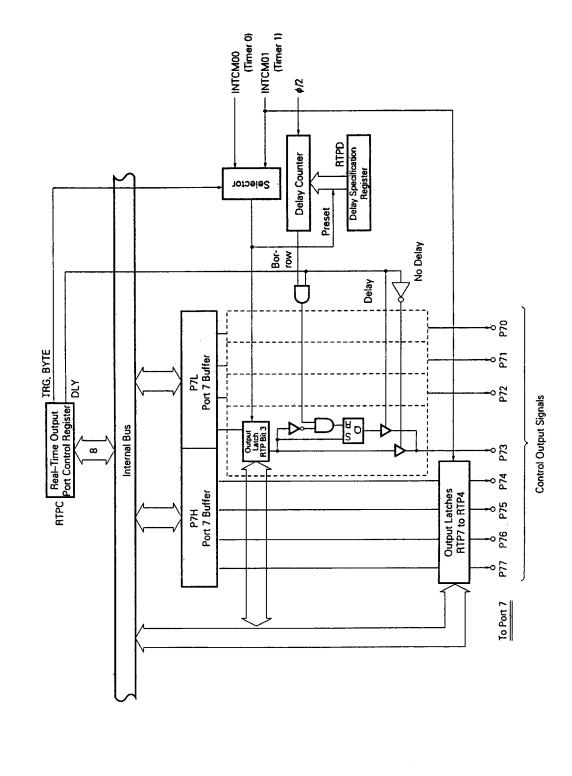

|     | 9.3           | REAL-TIME OUTPUT PORT FUNCTION                   | 57        |

|     |               | 9.3.1 Real-Time Output Port Configuration        | 57        |

|     |               | 9.3.2 Real-Time Output Port Operation            | <b>59</b> |

| 10  | -             | A UNIT                                           | 61        |

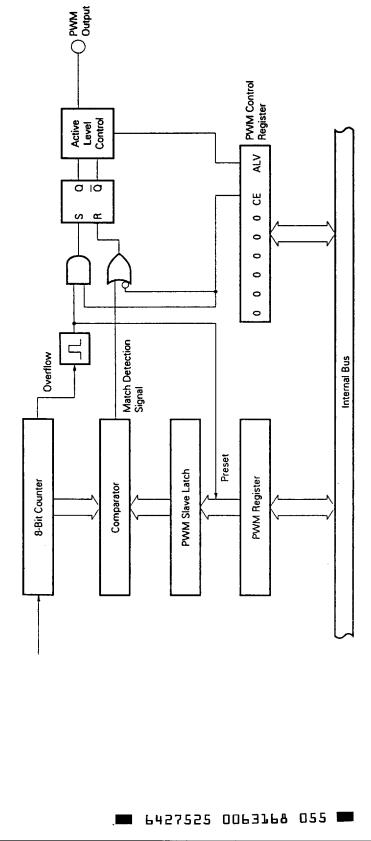

| 10  |               |                                                  |           |

|     | 10.1          |                                                  |           |

|     | 10.2          | PWM UNIT CONFIGURATION                           | 0(        |

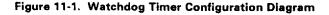

| -11 | . <b>WA</b> I | CHDOG TIMER FUNCTION                             | 63        |

|     | 11.1          | FEATURES                                         |           |

|     | 11.2          |                                                  |           |

|     |               |                                                  |           |

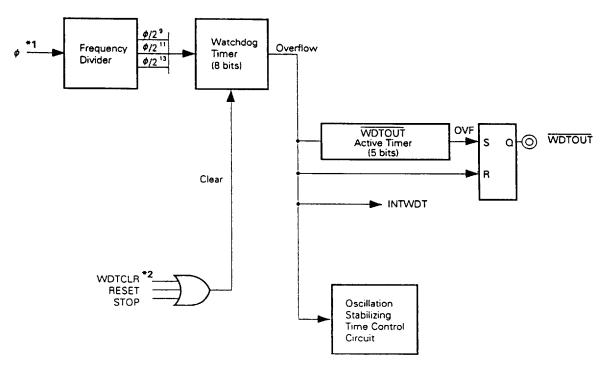

| 12  | -             | CONVERTER FUNCTION                               |           |

|     | 12.1          | FEATURES                                         | 64        |

|     |               |                                                  |           |

| 13  | . STA         | NDBY FUNCTION                                    |           |

|     | 13.1          | HALT MODE                                        |           |

|     | 13.2          | STOP MODE                                        | 67        |

| 4 4 | ~~~           | CK GENERATOR                                     | 60        |

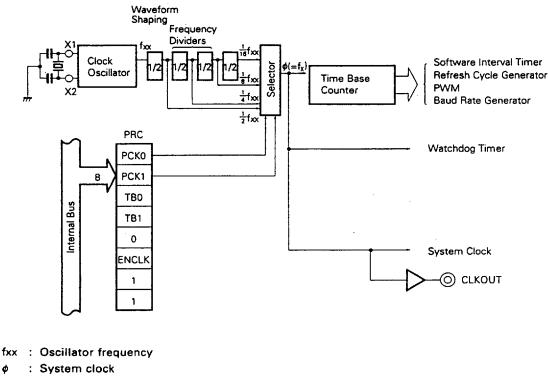

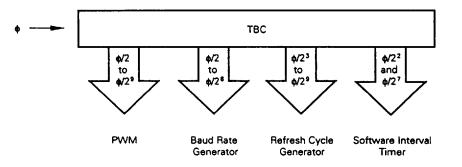

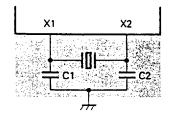

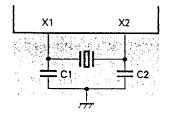

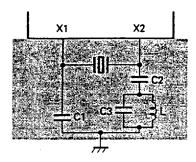

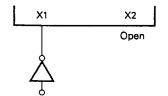

| 14  |               |                                                  |           |

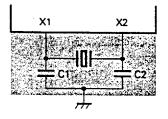

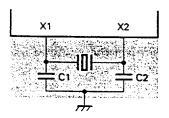

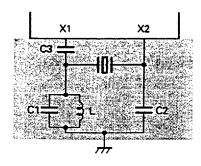

|     | 14.1          | CLOCK GENERATOR CONFIGURATION AND OPERATION      | 00        |

## 6427525 0063114 984 🖬

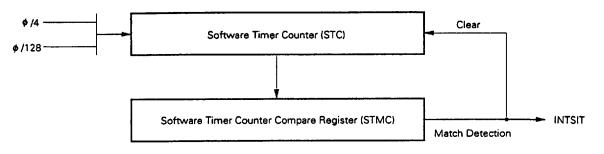

| 15. | SOFT | WARE INTERVAL TIMER FUNCTION                   | ) |

|-----|------|------------------------------------------------|---|

|     | 15.1 | SOFTWARE INTERVAL TIMER CONFIGURATION          | ) |

| 16. | CODE | C INSTRUCTION                                  | 1 |

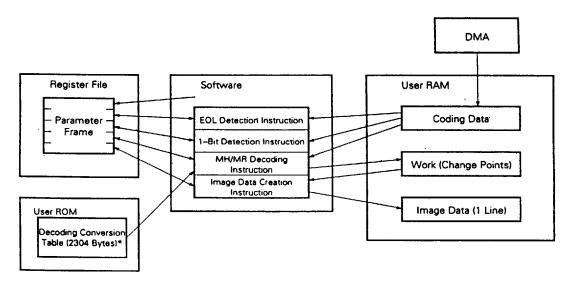

|     | 16.1 | FEATURES                                       | 1 |

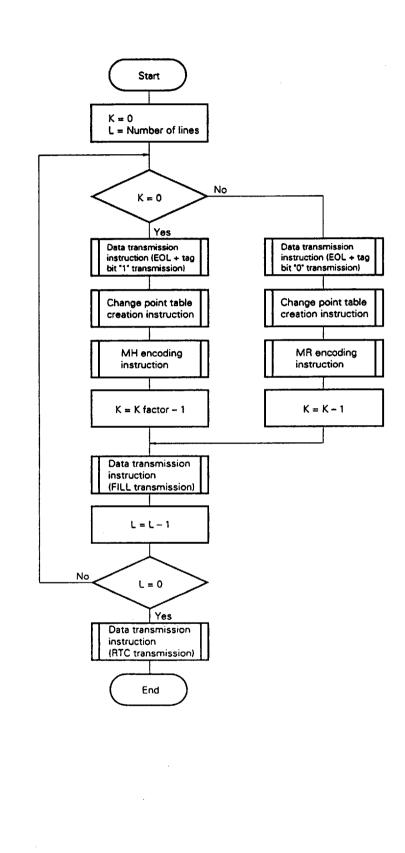

|     | 16.2 | MEMORY MAP                                     | ł |

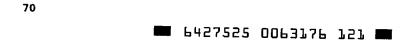

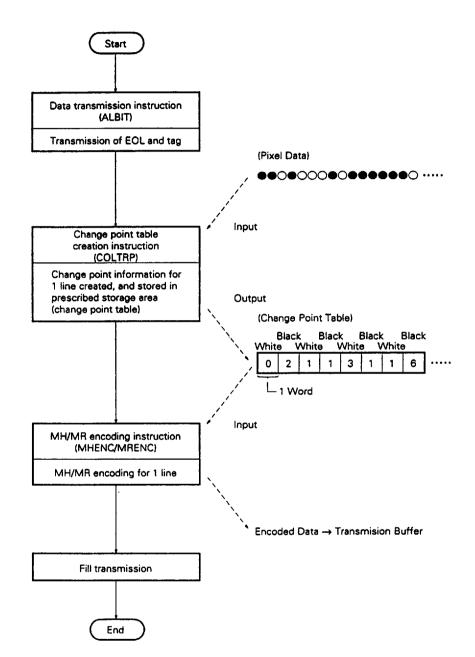

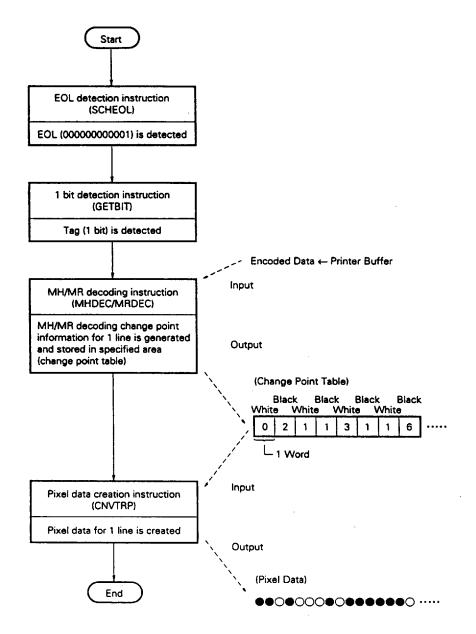

|     | 16.3 | PROCESSING FLOW                                | ; |

| 17. | INST | RUCTION SET                                    | 3 |

|     | 17.1 | INSTRUCTIONS NEWLY ADDED TO V20/V30 AND V25/35 | ł |

|     | 17.2 | INSTRUCTION SET OPERATIONS                     | , |

|     | 17.3 | INSTRUCTION SET TABLE                          | > |

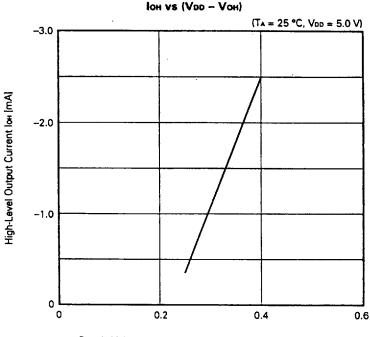

| 18. | ELEC | TRICAL SPECIFICATIONS128                       | } |

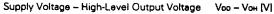

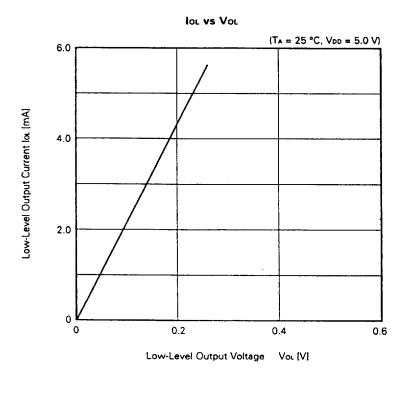

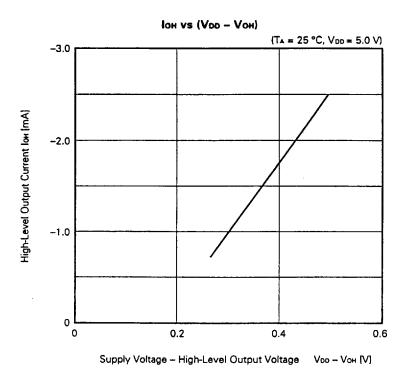

| 19. | CHAF | RACTERISTIC CURVES (FOR REFERENCE ONLY)165     | ; |

| 20. | PACK | AGE DRAWINGS                                   | , |

| 21. | RECO | DMMENDED SOLDERING CONDITIONS                  | ) |

#### **1. PIN FUNCTIONS**

#### 1.1 LIST OF PIN FUNCTIONS

#### 1.1.1 Port Pins

| Pin Name               | Input/Output | Function                                                                                                                                             | Alternate Function |

|------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| <del>P</del> 00 to P07 | Input/output | Port 0<br>Input/output specifiable bit-wise<br>8-bit input/output port                                                                               |                    |

| P10*                   |              |                                                                                                                                                      | NMI                |

| P11                    |              |                                                                                                                                                      | INTPO              |

| P12                    |              |                                                                                                                                                      | INTP1              |

| P13                    | Input        | Port 1<br>7-bit input port                                                                                                                           | INTP2              |

| P14                    |              |                                                                                                                                                      | INTP3/TI           |

| P15                    |              |                                                                                                                                                      | INTP4              |

| P16                    |              |                                                                                                                                                      | INTP5              |

| P20                    |              |                                                                                                                                                      | PWM                |

| P21                    |              |                                                                                                                                                      | TO00               |

| P22                    |              | Port 2                                                                                                                                               | TO01               |

| P23                    |              | Input/output specifiable bit-wise<br>6-bit input/output port<br>Port 3<br>put/output<br>Input/output specifiable bit-wise<br>7-bit input/output port | TO20               |

| P24                    |              |                                                                                                                                                      | TO21               |

| P25                    | -            |                                                                                                                                                      | TO30               |

| P30                    |              |                                                                                                                                                      | TxD0/SB0/SO0       |

| P31                    |              |                                                                                                                                                      | RxD0/SB1/SI0       |

| P32                    |              |                                                                                                                                                      | TxC/SCK0           |

| P33                    | Input/output |                                                                                                                                                      | CTS0               |

| P34                    |              |                                                                                                                                                      | TxD1/SO1           |

| P35                    |              |                                                                                                                                                      | RxD1/SI1           |

| P36                    |              |                                                                                                                                                      | CTS1/SCK1          |

| P40 to P47             |              | .Port 4<br>Input/output specifiable bit-wise<br>8-bit input/output port                                                                              | PD0 to PD7         |

| P50                    |              | Port 5                                                                                                                                               | DATASTB            |

| P51                    |              | Input/output specifiable bit-wise                                                                                                                    | ACK                |

| P52                    |              | 3-bit input/output port                                                                                                                              | BUSY               |

| P60 to P63             | Input        | Port 6<br>Input/output specifiable bit-wise<br>4-bit input/output port                                                                               | ANIO to ANI3       |

| P70 to P77             |              | Port 7<br>Input/output specifiable bit-wise<br>8-bit input/output port                                                                               | RTP0 to RTP7       |

| P80                    | Input/output | Port 8<br>Input/output specifiable bit-wise                                                                                                          | DMARQ0             |

| P81                    |              | 2-bit input/output specifiable bit-wise                                                                                                              | DMARQ1             |

\* Unusable as general-purpose port (non-maskable interrupt)

10

🖬 6427525 OO63116 757 📰

#### 1.1.2 Non-Port Pins

#### (1) Bus control pins

| Pin Name    | Input/<br>Output        | Function                                                                         | Alternate<br>Function |

|-------------|-------------------------|----------------------------------------------------------------------------------|-----------------------|

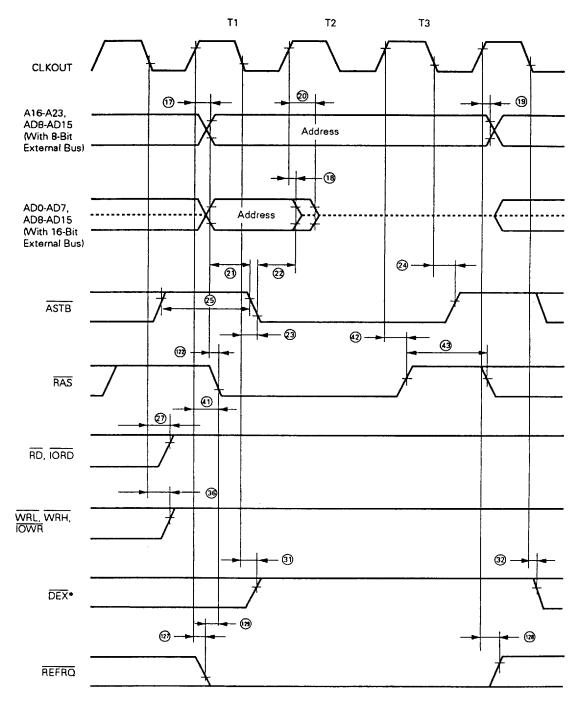

| ASTB        |                         | External bus cycle address strobe signal output in external bus                  |                       |

| RD          |                         | External memory cycle data read strobe signal output in external bus             |                       |

| WRL         | Output                  | External memory cycle lower byte data write strobe signal output in external bus |                       |

| WRH         |                         | External memory cycle upper byte data write strobe signal output in external bus |                       |

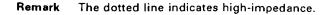

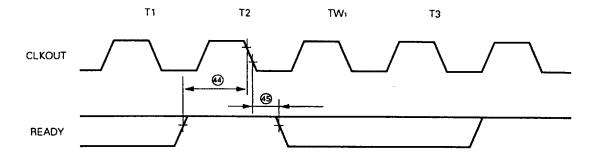

| READY       | Input                   | External bus cycle ready signal input in external bus                            |                       |

| DEX         |                         | External bus cycle upper byte data enable signal output                          |                       |

| RAS         | Output                  | DRAM low address latch timing signal output                                      |                       |

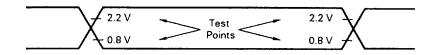

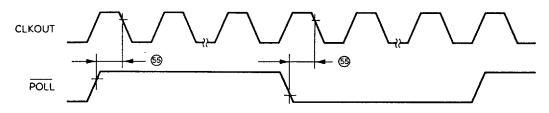

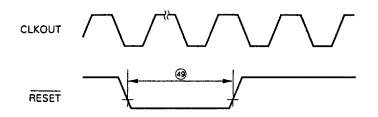

| D8/D16      | Input                   | External bus data bus width selection signal input                               |                       |