# Z80S183

# GENERAL-PURPOSE INTEGRATED MICROPROCESSOR

#### PRODUCT BLOCK DIAGRAM

| WDT     | 8S180 CPU |            | 8 ch, 10<br>bit A/D |

|---------|-----------|------------|---------------------|

| RTC     | MMU       |            |                     |

|         | ZDI       |            |                     |

| 24 1/0  | 2C/T      | 2 DMA      | 10-Bit<br>D/A       |

|         | 2 UART    | CSIO       |                     |

| Fre FLL | 1K ROM    | 2K<br>SRAM | POG                 |

#### **FEATURES**

- Z8S180 Macrocell

- Improved CPU performance. Extended instructions. Code-compatible with Z80 core.

- ✓ Up to 33Mhz speed

- 5V & 3.3V operation

- 2 DMA Channels

- 2 Enhanced UARTs (512Kbps)

- 2 16-Bit Timers

- CSIO

- On-chip MMU (1MByte)

- Edge/Level Triggered Interrupt Controller

- Wait State Generator

- Low Power Modes

- Low EMI modes

- 32-bit GPIO

- 8 Channels 10-bit A/D

- 8 Bit Programmable Output Generator (POG)

- 10-bit Digital to Analog Converter

- 2K Static SRAM

- 1K Boot ROM (Virtual Loader)

- · Real Time Clock

- · Low Power PLL Oscillator

- · Watch-Dog Timer

- Economical 100-pin VQFP package

#### **GENERAL DESCRIPTION**

The Z80S183 is a highly integrated general purpose controller. It consists of the full featured Z80S180 microprocessor, 32-bits of General Purpose I/O, an Analog-to-Digital channel with eight multiplexed inputs, Eight POG channels, a Digital to Analog converter, Watch-Dog Timer, 8K SRAM, a Real-Time Clock, and 1K Boot ROM.

The Z80S183 is an economical 100-pin VQFP package and is available Q499.

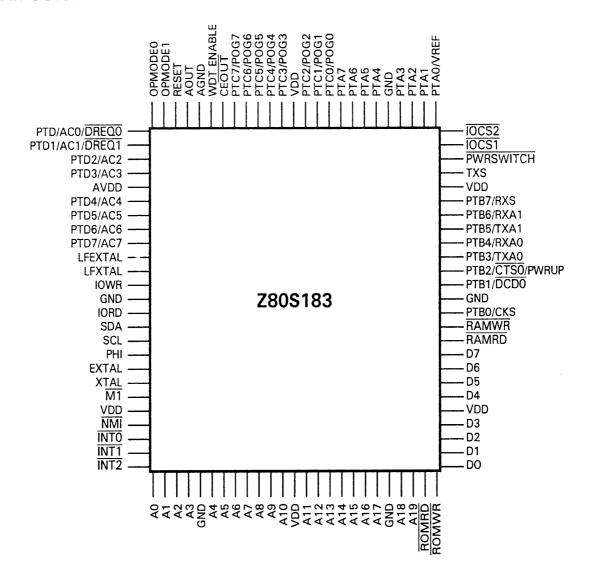

#### PIN-OUTS AND PIN DIRECTION

#### **DETAILED DESCRIPTION**

Z8S180 MICROPROCESSOR CORE. The enhanced Z8S180<sup>™</sup> significantly improves on the previous Z8S180 models while still providing full backward compatibility with existing ZiLOG Z80 devices. The Z8S180/Z8L180 now offers faster execution speeds, power-saving modes, and EMI noise reduction.

Not only does the Z8S180 core consume less power during normal operations than the previous Z80180 models, it has also been designed with three modes intended to further reduce the power consumption. ZiLOG reduced I<sub>cc</sub> power core con-

sumption during STANDBY Mode to a minimum of  $10\mu A$  by stopping the external oscillators and internal clock. The SLEEP mode reduces power by placing the CPU into a stopped state, thereby consuming less current while the on-chip I/O device is still operating. The SYSTEM STOP mode places both the CPU and the on-chip peripherals into a *stopped* mode, thereby reducing power consumption even further

#### **Z80S183 Peripheral Description**

2 FAST ASCI. With the addition of ESCC-like Baud Rate Generators (BRGs), the two ASCIs now have the flexibility and capability to transfer data asynchronously at rates of up to 512 Kbps. In addi-

tion, the ASCI receiver has added a 4-byte First In First Out (FIFO) which can be used to buffer incoming data to reduce the incidence of overrun errors.

2 DMA. The DMAs have been modified to allow for a chain-linking of the two DMA channels when set to take their DMA requests from the same peripherals device. This feature allows for non-stop DMA operation between the two DMA channels, reducing the amount of CPU intervention.

2 COUNTER/TIMERS. Two separate, 16-bit programmable reload counter/timers (PRT) are provided. PRT1 provides an optional output to allow for wave-form generation.

CSIO. The clock serial I/O provides a half-duplex serial transmitter and receiver. This channel can be used for simple high speed data connection to another microprocessor or microcomputer

32-BIT GENERAL PURPOSE I/O. Four 8- bit ports are provided for general purpose I/O. These pins are individually programmable for input or output mode. Each I/O is capable of sourcing and sinking 15mA

WATCH-DOG TIMER. A Watch-Dog timer is provided to prevent code runaway and possible resulting system damage. The range of time constants is up to 4s. The RESET input can be forced as an output upon the terminal count of the Watch-Dog Timer. This action allows external peripherals to be reset along with the Z80S183.

Eight Channel Analog to Digital Converters. There is a single Analog to Digital converter that has eight multiplexed pins. The Analog to Digital Converter is a 10-bit half-flash converter that uses two references resistor ladders for its upper 5 bits (MSB) and lower 5 bits (LSB) conversion. Two reference voltage pins AVCC and AGND are provided for external reference voltage supplies. The minimum conversion time is 8µs

DIGITAL TO ANALOG CONVERTER. There is a 10-bit Digital to Analog converter on board to support applications that require an Analog input. The DAC is a 10-bit register string. The DAC out voltages settles after the internal data is latched into the DAC Data register.

POG. The POG is a memory-mapped programmable event generator which can be used to create complex wave forms, trigger A/D and D/A conversions, and generates processor interrupts. POG events are timed relative to a high-speed clock, creating high speed performance. The POG consumes minimal processor overhead. A POG event is generated by programming event data, a next- event address pointer, and an event timer into POG RAM. The POG can handle up to 64 events. When a POG event begins, the POG event data and next address bytes are loaded into internal holding buffers and the POG even tim is loaded into the POG countdown timer. Once the timer counts to 0, the POG event occurs and POG next address points to the next PGO even block.

**ZDI.** A ZiLOG Debug Interface is included. ZDBI incorporates most of the functions of an In-Circuit Emulate on the IC. ZDBI allows the user (with an ICEBOX) to single step code, change registers, edit programs and view status of internal registers.

2K BYTES OF SRAM. There is 2K bytes of Static RAM. It resides at Address E000H-FFFFH. This RAM can be used for stack, read/write data storage, and POG events.

**1K** BOOT ROM. The Z80S183 contains 1K boot ROM.

REAL TIME CLOCK. The Z80S183 RTC provides a time and calendar function of seconds, minutes, hours, 12/24, AM/PM, day of week, day of month, month and year. It features a 24 hour alarm facility capable of generating an interrupt.

Power Fail Sensing. A power-fail trigger is implemented by detecting missed mains frequency cycles. This feature ensures the earliest possible warning of power failure. Once this event occurs, the systems generate an NMI interrupt if enabled, as well as a status bit in the System Status Register. This feature allows the application software to provide a graceful shutdown.

# **BLOCK DIAGRAMS**

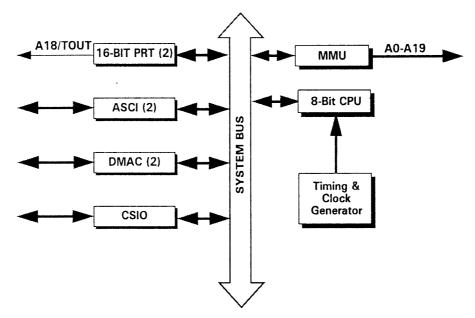

Z8S180 CORE PROCESSOR BLOCK DIAGRAM

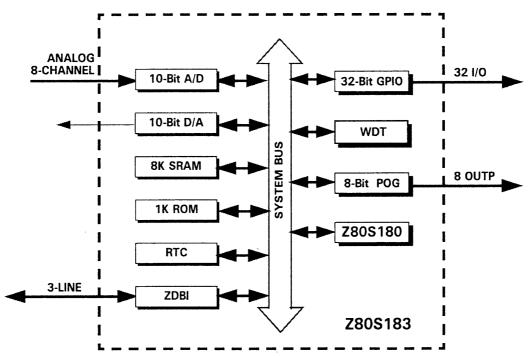

Z80S183 BLOCK DIAGRAM

# **APPLICATIONS AND SUPPORT TOOLS**

The following development tools are available for the programming and debug of this device:

- Orion emulators

- ZiLOG Development Suite (ZDS)

- Numerous 3rd party software support (Visit http://www.zilog.com/support/z80\_z185.html)

# RELATED PRODUCTS

Other Integrated Controllers of interest are:

| Z84C00  | Z80™ CPU (up to 20 MHz)                                                                                                                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Z84C15  | Z80™ + 2 SIO + 4x8 CTC + 2 PIO + WDT (up to 16 MHz)                                                                                                                          |

| Z80S180 | Improved Z80 + 1MByte MMU + 2 DMA +2-16bit PRT + 2 UARTs + CSIO (up to 33MHz)                                                                                                |

| Z80181  | Z8S180™ (see above) + SCC+CTC+ 16 GPIO (up to 33MHz)                                                                                                                         |

| Z80182  | Z8S180™ (see above) + 2 ESCC + 24 bit GPIO+ 16550 Mimic interface (up to 33MHz)                                                                                              |

| Z80189  | Z8S180™ (see above) + 24 GPIO + 16550 Mimic interface (up to 33MHz)                                                                                                          |

| Z80S188 | Z8S180™ (see above) + 2 SIO + 4x8 CTC + 2 PIO + WDT+ POR + 4K Boot ROM + 1K SRAM                                                                                             |

| Z80S190 | eZ80™ enhanced CPU (single cycle instruction fetch, 16Mbyte Linear Address) + Multiply and Accumulate, 2 UARTs, 6 C/T, CSIO, 2 DMA, 32 GPIO. (Up to 40MHz). Available Q1, 00 |

| Z84C00  | Z80™ CPU (up to 20 MHz)                                                                                                                                                      |

# **ELECTRICAL FEATURES SUMMARY**

- 50 μA maximum Supply Current

- 4.75V to 5.25V Operating Range

# ORDERING INFORMATION

| Part                   | PSI          | Description                        |

|------------------------|--------------|------------------------------------|

| Analog 180             | Z80S18333ASC | 100 VQFP, Standard temp            |

| Low voltage analog 180 | Z80L18320ASC | 100 VQFP, Standard temp, low power |

#### **Pre-Characterization Product**

The product represented by this Product Brief is newly introduced and ZiLOG has not completed the full characterization of the product. The Product Brief states what ZiLOG knows about this product at this time, but additional features or nonconformance with some aspects of the CPS may be found, either by ZiLOG or its customers in the course of further application and characterization work. In addition, ZiLOG cautions that delivery may be uncertain at times, due to start-up yield issues.

#### Low Margin

Customer is advised that this product does not meet ZiLOG's internal guardbanded test policies for the specification requested and is supplied on an exception basis. Customer is cautioned that delivery may be uncertain and that, in addition to all other limitations on ZiLOG liability stated on the front and back of the acknowledgment, ZiLOG makes no claim as to quality and reliability under the Product Brief. The product remains subject to standard warranty for replacement due to defects in materials and workmanship.

©1999 by ZiLOG, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of ZiLOG, Inc. The information in this document is subject to change without notice. Devices sold by ZiLOG, Inc. are covered by warranty and patent indemnification provisions appearing in ZiLOG, Inc. Terms and Conditions of Sale only.

ZiLOG, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose.

ZiLOG, Inc. shall not be responsible for any errors that may appear in this document. ZiLOG, Inc. makes no commitment to update or keep current the information contained in this document.

ZiLOG's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and ZiLOG prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

ZiLOG, Inc.

910 East Hamilton Avenue, Suite 110

Campbell, CA 95008

Telephone: (408) 558-8500

FAX: (408) 58-8300

Internet: http://www.ZiLOG.com