### RF251 Tx ASIC for CDMA, AMPS, and PCS Applications

#### **Product Description**

The RF251 Tx Application-Specific Integrated Circuit (ASIC) is a triple-mode, dual-band transmitter intended to be used in Code Division Multiple Access (CDMA) portable phones in both cellular and Personal Communications System (PCS) bands. As a dual mode IC it can be used in CDMA mode or Advanced Mobile Phone System (AMPS) mode.

The RF251 device includes the following functional blocks:

- In-Phase and Quadrature (I/Q) modulator.

- A VHF Voltage Controlled Oscillator (VCO).

- IF Variable Gain Amplifier (VGA).

- Cellular and PCS upconverters with RF gain control.

- Cellular and PCS Power Amplifier (PA) drivers.

The IF signals come off chip after the IF Automatic Gain Correction (AGC) for noise filtering. The RF signal comes off chip after the upconverter for noise filtering and image rejection.

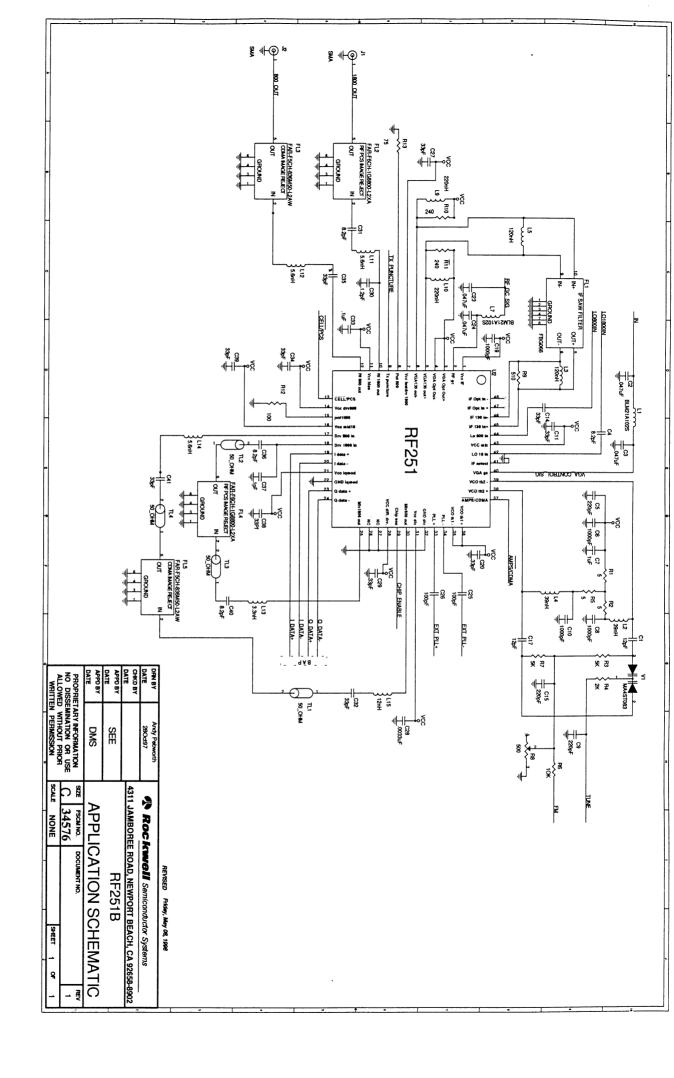

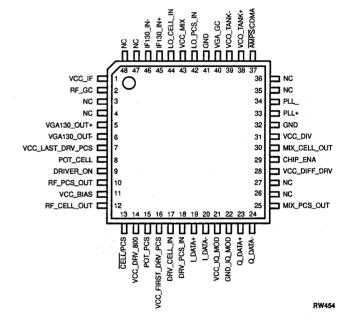

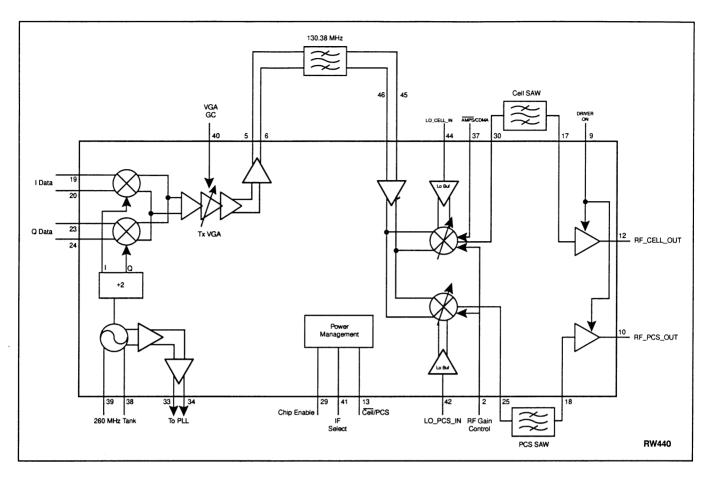

The device package and pinout are shown in Figure 1. A block diagram of the RF251 is shown in Figure 2.

#### **Features**

- Tri-mode operation with high linearity that meets the requirements of IS-95A, IS-98, and J-Std-008 standards.

- 90 dB dynamic range.

- Power saving operation in gated output power mode.

- 14 dB RF gain control to compensate for the gain variation of off-chip components.

- Lower power consumption in all modes.

- Enable line for the entire chip.

- Dual drivers for cellular and PCS bands.

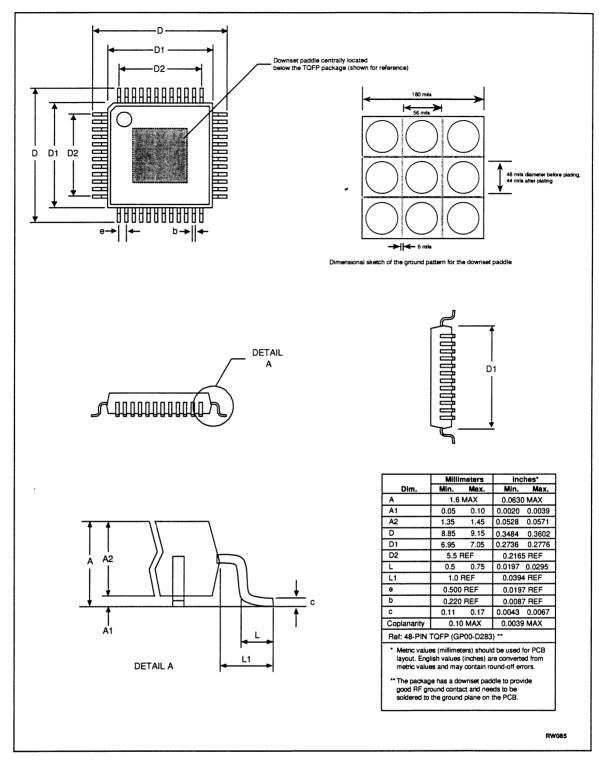

- 48-pin Thin Quad Flat Pack (TQFP) package with downset paddle.

### **Applications**

- · Cellular and PCS band phones.

- CDMA and AMPS modes in the cellular band:

- CDMA-US

- CDMA-J

- CDMA mode in the PCS band:

- US-PCS

- K-PCS

Figure 1. RF251 Tx ASIC Pinout – 48-Pin TQFP-package

Figure 2. RF251 Tx ASIC Block Diagram

#### **Technical Description**

The RF251 is a CDMA transmitter for the cellular and PCS bands. It also can be used as an FM transmitter in AMPS mode. A band select command chooses between the cellular band and the PCS band. A mode select command chooses between CDMA and AMPS mode in the cellular band. The chip consists of an I/Q modulator, a VHF VCO, an IF VGA, two variable gain upconverters for the cellular and PCS bands, and two PA drivers for both bands.

I/Q Modulator. The I/Q modulator converts the incoming analog baseband signals to balanced IF signals using the VHF local oscillator. These signals are fed directly to the VGA.

VHF VCOs. The Local Oscillator (LO) has a frequency range of 100 to 640 MHz. The oscillator has two pins to connect an external tank circuit. The tank circuit can be used to provide the FM modulation in the AMPS mode. It is also connected to a pin that provides an external Phase Locked Loop (PLL).

VGA. The VGA is a differential amplifier that receives its signal from the I/Q modulator, amplifies it, and sends it to the IF output pins (pins 5 and 6). A filter should be attached to the IF output pins for noise reduction. A dynamic range of 90 dB is available on the amplifier. A DC voltage of 0.2 to 2.7 V is needed to control the gain of the amplifier.

Upconverters. The cellular and PCS variable gain upconverters receive the IF signal from the VGA after passing through an external filter. Each upconverter uses an external LO controlled by an external PLL. The conversion gain control in the upconverter can be used to calibrate out any parto-to-part and temperature gain variation in the transmit path. The band select command switches between the cellular and PCS bands. The DRIVER\_ON command deactivates the driver during no transmission status. The output RF signal is sent to an output pin to be filtered before driver amplification.

**PA Drivers.** Two PA drivers are included, the cellular driver and the PCS driver.

Each driver takes its input from the upconverter after passing through an image rejection filter. The driver amplifies the signal and sends it to an external PA.

The DRIVER\_ON command is used during gated output power mode to deactivate the drivers in periods of no transmission. A Surface Acoustic Wave (SAW) filter for noise and image rejection should be placed between the driver and the external PA.

The signal pin assignments and functional pin descriptions are found in Table 1. The absolute maximum ratings of the RF251 are provided in Table 2, the recommended operating conditions are specified in Table 3, and electrical specifications are provided in Table 4. Figure 3 provides the package dimensions for the 48-pin TQFP RF251 Tx ASIC.

#### **ESD Sensitivity**

The RF251 is a Class 1 device. The following extreme Electrostatic Discharge (ESD) precautions are required according to the Human Body Model (HBM):

- Complete ESD training program required.

- Protective outer garments.

- Handle device in ESD safeguarded work area.

- Transport device in ESD shielded containers.

- Monitor and test all ESD protection equipment.

The HBM ESD withstand threshold value, with respect to ground, is  $\pm 1.5$  kV. The HBM ESD withstand threshold value, with respect to VDD (the positive power supply terminal) is also  $\pm 1.5$  kV.

Table 1. RF251 Signal Description (1 of 2)

| PIN | NAME              | DESCRIPTION                                                                                                                                                                                                                                                             |

|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCC_IF            | Supply voltage for the VGA, IF mux, and bias circuitry.                                                                                                                                                                                                                 |

| 2   | RF_GC             | The gain control pin for both RF upconverters. A DC voltage of 1 to 2.5 V is needed to cover the mixer RF range.                                                                                                                                                        |

| 3   | NC                | No connection.                                                                                                                                                                                                                                                          |

| 4   | NC                | No connection.                                                                                                                                                                                                                                                          |

| 5   | VGA130_OUT+       | The output pin for the 130.38 MHz VGA. This is a balanced output. It should be connected to an external bandpass filter for noise reduction. Requires an inductor choke to VCC IF.                                                                                      |

| 6   | VGA130_OUT-       | Same as pin 5, except complementary output.                                                                                                                                                                                                                             |

| 7   | VCC_LAST_DRV_PCS  | Supply voltage for the PCS driver amplifier. This pin can be used to turn the last driver on and off for a 24 dB gain step.                                                                                                                                             |

| 8   | POT_CELL          | This pin is connected to an external resistor. The value of the resistor varies the bias current of the cellular driver, which affects gain and Adjacent Channel Power Rejection (ACPR).                                                                                |

| 9   | DRIVER_ON         | This is the driver control signal. When the pin is low, the driver is deactivated during no transmission. During transmission the pin should be high to enable the driver. DRIVER_ON = On to DRIVER_ON = Off can be used to provide a 33 dB step in cellular CDMA mode. |

| 10  | RF_PCS_OUT        | This is the output pin for the PCS RF signal. The pin is connected to the output of the PCS driver amplifier. Impedance matching is required.                                                                                                                           |

| 11  | VCC_BIAS          | Supply voltage for the cellular driver bias.                                                                                                                                                                                                                            |

| 12  | RF_CELL_OUT       | This is the output pin for the cellular RF signal. The pin is connected to the output of the cellular driver amplifier. Impedance matching is required.                                                                                                                 |

| 13  | CELL/PCS          | This is a control signal input pin that selects between the cellular band and PCS band. When the input is low, the cellular band is chosen. When the input is high, the PCS band is chosen.                                                                             |

| 14  | VCC_DRV_800       | Supply voltage for the driver of the cellular band.                                                                                                                                                                                                                     |

| 15  | POT_PCS           | This pin is connected to an external resistor. The value of the resistor varies the bias current of the PCS driver, which affects gain and ACPR.                                                                                                                        |

| 16  | VCC_FIRST_DRV_PCS | Supply voltage for the first amplifier in the PCS driver block.                                                                                                                                                                                                         |

| 17  | DRV_CELL_IN       | The cellular driver input pin connected to the RF input of the cellular band driver. The input signal should pass through a SAW filter before being connected to the driver. Impedance matching is required.                                                            |

| 18  | DRV_PCS_IN        | The PCS driver input pin connected to the RF input of the PCS band driver. The input signal should pass through a SAW filter before being connected to the driver. Impedance matching is required.                                                                      |

| 19  | I_DATA+           | The I/Q modulator baseband balanced input for the I channel. A DC bias has to be supplied to the pin.                                                                                                                                                                   |

| 20  | I_DATA-           | Same as pin 19, except complementary input.                                                                                                                                                                                                                             |

| 21  | VCC_IQ_MOD        | Supply voltage for the I/Q modulator.                                                                                                                                                                                                                                   |

| 22  | GND_IQ_MOD        | Ground connection for I/Q modulator.                                                                                                                                                                                                                                    |

| 23  | Q_DATA+           | The I/Q modulator baseband balanced input for the Q channel. A DC bias has to be supplied to the pin.                                                                                                                                                                   |

| 24  | Q_DATA-           | Same as pin 23, except complementary input.                                                                                                                                                                                                                             |

5

Table 1. RF251 Signal Description (2 of 2)

| PIN | NAME         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                            |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25  | MIX_PCS_OUT  | This pin is connected to the RF output of the PCS upconverter. This pin needs impedance matching. The RF output signal should be routed through an image rejection filter before being connected to the driver input.                                                                                                                                                  |

| 26  | NC           | No connection.                                                                                                                                                                                                                                                                                                                                                         |

| 27  | NC           | No connection.                                                                                                                                                                                                                                                                                                                                                         |

| 28  | VCC_DIFF_DRV | Supply voltage for a differential amplifier in the upconverter block.                                                                                                                                                                                                                                                                                                  |

| 29  | CHIP_ENA     | This is the IQ modulator, VGA, and upconverter enable signal. When the input is low, the chip is disabled. When the input is high, the chip is enabled.                                                                                                                                                                                                                |

| 30  | MIX_CELL_OUT | This pin is connected to the RF output of the cellular upconverter. The RF output signal should be routed through an image rejection filter before being connected to the cell driver input.                                                                                                                                                                           |

| 31  | VCC_DIV      | Supply voltage for the divider and VCO buffer.                                                                                                                                                                                                                                                                                                                         |

| 32  | GND          | Ground pin for the divider and VCO buffer.                                                                                                                                                                                                                                                                                                                             |

| 33  | PLL+         | An output pin for the VCO. This is a balanced output. This output goes to an external PLL that locks the VCO frequency.                                                                                                                                                                                                                                                |

| 34  | PLL-         | Same as pin 33, except complementary input                                                                                                                                                                                                                                                                                                                             |

| 35  | NC           | No connection.                                                                                                                                                                                                                                                                                                                                                         |

| 36  | NC           | No connection.                                                                                                                                                                                                                                                                                                                                                         |

| 37  | AMPS/CDMA    | This is the cellular mode control signal input. When the input is low, the AMPS mode is selected. If the input is high, CDMA mode is selected.                                                                                                                                                                                                                         |

| 38  | VCO_TANK+    | The input pin for external VCO tank connection. This is a balanced input. The tank circuit values estimate the frequency of oscillation (and the Q factor) of the LO. This tank circuit should contain a varacter to directly frequency modulate the IF at the modulator output. The output frequency of the VCO is a divide-by 2 before applying to the I/Q modulator |

| 39  | VCO_TANK-    | Same as pin 38, except a complementary input.                                                                                                                                                                                                                                                                                                                          |

| 40  | VGA_GC       | The VGA gain control signal. A DC control voltage should be applied to this pin to vary the gain of the VGA.                                                                                                                                                                                                                                                           |

| 41  | GND          | Ground connection.                                                                                                                                                                                                                                                                                                                                                     |

| 42  | LO_PCS_IN    | This is the input pin for the local oscillator for the PCS band. It is internally matched.                                                                                                                                                                                                                                                                             |

| 43  | VCC_MIX      | Supply voltage for the mixer in the upconverter block and for the LO buffer.                                                                                                                                                                                                                                                                                           |

| 44  | LO_CELL_IN   | This is the input pin for the local oscillator for the cellular band. It is internally matched.                                                                                                                                                                                                                                                                        |

| 45  | IF130_IN+    | A band select command will switch the input IF signal, which is the balanced input to the upconverter, between the cellular upconverter and the PCS upconverter. The DC bias is set internally.                                                                                                                                                                        |

| 46  | IF130_IN-    | Same as pin 45, except a complementary input.                                                                                                                                                                                                                                                                                                                          |

| 47  | NC           | No connection.                                                                                                                                                                                                                                                                                                                                                         |

| 48  | NC           | No connection.                                                                                                                                                                                                                                                                                                                                                         |

**Table 2. Absolute Maximum Ratings**

| PARAMETER                     | MINIMUM | MAXIMUM | UNIT |

|-------------------------------|---------|---------|------|

| Supply voltage (VCC)          | -0.3    | 5.0     | V    |

| Input voltage range           | -0.3    | vcc     | V    |

| Power dissipation             |         | 600     | mW   |

| Ambient operating temperature | -30     | +80     | °C   |

| Storage temperature           | -40     | +125    | °C   |

**Table 3. Recommended Operating Conditions**

| Parameter                                                      | Min | Typical | Max | Units |

|----------------------------------------------------------------|-----|---------|-----|-------|

| Supply voltage                                                 | 2.7 | 3.3     | 3.6 | V     |

| Logic level high                                               | 1.9 |         |     | V     |

| Logic level low                                                |     |         | 0.6 | V     |

| Supply current in 800 MHz CDMA @ 8 dBm                         | 89  | 102     | 115 | mA    |

| Supply current in 800 MHz AMPS @ 11 dBm                        | 96  | 110     | 124 | mA    |

| Supply current in 800 MHz (DRIVER_ON = Off)                    | 57  | 68      | 79  | mA    |

| Supply current in 1900 MHz CDMA @ 9 dBm                        | 89  | 103     | 117 | mA    |

| Supply current in 1900 MHz CDMA (DRIVER_ON = Off)              | 56  | 68      | 80  | mA    |

| Supply current in sleep mode (CHIP_ENA = Off, DRIVER_ON = Off) |     |         | 10  | μА    |

# Table 4. RF251 Tx ASIC Electrical Specifications (1 of 3) TA = 25° C, VCC = 3.3 V, PLO = -10 dBm, input externally matched

| Parameter                                                       | Symbol          | Test Condition     | Min       | Typical   | Max       | Units    |

|-----------------------------------------------------------------|-----------------|--------------------|-----------|-----------|-----------|----------|

| VCO (e)                                                         | ternal tank)/Wi | deband Divide-By-2 |           |           |           |          |

| Frequency range for VCOs                                        |                 |                    | 100       |           | 640       | MHz      |

| 2nd harmonic (measured @ tank circuit)                          |                 |                    |           | -30       | -26       | dBc      |

| 3rd harmonic (measured @ tank circuit)                          |                 |                    |           | -20       |           | dBc      |

| Phase noise @100 kHz offset, Fc = 620 MHz, unloaded tank Q = 20 |                 | •                  |           | -109      |           | dBc/Hz   |

| Phase noise @100 kHz offset, Fc = 260 MHz, unloaded tank Q = 20 |                 |                    |           | -113      |           | dBc/Hz   |

| Input frequency range to /2 circuit                             |                 |                    | 100       |           | 640       | MHz      |

| Output impedance of buffer to PLL (differential)                |                 |                    |           | 300       |           | Ω        |

| Output signal level to PLL (differential)                       |                 |                    |           | 300       |           | mVp-p    |

|                                                                 | I/Q Modu        | ılator             |           |           |           |          |

| Input voltage level, differential                               |                 |                    |           | 1         |           | Vp-p     |

| Common mode input voltage level                                 |                 |                    | 1.6       | 1.85      | 2.1       | ٧        |

| Input DC offset                                                 |                 |                    |           |           | 4         | mV       |

| Input impedance                                                 |                 |                    | 100K      |           |           | Ω        |

| Gain variation over process, temperature, VCC                   |                 |                    |           | 0.4       |           | dB       |

| I/Q gain mismatch                                               |                 |                    |           | 0.3       | 0.4       | dB       |

| I/Q phase imbalance                                             |                 |                    |           | 2         | 4         | degree   |

|                                                                 | Tx VC           | A .                |           |           |           |          |

| VGA frequency range (-1 dB bandwidth)                           |                 |                    | 50        |           | 320       | MHz      |

| VGA gain (with 510 $\Omega$ load resistor): Maximum Minimum     |                 |                    | 25<br>-65 | 28<br>-62 | 30<br>-60 | dB<br>dB |

| VGA gain variation with VCC 3.0 to 3.6 V @ VCTRL 2 V            |                 |                    | -3        |           | 3         | dB       |

| Gain variation with temperature                                 |                 |                    | -1.5      |           | 1.5       | dB       |

| Gain control input impedance                                    |                 |                    |           | 40K       |           | Ω        |

| VGA gain slope                                                  |                 |                    | 40        | 45        | 50        | dB/V     |

| VGA gain control range                                          |                 |                    | 0.2       |           | 2.7       | V        |

| Gain slope variation over any 6 dB segment                      |                 |                    | -3        |           | +3        | dB/V     |

| Output power level @ 26dB gain                                  |                 |                    |           | -13       |           | dBm      |

| Minimum controllable output power (thermal noise:-113dBm)       |                 |                    |           | -107      |           |          |

| ACPR in 30 kHz band at 885 kHz offset, maximum gain             |                 |                    |           | -61       | -60       | dBc      |

| ACPR in 30 kHz band at 1.25 MHz offset, maximum gain            |                 |                    |           | -63       | -62       | dBc      |

## Table 4. RF251 Tx ASIC Electrical Specifications (2 of 3) TA = 25° C, VCC = 3.3 V, PLO = -10 dBm, input externally matched

| Parameter                                            | Symbol          | Test Condition  | Min  | Typical | Max  | Units |

|------------------------------------------------------|-----------------|-----------------|------|---------|------|-------|

|                                                      | Tx VGA (co      | intinued)       |      |         |      |       |

| ACPR in 30 kHz band at 1.98 MHz offset, maximum gain |                 |                 |      | -72     | -71  | dBc   |

| NF at maximum gain                                   |                 |                 |      | 5       | 6    | dB    |

| NF at -52 dB gain                                    |                 |                 |      | 52      | 53   | dB    |

| Cell                                                 | ular Variable G | aln Upconverter |      |         |      |       |

| LO frequency range                                   |                 |                 | 700  |         | 1000 | MHz   |

| LO input return loss (reference to 50 $\Omega$ )     |                 |                 |      | -10     |      | dB    |

| Terminating resistor across IF inputs                |                 |                 | 485  | 510     | 535  | Ω     |

| Output frequency                                     |                 |                 | 824  |         | 925  | MHz   |

| CDMA mode conversion gain, maximum                   |                 |                 | 20   | 22      |      | dB    |

| CDMA mode conversion gain, mininum                   |                 |                 |      | -10     |      | dB    |

| ACPR in 30 kHz at 885 kHz offset @ -2 dBm output     |                 |                 |      | -55     | -54  | dBc   |

| ACPR in 30 kHz at 1.98 MHz offset @ -2 dBm output    |                 |                 |      |         | -66  | dBc   |

| FM mode conversion gain, maximum                     |                 |                 | 22   | 25      |      | dB    |

| FM mode conversion gain, minimum                     |                 |                 |      | -6      |      | dB    |

| FM mode output P1dB                                  |                 |                 | +5   | +6      |      | dBm   |

| Noise figure @ 22 dB gain CDMA/22 dB gain FM         |                 |                 |      | 10      | 11   | dB    |

| Noise figure @ 12 dB gain CDMA/14 dB gain FM         |                 |                 |      | 16      | 18   | dB    |

| LO to RF leakage @ maximum gain, LO = -10 dBm        |                 |                 |      | -35     |      | dBm   |

| PC                                                   | CS Variable-Gal | n Upconverter   |      |         |      |       |

| LO frequency range                                   |                 |                 | 1600 |         | 1800 | MHz   |

| LO input return loss (reference to 50 $\Omega$ )     |                 |                 |      | -10     |      | dB    |

| Terminating resistor across IF inputs                |                 |                 | 485  | 510     | 535  | Ω     |

| Output frequency                                     |                 |                 | 1700 |         | 1910 | MHz   |

| Maximum conversion gain                              |                 |                 | 17   | 18      |      | dB    |

| Minimum conversion gain                              |                 |                 |      | -6      |      | dB    |

| Output power @ maximum gain                          |                 |                 |      | -3      |      | dBm   |

| ACPR in 30 kHz at 1.25 MHz offset @ -6 dBm output    |                 |                 |      | -56     | -54  | dBc   |

| ACPR in 1 MHz at 2.75 MHz offset @ -6 dBm output     |                 |                 |      | -56     | -54  | dBc   |

| Noise figure at 13 dB gain                           |                 |                 |      | 9       | 10   | dB    |

| Noise figure at minimum gain                         |                 |                 |      | 13      |      | dB    |

| LO to RF leakage @ maximum gain, LO = -15 dBm        |                 |                 |      | -35     |      | dBm   |

## Table 4. RF251 Tx ASIC Electrical Specifications (3 of 3) TA = 25° C, VCC = 3.3 V, PLO = -10 dBm, input externally matched

| Parameter                                             | Symbol     | Test Condition | Min  | Typical | Max  | Units |

|-------------------------------------------------------|------------|----------------|------|---------|------|-------|

|                                                       | Cellular P | A Driver       |      | -       |      |       |

| Output frequency                                      |            |                | 824  |         | 925  | MHz   |

| Gain (@ POT800 = 100 Ω)                               |            |                | 12.5 | 13.5    |      | dB    |

| Output power level                                    |            |                | 8    | 10      |      | dBm   |

| Saturated output power level (FM)                     |            |                | 12   | 14      |      | dBm   |

| ACPR in 30 kHz band at 885 kHz offset @ 8 dBm output  |            | •              |      | -54     | -53  | dBc   |

| ACPR in 30 kHz band at 1.98 MHz offset @ 8 dBm output |            |                |      | -67     | -66  | dBc   |

| Output return loss (reference to 50 $\Omega$ )        |            |                |      | -15     |      | dB    |

| Noise figure                                          |            |                |      | 6       | 8    | dB    |

|                                                       | PCS PA     | Driver         |      |         |      |       |

| Input return loss (reference to 50 $\Omega$ )         |            |                |      | -15     |      | dB    |

| Output frequency                                      |            |                | 1700 |         | 1910 | MHz   |

| Gain (@ POT1800 = 100 Ω)                              |            |                | 18   | 20      |      | dB    |

| Output power level with 1800 MHz mixer @ maximum gain |            |                | +9   | +10.5   |      | dBm   |

| ACPR in 30 kHz band at 1.25 MHz offset @ 9 dBm output |            |                |      | -52     | -51  | dBc   |

| ACPR in 1 MHz band at 2.75 MHz offset @ 9 dBm output  |            |                |      | -52     | -51  | dBc   |

| Noise figure                                          |            |                |      | 9       | 10   | dB    |

Figure 3. RF251 Tx ASIC Package Dimensions - 48-pin TQFP Package With Downset Paddle

Information provided by Rockwell International Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Rockwell International for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Rockwell International other than for circuitry embodied in Rockwell products. Rockwell International reserves the right to change circuitry at any time without notice. This document is subject to change without notice.

**Headquarters**Rockwell Semiconductor Systems 4311 Jamboree Road,

Newport Beach, CA 92658-8902 Phone: (714) 221-4600 Fax: (714 221-6375

European Headquarters Rockwell Semiconductor Systems

Les Taissounieres B1 Route des Dolines Sophia Antipolis Cedex 06905 Valbonne

France Phone: (33) 93 00 33 35 Fax: (33) 93 00 33 03

For more information: Call 1-800-854-8099 International information: Call 1-714-833-6996

URL Address: http://www.nb.rockwell.com E-Mail Address: literature@nb.rockwell.com

**REGIONAL SALES OFFICES**

US Southwest Office Rockwell Semiconductor Systems 5000 Birch Street

Newport Beach, CA 92660 Phone: (714) 222-9119 Fax: (714) 222-0620

US Southwest Satellite Office Rockwell Semiconductor Systems 1000 Business Center Circle

Suite 215

Thousand Oaks, CA 91320

Phone: (805) 376-0559

Fax: (805) 376-8180

US South Central Office Rockwell Semiconductor Systems 2001 North Collins Blvd

Suite 103 Richardson, TX 75080 Phone: (972) 479-9310 Fax: (972) 479-9317

**US Southeast Office**

Rockwell Semiconductor Systems 3500 Parkway Lane Suite 415 Norcross, GA 30092 Phone: (770) 246-8283 Fax: (770) 246-0018

**US Southeast Satellite Office Rockwell Semiconductor Systems** One Prestige Place 2600 McCormick Drive Suite 350 Clearwater, FL 34619 Phone: (813) 799-8406 Fax: (813) 799-8306

**US Northwest Office**

Rockwell Semiconductor Systems US Northwest Office 3600 Pruneridge Avenue Suite 100 Santa Clara, CA 95051 Phone: (408) 249-9696 Fax: (408) 249-7113

US North Central Office Rockwell Semiconductor Systems

Chancellory Park Suite 810 Itasca, IL 60143 Phone: (708) 773-3454 Fax: (708) 773-3907

Two Pierce Place

US Northeast Office Rockwell Semiconductor Systems 239 Littleton Road Suite 4A Westford, MA 01886 Phone: (508) 692-7660 Fax: (508) 692-8185

Australia

Australia

Rockwell Australia Pty Limited

Rockwell Semiconductor Systems

Suite 603, 51 Rawson Street

Epping, NSW 2121

Australia

(C.1.0) 0000, 4000

(61-2) 9869 4088 (61-2) 9869 4077 Phone: Fax:

Europe Mediterranean Rockwell Semiconductor Systems c/o Rockwell Automation s.r.l.

Via Di Vittorio, 1 20017 Mazzo Di Rho (MI)

Phone: (39 2) 9317 9911 Fax (39 2) 9317 9913

**Europe North**

Rockwell Semiconductor Systems, Ltd. Berkshire Court Western Road Bracknell Berkshire RG12 1RE England

Phone: +44 1344 486 444 Fax: +44 1344 486 555

**Europe South**

Rockwell Semiconductor Systems S.A.R.L. Tour GAN Cedex 13 92082 Paris La Defense 2

France Phone: (33-1) 49-06-3980 Fax: (33-1) 49-06-3990

Germany

Rockwell Semiconductor Systems Rockwell Int'l GmbH Germany Paul-Gerhardt-Allee 50 a 81245 Munchen

Germany Phone: (49-89) 829-1320 Fax: (49-89) 834-2734

Hong Kong Rockwell Int'l (Asia Pacific) Ltd. 13th Floor, Suites 8-10, Harbour Centre 25 Harbour Road Wanchai, Hong Kong

(852) 2 827-0181 Phone: Fax. (852) 2 827-6488 Japan

Rockwell Int'l Japan Co., Ltd. Shimomoto Bldg 1-46-3 Hatsudai, Shibuya-ku Tokvo, 151

Токуо, то. Japan Phone: (81-3) 5371 1520 Fax: (81-3) 5371 1501

Korea

Rockwell-Collins Int'l, Inc. Room No. 1508 Korea Textile Centre Building 944-31, Daechi-3dong Kangnam P.O. Box 2037 Kangnam-ku

Korea

Phone: (82-2) 565-2880 Fax: (82-2) 565-1440

Singapore Rockwell Semiconductor Systems 1 Kim Seng Promenade #09-01 East Tower Great World City Singapore 237994 Phone: (65) 737-7355 Fax: (65) 737-9077

Taiwan Rockwell Int'l Taiwan Company, Ltd. Room 2808 International Trade Bldg. 333, Keelung Road, Section I Taipei, Taiwan

10548 ROC Phone: (886-2) 720-0282 Fax: (886-2) 757-6760

©1998, Rockwell International Corporation Printed in U.S.A. All Rights Reserved