SONET STS-12 LINE INTERFACE MODULE

### **FEATURES**

- Integrates a SONET STS-12 compatible, duplex line interface circuit in a single compact module.

- Provides high speed clock recovery, serial-to-parallel conversion, processing of section level and line level overhead, byte interleaved demultiplexing, byte interleaved multiplexing, insertion of line level and section level overhead, high speed clock generation, and parallel-to-serial conversion.

- Supports an OC-12 compatible line interface when combined with a duplex electrical to optical converter device.

- Compact module that utilizes HDIC technology to integrate CMOS, ECL, GaAs. and discrete components in a single device.

- When used in conjunction with TSPP, will support both STS-12 and STS-12C (and STS3/3C) payload formats.

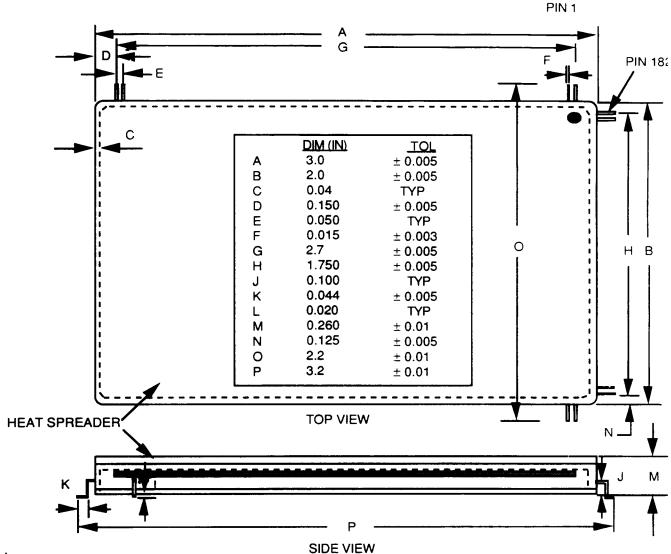

- 182-pin metalized flatpack package.

- 12 Watts typical power dissipation.

### The receiver section

- Provides high speed clock recovery, frame synchronization, and serial-to-parallel conversion in the receiver.

- Descrambles received data and performs section and line level alarm and performance monitoring including loss of signal detection, loss of frame detection, alarm indication signal (AIS) detection, and accumulation of BIP-8 errors and far end block errors.

- Extracts and serializes section and line level order wire channels.

- Extracts and serializes user channel and automatic protection switching channel.

- Extracts and serializes section and line level data communication channels and allows optional termination of the section data communication channel using an on-board HDLC receiver.

- Performs byte interleaved demultiplexing to provide four byte-wide STS-3 data streams from a single STS-12 data stream.

SONET STS-12 LINE INTERFACE MODULE

# The transmitter section

- Provides frame insertion, high speed clock generation, and parallel-to-serial conversion in the transmitter.

- Scrambles transmitted data after insertion of section and line level overhead including BIP-8 codes and alarm and status signals such as far end block error far end receive failure, and alarm indication signal (AIS).

- Serially accepts and inserts user channel and automatic protection switching channel.

- Serially accepts and inserts section and line level data communication channels and allows optional sourcing of the section data communication channel using an on-board HDLC transmitter.

- Performs byte interleaved multiplexing to provide a single STS-12 data stream from four byte-wide STS-3 data streams.

- Testmode loopback to receiver section.

# **REFERENCES**

- American National Standard for Telecommunications Digital Hierarchy Optical Interface Rates and Formats Specification, ANSI T1.105-1988.

- Bell Communications Research SONET Transport Systems: Common Generic Criteria, TR-TSY-000253, Issue 1, September, 1989.

### DESCRIPTION

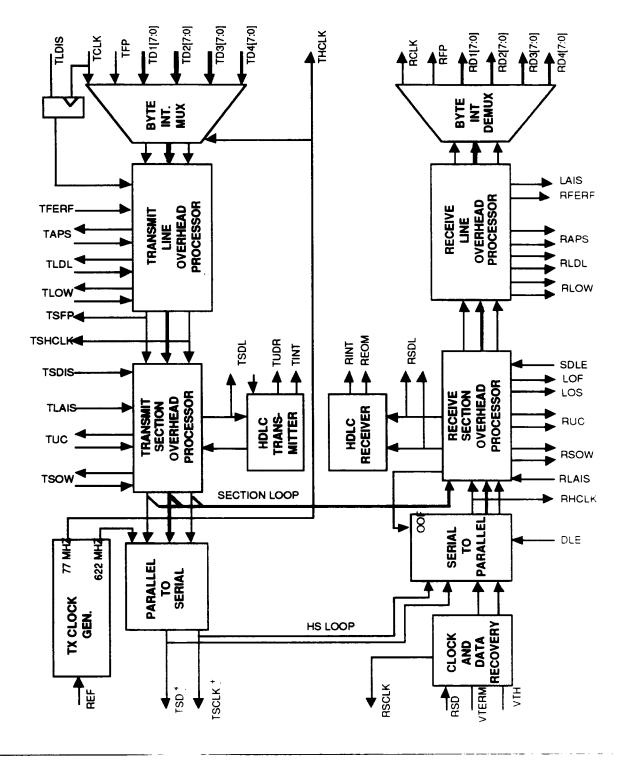

The PM5712 SONET STS-12 Line Interface Module (SLIM-12) is an integrated subsystem that supports STS-12 compatible line level transmit and receive interfaces for a 622.08 Mbit/s duplex data stream on the network side and a byte parallel interface for the four constituent STS-3s on the equipment side. The module processes the bytes contained in the section and line overhead. The SLIM-12 is configured, controlled, and monitored using registers that are accessed via a generic microprocessor interface.

At the receive serial input, the module accepts a a single ended STS-12 signal from a number of industry standard optical interfaces, and utilizes a phase locked loop (PLL) to extract clock and data. Once frame synchronization is obtained on the incoming 622 MHz data stream, a serial to parallel conversion is performed prior to processing of section and line overhead bytes.

# PM5712 SLIM-12

#### ADVANCE INFORMATION

SONET STS-12 LINE INTERFACE MODULE

The section overhead processor confirms the frame synchronization of the serial-to-parallel converter and determines loss of frame and loss of signal states. Once frame synchronization are validated, the section orderwire, user channel, and data link from the section overhead data stream are extracted. These signals and their associated clocks are available at output pins of the SLIM-12 module. An on chip HDLC receiver monitors the receive data link outputs, and makes the data link payload available to a central CPU via a common CPU bus.

The receive line overhead processor extracts the receive line data link, the receive line order wire, and the receive line automatic protection switching signals. It also detects the line AIS and Far End Receive Failure signals. These signals and their associated clocks are available at output pins of the SLIM-12 module.

The final function in the receive direction is the demultiplexing of the STS-12 bytes into four streams of STS-3 bytes with data rates of 19.44 Mbytes/s and a frame pulse which indicates the first byte of the synchronous payload envelope.

To extract the constituent STS-1 payload data from each STS-3, an external payload processor, such as the PM5323 Triple STS-1 Payload Processor (TSPP) must be used.

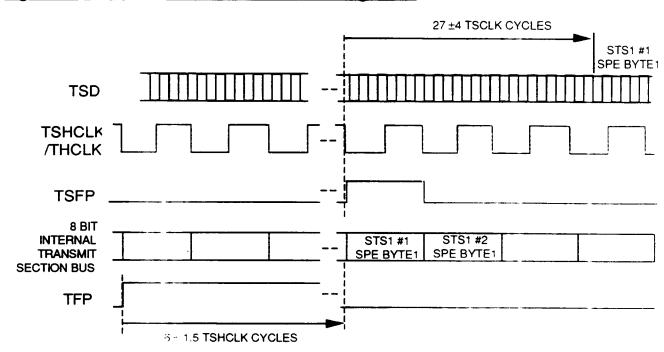

At the transmit parallel input, the module accepts four byte-wide STS-3 streams with a rate of 19.44 Mbyte/s each, which it multiplexes into one byte-wide STS-12 stream, with a data rate of 77.76 Mbyte/s. A frame pulse is required to mark the first byte of the STS-12 payload envelope. This data and frame pulse could be provided by an external payload processor device such as the TSPP.

The byte wide STS-12 stream is fed into the transmit line overhead processor, which adds the transmit line data link, line order wire, far end receive failure indication, and automatic protection switching channel to the line overhead bit stream. Existing bytes which are allocated for the line overhead bit stream are overwritten with the new line overhead data, so that the output data rate is the same as its input rate. Overwriting of the line overhead stream can be disabled in four byte wide blocks, if desired. Data inputs and clock outputs for the order wire, automatic protection switching channel, and data link are accessible at pins of the SLIM-12 module.

SONET STS-12 LINE INTERFACE MODULE

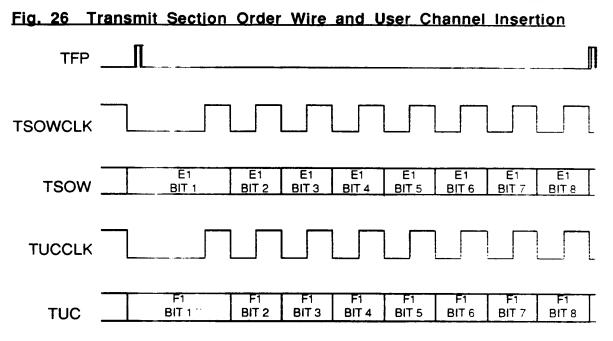

The transmit section overhead processor adds the transmit section order wire, section user channel, and section data link. The line alarm indication signal (AIS) can also be inserted if desired. As with the line overhead, the section overhead data overwrites allocated bytes so that the output data rate is the same as the input rate. This overwriting can be disabled on a byte by byte basis if desired. Data inputs and clock outputs for the section order wire, data link, and user channel are accessible at pins of the SLIM-12 module. The input to the section data link can be switched from the external pins to an on chip HDLC transmitter, so that data destined for the data link can be written to the HDLC transmitter via the CPU interface.

The final function in the transmit direction is parallel-to-serial conversion. Data with a rate of 77.76 Mbyte/s is shifted out of the parallel-to-serial converter at 622.08 Mbit/s. The module contains a second PLL on the transmit side to synchronize outgoing data with a reference clock. The 622.08 MHz clock which drives the transmit functions is synchronized to a 19.44 MHz square wave at the REF input pin. The STS-12 serial data and associated 622.08 MHz clock exit the SLIM-12 module via differential ECL outputs designed to drive 50  $\Omega$  loads.

The SLIM-12 transmit output operates in conjunction with an external electrical to optical converter. For long haul applications, the optical transmitter would normally be a laser designed for single mode operation, which would convert the high/low ECL levels to on/off light pulses.

# Suggested Optical Transmitters:

| Company | Model Number  | Max. Speed |

|---------|---------------|------------|

| AT&T    | ASTROTEC 1218 | 1000 MB    |

| Ortel   | 3510A         | 3000 MB    |

| Ortel   | 3510B         | 6000 MB    |

| BT&D    | XMT 1300-1.2  | 1200 MB    |

# PM5712 SLIM-12

ADVANCE INFORMATION

SONET STS-12 LINE INTERFACE MODULE

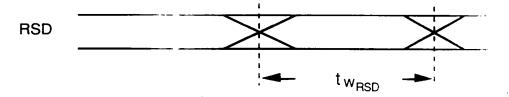

The optical receiver module would be either a PIN diode, or an avalanche diode (depending on the application) with a low noise transconductance amplifier. The output of the amplifier would have an amplitude of between 0.6 and 2.0 Vpp, centred at -1.3V, and be designed to drive a  $50\Omega$  load. AGC would normally be required to keep the output within the operating range over the desired sensitivity range of the receiver. The Data Slicing Comparator in the SLIM-12 module has no hysteresis, so if hysteresis is desired to reduce noise, then data slicing comparators should be placed before the Receive Serial Data (RSD) input.

# Suggested Optical Receivers:

| Company | Model Number | Max. Speed    |

|---------|--------------|---------------|

| AT&T    | ASTROTEC     | 1306A 1700 MB |

| Ortel   | 3510A        | 3000 MB       |

| Ortel   | 3510B        | 6000 MB       |

| BT&D    | RCV1201-1.   | 2 1200 MB     |

Both the transmit and receive circuitry have a high speed to low speed clock derivation structure. The clock outputs from the receive.side are derived from the recovered 622.08 MHz serial data clock, which is synchronized to the received STS-12 serial data. The clock outputs from the transmit side are derived from the 622 MHz transmit clock, which is synchronized to a 19.44 MHz reference. The STS-3 transmit clock inputs must be synchronous and should be stable in phase to the transmit clock outputs.

SONET STS-12 LINE INTERFACE MODULE

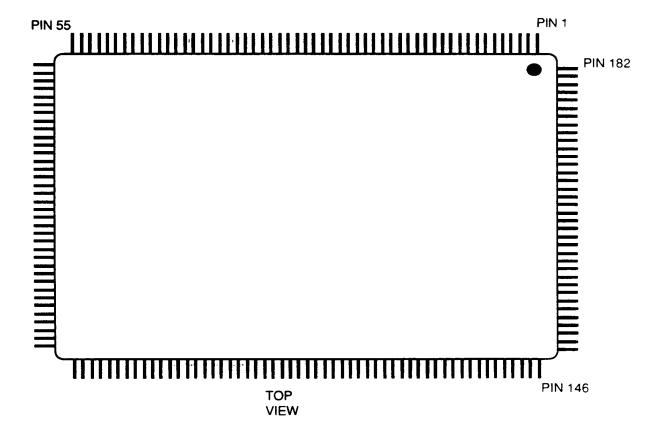

# PIN DIAGRAM

The SLIM-12 is implemented with PMC's proprietary HDIC technology and is packaged in an 182 pin metalized kovar flatpack package, denoted by part number PM5712AU, shown below. Gull Wing lead forms and cavity down are standard. Pin 1 is indicated by a dot on the top of the package. Pin numbering is counterclockwise when the package is viewed from the top with the dot indicator visible.

SONET STS-12 LINE INTERFACE MODULE

# **BLOCK DIAGRAM**

SONET STS-12 LINE INTERFACE MODULE

# PIN DESCRIPTION

| Connector<br>Name                                                            | Туре          | Pin<br>No.<br>Top<br>Sink                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------|---------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

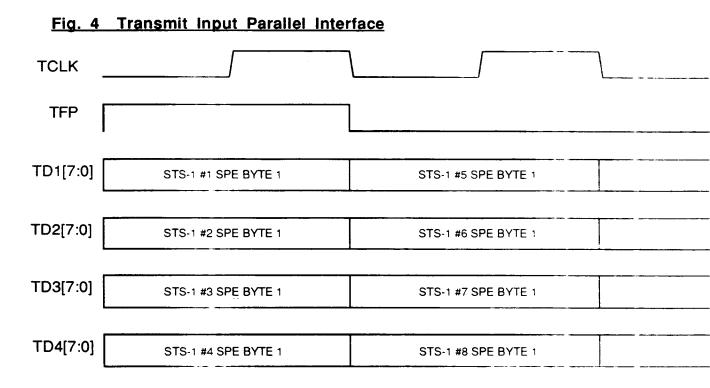

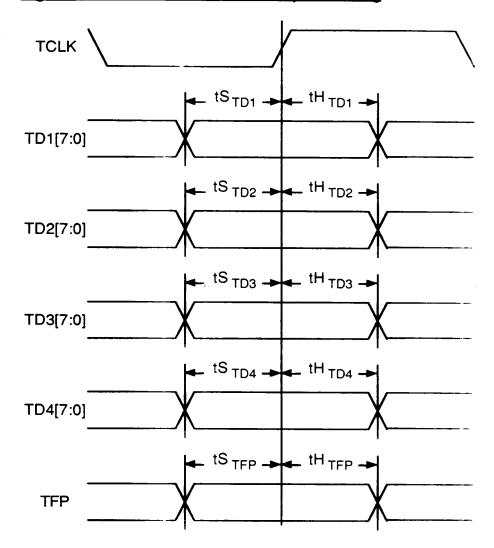

| TD4[0]<br>TD4[1]<br>TD4[2]<br>TD4[3]<br>TD4[4]<br>TD4[5]<br>TD4[6]<br>TD4[7] | CMOS<br>Input | 171<br>170<br>169<br>167<br>166<br>164<br>163<br>162 | The transmit PCM data (TD4[7:0]) bus carries PCM data in byte serial format. TD4[7:0] carries the transmit PCM data of STS-1 #4, STS-1 #8, and STS-1 #12. TD4[7:0] is sampled on the rising edge of TCLK. TD4[7] is the most significant bit (corresponding to bit 1, the first bit transmitted of each serial PCM word). TD4[0] is the least significant bit (corresponding to bit 8, the last bit transmitted of each PCM word). |

| TD3[0]<br>TD3[1]<br>TD3[2]<br>TD3[3]<br>TD3[4]<br>TD3[5]<br>TD3[6]<br>TD3[7] | CMOS<br>Input | 182<br>181<br>180<br>179<br>177<br>176<br>174<br>173 | The transmit PCM data (TD3[7:0]) bus carries PCM data in byte serial format. TD3[7:0] carries the transmit PCM data of STS-1 #3, STS-1 #7, and STS-1 #11. TD3[7:0] is sampled on the rising edge of TCLK. TD3[7] is the most significant bit (corresponding to bit 1, the first bit transmitted of each serial PCM word). TD3[0] is the least significant bit (corresponding to bit 8, the last bit transmitted of each PCM word). |

| TD2[0]<br>TD2[1]<br>TD2[2]<br>TD2[3]<br>TD2[4]<br>TD2[5]<br>TD2[6]<br>TD2[7] | CMOS<br>Input | 10<br>9<br>7<br>6<br>5<br>4<br>3<br>2                | The transmit PCM data (TD2[7:0]) bus carries PCM data in byte serial format. TD2[7:0] carries the transmit PCM data of STS-1 #2, STS-1 #6, and STS-1 #10. TD2[7:0] is sampled on the rising edge of TCLK. TD2[7] is the most significant bit (corresponding to bit 1, the first bit transmitted of each serial PCM word). TD2[0] is the least significant bit (corresponding to bit 8, the last bit transmitted of each PCM word). |

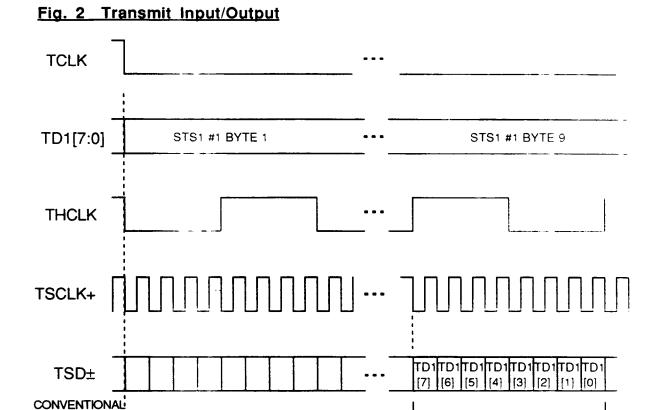

| TD1[0]<br>TD1[1]<br>TD1[2]<br>TD1[3]<br>TD1[4]<br>TD1[5]<br>TD1[6]<br>TD1[7] | CMOS<br>Input | 21<br>20<br>18<br>17<br>15<br>14<br>12               | The transmit PCM data (TD1[7:0]) bus carries PCM data in byte serial format. TD1[7:0] carries the transmit PCM data of STS-1 #1, STS-1 #5, and STS-1 #9. TD1[7:0] is sampled on the rising edge of TCLK. TD1[7] is the most significant bit (corresponding to bit 1, the first bit transmitted of each serial PCM word). TD1[0] is the least significant bit (corresponding to bit 8, the last bit transmitted of each PCM word).  |

|                  | 1              |          |                                                                                                                                                                                                                                                                                                                     |

|------------------|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

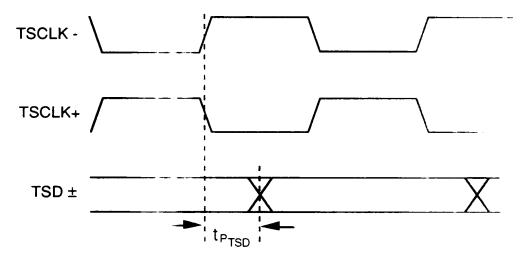

| TSCLK+<br>TSCLK- | ECL<br>Output  | 24<br>23 | The transmit serial clock (TSCLK) balanced signals carry the clock signal generated for the TSD data stream by the SLIM-12 module. TSCLK is nominally a 622.08 MHz, 50% duty cycle clock.                                                                                                                           |

| TSD+<br>TSD-     | ECL<br>Output  | 27<br>26 | The transmit serial data (TSD) balanced signals carry the 622.08 Mbit/s scrambled NRZ serial STS-12 data stream.                                                                                                                                                                                                    |

| REF              | TTL<br>Input   | 29       | Frequency reference input for the transmit clock generator. 19.44 MHz ±20 ppm, 50 ± 10% duty cycle.                                                                                                                                                                                                                 |

| TFP              | CMOS<br>Input  | 30       | The transmit frame pulse (TFP) signal marks the transport frame alignment on the TD1, TD2, TD3, and TD4 byte serial busses. TFP is high to mark the first byte of the synchronous payload envelope of the first constituent STS-1 stream output on each of these busses. TFP is sampled on the rising edge of TCLK. |

| TCLK             | CMOS<br>Input  | 32       | The transmit clock (TCLK) signal provides timing for processing the TD1, TD2, TD3, and TD4 byte serial busses. These busses are sampled on the rising edge of TCLK. TCLK is nominally a 19.44 MHz, 50% duty cycle clock.                                                                                            |

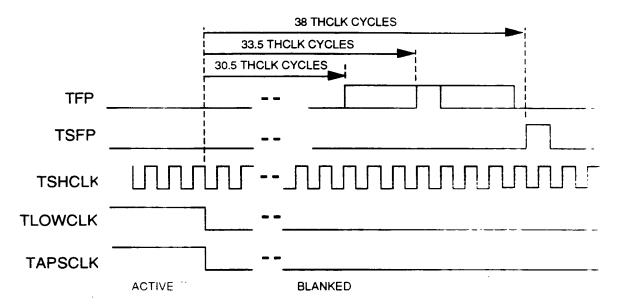

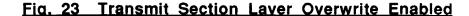

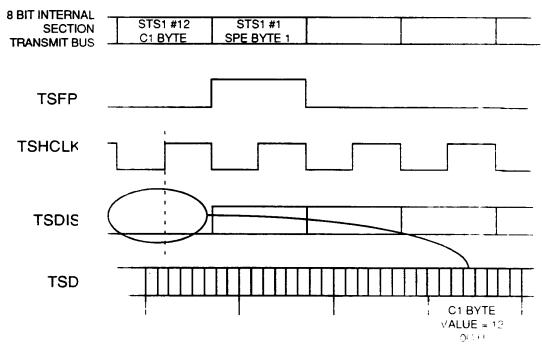

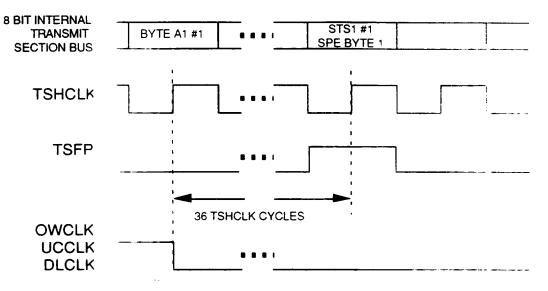

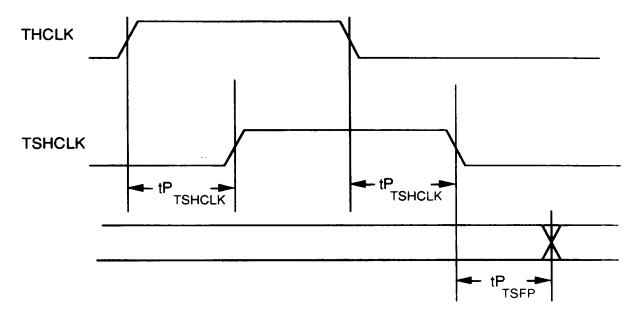

| TSHCLK           | CMOS<br>Output | 33       | The Transmit Section High Speed Clock (THSCLK) signal is a delayed version of THCLK, and provides timing for the transmit section overhead processor. TSDIS and TLAIS are sampled on the rising edge of TSHCLK.                                                                                                     |

| TSFP             | CMOS<br>Output | 34       | The active high Transmit Section Frame Pulse (TSFP) is a delayed version of the Transmit Line Frame Pulse output, TFP. It is used to synchronise the Transmit Section Disable input, TSDIS. TSFP is high for one TSHCLK period each frame.                                                                          |

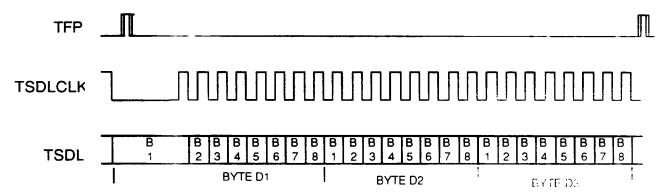

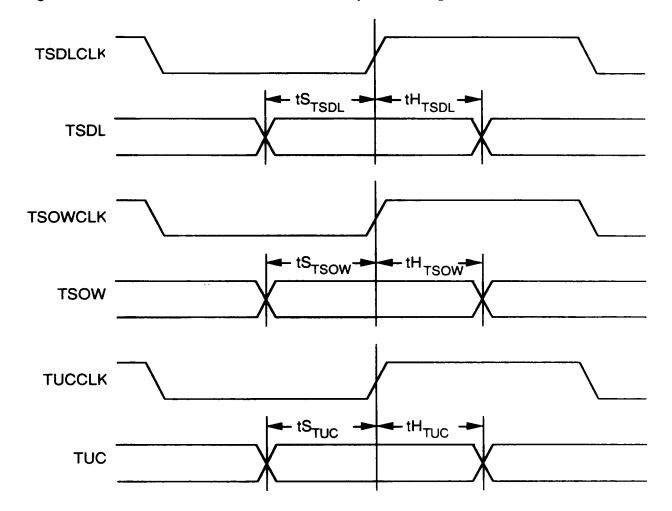

| TSDLCLK          | CMOS<br>Output | 35       | The transmit section data link clock (TSDLCLK) signal is a 192 kHz clock for use by upstream circuitry that processes the section data communication channel. TSDLCLK is a gapped 216 kHz clock.                                                                                                                    |

| TSDL    | CMOS<br>Input  | 36 | The transmit section data link (TSDL) signal carries the 192 kbit/s section data communication channel inserted into the STS-1 #1, D1-D3 section overhead bytes of the the STS-12 stream. TSDL is sampled on the rising edge of TSDLCLK.                                   |

|---------|----------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSOWCLK | CMOS<br>Output | 38 | The transmit section order wire clock (TSOWCLK) signal is a 64 kHz clock for use by upstream circuitry that processes the section order wire channel. TSOWCLK is a gapped 72 kHz clock.                                                                                    |

| TSOW    | CMOS<br>Input  | 39 | The transmit section order wire (TSOW) signal carries the 64 kbit/s section order wire channel inserted into the STS-1 #1 section overhead E1 byte of the STS-12 stream. TSOW is sampled on the rising edge of TSOWCLK. The byte boundaries on TSOW are identified by TFP. |

| TUCCLK  | CMOS<br>Output | 40 | The transmit section user channel clock (TUCCLK) signal is a 64 kHz clock for use by upstream circuitry that processes the section user channel. TUCCLK is a gapped 72 kHz clock.                                                                                          |

| TUC     | CMOS<br>Input  | 41 | The transmit user channel (TUC) signal carries the 64 kbit/s section user channel inserted into the STS-1 #1 section overhead F1 byte of the STS-12 stream. TUC is sampled on the rising edge of TUCCLK. The byte boundaries on TUC are identified by TFP.                 |

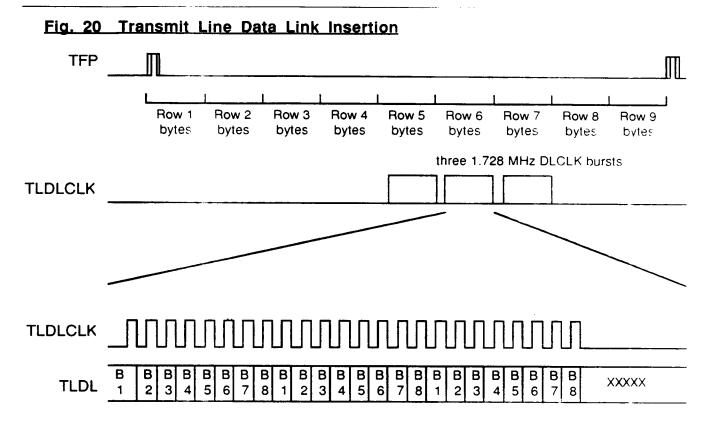

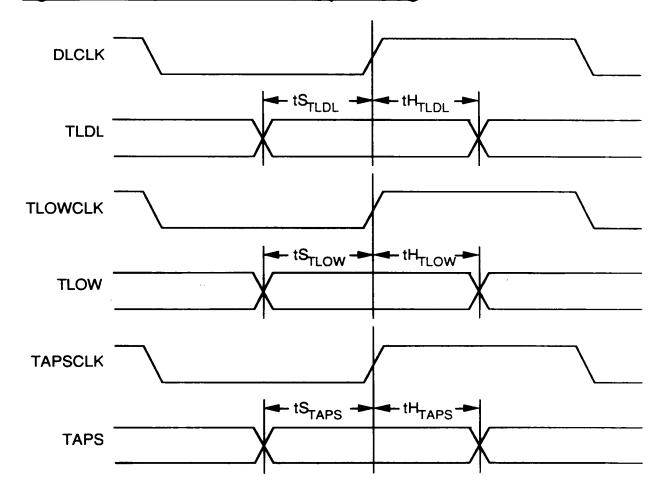

| TLDLCLK | CMOS<br>Output | 42 | The transmit line data link clock (TLDLCLK) signal is a 576 kHz clock for use by upstream circuitry that processes the line data communication channel. TLDLCLK is a gapped 2.16 MHz 67%(high)/33%(low) duty cycle clock.                                                  |

| TLDL    | CMOS<br>Input  | 44 | The transmit line data link (TLDL) signal carries the 576 kbit/s line data communication channel inserted into the STS-1 #1, D4-D12 line overhead bytes of the the STS-12 stream. TLDL is sampled on the rising edge of TLDLCLK.                                           |

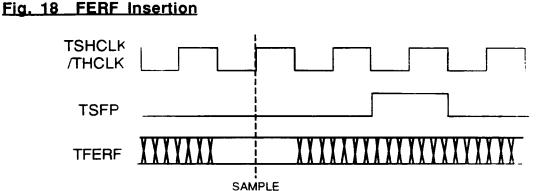

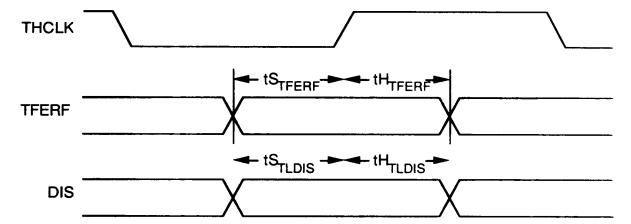

| TFERF   | CMOS<br>Input  | 45 | The active high Transmit Far End Receive Failure (TFERF) signal controls the insertion of the line Far End Receive Failure indication into the STS-12 overhead data. FERF is sampled on the rising edge of THCLK.                                                          |

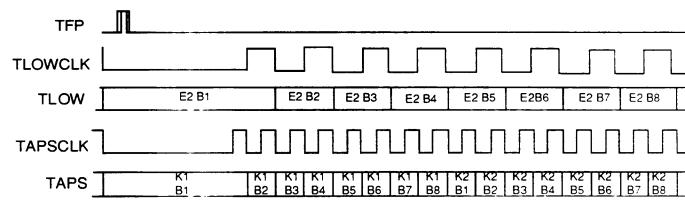

| TLOWCLK | CMOS<br>Output | 46 | The transmit line order wire clock (TLOWCLK) signal is a 64 kHz clock for use by upstream circuitry that processes the line order wire channel. TLOWCLK is a gapped 72 kHz clock.                                                                                                                       |

|---------|----------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TLOW    | CMOS<br>Input  | 47 | The transmit line order wire (TLOW) signal carries the 64 kbit/s line order wire channel into the STS-1 line overhead E2 byte of the STS-12 stream. TLOW is sampled on the rising edge of TLOWCLK. The byte boundaries on TLOW are identified by TFP.                                                   |

| TAPSCLK | CMOS<br>Output | 48 | The transmit automatic protection switch clock (TAPSCLK) signal is a 128 kHz clock for use by upstream circuitry that processes the line automatic protection switch channel. TAPSCLK is a gapped 144 kHz clock.                                                                                        |

| TAPS    | CMOS<br>Input  | 50 | The transmit automatic protection switch (TAPS) signal carries the 128 kbit/s line automatic protection switch channel inserted into the STS-1 #1 line overhead K1 and K2 bytes of the STS-12 stream. TAPS is sampled on the rising edge of TAPSCLK. The byte boundaries on TAPS are identified by TFP. |

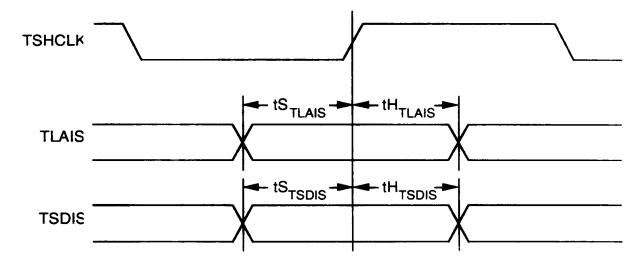

| TLAIS   | CMOS<br>Input  | 51 | The active high transmit line alarm indication (TLAIS) signal controls the insertion of line AIS in the transmitted STS-12 stream. TLAIS is sampled on the rising edge of TSHCLK.                                                                                                                       |

| TSDIS   | CMOS<br>Input  | 52 | The active high transmit section disable (TSDIS) signal selectively, on a byte by byte basis, disables overwriting the outgoing STS-12 stream with section overhead bytes. TSDIS is sampled on the rising edge of TSHCLK.                                                                               |

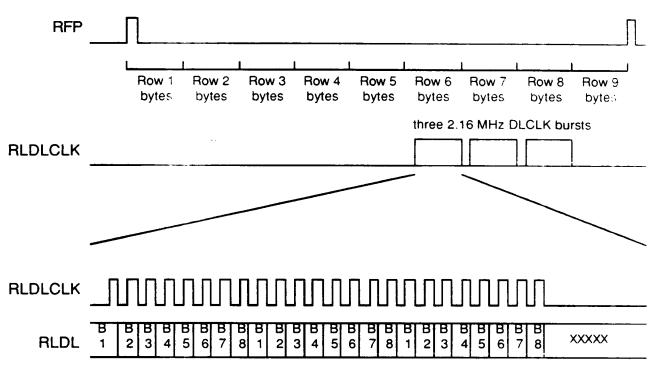

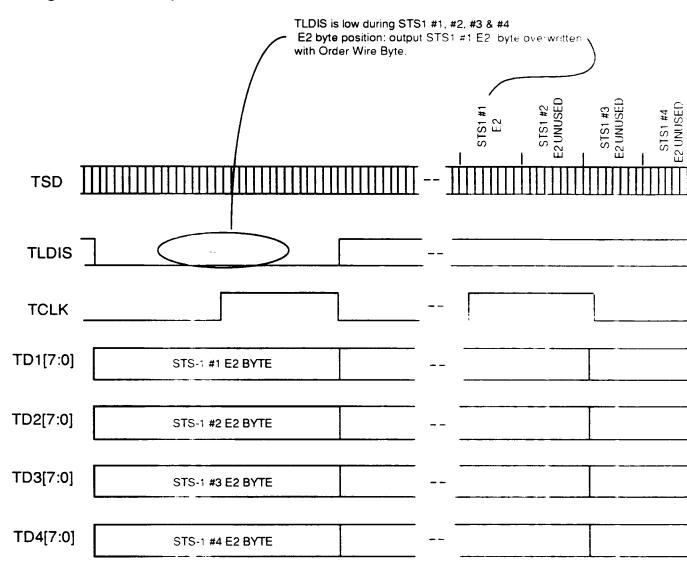

| TLDIS   | CMOS<br>Input  | 53 | The active high transmit line disable (TLDIS) signal selectively, on a byte by byte basis, disables overwriting the overhead bytes of all four of the incoming STS-3 streams. TLDIS is sampled on the rising edge of TCLK.                                                                              |

| THCLK | ECL<br>Test<br>Point | 54 | The transmit high speed clock (THCLK) is a 77.76 MHz ECL level output which is used for production and diagnostic tests only. DO NOT TERMINATE THIS PIN, NOR CONNECT IT TO ANY INPUT.                                                                                   |

|-------|----------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTE   | Unused               | 56 | Reserved for future loopback function.                                                                                                                                                                                                                                  |

| SDLE  | CMOS<br>Input        | 57 | The active high section diagnostic loopback enable (SDLE) signal controls the source of received data. When SDLE is high, the parallel transmit data is looped back to the receive side for diagnostic purposes just past the point where section overhead is inserted. |

| DLE   | Unused               | 58 | Reserved for future loopback function.                                                                                                                                                                                                                                  |

| TUDR  | CMOS<br>Output       | 59 | The active high Transmit HDLC Underrun (TUDR) signal is asserted when the data buffer of the transmit HDLC controller has underrun, and the current HDLC frame has been aborted.                                                                                        |

| TINT  | CMOS<br>Output       | 60 | The active high Transmit HDLC Interrupt (TINT) signal is asserted when the transmit HDLC controller requests additional HDLC frame data.                                                                                                                                |

| REOM  | CMOS<br>Output       | 61 | The active high Receive HDLC End of Message (REOM) signal is asserted when the last byte of an HDLC frame is read from the receive HDLC data register, or a FIFO overrun occurs in the HDLC receiver.                                                                   |

| RINT  | CMOS<br>Output       | 62 | The active high Receive HDLC Interrupt (RINT) signal is asserted when the receive HDLC controller detects a change in status of the receive section data communication channel.                                                                                         |

| LINITO                                                       | Ta            |                                              |                                                                                                                                                                                                                              |

|--------------------------------------------------------------|---------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LINTB                                                        | Open<br>Drain | 63                                           | The interrupt (LINT) signal goes high when one of the various interrupting sources within the line overhead processor or byte interleaved multiplexor / demultiplexor circuits is active and enabled to generate interrupts. |

| SINT                                                         | TTL<br>Output | 64                                           | The interrupt (SINT) signal goes high when one of the various interrupting sources within the section overhead processor or HDLC circuits is active and enabled to generate interrupts.                                      |

|                                                              |               |                                              | The interrupt signals go low when the interrupt is acknowledged by reading a status register or masked by writing to an interrupt enable register.                                                                           |

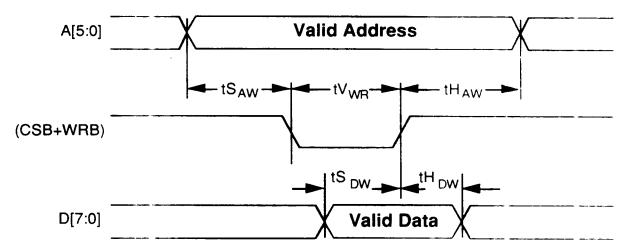

| D[0]<br>D[1]<br>D[2]<br>D[3]<br>D[4]<br>D[5]<br>D[6]<br>D[7] | CMOS<br>I/O   | 73<br>72<br>71<br>70<br>69<br>68<br>67<br>66 | The bidirectional data bus (D[7:0]) is used during SLIM-12 register read and write accesses.                                                                                                                                 |

| LCSB                                                         | CMOS<br>Input | 77                                           | The active low Line Chip Select signal LCSB is low during register accesses of the SONET line overhead processor.                                                                                                            |

| SCSB                                                         | CMOS<br>Input | 76                                           | The active low Section Chip Select signal SCSB is low during register accesses of the SONET section overhead processor.                                                                                                      |

| HSCSB                                                        | Unused        | 75                                           | This pin is reserved for future mode selection of the high speed parallel-serial converter block.                                                                                                                            |

| RSTB                                                         | CMOS<br>Input | 78                                           | The active low reset (RSTB) signal provides an asynchronous SLIM-12 reset. RSTB is a Schmitt triggered input with an integral pull up resistor.                                                                              |

| WRB                                                          | CMOS<br>Input | 79                                           | The active low write strobe (WRB) signal is low during a SLIM-12 register write access. The D[7:0] bus contents are clocked into the addressed register on the rising WRB edge while LCSB, SCSB, and HSCSB are low.          |

|                                      | 10400          |                            |                                                                                                                                                                                                                                                                                                          |

|--------------------------------------|----------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

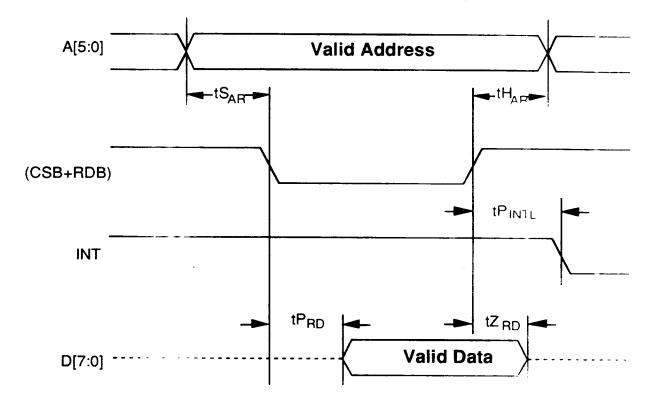

| RDB                                  | CMOS<br>Input  | 80                         | The active low read enable (RDB) signal is low during a SLIM-12 register read access. The SLIM-12 drives the D[7:0] bus with the contents of the addressed register while RDB and LCSB, SCSB, and HSCSB are low.                                                                                         |

| ТЅТВ                                 | CMOS<br>Input  | 81                         | Used only in production test to put the module into test mode.                                                                                                                                                                                                                                           |

| TRSB                                 | CMOS<br>Input  | 83                         | The test register select (TRSB) signal discriminates between normal and test mode register accesses. TRSB is low during test mode register accesses, and is high during normal mode register accesses. This pad contains an internal pull up resistor.                                                   |

| A[0]<br>A[1]<br>A[2]<br>A[3]<br>A[4] | CMOS<br>Input  | 88<br>87<br>86<br>85<br>84 | The address bus (A[4:0]) selects specific registers during SLIM-12 register accesses.                                                                                                                                                                                                                    |

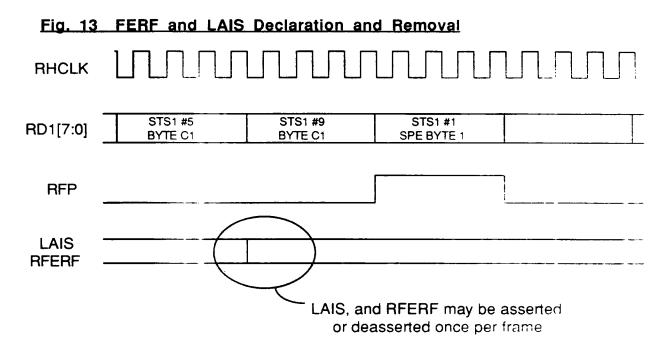

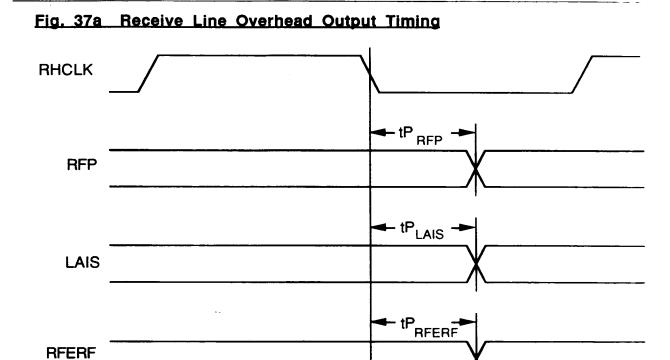

| LAIS                                 | CMOS<br>output | 89                         | The line alarm indication Signal (LAIS) is high while Line AIS is detected in the STS-12 stream. LAIS is updated on the falling edge of RHCLK                                                                                                                                                            |

| RFERF                                | CMOS<br>Output | 90                         | The line Received Far End Receive Failure indication (RFERF) is high while a line Far End Receive Failure signal is detected in the incoming STS-12 stream. RFERF is updated on the falling edge of RHCLK.                                                                                               |

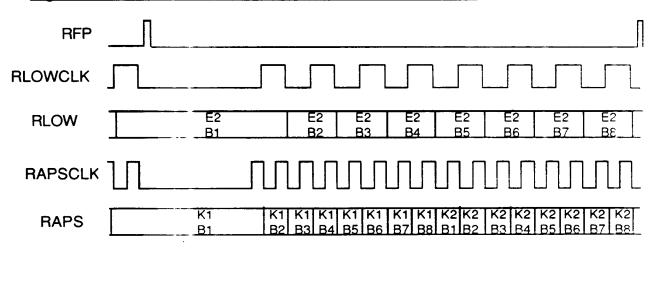

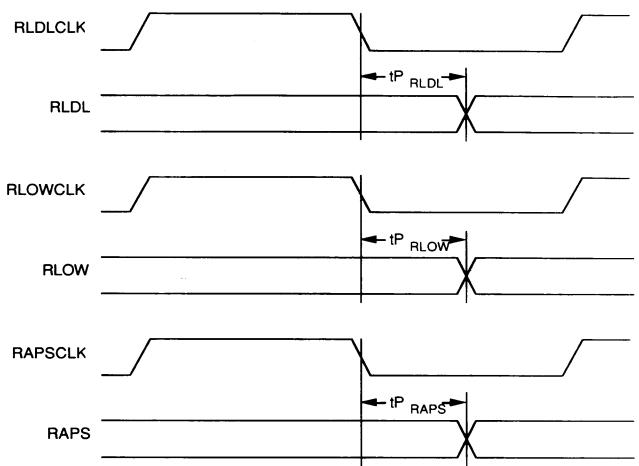

| RAPS                                 | CMOS<br>Output | 91                         | The receive automatic protection switch (RAPS) signal carries the 128 kbit/s line automatic protection switch channel extracted from STS-1 #1 line overhead K1 and K2 bytes of the STS-12 stream. RAPS is updated on the falling edge of RAPSCLK. The byte boundaries RAPS signal are identified by RFP. |

| RAPSCLK                              | CMOS<br>Output | 93                         | The receive automatic protection switch clock (RAPSCLK) signal is a 128 kHz clock for use by downstream circuitry that processes the line automatic protection switch channel. RAPSCLK is a gapped 144 kHz clock.                                                                                        |

| RLOW    | CMOS<br>Output | 94  | The receive line order wire (RLOW) signal carries the 64 kbit/s line order wire channel extracted from STS-1 #1 line overhead E2 byte of the STS-12 stream. RLOW is updated on the falling edge of RLOWCLK. The byte boundaries on RLOW are identified by RFP.                                                                                                                                                               |

|---------|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLOWCLK | CMOS<br>Output | 95  | The receive line order wire clock (RLOWCLK) signal is a 64 kHz clock for use by downstream circuitry that processes the line order wire channel. RLOWCLK is a gapped 72 kHz clock.                                                                                                                                                                                                                                           |

| RLDL    | CMOS<br>Output | 96  | The receive line data link (RLDL) signal carries the 576 kbit/s line data communication channel extracted from the STS-1 #1, D4-D12 line overhead bytes of the the STS-12 stream. RLDL is updated on the falling edge of RLDLCLK.                                                                                                                                                                                            |

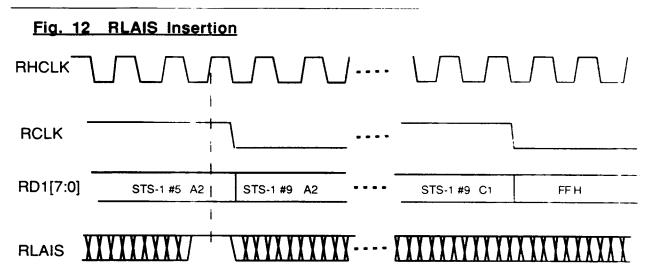

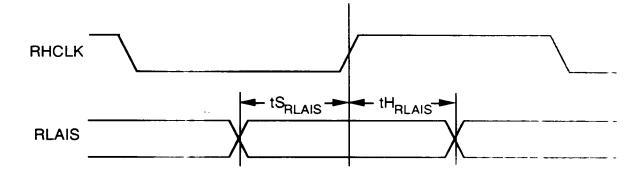

| RLAIS   | CMOS<br>Input  | 97  | The active high receive line alarm indication (RLAIS) signal controls the insertion of line AIS in the received STS-12 stream. RLAIS is sampled on the rising edge of RHCLK.                                                                                                                                                                                                                                                 |

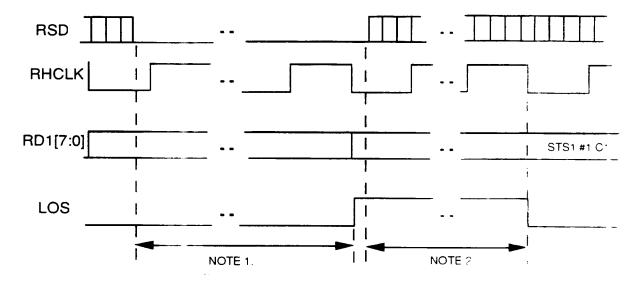

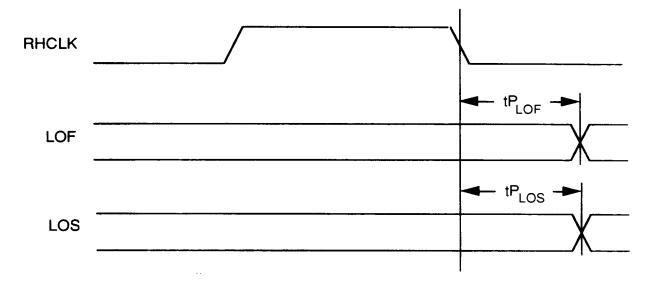

| LOS     | CMOS<br>Output | 98  | The loss of signal (LOS) output is asserted when a loss of signal is declared. This occurs when a violating period ( $20\pm3~\mu s$ ) of consecutive all zeros patterns is detected in the incoming STS-12 stream. LOS is cleared when two valid framing words are detected and during the intervening time, no violating period of consecutive all zeros patterns is detected. LOS is updated on the falling edge of RHCLK. |

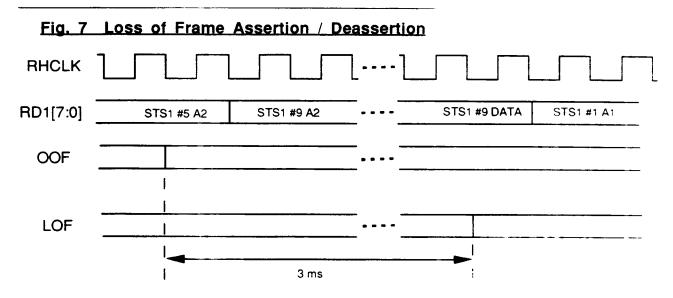

| LOF     | CMOS<br>Output | 100 | The loss of frame (LOF) output is asserted when a loss of frame is declared. This occurs when an out-of-frame condition persists for a period of 3 ms. LOF is cleared when an in-frame condition persists for a period of 3 ms. LOF is updated on the falling edge of RHCLK.                                                                                                                                                 |

| RLDLCLK | CMOS<br>Output | 101 | The receive line data link clock (RLDLCLK) signal is a 576 kHz clock for use by downstream circuitry that processes the line data communication channel. RLDLCLK is a gapped 2.16 MHz 67%(high)/33%(low) duty cycle clock.                                                                                                                                                                                                   |

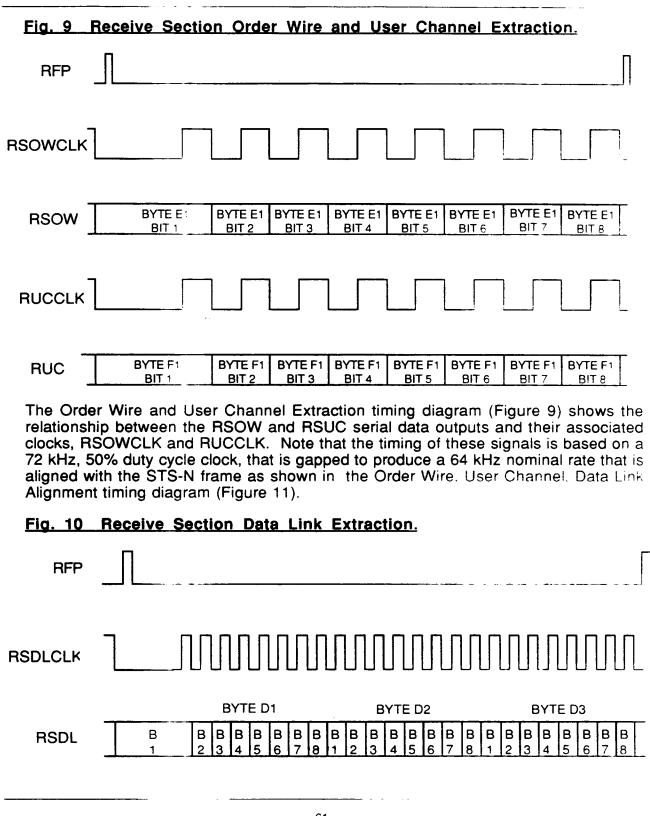

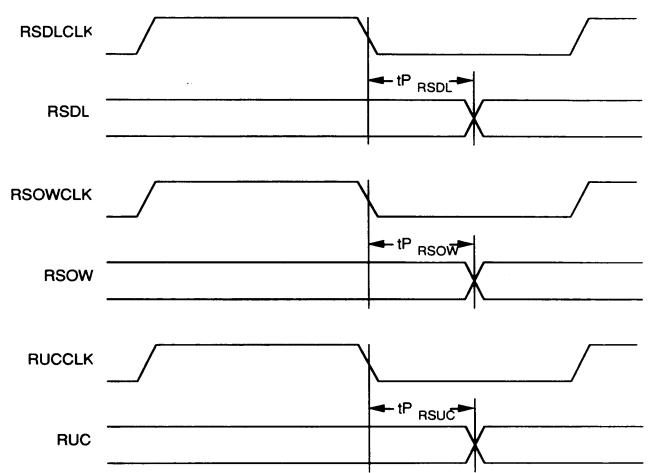

| RUC     | CMOS<br>Output | 102 | The receive section user channel (RUC) signal carries the 64 kbit/s section user channel extracted from the STS-1 #1 section overhead F1 byte of the STS-12 stream. RUC is updated on the falling edge of RUCCLK. The byte boundaries on RUC are identified by RFP.                                         |

|---------|----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RUCCLK  | CMOS<br>Output | 103 | The receive section user channel clock (RUCCLK) signal is a 64 kHz clock for use by downstream circuitry that processes the section user channel. RUCCLK is a gapped 72 kHz clock.                                                                                                                          |

| RSOW    | CMOS<br>Output | 105 | The receive section order wire (RSOW) signal carries the 64 kbit/s section order wire channel extracted from the STS-1 #1 section overhead E1 byte of the STS-12 stream. RSOW is updated on the falling edge of RSOWCLK. The byte boundaries on RSOW are identified by RFP.                                 |

| RSOWCLK | CMOS<br>Output | 106 | The receive section order wire clock (RSOWCLK) signal is a 64 kHz clock for use by downstream circuitry that processes the section order wire channel. RSOWCLK is a gapped 72 kHz clock.                                                                                                                    |

| RSDL    | CMOS<br>Output | 107 | The receive section data link (RSDL) signal carries the 192 kbit/s section data communication channel extracted from the STS-1 #1, D1-D3 section overhead bytes of the the STS-12 stream. RSDL is updated on the falling edge of RSDLCLK.                                                                   |

| RSDLCLK | CMOS<br>Output | 108 | The receive section data link clock (RSDLCLK) signal is a 192 kHz clock for use by downstream circuitry that processes the section data communication channel. RSDLCLK is a gapped 216 kHz clock.                                                                                                           |

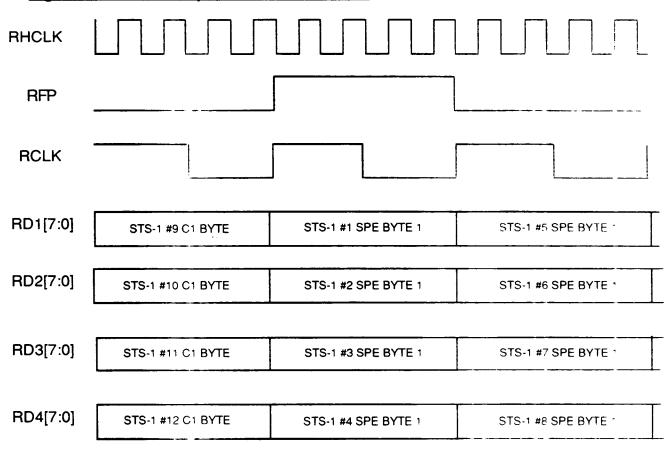

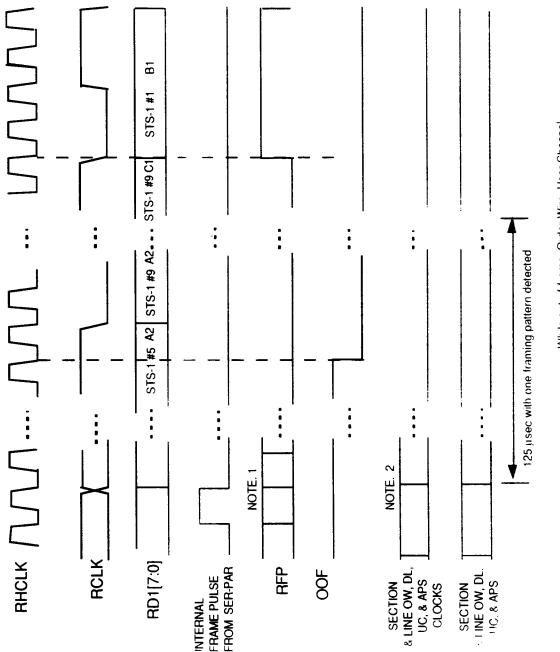

| RHCLK   | TTL<br>Output  | 109 | The receive high speed clock (RHCLK) signal provides timing for processing the internal receive high speed byte serial busses. RHCLK is nominally a 77.76 MHz, 50% duty cycle clock, and is internally generated by dividing down the recovered clock, RSCLK. RLAIS is sampled on the rising edge of RHCLK. |

| p                                                                            |                |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------|----------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

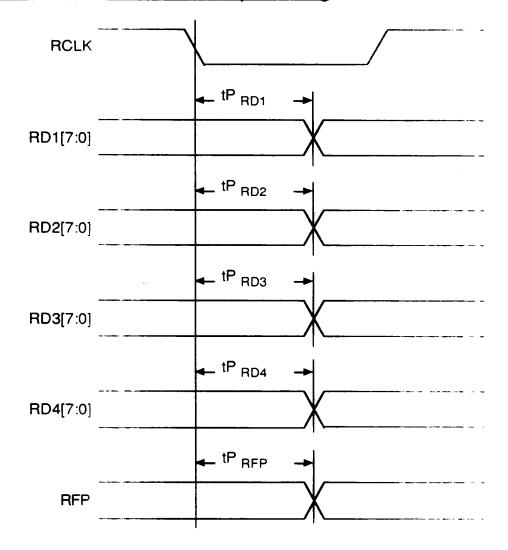

| RCLK                                                                         | CMOS<br>Output | 111                                                  | The receive clock (RCLK) signal provides timing for processing the RD1, RD2, RD3, and RD4 byte serial busses. These busses are updated on the falling edge of RCLK. RCLK is nominally a 19.44 MHz, 50% duty cycle clock, and is generated by dividing RHCLK.                                                                                                                                                                      |

| RFP                                                                          | CMOS<br>Output | 112                                                  | The receive frame pulse (RFP) signal marks the transport frame alignment on the RD1, RD2, RD3, and RD4 byte serial busses. RFP is high to mark the first byte of the synchronous payload envelope of the first constituent STS-1 stream output on each of these busses. RFP is updated on the falling edge of RCLK.                                                                                                               |

| RD1[0]<br>RD1[1]<br>RD1[2]<br>RD1[3]<br>RD1[4]<br>RD1[5]<br>RD1[6]<br>RD1[7] | CMOS<br>Output | 113<br>114<br>115<br>117<br>118<br>120<br>121<br>123 | The receive PCM data (RD1[7:0]) bus carries PCM data in byte serial format. RD1[7:0] carries the receive PCM data of STS-1 #1, STS-1 #5, and STS-1 #9. RD1[7:0] is updated on the falling edge of RCLK. RD1[7] is the most significant bit (corresponding to bit 1, the first bit transmitted of each serial PCM word). RD1[0] is the least significant bit (corresponding to bit 8, the last bit transmitted of each PCM word).  |

| RD2[0]<br>RD2[1]<br>RD2[2]<br>RD2[3]<br>RD2[4]<br>RD2[5]<br>RD2[6]<br>RD2[7] | CMOS<br>Output | 124<br>126<br>127<br>129<br>130<br>131<br>132<br>134 | The receive PCM data (RD2[7:0]) bus carries PCM data in byte serial format. RD2[7:0] carries the receive PCM data of STS-1 #2, STS-1 #6, and STS-1 #10. RD2[7:0] is updated on the falling edge of RCLK. RD2[7] is the most significant bit (corresponding to bit 1, the first bit transmitted of each serial PCM word). RD2[0] is the least significant bit (corresponding to bit 8, the last bit transmitted of each PCM word). |

| RD3[0]<br>RD3[1]<br>RD3[2]<br>RD3[3]<br>RD3[4]<br>RD3[5]<br>RD3[6]<br>RD3[7] | CMOS<br>Output | 135<br>136<br>137<br>138<br>140<br>141<br>142<br>143 | The receive PCM data (RD3[7:0]) bus carries PCM data in byte serial format. RD3[7:0] carries the receive PCM data of STS-1 #3, STS-1 #7, and STS-1 #11. RD3[7:0] is updated on the falling edge of RCLK. RD3[7] is the most significant bit (corresponding to bit 1, the first bit transmitted of each serial PCM word). RD3[0] is the least significant bit (corresponding to bit 8. the last bit transmitted of each PCM word). |

| RD4[0]<br>RD4[1]<br>RD4[2]<br>RD4[3]<br>RD4[4]<br>RD4[5]<br>RD4[6]<br>RD4[7] | CMOS<br>Output            | 144<br>145<br>147<br>148<br>150<br>151<br>153<br>154 | The receive PCM data (RD4[7:0]) bus carries PCM data in byte serial format. RD4[7:0] carries the receive PCM data of STS-1 #4, STS-1 #8, and STS-1 #12. RD4[7:0] is updated on the falling edge of RCLK. RD4[7] is the most significant bit (corresponding to bit 1, the first bit transmitted of each serial PCM word). RD4[0] is the least significant bit (corresponding to bit 8, the last bit transmitted of each PCM word). |

|------------------------------------------------------------------------------|---------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSD                                                                          | Analog<br>or ECL<br>input | 156                                                  | The receive serial data (RSD) is the 50 $\Omega$ , unbalanced input for the 622.08 Mbit/s. scrambled NRZ serial STS-12 data stream.                                                                                                                                                                                                                                                                                               |

| VTERM                                                                        | Analog                    | 157                                                  | Terminating voltage for the RSD input signal terminating resistor. If RSD is dc coupled to an ECL output, then VTERM should be connected a to -2V supply with good ac coupling to the driver's ground. If RDSC is ac coupled to the output of a transconductance amplifier, then VTERM should be connected to VTH.                                                                                                                |

| VTH                                                                          | Analog                    | 158                                                  | Threshold voltage for the data slicers. Nominally -1.3 V, it can be adjusted within a $\pm$ 0.2 V range if desired. VTH has an internal resistance of 1k $\Omega$ .If RDSC is ac coupled to its source, then VTH should be connected to VTERM.                                                                                                                                                                                    |

| RSCLK+                                                                       | ECL<br>Output             | 160                                                  | The recovered serial clock (RSCLK) signal carries the clock signal recovered from the RSD data stream by the SLIM-12 module. RSCLK is nominally a 622.08 MHz, 50% duty cycle clock.                                                                                                                                                                                                                                               |

| VCCR                                                                         | Power                     | 149                                                  | +5V dc supply to the high speed receiver clock and data generator.                                                                                                                                                                                                                                                                                                                                                                |

| VCCT                                                                         | Power                     | 16                                                   | +5V dc supply to the transmit high speed clock generator.                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                              |                           |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VEER | Power | 161                                                                                      | -5.2 V dc supply to the high speed receive clock and data generator.                                                                                                   |

|------|-------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VEET | Power | 175<br>168                                                                               | -5.2 V dc supply to the high speed transmit clock<br>generator.                                                                                                        |

| VDD  | Power | 128<br>116<br>104<br>92<br>74<br>55                                                      | +5V supply for the ECL-CMOS translators, section overhead transceiver, and line overhead transceiver and STS-12 to STS-3 muldems.                                      |

| GND  | Power | 146<br>133<br>122<br>110<br>99<br>82<br>65<br>28<br>25<br>13<br>172<br>165<br>159<br>155 | OV supply return for the STS-12 parallel-serial converter, ECL-CMOS translators, section overhead transceiver, line overhead transceiver, and STS-3 to STS-12 muldems. |

SONET STS-12 LINE INTERFACE MODULE

| VTT | Power | 125<br>119<br>49<br>22           | -2V for the internal high speed ECL pull down resistors.                         |

|-----|-------|----------------------------------|----------------------------------------------------------------------------------|

| VEE | Power | 139<br>43<br>37<br>31<br>19<br>8 | -5.2V For the STS-12 parallel-to-serial converter. and the ECL-CMOS translators. |

# Notes on Pin Description:

- 1. All SLIM-12 CMOS inputs and bidirectionals operate at CMOS logic levels

- 2. All SLIM-12 CMOS outputs and bidirectionals have 2 mA drive capability, except the SINT, LINT, and HSINT outputs and the D[7:0] bidirectionals which have 4 mA drive capability.

- 3. All SLIM-12 TTL inputs have 74F logic level and loading characteristics.

- 4. All SLIM-12 ECL inputs and outputs are compatible with 100K ECL

SONET STS-12 LINE INTERFACE MODULE

# **FUNCTIONAL DESCRIPTION**

# Clock and Data Recovery

The Clock and Data Recovery is implemented with a GaAs Phase Locked Loop integrated circuit which accepts an ECL compatible input signal, and produces ECL clock and data outputs to be used by the serial to parallel converter.

The receive signal at the RSD input is a serial non return to zero data stream with a peak to peak amplitude at least 0.6 V and at most 2.0 V which is centred at 1.3 V. RSD is a 50  $\Omega$  unbalanced input, terminated to the VTERM pin. If RSD is A.C. coupled to its source, then its termination point VTERM should be connected to the slicing threshold voltage VTH. If RSD is an ECL input, then VTERM should be connected to -2V. A comparator slices the data into logic levels with respect to the voltage at VTH.

The receive clock recovery circuit is a PLL which synchronizes the 622.08 MHz output of a VCO to the incoming data stream by comparing the rising transitions of the VCO output with those of the incoming NRZ data. The greater the number of transitions in the data, the greater the stability of the recovered clock. The falling edge of the recovered clock strobes a data sampling flip-flop which regenerates the data at ECL levels for use by the down stream serial-to-parallel converter. The RSCLK output caries an unbalanced ECL version of the 622.08 MHz recovered clock to the outside world.

The jitter transfer function of the PLL attenuates jitter at 6 dB per octave for jitter frequencies above approxamately300 kHz. Jitter tolerance is greater than 0.2 Ulpp for jitter frequencies above 250 kHz, 2 Ulpp from 250 kHz to 25 kHz, and 20 Ulpp below 2.5 kHz.

# Serial-To-Parallel Conversion

The outputs of the Clock and Data Recovery circuit drives the ECL compatible inputs of the Serial-to-Parallel Converter. This converter searches for the A1 and A2 bytes in the STS-12 frame pattern. Three valid A1 bytes followed by three valid A2 bytes synchronize the byte-wide parallel output to the byte boundaries of the serial input signal. The framer searches for the last three of the 12 A1, and the first three of the 12 A2 bytes.

Once the STS-12 frame has been found, the frame search process halts, and the parallel output data continues to be partitioned according to the initially found frame position. Should the frame verification circuit in the down stream Receive Section Overhead Processor determine that the frame synchronization is incorrect, it reactivates the frame search process.

PM5712 SLIM-12

#### ADVANCE INFORMATION

SONET STS-12 LINE INTERFACE MODULE

There are three outputs from the serial-to-parallel converter. The byte-wide data bus with a data rate of 77.76 Mbyte/s, the 77.76 MHz byte clock generated from the 622.08 MHz recovered clock, and the 8 kHz frame pulse indicating the transition from A1 bytes to A2 bytes in the STS-12 frame pattern are all transferred to the down stream section overhead processor. These signals are CMOS compatible in order to drive the Receive Section Overhead Processor.

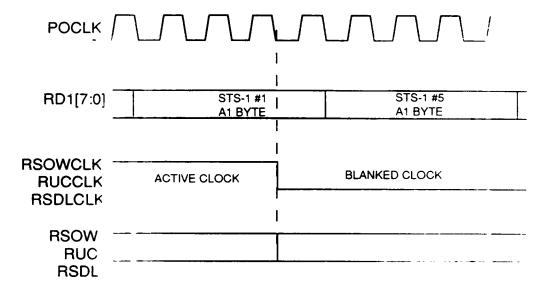

# Receive Section Overhead Processing

The Receive Section Overhead Processor (RSOP) is implemented using the PM5301 SONET Section Transceiver (SSTX) integrated circuit. The Section Overhead Processor descrambles the received data and extracts the data link channel, order wire channel, and user channel from the section overhead. The SSTX also contains a Byte Interleaved Parity (BIP-8) detector, and a microprocessor peripheral used to receive LAPD/HDLC frames from the section overhead data link. All configuring of the SSTX and monitoring of its alarms are performed via the SLIM-12 microprocessor bus.

The SSTX is is configured to process an STS-12 data stream that is presented in byte serial format at 77.76 Mbytes/s. Receive Section Overhead Processor descrambles the received data and extracts the data link channel, order wire channel and user channel from the section overhead, and provides them as lower rate bit serial outputs (RDL, ROW, RUC) together with associated clock signals (RDLCLK, ROWCLK, RUCCLK). The complete descrambled SONET data stream is then passed to the Receive Line Terminating Receiver in byte serial format. Line alarm indication signal may be inserted into this descrambled byte serial data stream by setting the RLAIS input high.

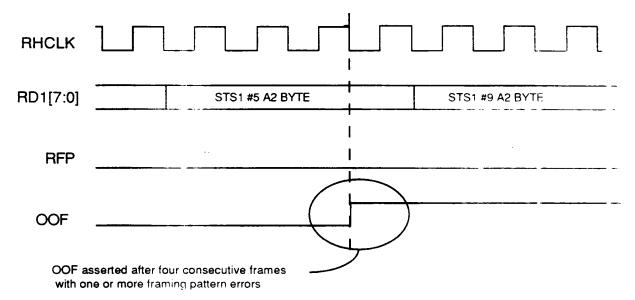

The Receive Section Overhead Processor verifies that the frame pulse provided by the upstream frame pattern detector in the serial-to-parallel converter by watching for the frame pattern to recur at the same position in the frame. It generates an out-of-frame signal (OOF) which causes the frame recovery process in the serial-to-parallel converter to engage if the frame pattern does not recur. Loss of frame (LOF), and loss of signal (LOS) outputs are provided at pins on the module. LOF is high after a 3 ms period without a valid frame pulse. LOS is high after a 20  $\pm$  2.5  $\mu s$  period of all zeros data at the input. LOS and LOF return low after a frame pattern has been detected and verified.

Microprocessor accessible registers hold the states of the OOF, LOF, or LOS alarms and count section level bit-interleaved parity (BIP-8) errors. BIP-8 accumulators are large enough to be read as infrequently as once per second. The section overhead interrupt, SINT may be activated by state transitions on the OOF, LOF, or LOS outputs, or by a single BIP-8 error event, depending on which is unmasked. Each interrupt source is individually maskable, and is cleared by reading the interrupting register.

#### ADVANCE INFORMATION

SONET STS-12 LINE INTERFACE MODULE

The Receive Section Overhead Processor provides descrambled data, along with appropriate clock and frame alignment indication signals for use by downstream circuitry that processes the SONET line overhead, synchronous payload envelope.

# Receive Section HDLC Receiver

The Section HDLC receiver is connected to the receive section data communications channel. The HDLC receiver is a microprocessor peripheral used to receive LAPD/HDLC frames.

The HDLC receiver detects the change from flag characters to the first data frame byte, removes stuffed zeros on the incoming data stream, receives frame data, and calculates the CRC-CCITT frame check sequence.

Received data is placed into a 4-level FIFO buffer. A status register contains the Overrun, End of Message, Flag, and Data Available flags.

On End of Message, the status register also indicates the FCS status and the number of valid bits in the final byte. An interrupt (RINT) may be generated when 1, 2, or 3 (programmable count) bytes are stored in the FIFO. An interrupt may also be generated when the terminating flag sequence, abort sequence, or FIFO overrun are detected.

An external DMA controller may be used to transfer packets from the HDLC Receiver to external memory.

# Receive Line Overhead Processing

The Receive Line Overhead Processing function is performed by the PM5311 SONET Line Transceiver integrated circuit (RLOP). All performance monitoring information, alarm states, and option controls are accessible via the SLIM-12 microprocessor bus. Note that after a reset, the SLTX is not optioned for STS-12 operation. 03H must be written to register 00H of the SLTX to set it for STS-12.

The Receive Line Overhead Processor comprises the following seven functional blocks:

- 1. Timing Block: interfaces the data inputs with the other blocks of the RLOP.

- 2. FERF Detect Block: detects the presence of Line Far End Receive Failure in the STS-12 stream.

- 3. Line AIS Block: detects the presence of a Line Alarm Indication Signal (AIS) in the STS-12 stream.

- APS Extract Block: extracts the Automatic Protection Switch Channel.

#### ADVANCE INFORMATION

# SONET STS-12 LINE INTERFACE MODULE

PM5712 SLIM-12

- 5. Data Link Extract Block: extracts the line data communications channel.

- 6. Order Wire Extract Block: extracts the line order wire channel.

- 7 The Error Monitor Block calculates the received line BIP-8 error detection codes

The Timing Block provides timing for the other RLOP blocks using the parallel data clock, and frame pulse inputs as reference sources. The Timing Block maintains counters which identify channels and bytes within channels. Identified bytes along with generated clocks are provided to other RLOP blocks.

The FERF Detect Block detects the presence of Line Far End Receive Failure in the STS-12 stream. Output FERF is asserted when a 110 binary pattern is detected in bits 6, 7, and 8 of the STS-1 #1 K2 line layer byte, for five consecutive frames. FERF is deasserted when any pattern other than 110 is detected in bits 6, 7, and 8 of the K2 byte for five consecutive frames. The Received FERF alarm is available at the RFERF output pin, and is updated on the falling edge of RHCLK.

The Line AIS Block detects the presence of a Line Alarm Indication Signal (LAIS) in the STS-12 stream. Output LAIS is asserted when a 111 binary pattern is detected in bits 6,7,8 of the K2 byte, contained in the line layer of STS-1 #1, for five consecutive frames. LAIS is deasserted when any pattern other than 111 is detected in bits 6, 7, and 8 of the K2 byte for five consecutive frames. LAIS is updated with timing aligned to RHCLK.

The APS Extract Block extracts the Automatic Protection Switch Channel (bytes K1 and K2) from STS-1 #1 of the STS-12 stream. The extracted bytes are serialized and output on signal RAPS at a nominal 128 kbit/s rate. Timing for downstream processing of the APS channel is provided by the RAPSCLK output. RAPSCLK is derived from a 144 kHz clock that is gapped to yield an average frequency of 128 kHz. APS is updated with timing aligned to RAPSCLK. In turn, RAPSCLK is updated with timing aligned to RHCLK.

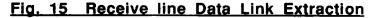

The Data Link Extract Block extracts the line data communication channel (bytes D4 to D12) from STS-1 #1 of the STS-12 stream. The extracted bytes are serialized and output on signal DL at a nominal 576 kbit/s rate. Timing for downstream processing of the data communication channel is provided by the DLCLK output. DLCLK is derived from a 2.16 MHz 67%(high)/33%(low) clock that is gapped to yield an average frequency of 576 kHz. DL is updated with timing aligned to DLCLK. In turn, DLCLK is updated with timing aligned to RHCLK.

The Order Wire Extract Block extracts the line order wire channel (byte E2) from STS-1 #1 of the STS-12 stream. The extracted bytes are serialized and output on signal OW at a nominal 64 kbit/s rate. Timing for downstream processing of the order wire channel is provided by the OWCLK output. OWCLK is derived from an 72 kHz clock that is gapped to yield an average frequency of 64 kHz. RLOW is updated with

#### PRELIMINARY INFORMATION

SONET STS-12 LINE INTERFACE MODULE

timing aligned to RLOWCLK. In turn, RLOWCLK is updated with timing aligned to RHCLK.

The Error Monitor Block calculates the received line BIP-8 error detection codes based on the line overheads and synchronous payload envelopes of each of the constituent STS-1s in the STS-12 stream. The line BIP-8 code is a bit interleaved parity calculation using even parity. Details are provided in the references. The calculated BIP-8 codes are compared with the BIP-8 codes extracted from each constituent STS-1 of the following frame. Any differences indicate that a line layer bit error has occurred. Up to 768000 (12 x 8 x 8000) bit errors can be detected per second.

The Error Monitor Block accumulates these line layer bit errors in a 20 bit saturating counter that can be read via the microprocessor interface. The counter's contents are transferred to the read register, then cleared to 0 by a write command. Note, this counter should be polled at least once per second to avoid saturation which in turn may result in missed bit error events.

# Byte Interleaved Demultiplexing

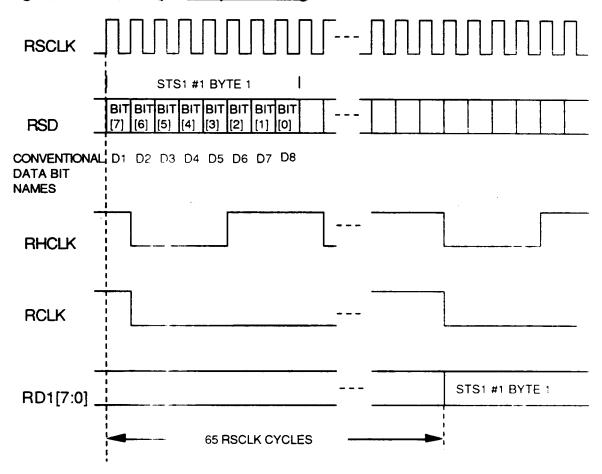

Byte Interleaved Demultiplexing is located on the PM5311 SLTX integrated circuit along with the Receive Line Overhead Processor. Once the SLTX has been optioned for STS-12, this demultiplexor will separate a byte-serial STS-12 data stream into 4 byte serial STS-3 streams with a common 19.44 MHz clock (RCLK) and a common 8 kHz frame pulse (RFP).

The high speed input clock, RHCLK, is divided by four to produce the RCLK signal. The falling edge of RCLK updates the low speed output streams. RFP signal indicates the location of the first byte of the transport overhead in the low speed output streams.

A demultiplex block controls the demultiplexing of the high speed byte serial input stream from the receive line overhead processor. The high speed clock, RHCLK, loads the byte wide input stream into one of four demultiplexor registers. The demultiplex block loads these registers sequentially, so that outputs RD1[7:0], RD2[7:0], RD3[7:0], and RD4[7:0] receive data for STS-3 #1, STS-3 #2, STS-3 #3, STS-3 #4, etc.

A retiming block contains registers which sample the demultiplexed byte serial stream on the falling edge of the low speed output clock, RCLK. Thus, RD1[7:0], RD2[7:0], RD3[7:0], and RD4[7:0] are updated on the falling edge of RCLK.

# **Byte Interleaved Multiplexing**

The STS-3 to STS-12 Byte Interleaved Multiplexing is located on the PM5311 SLTX. It is comprised of a timing interface block, and a sample and mux block.

# PM5712 SLIM-12

#### ADVANCE INFORMATION

SONET STS-12 LINE INTERFACE MODULE

The Timing Block provides timing signals necessary for the operation of the multiplexer. Its high speed input clock, THCLK, is divided by four to produce a data sample clock. The phase alignments of the sample clock, and the 19.44 MHz input clock, TCLK, are compared in order to monitor for violations of set-up or hold times. These violations may occur during the transfer of the low speed input data from TCLK based timing to THCLK based timing. If the two clocks are aligned such that set-up or hold times may be violated, a phase alignment error event is generated, and the phase alignment of the sample clock is modified to avoid timing errors. A jitter tolerance between the sample clock and the nominal phase alignment of TCLK is up to  $\pm 0.375$  unit intervals for STS-3 to STS-12 multiplexing.

The Sample and Mux Block contains registers used to sample the low speed input data using TCLK. The sampled data is then transferred to THCLK based timing using the data sample clock, and multiplexed onto the high speed data output bus to the transmit line overhead processor.

### Transmit Line Overhead Insertion

Line overhead is inserted into the transmit signal by the Transmit Line Overhead Processor, (TLOP) which is located on the PM5311 SLTX integrated circuit. The Transmit Line Overhead Processor is composed of six functional blocks.

- 1. Timing Block: provides timing for the other blocks within the Transmit Line Overhead Processor.

- 2. APS Insert Block inserts the Automatic Protection Switch channel data into the STS-12 stream.

- 3. Data Link Insert Block inserts the line data communication channel into the STS-12 stream.

- 4. Order Wire Insert Block inserts the line order wire channel data into the STS-12 stream.

- 5. BIP-8 Calculate and Insert Block: calculates the line BIP-8 error detection code for each of the constituent STS-1s.

- The input to the data link can be connected to the HDLC Transmitter so that it can be written to directly from a microprocessor.

The Timing Block provides timing for the other blocks within the Transmit Line Overhead Processor. The PICLK and FPIN inputs are the source of timing. The timing is preset for the STS-12 byte serial format. A channel counter is maintained, allowing individual bytes to be identified as required for the other blocks within the Transmit Line Overhead Processor. The channel counter skips the section overhead byte locations. The Timing Block regenerates the input clock and frame pulses from

PM5712 SLIM-12

#### ADVANCE INFORMATION

SONET STS-12 LINE INTERFACE MODULE

the Byte Interleaved MUX block, and provides them to the Transmit Section Overhead processor

The APS Insert Block inserts the automatic protection switch channel (bytes K1 and K2) into STS-1 #1 of the STS-12 stream when enabled by an internal register. The data in the K1 and K2 slots is passed transparently while APS insertion is disabled. The K1 and K2 bytes are input serially using the TAPS signal at a nominal 128 kbit/s rate. Timing for processing of the TAPS channel is provided by the TAPSCLK output. TAPSCLK is derived from a 144 kHz clock that is gapped to yield an average frequency of 128 kHz. TAPS is sampled on the rising edge of TAPSCLK. APS insertion, when enabled, may be disabled by the TLDIS input.

The Data Link Insert Block inserts the line data communication channel (bytes D4 to D12) into STS-1 #1 of the STS-12 stream when enabled by an internal register. The data on PIN[7:0] is passed transparently while data link insertion is disabled. The D4 to D12 bytes are input serially using the TLDL signal at a nominal 576 kbit/s rate. Timing for processing of the line data communication channel is provided by the TLDLCLK output, which is derived from a 1.728 MHz clock that is gapped to yield an average frequency of 576 kHz. TLDL is sampled on the rising edge of TLDLCLK. Line data communication channel insertion, when enabled, may be disabled by the TLDIS input.

The Order Wire Insert Block inserts the line order wire channel (E2 byte) into STS-1 #1 of the STS-12 stream when enabled by an internal register. The data in the order wire time slots is passed transparently while order wire insertion is disabled. The E2 byte is input serially using the TLOW signal at a nominal 64 kbit/s rate. Timing for processing of the line order wire is provided by the TLOWCLK output, which is derived from a 72 kHz clock that is gapped to yield an average frequency of 64 kHz. TLOW is sampled on the rising edge of TLOWCLK. Line order wire insertion, when enabled, may be disabled by the TLDIS input.

The BIP-8 Calculate and Insert Block calculates the line BIP-8 error detection codes based on the line overheads and synchronous payload envelopes of each of the constituent STS-1s in the STS-12 stream. The line BIP-8 code is a bit interleaved parity calculation using even parity. Details are provided in the references. The calculated BIP-8 codes are inserted into the B2 byte positions of the constituent STS-1s of the following frame. Line BIP-8 insertion may be disabled by the TLDIS input. A diagnostic register bit may be set high to force a single bit error continuously in the least significant bit (bit 8) of each of the B2 bytes inserted in the STS-12 stream.

# **Transmit Section Overhead Insertion**

Section overhead is inserted into the transmit signal by the Transmit Section Overhead Processor, (TSOP) which is located in the PM5301 SSTX. The Transmit Section Overhead Processor inserts the section overhead into the transmit SONET

#### ADVANCE INFORMATION

#### SONET STS-12 LINE INTERFACE MODULE

The Transmit Section Overhead Processor accepts an unscrambled SONET data stream in byte serial format. It optionally inserts the data communication channel, the order wire channel, and the user channel into the section overhead of the unscrambled data stream. These section overhead channels are separately fed to the TSOP as bit serial inputs (TSDL, TSOW, TSUC). The Transmit Section Overhead Processor provides the bit serial clock for each section overhead channel (TSDLCLK, TSOWCLK, TSUCCLK). Line alarm indication signal may optionally be inserted into the data stream under the control of an external input (TLAIS), or a microprocessor writeable register.

The section BIP-8 error detection code is calculated by the TSOP and is optionally inserted into the section overhead of the SONET data stream. Framing and identity bytes are also optionally inserted. Finally, the complete SONET data stream is optionally scrambled and output by the Transmit Section Overhead Processor in byte serial format on outputs TSC\_POUT[7:0].

The Transmit Section Overhead Processor operates with the downstream parallel-to-serial converter that accepts the SONET data stream in byte serial format and serializes it at the STS-12 line rate. The TSOP accepts data and appropriate clock and frame alignment indication signals supplied by the upstream line overhead processor.

# Transmit Section HDLC Transmitter

The HDLC Transmitter is connected to the transmit section data communications channel. The HDLC Transmitter is a microprocessor peripheral used to transmit LAPD/HDLC frames. It performs all of the data serialization, CRC generation, zero-bit stuffing, as well as flag, idle, and abort sequence insertion. Transmit data is provided on an interrupt-driven basis by writing to a double-buffered transmit data register. Upon completion of the frames, a CRC-CCITT frame check sequence is transmitted, followed by idle flag sequences. If the transmit data register under flows, an abort sequence is automatically transmitted.

When enabled, the HDLC Transmitter continuously transmits the flag (01111110). Data to be transmitted is written into the Transmit Data Register. After the parallel-to-serial conversion of each data byte, (TINT) goes high to signal the microprocessor to write the next byte into the Transmit Data Register. After writing the last data frame byte, the EOM bit in the HDLC Transmitter Control Register must be set to transmit the CRC word (if CRC insertion bit is high), or to transmit a flag (if the CRC insertion bit is low). The HDLC Transmitter then returns transmitting flag characters.

An underrun situation can occur if data is not written to the HDLC Transmitter Transmit Data Register before the previous byte has been shifted out. In this case, the UDR bit in the Status Register is set to 1, TUDR is asserted, and an abort sequence is transmitted. An abort sequence can also be continuously transmitted by setting the ABT bit in the HDLC Transmitter Control Register. To free up CPU time

# PM5712 SLIM-12

#### ADVANCE INFORMATION

SONET STS-12 LINE INTERFACE MODULE

and avoid underruns, an external DMA controller may be used to transfer data from external memory to the HDLC Transmitter.

When the HDLC Transmitter is disabled, the external serial TSDL input is inserted in the section data communication channel. TSDL is sampled on the rising edge of TSDLCLK.

# Parallel-To-Serial Conversion

The parallel-to-serial (8:1) multiplexor accepts the byte-wide transmit data at 77.76 Mbyte/s from the Transmit Section Overhead processor, and transmits a single 622.08 Mbit/s data stream at the balanced ECL outputs, TSD+/-. It is implemented with a GaAs integrated circuit which has ECL compatible inputs and outputs. CMOS to ECL level translators interface the up stream circuits with this IC.

The parallel data is clocked into the converter by the 77.76 MHz parallel output clock from the section overhead insertion block. The 622.08 MHz clock from the Transmit Clock Generator is divided by 8 to create a clock that is used to synchronize the input data to the internal timing of the multiplexor.

The parallel output clock loads the data into a buffer register, then the internal 77.76 MHz clock transfers the data from the buffer into another register. A transfer verification circuit monitors the two registers for discrepancies caused by setup and hold violations during the transfer. If there are discrepancies, the internal 77.76 MHz clock will invert at the beginning of the next frame, in order to correct the phase relationship between it and up stream 77.76 MHz clock. This corrective action will provide a phase difference between the two clocks that is sufficiently large to prevent further corrections.

The parallel data from the second register is then clocked into a parallel in, serial out shift register by the internal 77.76 MHz clock. The output data at the balanced ECL outputs, TSD+/- is updated by the falling edge of the 622 MHz clock provided at the balanced ECL outputs, TSCLK+/-. This clock is driven from the output of the Transmit Clock Generator.

# **Transmit Clock Generation**

The 622.08 MHz transmit clock is generated by a VCO which is phase locked to the reference input, REF. The frequency of this input must be 19.44 MHZ  $\pm$  20 ppm. and must have phase noise of less than 0.01 UI pp in a 12 KHz to 2.5 MHz pass band.

The phase locked loop is implemented with a GaAs circuit which is similar to the receive clock regenerator. It aligns the low to high transitions of a 19.44 MHz signal, derived by dividing the transmit clock by 32, to those of the reference input REF. The transmit clock generator drives the transmit parallel to serial converter's

ADVANCE INFORMATION

SONET STS-12 LINE INTERFACE MODULE

PM5712 SLIM-12

The phase locked loop is implemented with a GaAs circuit which is similar to the receive clock regenerator. It aligns the low to high transitions of a 19.44 MHz signal, derived by dividing the transmit clock by 32, to those of the reference input REF. The transmit clock generator drives the transmit parallel to serial converter's 622.08 MHz clock input. It also provides the 77.76 MHz THCLK for the transmit multiplexor and overhead processors.

# Microprocessor Interface

The Microprocessor Interface Block provides the logic required to interface the normal mode and test mode registers within the SLIM-12 to a generic microprocessor bus. The normal mode registers are used during normal operation to configure and monitor the SLIM-12 and the test mode registers are used to enhance the testability of the SLIM-12 during production. The register set is accessed as shown in the following Register Map tables.

SONET STS-12 LINE INTERFACE MODULE

# SECTION REGISTER MAP (SCSB = Low)

| A[4:0]  | Register                               |  |

|---------|----------------------------------------|--|

| 00H     | RSOP Control                           |  |

| 01H     | RSOP Interrupt Status                  |  |

| 02H     | RSOP Lower Error Count                 |  |

| 03H     | RSOP Upper Error Count                 |  |

| 04H     | HDLC Receiver Control                  |  |

| 05H     | HDLC Receiver Interrupt Status/Control |  |

| 06H     | HDLC Receiver Status                   |  |

| 07H     | HDLC Receiver Receive Data             |  |

| 08H     | TSOP Control                           |  |

| 09H     | TSOP Diagnostic                        |  |

| 0AH-0BH | TSOP Reserved                          |  |

| 0CH     | HDLC Transmitter Control               |  |

| 0DH     | HDLC Transmitter Status                |  |

| 0EH     | HDLC Transmitter Transmit Data         |  |

| 0FH     | HDLC Transmitter Reserved              |  |

| 10H     | Reserved                               |  |

| 11H-1FH | Unused                                 |  |

SONET STS-12 LINE INTERFACE MODULE

# LINE REGISTER MAP (LCSB = Low)

| A[4:0]    | Register                  |  |

|-----------|---------------------------|--|

| 00H       | Master Configuration      |  |

| 01H       | Master Interrupt Enable   |  |

| 02H       | Master Interrupt Status   |  |

| 03H       | Master Reset and Identity |  |

| 04H       | TLOP Control              |  |

| 05H       | TLOP Diagnostic           |  |

| 06H - 07H | Reserved                  |  |

| 08H       | RLOP Control/Status       |  |

| 09H       | RLOP Interrupt            |  |

| 0AH       | Line BIP-8 Error Count #1 |  |

| 0BH       | Line BIP-8 Error Count #2 |  |