# 100MSPS 12-Bit Track and Hold Amplifier

**AL1210**

### **FEATURES**

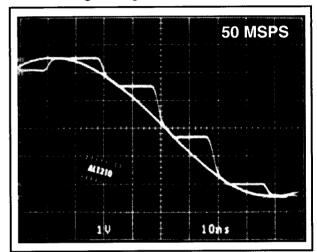

- 100MSPS Sampling Rate (8-Bit)

- 50MSPS Sampling Rate (12-Bit)

- 5ns Acquisition Time (8-Bit)

- 4ns Output Settling Time (8-Bit)

- 0.018% Nonlinearity

- 5µV/°C Hold Offset

- 1ps Aperture Jitter

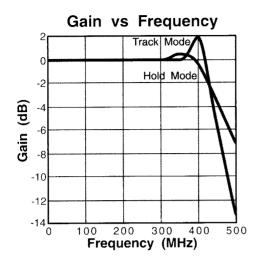

- 400MHz Small Signal Bandwidth

- Low Power (400mW Max.)

- Small Footprint Package (SOIC)

#### **GENERAL DESCRIPTION**

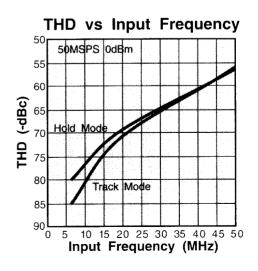

The AL1210 is an extremely fast and accurate monolithic track and hold amplifier. Even at input frequencies of up to **20MHz**, and sampling rates of **50MSPS**, its outstanding performance allows full 12-bit linearity to be maintained. Under these extremely fast conditions, the **TOTAL** harmonic distortion introduced by the AL1210 is still only **-70dBc**.

Its primary application is as a track and hold with the new generation high speed flash A/D converters. By using the AL1210 with these converters, it is now possible to obtain meaningful 10-bit performance at input frequencies of up to 40MHz and sampling rates of up to 75MSPS. If the AL1210 were not used, the meaningful resolution would drop down to 6 bits or less. At 50MHz the TOTAL harmonic distortion is only -59dBc.

The noise that a track and hold circuit generates must be significantly below the resolution or noise of the A/D converter in order not to limit the dynamic range of the system. The causes of noise in a track and hold are quite complex and come from several sources. In the AL1210 these noise sources are kept very low, for example, an aperture jitter of only 1ps and a total output noise of only  $50\mu V$ .

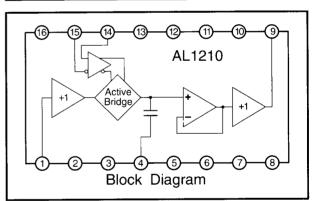

To obtain this remarkable performance, **innovative circuit design** and careful layout have been used. It is fabricated in a very fast complementary bipolar process. The AL1210 is packaged in a 16-pin SOIC in order to keep the pin inductances and capacitances to a minimum.

### **APPLICATIONS**

- Flash A/D Driving

- CCD Imaging Systems

- Radar and IF Processors

- Data Acquisition Systems

- Deglitching

Acculin supplies information in the belief that it is accurate, but is not responsible for its use; nor for any infringements of patents or other rights of third parties which may result from its use. If it is found not to be accurate, please inform Acculin as soon as possible. No license is granted by implication or otherwise under any patent rights of Acculin.

### Acculin Inc.

214 North Main Street, Natick Massachusetts 01760 U.S.A.

Tel: (508) 650-1012 Fax: (508) 650-1457

# Electrical Characteristics (Vcc=5V, VEE=-5V, RL=1k, CL=20pF, unless otherwise specified)

|                                            | _          |              |               | <del></del> |                |            |          |                  |       | 1     | . T 10101        |       |

|--------------------------------------------|------------|--------------|---------------|-------------|----------------|------------|----------|------------------|-------|-------|------------------|-------|

| Parameter                                  | Units      | Temp         | Test<br>Level | Min         | AL1210S<br>Typ | Max        | Min      | AL1210A<br>Typ   | Max   | Min   | AL1210J<br>Typ   | Max   |

| DC ACCURACY                                |            |              |               |             |                |            |          |                  |       |       |                  |       |

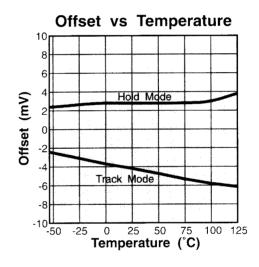

| Track Offset                               | mV         | +25°C        | I             | -15         | -8             | 0          | -15      | -8               | 0     | -15   | -8               | 0     |

|                                            | mV         | Full         | VI            | -20         |                | 5          | -20      |                  | 5     | -20   |                  | 5     |

| Track temperature coefficient <sup>1</sup> | μV/°C      | Full         | IV            |             | 20             | 40         |          | 20               | 40    |       | 20               | 40    |

| Hold temperature coefficient 1,2           | μV/°C      | Full         | IV            |             | 2              | 20         |          | 2                | 20    |       | 2                | 20    |

| Track Gain (no load)                       | 'v/v       | +25℃         | I             | 0.990       | 0.993          | 1.000      | 0.990    | 0.993            | 1.000 | 0.990 | 0.993            | 1.000 |

|                                            | V/V        | Full         | VI            | 0.980       | 0.990          | 1.000      | 0.980    | 0.990            | 1.000 | 0.980 | 0.990            | 1.000 |

| temperature coefficient <sup>1</sup>       | ppm/°C     | Full         | IV            |             | 20             | 30         |          | 20               | 30    |       | 20               | 30    |

| Hold Gain (no load) <sup>2</sup>           | V/V        | +25℃         | I             | 0.990       | 0.995          | 1.000      | 0.990    | 0.995            | 1.000 | 0.990 | 0.995            | 1.000 |

|                                            | V/V        | Full         | VI I          | 0.990       | 0.995          | 1.000      | 0.990    | 0.995            | 1.000 | 0.990 | 0.995            | 1.000 |

| temperature coefficient <sup>1</sup>       | ppm/°C     | Full         | IV            |             | 15             | 30         |          | 15               | 30    |       | 15               | 30    |

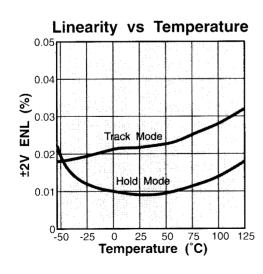

| Track Nonlinearity <sup>3</sup>            | %          | +25℃         | I             |             | 0.018          | 0.030      |          | 0.018            | 0.030 |       | 0.018            | 0.030 |

|                                            | %          | Full         | VI            |             |                | 0.035      |          |                  | 0.030 |       |                  | 0.030 |

| Hold Nonlinearity <sup>2,3</sup>           | %          | +25°C        | I             |             | 0.015          | 0.030      |          | 0.015            | 0.030 |       | 0.015            | 0.030 |

|                                            | %          | Full         | VI            |             |                | 0.030      | ŀ        |                  | 0.030 |       |                  | 0.030 |

| Output resistance <sup>4</sup>             | Ω          | +25°C        | I             | 6           | 8              | 10         | 6        | 8                | 10    | 6     | 8                | 10    |

|                                            | Ω          | Full         | IV            | 6           |                | 11         | 6        |                  | 11    | 6     |                  | 11    |

| Output drive capability                    | mA         | +25°C        | I             | 20          |                | 45         | 20       |                  | 45    | 20    |                  | 45    |

|                                            | mA         | Full         | VI            | 15          |                | 50         | 15       |                  | 50    | 15    |                  | 50    |

| without short circuit protection           | mA         | Full         | IV            | 50          |                |            | 50       |                  |       | 50    |                  |       |

| PSRR                                       | mV/V       | +25℃         | I             |             |                | 4          |          |                  | 4     | 1     |                  | 4     |

|                                            | mV/V       | Full         | VI            |             |                | 6          |          |                  | 6     |       |                  | 6     |

| ANALOG INPUT.                              |            |              |               |             |                |            |          |                  |       |       |                  |       |

| Voltage range <sup>5</sup>                 | V          | Full         | IV            | -2.5        |                | 2.5        | -2.6     |                  | 2.6   | -2.7  |                  | 2.7   |

| Bias current                               | μΑ         | +25℃         | I             | -65         | -15            | 10         | -65      | -15              | 10    | -65   | -15              | 10    |

|                                            | μA         | Full         | VI            | -90         |                | 20         | -75      |                  | 15    | -65   |                  | 15    |

| Resistance                                 | kΩ         | +25°C        | 1             | 170         | 300            |            | 170      | 300              |       | 170   | 300              |       |

|                                            | kΩ         | Full         | VI            | 110         |                |            | 140      |                  |       | 170   |                  |       |

| Capacitance                                | pF         | Full         | IV            |             |                | 2          | <u> </u> |                  | 2     |       |                  | 2     |

| DIGITAL INPUTS                             |            |              |               |             |                |            |          |                  |       |       |                  |       |

| Voltage range                              | v          | Full         | IV            | -2.9        |                | 1.9        | -3.0     |                  | 2.0   | -3.1  |                  | 2.1   |

| differential                               | V          | Full         | IV            | 0.4         |                | 5          | 0.4      |                  | 5     | 0.4   |                  | 5     |

| Bias current high                          | μA         | +25℃         | I             |             | 10             | 25         |          | 10               | 25    |       | 10               | 25    |

|                                            | μA         | Full         | IV            |             |                | 50         |          |                  | 40    |       |                  | 35    |

| Bias current low                           | μA         | +25℃         | I             | -85         | -40            |            | -85      | -40              |       | -85   | -40              |       |

|                                            | μA         | Full         | IV            | -170        |                |            | -130     |                  |       | -110  |                  |       |

| TRACK MODE DYNAMICS                        |            |              |               |             |                |            |          |                  |       |       |                  |       |

| Bandwidth to output (-3dB)                 | MHz        | +25℃         | IV            | 300         | 400            |            | 300      | 400              |       | 300   | 400              |       |

|                                            | MHz        | Full         | IV            | 300         |                |            | 300      |                  |       | 300   |                  |       |

| Bandwidth to hold cap. (-3dB)              | MHz        | +25℃         | IV            | 350         | 400            |            | 350      | 400              |       | 350   | 400              |       |

|                                            | MHz        | Full         | IV            | 350         |                |            | 350      |                  |       | 350   |                  |       |

| Total noise at output                      |            | +25°C        | IV            |             | 45             | 55         |          | 45               | 55    |       | 45               | 55    |

|                                            | μVrms      | Full         | IV            |             |                | 65         |          |                  | 65    |       |                  | 65    |

| Output noise density                       | nV∧Hz      | +25°C        | IV            |             | 5              | 5.5        |          | 5                | 5.5   |       | 5                | 5.5   |

|                                            | nV√Hz      | Full         | IV            |             |                | 6.5        |          |                  | 6     |       |                  | 6     |

| Input current noise                        | pA√Hz      | +25°C        | IV            |             | 3.5            | 5.5        |          | 3.5              | 5.5   |       | 3.5              | 5.5   |

|                                            | pA√Hz      |              | IV            |             |                | 7          |          |                  | 6.5   |       | =00              | 6     |

| Capacitor slew rate                        | V/µs       | +25°C        | l V           |             | 700            |            |          | 700              |       |       | 700              |       |

|                                            | V/µs       | Full         | IV            | 550         |                |            | 550      |                  |       | 550   | 550              |       |

| Output slew rate                           | V/µs       | +25°C        | V             |             | 550            |            | 47.5     | 550              |       | 175   | 550              |       |

| T-4-1 Ham and District                     | V/µs       | Full         | IV            | 475         |                |            | 475      |                  |       | 475   |                  |       |

| Total Harmonic Distortion                  | 125        | . 2500       | ,,,           |             | 7.4            |            |          | 7.4              |       |       | -74              |       |

| 20MHz 0.5Vpp                               | dBc        | +25°C        | IV            |             | -74            | <i>E</i> 0 |          | -74              | ۷0    |       | -/4              | 60    |

| 50MH- 0.5V                                 | dBc        | Full<br>+25℃ | IV<br>V       |             | -54            | -68        |          | -54              | -68   |       | -54              | -68   |

| 50MHz 0.5Vpp                               | dBc<br>dBc | Full         | IV            |             | -34            | -48        |          | -54              | -48   |       | -J <del>-4</del> | -48   |

| PSRR to hold cap. (20MHz)                  | dB         | +25°C        | V             |             | -34            | -40        |          | -34              | -40   |       | -34              | +0    |

| r SKK to floid cap. (20Minz)               | dB<br>dB   | Full         | IV            |             | -34            | -32        |          | -J <del>-1</del> | -32   |       | -94              | -32   |

| PSRR to output (20MHz)                     | dB         | +25°C        | V             |             | -26            | -54        |          | -26              | -54   |       | -26              | -34   |

| 1 SKK to output (ZOMITZ)                   | dB         | Full         | IV            |             | -20            | -24        |          | -20              | -24   |       | 20               | -24   |

|                                            | uD         | i un         | 'V            | 1           |                | -24        | 1        |                  | -24   | 1     |                  | -24   |

## **AL1210**

|                                            |             |              | 1        |       |            |       |       |        | -     |          |         |       |

|--------------------------------------------|-------------|--------------|----------|-------|------------|-------|-------|--------|-------|----------|---------|-------|

|                                            |             |              | Test     |       | AL12108    |       |       | L1210A |       |          | AL1210, |       |

| Parameter                                  | Units       | Temp         | Level    | Min   | Тур        | Max   | Min   | Тур    | Max   | Min      | Тур     | Max   |

| HOLD MODE DYNAMICS                         |             |              |          |       |            |       |       |        |       |          |         |       |

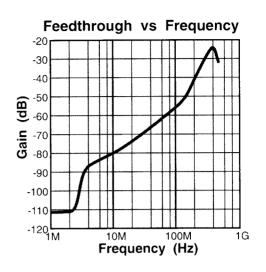

| Feedthrough (10MHz, 2Vpp)                  | dB          | +25°C        | IV       |       | -80        | -75   |       | -80    | -75   |          | -80     | -75   |

| -                                          | dB          | Full         | IV       |       |            | -75   |       |        | -75   |          |         | -75   |

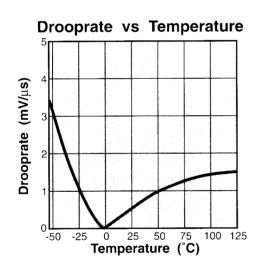

| Droop rate <sup>6</sup>                    | mV/μs       | +25°C        | I        |       | 2.5        | 5     |       | 2.5    | 5     |          | 2.5     | 5     |

| ·                                          | mV/μs       | Full         | VI       |       |            | 15    |       |        | 10    |          |         | 15    |

| time constant <sup>7</sup>                 | ms          | +25°C        | V        |       | 0.5        | 2     |       | 0.5    | 2     | 0.5      | 2       |       |

|                                            | ms          | Full         | IV       | 0.2   |            |       | 0.5   |        |       | 0.5      |         |       |

| Hold noise <sup>8</sup>                    | mV√s        | +25°C        | V        |       | 50         |       | ]     | 50     |       |          | 50      |       |

|                                            | mV√s        | Full         | IV       |       |            | 150   |       |        | 150   |          |         | 150   |

| PSRR (20MHz)                               | dB          | Full         | IV       | 18    | 21         |       | 18    | 21     |       | 18       | 21      |       |

| TRACK TO HOLD                              |             |              |          |       |            |       |       |        |       |          |         |       |

| SWITCHING                                  |             |              |          |       |            |       |       |        |       |          |         |       |

| Effective aperture delay <sup>9</sup>      | ps          | Full         | IV       | -500  | -250       | 0     | -500  | -250   | 0     | -500     | -250    | 0     |

| Aperture jitter                            | ps rms      | Full         | IV       |       | 1          | 2     |       | 1      | 2     |          | 1       | 2     |

| Pedestal offset                            | l mV        | +25°C        | l ı l    |       | 5          | 15    | ]     | 5      | 15    |          | 5       | 15    |

| 10000000                                   | mV          | Full         | VI       |       |            | 20    |       |        | 20    |          |         | 20    |

| temperature coefficient <sup>1</sup>       | μV/°C       | Full         | IV       |       | 20         | 40    |       | 20     | 40    |          | 20      | 40    |

| sensitivity to supply voltage              | mV/V        | +25°C        | IV       |       | 0.5        | 1     |       | 0.5    | 1     |          | 0.5     | 1     |

| sensativity to supply vollage              | mV/V        | Full         | IV       |       |            | 2     |       |        | 2     |          |         | 2     |

| Transient amplitude peak-peak 10           | mV          | +25°C        | IV       |       | 20         |       |       | 20     |       |          | 20      |       |

| Transient ampirtude peak peak              | mV          | Full         | IV       |       |            | 50    |       |        | 50    |          |         | 50    |

| Glitch impulse 10                          | pVs         | +25°C        | IV       |       | 20         |       |       | 20     |       |          | 20      |       |

| Gitten impuise                             | pVs         | Full         | IV       |       | 20         | 50    |       |        | 50    |          |         | 50    |

| Settling time to 4mV <sup>11</sup>         | ns          | +25°℃        | IV       |       | 4          |       |       | 4      |       |          | 4       |       |

| Setting thic to 4m v                       | ns          | Full         | IV       |       | •          | 6     |       |        | 6     |          | •       | 6     |

| Settling time to 0.5mV <sup>11</sup>       | ns          | +25°C        | IV       |       | 8          | Ü     |       | 8      | Ü     |          | 8       |       |

| Settling time to 0.5iii v                  | ns          | Full         | IV       |       | J          | 12    |       | v      | 12    |          |         | 12    |

| Total sampled noise (50MSPS) <sup>12</sup> | μV          | +25°C        | IV       |       | 50         | 12    |       | 50     | 12    |          | 50      |       |

| Total sampled hoise (30,4131 3)            | μV          | Full         | IV       |       | 50         | 100   |       |        | 100   |          | • •     | 100   |

| HOLD TO TRACK                              |             |              |          |       |            |       |       |        |       |          |         |       |

| SWITCHING                                  |             |              |          |       |            |       |       |        |       |          |         |       |

| Acquisition time 11,13                     |             |              |          |       |            |       |       |        |       |          |         |       |

| 1% 2V step                                 | ns          | +25°C        | IV       |       | 6          | 8     |       | 6      | 8     |          | 6       | 8     |

| 1 /0 2 <b>v</b> step                       | ns          | Full         | IV       |       | V          | Ü     |       |        |       |          |         |       |

| 0.1% 2V step                               | ns          | +25°C        | IV       |       | 7.5        | 9     |       | 7.5    | 9     | <u> </u> | 7.5     | 9     |

| 0.1 % 2 v step                             | ns          | Full         | IV       |       | 7.10       |       |       |        | -     |          |         |       |

| 0.01% 2V step                              | ns          | +25℃         | IV       |       | 12         | 14    |       | 12     | 14    |          | 12      | 14    |

| 0.01 % 2 v step                            | ns          | Full         | IV       |       | 12         | • •   | 1     |        | • •   |          |         |       |

| 1% 200mV step                              | ns          | +25℃         | IV       |       | 4          | 6     |       | 4      | 6     |          | 4       | 6     |

| 1 % 200m v step                            | ns          | Full         | IV       |       | .,         | ·     |       | •      | Ü     |          |         | ~     |

| 0.1% 200mV step                            | ns          | +25°C        | IV       |       | 6.5        | 7     |       | 6.5    | 7     |          | 6.5     | 7     |

| 0.1% 200mv step                            | ns          | Full         | IV       |       | 0.5        | ,     |       | 0.5    | ,     |          | 0.5     | ,     |

| Output overshoot 2V step                   | mV          | +25°C        |          |       | 10         | 20    |       | 10     | 20    |          | 10      | 20    |

|                                            |             |              | <u> </u> |       |            |       |       |        |       |          |         |       |

| THROUGHPUT DISTORTION                      | ļ           |              | 1        |       |            |       |       |        |       |          |         |       |

| Total harmonics 0dBm, 50MSPS <sup>14</sup> |             | P 11         | VI       |       | -70        | -64   |       | -70    | -64   |          | -70     | -64   |

| 18.75MHz<br>43.75MHz <sup>15</sup>         | dBc<br>dBc  | Full<br>Full | VI       |       | -70<br>-59 | -53   |       | -59    | -53   |          | -59     | -53   |

| POWER REQUIREMENTS                         |             | <u> </u>     |          |       |            |       |       |        |       |          |         |       |

| Total supply current                       | mA          | Full         | VI       | 30    | 36         | 40    | 30    | 36     | 40    | 30       | 36      | 40    |

| Supply voltages                            |             |              |          | ~~~   |            | -     |       | -      |       |          |         |       |

| positive                                   | l v         | Full         | V        | 4.75  | 5          | 5.25  | 4.75  | 5      | 5.25  | 4.75     | 5       | 5.25  |

| negative                                   | v           | Full         | v        | -5.25 | -5         | -4.75 | -5.25 | -5     | -4.75 | -5.25    | -5      | -4.75 |

| Power dissipation                          | w           | Full         | VΙ       | 0.3   | 0.36       | 0.4   | 0.3   | 0.36   | 0.4   | 0.3      | 0.36    | 0.4   |

| Tower dissipation                          | <del></del> |              | <u> </u> |       |            |       |       |        |       | l        |         |       |

#### NOTES

- End point average

Hold mode values include track mode and pedestal errors

End point over ±2V

- Measured at 5mA output current

Voltage range which the output is guaranteed to cover

Rate of voltage change in hold mode

Decay time constant of the voltage on the hold capacitor

- 8 Noise accumulated during hold, e.g. at 50mV√s, holding for 10ns will

- accumulate a 5 µ Vrms error

The delay in the analog signal path is greater than the delay in the digital signal path; therefore the effective aperture delay is negative

- 10 Excluding pedestal11 Specified from the time of the digital command

- 12 Includes all sources of noise above 10kHz in the track and hold, driven from a

- 50-ohm source, excluding aperture jitter

13 Time for which the track and hold must be kept in track mode to acquire to within the specified precision

- 14 Includes all sources of distortion in the track and hold, measured by FFT analysis

- 15 This signal is under sampled, and therefore aliased, which does not present a problem in specifying the distortion

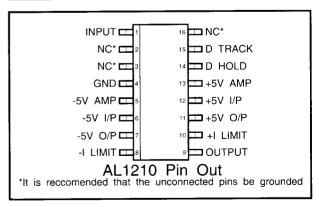

| Pin Name | Pin No. | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUT    | 1       | Analog input to the track and hold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NC       | 2,3,16  | These pins have no internal connection, but do perform an important function. They should be grounded to obtain good isolation between the adjacent pins in the lead frame.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GND      | 4       | Ground connection for the hold capacitor. This should be connected to a ground plane with the minimum inductance possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| –5V AMP  | 5       | Negative power supply for the amplifier following the hold capacitor. This should be connected to -5V. In order to achieve good isolation from the digital signals and the analog input, it may be desirable to isolate this supply from the input supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| –5V I/P  | 6       | Negative power supply for the input stages of the track and hold should be connected to -5V. This supply is connected to the internal substrate of the circuit, and therefore no pin should be significantly more negative than this one. Since the current drawn from this supply charges the storage capacitor, it has substantial transients during high slew rates, such as acquisition. It is important for optimum operation that these currents do not induce high speed voltage changes, and this pin therefore should be well decoupled to ground. Series resistance on the power supply side of the decoupling capacitor also can be used to prevent any remaining transients from disturbing the other supplies. |

| –5V O/P  | 7       | Negative power supply for the output devices. The nature of the current drawn by this pin is dependent on the load presented to the track and hold output. If the -I LIMIT pin is well decoupled, then the currents drawn will not be subject to large high speed transients. However if a 50-ohm load is driven, then the current drawn by this pin may be correspondingly large.                                                                                                                                                                                                                                                                                                                                          |

| –I LIMIT |         | In normal operation this pin should be decoupled to ground, and will supply transient currents required by the load. The internal output current limit is between this pin and the -5V O/P pin, and therefore these transients will not cause current limiting. If this pin is left unconnected, the current limit will be fast acting, and the -5V O/P should be well decoupled. A large transient of output current will cause current limiting, and consequent serious degradation of output settling time. If current limiting is not required, this pin may be connected to -5V O/P and the pair well decoupled. An output short circuit under these conditions will destroy the device.                               |

| OUTPUT   | 9       | Output of the track and hold. This pin is capable of directly driving highly capacitive loads, such as flash A/D converters, or 50-ohm line. If it is required to drive more than 20mA continuously, the current limit should be disabled. No more than 50mA should be drawn.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| +I LIMIT | 10      | See - I LIMIT, except with respect to +5V O/P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| +5V O/P  | 11      | See -5V O/P, except positive supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| +5V I/P  | 12      | See -5V I/P, except positive supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| +5V AMP  | 13      | See -5V AMP, except positive supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DHOLD    | 14      | One of the digital input pins. It is recommended that these be driven by high speed ECL in a complementary fashion. Particular care should be taken in deriving these signals to keep the edge position jitter to a minimum. This track and hold has very good aperture jitter performance, but can be no better than the jitter on signals presented to the device. High slew rate and fast settling also are desirable attributes for these signals.                                                                                                                                                                                                                                                                      |

| DTRACK   | 15      | Complementary signal to DHOLD. When DTRACK is higher than DHOLD, the device is in track mode; and when lower, it is in hold mode. Although for optimum performance, high speed ECL is recommended; it is possible to use other levels, subject to the limitations of the common mode and differential voltages in the                                                                                                                                                                                                                                                                                                                                                                                                       |

### RECOMMENDED OPERATING CONDITIONS

specification.

| Supply voltages     |               | ± 5V          |

|---------------------|---------------|---------------|

| Ambient temperature | range AL1210S | -55 to +125°C |

| <u>-</u>            | AL1210A       | -25 to +85°C  |

|                     | AL1210J       | 0 to +70°C    |

| Analog input range  |               | $\pm 2V$      |

| Digital inputs      |               | Balanced ECL  |

#### EXPLANATION OF TEST LEVELS

- I 100% production tested

- II 100% production tested at +25°C; sample tested at temperature extremes

- III Sample tested only

- IV Parameter is guaranteed by design and characterization

- V Parameter is a typical value only VI 100% production tested at +25°C; military parts 100% tested at temperature extremes

#### ABSOLUTE MAXIMUM RATINGS -0.5V (+5V I/P) - (-5V I/P) 12.5V INPUT 3V -3V -5V < (D TRACK) - (D HOLD) < 5V < (+5V I/P) + 0.5V(-5V I/P) - 0.5V <(Any Pin) -55°C Ambient temperature 125°C 150°C -65°C Storage temperature < Lead temperature (10s) 300°C 50mA < Continuous output current < -50mA Operation of the device beyond these limits may impair performance permanently

### TYPICAL PERFORMANCE CHARACTERISTICS

### **GLOSSARY OF TRACK AND HOLD TERMINOLOGY**

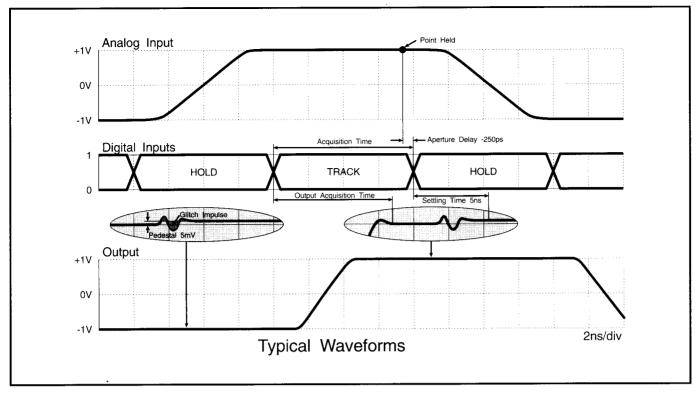

**Acquisition Time** is the time for which the device has to be switched into track mode in order to acquire the new voltage within a specified percentage of the specified change in voltage.

**Aperture Delay** is the time delay between the hold command input and the point at which the input is sampled. This can be either positive or negative, depending on the relative delays in the analog and digital signal paths. The exact value is rarely important, but matching between multiple track and holds in a system can be. In some vendors' specifications this figure is excluded from settling time, in which case its magnitude does become significant.

**Aperture Jitter** is the random variation in aperture delay from sample to sample, expressed as an rms time. Aperture jitter will cause an increase in noise in the presence of high slew rate input waveforms. The extra voltage noise on a sample will be the product of the input slew rate and the aperture jitter.

**Delays** are included in the acquisition and settling times, and therefore are not specified.

**Droop Rate** is the rate at which the output voltage changes while the device is in hold mode. For short hold times this is not significant, but over long hold intervals it can cause errors. The estimation of these errors is discussed elsewhere in this data sheet.

**Feedthrough** is the effect that a change in the analog input voltage has upon the output voltage when the device is in hold mode. Feedthrough is usually worse at higher frequencies.

**Output Acquisition Time** is the time from when the device is switched into track mode, to when the output has settled to within a specified percentage of the specified change in voltage. Some vendors' specifications call this the acquisition time.

**Output Settling Time** is the time from when the device is switched into hold mode, to when the output has settled to within a specified voltage of its final value.

**Pedestal Offset** is the voltage step on the output as the device switches into hold mode, and may be treated as an offset. If it is nonlinear with respect to the input voltage or the slew rate, it will introduce distortion. The pedestal offset of the AL1210 is very linear and stable, and the linearity specification includes pedestal error.

**Throughput Cycle Time** is the total throughput capability of the device while the output is settling to a given level of accuracy.

**Track to Hold Transient** is the glitch on the output voltage when the device is switched into hold mode. This is specified in four ways: 1) peak-to-peak magnitude; 2) glitch impulse, which is the area contained within the glitch in Volt-seconds; 3) pedestal offset, which is where it finally settles; and 4) output settling time.

### GENERAL DISCUSSION OF TRACK AND HOLD PERFORMANCE

### **Noise Considerations**

There are various sources of noise present in any electronic circuit. The AL1210 has been characterized for its noise performance, but many contributions to noise are dependent on the circuit in which it is used. The various sources of noise are uncorrelated, and the total voltage noise is therefore the rms sum of the noise contributions.

Low drive impedance is desirable to prevent input current noise from developing extra voltage noise at the input. The contribution to noise will be the product of the input current noise and the driving impedance. The resistive part of the source impedance also will generate thermal noise.

Any noise present at the input obviously is included in the sampled signal, and therefore should be minimized. Attention should be given to the bandwidth of the noise source. If the noise density on the input is sufficiently low, then the high bandwidth of the AL1210 will not present a problem; on the other hand, if reduction of amplitude response variation with frequency is important, it will be undesirable to limit the bandwidth.

Hold noise is a result of random charges accumulating on the hold capacitor. Voltage error will accumulate in proportion to the square root of the hold time, and normally will not be significant, although it is specified for the AL1210.

Noise on the power supplies will couple into the signal path, reduced by the power supply rejection ratio. This noise can be minimized by effective decoupling of the supplies at the pins.

Aperture jitter will cause an increase in noise in the presence of high slew rate input waveforms. The extra voltage noise on a sample will be the product of the input slew rate and the aperture jitter.

Aperture jitter of 1ps rms is difficult to maintain. The use of balanced high-speed low-impedance logic helps to minimize jitter degradation. Single-ended TTL driving, although convenient, will degrade this aspect of performance.

## **Nonlinearity Considerations**

Nonlinearity can arise in a variety of ways and is normally measured either as a proportion of the voltage range used (the usual low frequency measurement), or as the harmonic distortion introduced to a sine wave (the usual high frequency measurement). Some caution should be taken in comparing harmonic distortion specifications. Often harmonic distortion will be specified as the ratio of the largest harmonic to the fundamental. Furthermore with track and hold circuits, it is commonly specified in track mode only. While these are useful specifications other factors are significant, in particular:

1) The total harmonic distortion is often of interest, and is sometimes specified as a signal-to-noise ratio, which includes the noise contribution. In systems where data from the converter is subject to digital signal processing, it is necessary to know the contributions to error separately. Distortion and noise integrate differently because distortion is correlated to the signal whereas noise is uncorrelated.

2) A distortion specified in track mode does not include errors introduced by the sampling process. The hold-to-track and track-to-hold settling times place limits on the distortion, but the figures are not readily convertible.

There is a nonlinear DC transfer characteristic imposed upon the signal which causes distortion of the signal independent of frequency. This nonlinearity is usually specified as a percentage of the voltage range over which it is measured, either compared to a straight line joining the endpoints (endpoint nonlinearity or ENL), or to a best-fit straight line. The AL1210 specification is endpoint nonlinearity.

There is a dynamic contribution to nonlinearity during slew. While the signal is slewing, the output of any circuit will lag behind the change in the input. As the slewrate of the signal changes, this lag changes; and there is some nonlinearity in the change. Typically in flash A/D converters, this nonlinearity results in increased distortion as the input slew rate increases. The AL1210 is of great value in alleviating this problem. The level of dynamic distortion in the AL1210 is much lower than in flash A/D converters. The output of the AL1210 is not slewing when the flash A/D is sampling the signal, which results in the full accuracy of the converter being realized, even at high input frequencies. Thus the harmonic distortion performance of the system is improved dramatically.

Further dynamic distortion occurs in flash A/D converters because of a variation in aperture time with input voltage. The distortion associated with this aperture time change is removed when the AL1210 is used to drive the A/D. The output of the AL1210 is not slewing at the time the flash converter samples it; therefore the change in aperture time does not result in a voltage error.

The output stage of the AL1210 is capable of driving low impedance loads. While high currents are being drawn from the output, there is an additional contribution to nonlinearity. This does not affect the system performance driving a flash A/D with a high capacitance input. At the time the flash conversion occurs, the voltage on the output of the AL1210 is static, so no capacitive current is drawn. However if a low resistive impedance is presented to the output of the AL1210, the linearity will be reduced. The input resistance of a flash A/D is unlikely to be low enough to cause any significant degradation of linearity.

During hold mode, the leakage current to the hold capacitor will cause the voltage on the capacitor to drift. As a result, an offset will develop during the hold interval prior to a flash A/D sampling the output. If this interval is not fixed, and if the hold interval and the signal are uncorrelated, this offset will manifest itself as noise. If the hold interval and signal are correlated, this offset will manifest itself as distortion. The most probable situation is that the flash A/D converter will sample the output of the track and hold at a fixed time after the signal is acquired. The drift will result in an offset error, which will have a temperature coefficient related to the temperature coefficient of the leakage current. If the leakage current contains a resistive component, the amplitude of the signal will change with hold time, thereby causing a gain error. However if the leakage current is nonlinear with voltage, a distortion will be introduced with hold time. In a flash A/D driving circuit, this distortion is unlikely to be significant.

### **Timing Considerations**

Throughput is the key specification for the performance of a track and hold and is the rate at which the device can sample signals to a given level of accuracy. Unfortunately this is rarely specified, and therefore has to be estimated. The specifications that are given for track and hold devices vary, and the definitions of the same specification figure also vary. The definitions used for the AL1210 are given in the Glossary.

The AL1210 timing specifications are all measured from the time of the digital command, which is when the two input logic levels cross. This results in a relatively simple estimation of cycle time as the sum of the acquisition time to the required accuracy; the output settling time to the required accuracy; and any interval for which the output is to be held stable for the benefit of subsequent circuitry. Some specifications do not measure from the digital command, but add delay specifications and then specify times from when the output begins to change. This is not a very satisfactory specification because "begins to change" is not a well-defined point, and the output will probably have a transient upon it at the time the logic levels on the digital input change. This may be satisfactory if the interval is a pure delay, but this is not the case if the output has a transient at the logic switching time. Few designers will be prepared to sample the output of the track and hold during this interval; and therefore this delay adds to the useful acquisition and output settling times and reduces the total throughput.

Analog delay is the propagation time for a signal from the input to the output. In some specifications this is excluded from settling time figures; if it is included in settling time, it is of little significance. From a designer's viewpoint, the most useful specification is the throughput rate for the required accuracy, which is usually not specified directly in the data sheet. It is a difficult parameter to test in production, and depends to some extent upon the circuit in which it is used. The AL1210 has a specified throughput harmonic distortion (sometimes called hold mode distortion).

### **Sampling Below Nyquist**

The AL1210 is quite capable of sampling signals of higher frequencies than can be resolved by the sampling rate unambiguously, subject to the available bandwidth. However it should be recognized that distortion of the input signal is primarily a result of slew rate: the higher the amplitude of a high frequency sine wave, the higher the distortion. The AL1210 has a distortion specification for a 1Vpp 50MHz input. The effect of aperture jitter at high slew rates also will increase the noise level.

### **Circuit Techniques**

The AL1210 is capable of driving typical capacitive loads with relatively little lengthening of output settling time; however resonant loads can cause more significant settling time increases. The most common way of presenting a resonant load is as a capacitive load at the far end of a length of line. Even a few centimeters of line can be very significant. The AL1210 therefore should be mounted very close to the load it is driving. If this is not possible, then a resistor in series with the output can help to damp the ringing that occurs, and can keep the output settling time reasonably short.

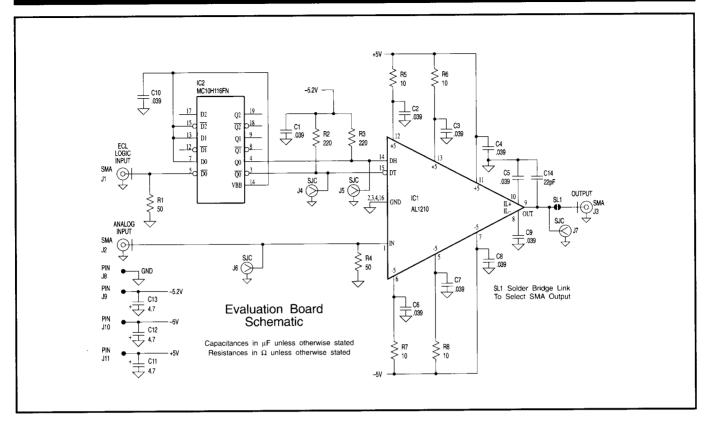

The power supplies of the AL1210 are brought out of the package separately. This minimizes the mutual coupling that would occur as a result of the inductance of the package pin. In order to preserve isolation, the tracks from these pins should be kept separate until they are decoupled to ground, which should be as close as possible to the package. Series resistors in the power supplies, as shown in the evaluation board schematic, can help to preserve this isolation.

The AL1210 contains current limiting circuitry to prevent destruction of the device under short circuit output conditions. Decoupling the -I limit and +I limit pins will allow larger output currents to flow for short periods. Connecting -I limit to -5V O/P and +I limit to +5V O/P will disable completely the current limiting function.

### LAYOUT CONSIDERATIONS

As with any high speed precision circuit, good printed circuit board layout is necessary. A small package and the use of surface mounting help to reduce the parasitic inductances associated with the pins.

The package inductance of pin 4 to ground is already the limiting factor for both acquisition time and output settling time. Therefore pin 4 should be connected directly to an extensive ground plane. Pins 2, 3 and 16 should be grounded; this will minimize capacitive coupling between digital and analog inputs which would otherwise degrade performance.

Ground return paths for the input, digital inputs, output and power supply decoupling should not intersect within the ground plane as this would cause mutual coupling of these signals.

The input and digital control lines should be transmitted via properly terminated transmission lines, such as microstrip or stripline, if they are longer than 20 or 30mm. The output path should either be kept very short or be properly terminated. The part is capable of driving 50-ohm line, although doing so will reduce the linearity. Unterminated line on the output will adversely affect output settling time. The capacitive load presented by typical flash A/D converters does not present a linearity problem, in spite of its very nonlinear nature, because the output voltage is settled at the time the flash converter is fired.

Correct power supply decoupling is very important; typically  $0.01\mu F$  surface-mounted multilayer capacitors should be placed as close as possible to the power supply pins of the AL1210. Further isolation of the supplies may be achieved by the use of small series resistors, as in the evaluation board. These resistors and capacitors prevent the high speed transient currents from the track and hold causing voltage transients on the supplies; and also prevent external high frequency transients from reaching the device supplies. It is important that the supplies are stable and contain no lower frequency transients; therefore sharing a supply with logic is not recommended unless thorough supply filtering is employed.

The use of sockets is not recommended because of the associated increase in stray inductances.

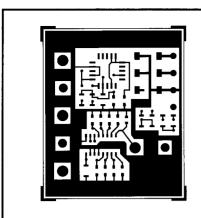

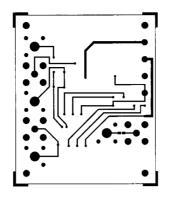

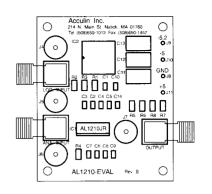

The layout of the evaluation board (AL1210-EVAL) is shown above, and fulfills all of the layout requirements satisfactorily. The schematic of the board is shown above, and illustrates how the part may be used. When the device forms part of a larger circuit, considerable benefit can be gained through the use of a multilayer board. The evaluation board is available to assist the designer in assessing the capabilites of the AL1210 without having to arrange a test fixture.

The evaluation board includes an ECL line receiver (IC2) as a convenience to provide balanced logic to the AL1210; other balanced logic sources may be used. In a larger circuit, it may be preferable to terminate the ECL in 50 ohms to -2V depending upon the logic transmission environment.

**Component Side Metal**

**Back Side Metal Evaluation Board Layout**

**Component Layout**

| ORDERING INFORMATION               |                         |                   |  |  |  |  |  |  |  |  |

|------------------------------------|-------------------------|-------------------|--|--|--|--|--|--|--|--|

| Model                              | Temp Range              | Package           |  |  |  |  |  |  |  |  |

| AL1210JR                           | 0 to +70°C              | 16-pin SOIC       |  |  |  |  |  |  |  |  |

| AL1210AR                           | -25 to +85°C            | 16-pin SOIC       |  |  |  |  |  |  |  |  |

| AL1210SE*                          | -55 to +125°C           | 20-terminal LCC   |  |  |  |  |  |  |  |  |

| AL1210SJ*                          | -55 to 125°C            | 20 J-Lead Ceramic |  |  |  |  |  |  |  |  |

| AL1210-DIE                         | Various                 | Unpackaged        |  |  |  |  |  |  |  |  |

| AL1210-EVAL                        | <b>Evaluation Board</b> | РСВ               |  |  |  |  |  |  |  |  |

| *Contact factory for availability. |                         |                   |  |  |  |  |  |  |  |  |

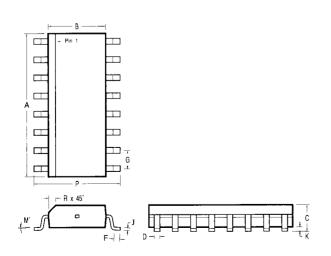

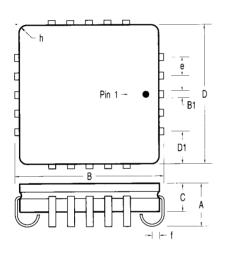

### **PACKAGE DIMENSIONS**

## **SOIC-16 PACKAGE (R SUFFIX)**

|     | MILLIM | ETERS | INC       | HES   |  |

|-----|--------|-------|-----------|-------|--|

| DIM | MIN    | MAX   | MIN       | MAX   |  |

| Α   | 9.80   | 10.00 | 0.386     | 0.393 |  |

| В   | 3.80   | 4.00  | 0.150     | 0.157 |  |

| С   | 1.35   | 1.75  | 0.054     | 0.068 |  |

| D   | 0.35   | 0.49  | 0.014     | 0.019 |  |

| F   | 0.40   | 1.25  | 0.016     | 0.049 |  |

| G   | 1.27   | BSC   | 0.050 BSC |       |  |

| J   | 0.19   | 0.25  | 0.008     | 0.009 |  |

| К   | 0.10   | 0.25  | 0.004     | 0.009 |  |

| М   | 0°     | 7°    | 0°        | 7°    |  |

| Р   | 5.80   | 6.20  | 0.229     | 0.244 |  |

| R   | 0.25   | 0.50  | 0.010     | 0.019 |  |

### NOTES:

- 1. CONTROLLING DIMENSION: MILLIMETER

2. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION

- 3. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

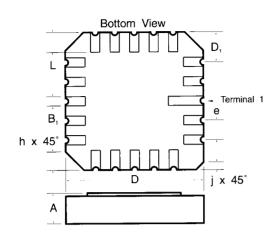

### **LCC-20 PACKAGE (E SUFFIX)**

|                | MILLIM | ETERS | INCHES    |       |  |  |

|----------------|--------|-------|-----------|-------|--|--|

| DIM            | MIN    | MAX   | MIN       | MAX   |  |  |

| Α              | 1.63   | 2.54  | 0.064     | 0.100 |  |  |

| B <sub>1</sub> | 0.56   | 0.71  | 0.022     | 0.028 |  |  |

| D              | 8.69   | 9.09  | 0.342     | 0.358 |  |  |

| D <sub>1</sub> | 1.91   | REF   | 0.075 REF |       |  |  |

| е              | 1.27   | BSC   | 0.050 BSC |       |  |  |

| j              | 0.51   | REF   | 0.020 REF |       |  |  |

| h              | 1.02   | REF   | 0.040 REF |       |  |  |

| L              | 1.14   | 1.40  | 0.045     | 0.055 |  |  |

#### NOTES

- 1. CONTROLLING DIMENSION: INCH

- 2. DIMENSION A IS OVERALL PACKAGE THICKNESS

- 3. DIMENSION D APPLIES TO ALL FOUR SIDES

### 20 J-LEADED CERAMIC (J SUFFIX)

|                | MILLIM | ETERS | INCHES    |       |  |  |  |

|----------------|--------|-------|-----------|-------|--|--|--|

| DIM            | MIN    | MAX   | MIN       | MAX   |  |  |  |

| А              | 2.97   | TYP   | 0.117 TYP |       |  |  |  |

| В              | 9.90   | 10.29 | 0.390     | 0.405 |  |  |  |

| B <sub>1</sub> | 0.40   | 0.56  | 0.016     | 0.022 |  |  |  |

| С              | 1.65   | 2.26  | 0.089     | 0.065 |  |  |  |

| D              | 9.40   | 9.65  | 0.370     | 0.380 |  |  |  |

| D <sub>1</sub> | 1.90   | 2.54  | 0.075     | 0.100 |  |  |  |

| е              | 1.27   | BSC   | 0.050 BSC |       |  |  |  |

| f              | 1.02   | TYP   | 0.040 TYP |       |  |  |  |

| h              | 0.51   | TYP   | 0.020 TYP |       |  |  |  |

#### NOTES:

- 1. CONTROLLING DIMENSION: INCH

- 2. DIMENSIONS B AND D APPLY TO ALL FOUR SIDES

### Conversion Table

|                 |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    | 16 |

|-----------------|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|

| 20-Term Ceramic | 2 | 3 | 4 | 5 | 7 | 8 | 9 | 10 | 12 | 13 | 14 | 15 | 17 | 18 | 19 | 20 |

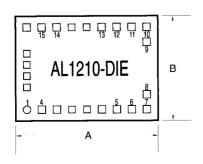

## **UNPACKAGED DIE (-DIE SUFFIX)**

|     | MILLIM | ETERS | INC   | HES   |

|-----|--------|-------|-------|-------|

| DIM | MIN    | MAX   | MIN   | MAX   |

| Α   | 1.93   | 2.18  | 0.076 | 0.086 |

| В   | 1.27   | 1.52  | 0.050 | 0.060 |

| С   | 0.28   | 0.43  | 0.011 | 0.017 |

#### NOTES:

- 1. CONTROLLING DIMENSION: MILLIMETER

- 2. DIMENSION C IS OVERALL DIE THICKNESS

- 3. NUMBERS BY BONDPADS REFER TO SOIC PINS