PARALLEL ASYNCHRONOUS SINGLE-BANK BIDIRECTIONAL FIFO 512 x 9-BIT, 1024 x 9-BIT, 2048 x 9-BIT PRELIMINARY IDT7271 IDT7272 IDT7273

T-46-35

### **FEATURES:**

- Bidirectional data transfer

- 512 x 9 organization (IDT7271)

- 1024 x 9 organization (IDT7272)

- 2048 x 9 organization (IDT7273)

- · Fast 25ns access time

- Single bank FIFO memory with data flow in one direction at a time

- Direction pin controls data flow from Port A-to-B, or Port B-to-A

- · Full and Empty flags

- · Fixed Almost-Full and Almost-Empty partial flags

- · Bypass and Diagnostic modes

- · 32-pin DIP, PLCC, LCC and SOJ

- Military product compliant to MIL-STD-883, Class B

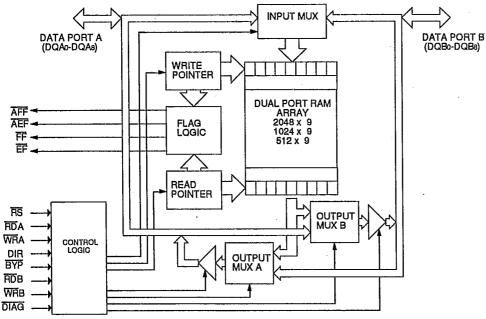

### **DESCRIPTION:**

The !DT7271/7272/7273 are very high speed, low power FIFO memories that enhance processor-to-processor and processor-to-peripheral communications. The 727x family use a single bank of memory; therefore, allowing one port to be accessed at any time. A direction pin (DIR) is provided to

determine data flow direction. When the DIR pin is Low, data flows from port A-to-B. Data flows in the opposite direction when the DIR pin is High.

A device reset can be initiated at any time by bringing the Reset (RS) pin LOW while holding the Read (RD), Bypass (BYP), Diagnostic (DIAG) and Write (WR) pins High.

There are four separate flags on these BiFIFOs. The two end-point flags are Empty (EF) and Full (FF); and the two partial flags with fixed offset size of 07H (eight bytes from the boundaries) are Almost-Empty (AE) and Almost-Full (AF). All flags are active low.

Bypass control allows data to be directly transferred from port A to port B, or vice versa, without going through the memory array. The bypass mode can be set by asserting the BYP pin (active Low).

The diagnostic mode allows written data to be read through the same port. This provides systems memory self-test upon power up or after a system failure.

The IDT7271/2/3 are fabricated using IDT's high speed submicron CEMOS™ technology. Military grade products are manufactured in compliant with the latest revision of MIL-STD-883, Class B.

## **FUNCTIONAL BLOCK DIAGRAMS**

CEMOS and SyncFIFO are trademarks of Integrated Device Technology, Inc.

2529 drw 01

**COMMERCIAL TEMPERATURE RANGE**

@1992 Integrated Device Technology, Inc.

**APRIL 1992**

DSC-2047/

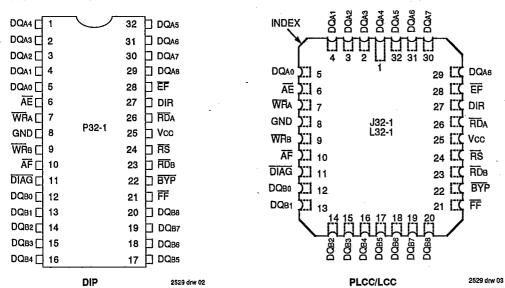

**TOP VIEW**

**TOP VIEW**

MILITARY AND COMMERCIAL TEMPERATURE RANGES

# PIN CONFIGURATIONS

T-46-35

### **PIN DESCRIPTION**

| Symbol    | Name         | 1/0 | Description                                                                                                                                             |

|-----------|--------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQA0-DQA8 | Data A       | 1/0 | 9-bit data pins for port A. The DIR pin controls direction of these pins (input or output)                                                              |

| DQ80-DQ88 | Data B       | 1/0 | 9-bit data pins for port B. The DIR pin controls state of these pins (inputs or outputs)                                                                |

| RDA       | Read A       | ı   | This input pin controls port A read operation. In bypass mode this pin controls the A port output enables. Active Low input.                            |

| RDs       | Read B       | ı   | This input pin controls port B read operation. Active Low input.                                                                                        |

| WRA       | Write A      | ŀ   | This input pin controls port A write operation. In bypass mode this pin controls the port B output enables, Active Low input.                           |

| WR8       | Write B      | 1   | This input pin controls port B write operation. Active Low input.                                                                                       |

| DIR       | Direction    | ı   | This input pin determines data flow direction. When it is Low, data flows from port A to port B. When it is High, data flows in the opposite direction. |

| DIAG      | Diagnostic   | l   | Once the data is loaded, the DIAG pin can be asserted followed by the DIR pin's state change, the written data can then be read through the same port.  |

| BYP       | Bypass       | 1   | This input pin sets the FIFO in the bypass mode, in which the FIFO acts as a transceiver Active Low input.                                              |

| RS        | Reset        | ı   | This pin resets all functions. Active Low input.                                                                                                        |

| ĀĒ        | Partial Flag | 0   | This output pin is asserted when the FIFO is almost empty. Active Low output.                                                                           |

| ĀĒ        | Partial Flag | 0   | This output pin is asserted when the FIFO is almost full. Active Low output.                                                                            |

| FF        | Full Flag    | 0   | This output is asserted when the FIFO is completely full. Active Low output.                                                                            |

| <b>EF</b> | Empty Flag   | 0   | This output is asserted when the FIFO is completely empty. Active Low output.                                                                           |

| Vcc       | Power        | 1   | One +5V power pins.                                                                                                                                     |

| GND       | Ground       |     | One ground pin at 0V.                                                                                                                                   |

2529 tbl 01

IDT7271/IDT7272/IDT7273 PARALLEL ASYNCHRONOUS SINGLE-BANK BIDIRECTIONAL FIFO 512 x 9-BIT, 1024 x 9-BIT & 2048 x 9-BIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

# ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Rating                                     | Com'l.       | MII.         | Unit |

|--------|--------------------------------------------|--------------|--------------|------|

| Vтеям  | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0 | -0.5 to +7.0 | ٧    |

| TA     | Operating<br>Temperature                   | 0 to +70     | -55 to +125  | °C   |

| TBIAS  | Temperature<br>Under Bias                  | -55 to +125  | -65 to +135  | °C   |

| TSTG   | Storage<br>Temperature                     | -55 to +125  | -65 to +155  | °C   |

| IQUT   | DC Output<br>Current                       | 50           | 50           | mA   |

NOTE: 2529 tbl 02 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS

may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# T- 46-35 RECOMMENDED DC **OPERATING CONDITIONS**

| Symbol              | Parameter                            | Min. | Тур. | Max. | Unit |  |

|---------------------|--------------------------------------|------|------|------|------|--|

| Vссм                | Military Supply<br>Voltage           | 4.5  | 5,0  | 5.5  | ٧    |  |

| Vccc                | Commercial Supply<br>Voltage         | 4.5  | 5.0  | 5.5  | ٧    |  |

| GND                 | Supply Voltage                       | 0    | 0    | 0    | V    |  |

| ViH                 | Input High Votage<br>Commercial      | 2.0  | _    | _    | ٧    |  |

| ViH                 | Input High Votage<br>Military        | 2.2  | -    | -    | ٧    |  |

| V <sub>IL</sub> (1) | Input Low Voltage<br>Com'l. and Mil. | -    | _    | 0.8  | ٧    |  |

NOTE:

1, 1,5V undershoots are allowed for 10ns once per cycle.

2529 tbl 04

2529 tbl 04

# DC ELECTRICAL CHARACTERISTICS

(Commercial:  $Vcc = 5.0V \pm 10\%$ ,  $TA = 0^{\circ}C$  to  $+70^{\circ}C$ ; Military:  $Vcc = 5.0V \pm 10\%$ ,  $TA = -55^{\circ}C + 125^{\circ}C$ )

|                     |                                                       |      | IDT7271L<br>IDT7272L<br>IDT7273L<br>IOMMERCI<br>25, 35, 50 | al   | IDT7271L<br>IDT7272L<br>IDT7273L<br>Military<br>tA = 30, 35, 50ns |      |      |      |

|---------------------|-------------------------------------------------------|------|------------------------------------------------------------|------|-------------------------------------------------------------------|------|------|------|

| Symbol              | Parameter                                             | Min. | Тур.                                                       | Max. | Min.                                                              | Typ. | Max. | Unit |

| L(1)                | Input Leakage Current (Any Input)                     | -1   |                                                            | 1    | -10                                                               |      | 10   | μА   |

| IOL(2)              | Output Leakage Current                                | -10  |                                                            | 10   | -10                                                               |      | 10   | μА   |

| Vон                 | Output Logic "1" Voltage louT= -2mA                   | 2.4  |                                                            |      | 2.4                                                               |      |      | V    |

| Vol                 | Output Logic "0" Voltage lour = 8mA                   | 1    |                                                            | 0.4  |                                                                   |      | 0.4  | V    |

| Icc1 <sup>(3)</sup> | Average VCC Power Supply Current                      |      | 75                                                         | 120  |                                                                   | 100  | 150  | mA   |

| lcc2 <sup>(3)</sup> | Average Standby Current (RA = WA = RB = WB = RS = VH) |      | 8                                                          | 15   | <u> </u>                                                          | 12   | 25   | mA   |

| ICC3 <sup>(3)</sup> | Power Down Current (All Inputs = Vcc - 0.2V)          |      | <del></del>                                                | 8    |                                                                   | _    | 12   | mA   |

## NOTES:

- Measurements with 0.4 ≤ V<sub>IN</sub> ≤ V<sub>CC</sub>.

OE ≥ V<sub>IH</sub>, 0.4 ≤ V<sub>OUT</sub> ≤ V<sub>CC</sub>.

- 3. Tested at f = 20 MHz.

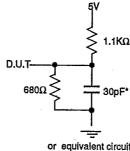

### **AC TEST CONDITIONS**

| Input Pulse Levels                                  | GND to 3.0V          |

|-----------------------------------------------------|----------------------|

| Input Rise/Fall Times Input Timing Reference Levels | 5ns<br>1.5V          |

| Output Reference Levels Output Load                 | 1.5V<br>See Figure 1 |

|                                                     | 5001190101           |

2529 lbl 08

# **CAPACITANCE**(1) (TA = +25°C, f = 1.0 MHz)

| Symbol                | Parameter          | Condition | Max. | Unit |

|-----------------------|--------------------|-----------|------|------|

| CIN <sup>(3)</sup>    | Input Capacitance  | VIN = OV  | 10.  | ρF   |

| Соит <sup>(2,3)</sup> | Output Capacitance | Vour = 0V | 10   | pF   |

1. This parameter is sampled and not 100% tested.

2. With output deselected.

3. Characterized values, not currently tested.

or equivalent circuit

Figure 1. Output Load

\*Includes jig and scope capacitances.

IDT7271/IDT7272/IDT7273 PARALLEL ASYNCHRONOUS SINGLE-BANK BIDIRECTIONAL FIFO 512 x 9-BIT, 1024 x 9-BIT & 2048 x 9-BIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

# **AC ELECTRICAL CHARACTERISTICS**

(Commercial:  $Vcc = 5.0V \pm 10\%$ ,  $TA = 0^{\circ}C$  to  $+70^{\circ}C$ ; Military:  $Vcc = 5.0V \pm 10\%$ ,  $TA = -55^{\circ}C + 125^{\circ}C$ )

|             |                                      | Comm           | nercial                  | Mill       | tary  | Commercial and Military |          |             |             |             |

|-------------|--------------------------------------|----------------|--------------------------|------------|-------|-------------------------|----------|-------------|-------------|-------------|

|             |                                      | IDT72          | 71L25                    |            | 71L30 |                         | 71L35    |             | 71L50       | i           |

|             |                                      |                | IDT7272L25<br>IDT7273L25 |            | 72L30 |                         | 72L35    | IDT7272L50  |             |             |

|             |                                      | -              |                          | IDT7273L30 |       | IDT7273L35              |          | IDT7273L50  |             |             |

| Symbol      | Parameter                            | Min.           | Max.                     | Min.       | Max.  | Min.                    | Max.     | Min.        | Max.        | Unit        |

| Reset Tir   |                                      | ·              |                          |            |       | r                       |          | ·           |             | <del></del> |

| trsc        | Reset Cycle Time                     | 35             |                          | 40         | ·     | 45                      |          | 65          |             | ns          |

| tas         | Reset Pulse Width                    | 25             |                          | 30         |       | 35                      |          | 50          |             | ns          |

| tass        | Reset Set-up Time                    | 25             |                          | 30         |       | 35                      |          | 50          |             | ns          |

| tasa        | Reset Recovery Time                  | 10             |                          | 10         |       | 10                      | _=       | 15          |             | ns          |

| trfv        | Reset to Flag Valid                  | <u> </u>       | 25                       |            | 30    | <u>L-</u> _             | 35       |             | 50          | ns          |

| Read/Wr     | te Timing                            |                |                          |            |       |                         |          | <del></del> |             |             |

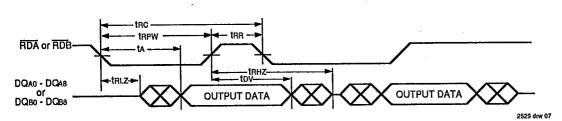

| tA          | Read Access Time                     |                | 25                       |            | 30    |                         | 35       |             | 50          | ns          |

| tac         | Read Cycle Time                      | 35             |                          | 40         |       | 45                      |          | 65          |             | ns          |

| trpw        | Read Pulse Width                     | 25             |                          | 30         |       | 35                      |          | 50          |             | ns          |

| tar         | Read Recovery Time                   | 10             |                          | 10         |       | 10                      |          | 15          |             | ns          |

| tov         | Data valid from read pulse HIGH      | 3              |                          | 3          |       | 3                       |          | 3           | <del></del> | ns          |

| tanz        | Read HIGH to data bus at High Z      |                | 18                       |            | 20    |                         | 20       |             | 30          | ns          |

| truz        | Read LOW to data bus at Low Z        | 3              |                          | 3          |       | 3                       | _        | 3           |             | กร          |

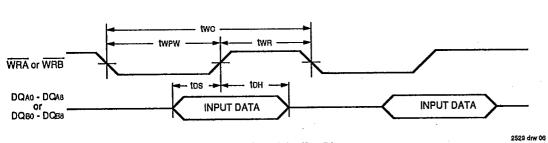

| twc         | Write Cycle Time                     | 35             | _                        | 40         |       | 45                      |          | 65          |             | ns          |

| twpw        | Write Pulse Width                    | 25             | <b>—</b> ,               | 30         | _     | 35                      |          | 50          |             | ns          |

| twn         | Write Recovery Time                  | 10             |                          | 10         |       | 10                      | <u> </u> | 15          | _           | ns          |

| tos         | Data Set-up Time                     | 15             | -                        | 18         |       | 18                      |          | 30          | _           | ns          |

| ton         | Data Hold Time                       | 0              |                          | 0          |       | 1                       |          | 5           | -           | ns          |

| Direction   | Change, Diagnostic and Bypass Timing | -              | ,                        |            |       |                         |          |             |             |             |

| torwi.      | DIR Change to Write Low              | 25             |                          | 30         |       | 35                      |          | 50          |             | ns          |

| tDFV        | DIR Change to Valid Flags            |                | 20                       | <b>—</b>   | 25    |                         | 30       | _           | 45          | ns          |

| TORL        | DIR Change to Read Low               | 20             |                          | 25         |       | 30                      | -        | 35          | _           | ns          |

| TOHDGL      | DIR Change to DIAG High              | 0              |                          | 0          |       | 1                       | _        | 5           | _           | пѕ          |

| torsu       | DIR Setup                            | 10             | _                        | 15         |       | 20                      | _        | 30          | -           | ns          |

| togue       | DIAG Low to DIR Change               | 10             |                          | 15         |       | 20                      |          | 30          |             | ns          |

| toghwl.     | DIAG High to Write Low               | 25             |                          | 30         |       | 35                      |          | 50          |             | ns          |

| togwa       | DIAG Low to Write Low (either port)  | 10             |                          | 15         |       | 20                      | _        | 30          |             | ns          |

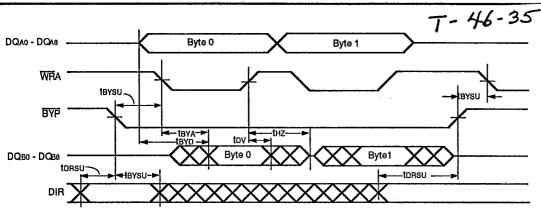

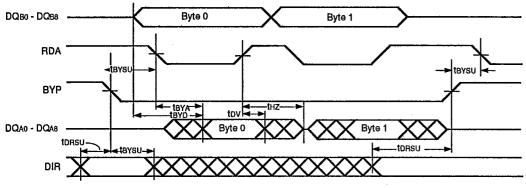

| taysu       | BYP Set-up Time                      | 10             |                          | 15         |       | 20                      |          | 30          |             | ns          |

| <b>TBYA</b> | Bypass Access Time                   | <del>  -</del> | 25                       |            | 30    | _                       | 35       | <b>—</b>    | 50          | ns          |

| teyp        | Bypass Delay Time                    | <del>  _</del> | 25                       |            | 30    | _                       | 35       | _           | 50          | ns          |

| Flag Tim    |                                      |                |                          | <u> </u>   |       |                         |          |             |             |             |

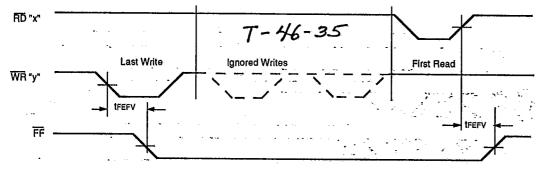

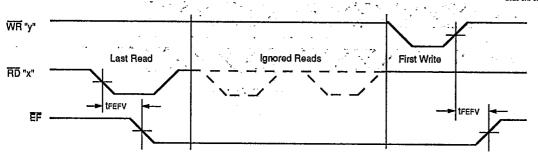

| tFEFV       | Full or Empty Flag Valid             | Т-             | 20                       | T -        | 25    | T                       | 30       | Τ —         | 40          | ns          |

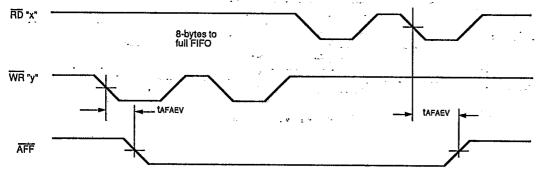

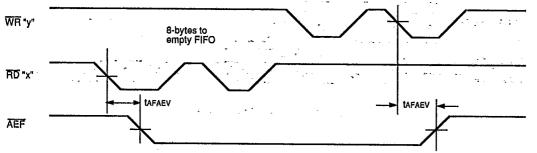

| tAFAEV      | Almost-Full or Empty Flag Valid      | <b>—</b>       | 35                       | <b> </b>   | 40    |                         | 45       | <b> </b>    | 65          | ns          |

| <u> </u>    | 1                                    |                |                          |            |       | -\                      |          | <u></u>     |             | 2529 tbl 0  |

IDT7271/IDT7272/IDT7273 PARALLEL ASYNCHRONOUS SINGLE-BANK BIDIRECTIONAL FIFO 512 x 9-BIT, 1024 x 9-BIT & 2048 x 9-BIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

### **FUNCTIONAL DESCRIPTION**

IDT's Single-Bank BiFIFO family is versatile for both multiprocessor and peripheral applications. The 727x family is a low-cost solution for bidirectional systems where data flow in only one direction at a time is needed. The Single-Bank BiFIFO implies that there is only one bank of memory shared by two ports, with a direction pin provided for altering data flow direction.

Care must be taken to assure that the appropriate flag is monitored by each system (i.e. FF is monitored on the writing side; EF is monitored on the reading side). In general a write cycle cannot be allowed to begin if FF is asserted and a read cycle cannot be allowed to begin if EF is asserted. For additional information, refer to Tech Note 8: Operating FIFOs on Full and Empty Boundary Conditions and Tech Note 6: Designing with FIFOs.

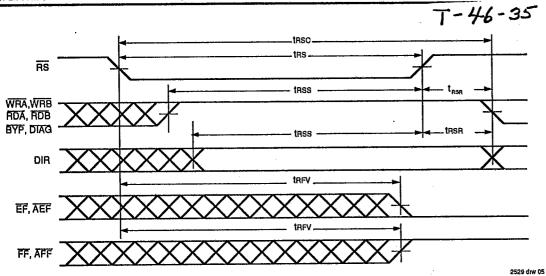

#### Reset

A reset is initiated by bringing the Reset ( $\overline{RS}$ ) pin Low, while holding the Read ( $\overline{RD}$ ), Bypass ( $\overline{BYP}$ ), Diagnostic ( $\overline{DIAG}$ ) and Write ( $\overline{WR}$ ) pins High. After a device reset, all internal pointers are cleared and flags are adjusted accordingly. For proper device operation, all control inputs pins must be stable before the reset signal is deasserted. A recovery time is required before loading the device or altering operation mode (Bypass, Diagnostic, etc).

### Flags

There are four separate flags on the 7271/2/3 BiFIFO, two partial flags, a full flag and an empty flag. All are active low. The two partial flags are the Almost Full (ĀF) and the Almost Empty (ĀE) flags, each with a fixed offset size of 07H (eight bytes from the empty or full conditions). These can be used as an early warning signal. The two other flags are fixed at Empty EF and Full FF. These are asserted during the last read or write operation respectively. These are used to prevent device overflow or underflow.

### **Data Flow Direction**

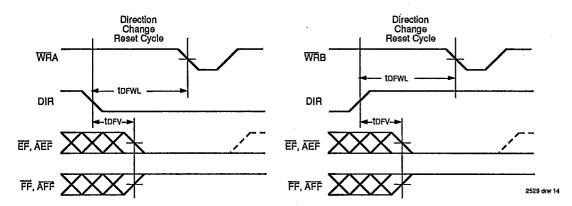

Data can only flow from one port to another at any given time. The direction of data flow is determined by the state of the DIR pin. When the DIR pin is Low, data can be written only into port A. Data can be read only out of port B. Data flows in the opposite direction when the DIR pin is High. Data flow function can be changed at any time. By altering the DIR state, the two read and write pointers are reset and data flows in the opposite direction. The falling edge of the first write cycle is used to determine the end of the reset cycle. Flags outputs reflect the pointer states and thus change on the change of the DIR signal.

## Bypass Mode

Asserting the  $\overline{BYP}$  pin (active Low) places the device in the bypass mode. The FIFO functions as a simple transciever in this mode. Data can be directly written into or read out of a device which is connected to the B port by a device connected to the A port.

While in this mode, both RDB and WRB must be held High.

By asserting the  $\overline{WR}A$ , data on the A port will be driven out the B port. By asserting the  $\overline{RD}A$ , data on the B port will be driven out the A port. The  $\overline{WR}A$  signal is used to enable the B port's bus drivers. The  $\overline{RD}A$  signal is used enable the A ports.  $\overline{WR}A$  and  $\overline{RD}A$  must not be low at the same time.

Entering and exiting the bypass mode does not affect the internal pointers. The state of the DIR pin is ignored in the bypass mode. If DIR changes state in Bypass mode, the pointers will not reset until leaving the Bypass mode. If DIR changes state momentarily in Bypass mode there is no effect. Bypass mode does not alter flag states.

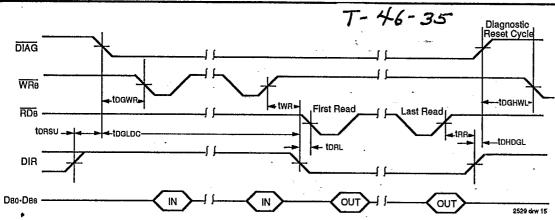

### **Diagnostic Mode**

Many systems require memory testing upon power up or after a system failure. The 727x family has a built-in diagnostic mode for self test. When in the diagnostic mode, written data can be read through the same port by altering the state of the DIR pin. In this case, the pointers are not reset (with direction change) allowing the retrieval of written data. The read and write pointers are reset upon exting the diagnostic mode. The leading edge of the first write cycle experienced after leaving diagnostic mode is used to terminate the reset cycle. Flag operations are normal in diagnostic mode, reflecting only the relative states of the read and write pointers. Thus they change on the rising edge of the DIAG signal when the pointers are reset upon leaving diagnostic mode.

The state of the DIR pin is latched when DIAG is brought low, determining which port of the FIFO is used for diagnostics. If DIR is Low at the High-to-Low transition of DIAG, A port is used for diagnostics. If High, B port is used. Figure 12 shows diagnostics for B port, but the timing also applies to A port diagnostics if DIR is inverted.

Data can be loaded into the memory array before or after setting the part into diagnostic mode. The DIAG pin must be asserted before by the DIR pin's first state change. Once in the diagnostic mode, data that has been written can be retrieved through the same port by reading from that port. Reading and writing can continue indefinately until the diagnostic mode has been exited.

Figure 2. Reset Cycle Timing

Figure 3. Write Timing (A or B)

Figure 4. Read Timing (A or B)

IDT7271/IDT7272/IDT7273 PARALLEL ASYNCHRONOUS SINGLE-BANK BIDIRECTIONAL FIFO 512 x 9-BIT, 1024 x 9-BIT & 2048 x 9-BIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

Figure 5. Full Flag Assertion/Deassertion Timing, in either direction or in Diagnostic mode

Figure 6. Empty Flag Assertion/Deassertion Timing, in either direction or in Diagnostic mode

2529 drw 09

Figure 7. Almost Full Flag Assertion/Deassertion Timing, in either direction or in Diagnostic mode

Figure 8. Almost Empty Flag Assertion/Deassertion Timing, in either direction or in Diagnostic mode

Figure 9. Bypass mode: Data flow from A to B

2529 drw 12

5

2529 drw 13

Figure 10. Bypass mode: Data Flow from B to A

Figure 11. Data Flow Direction Change and Reset cycle Timing

MILITARY AND COMMERCIAL TEMPERATURE RANGES

Figure 12. Diagnostic Mode Read/Write Timing and Diagnostic Reset Cycle.

## **TABLE I — OPERATING MODES**

| RS | BYP | DIAG | DIR | RDA | WRA | RDB | WRB | Operating Mode                                                        |

|----|-----|------|-----|-----|-----|-----|-----|-----------------------------------------------------------------------|

|    | 1   | 1    | ×   | 1   | 1   | 1   | 1   | Device reset                                                          |

| 1  | 1   | 0    | 0   | 1   | 7_  | 1   | 1   | Diagnostic mode: data is being loaded through A port                  |

| 1  | 1   | 0    | 1   | ı   | 1   | 1   | 1   | Diagnostic mode: data is being retrieved through A port               |

| 1  | 1   | 0    | 1   | 1   | 1   | 1   | 5   | Diagnostic mode: data is being loaded through B port                  |

| 1  | 1   | 0    | 0   | 1   | 1   | 7   | 1   | Diagnostic mode: data is being retrieved through B port               |

| 1  | 0   | 1    | x   | 1   | 0   | 1   | 1   | Bypass mode: Data flows from A port to B port                         |

| 1  | 0   | 1    | х   | 0   | 1   | 1   | 1   | Bypass mode: Data flows from B port to A port                         |

| 91 | 1   | 1    | 0   | 1   | 7   |     | 1   | FIFO Mode: Asynchronous read/write. Data flows from port A to port B. |

| 1  | 1   | 1    | 1   | 7.  | 1   | 1   |     | FIFO Mode: Asynchronous read/write. Data flows from port B to port A  |

Unspecified states are not allowed