NOMINAL SIZE =

1 in x 0.62 in (25,4 mm x 15,75 mm)

#### **Features**

- Up to 10-A Output Current

- 5-V Input Voltage

- Wide-Output Voltage Adjust (0.8 V to 3.6 V)

- Efficiencies up to 96 %

- 150 W/in³ Power Density

- On/Off Inhibit

- Output Voltage Sense

- Pre-Bias Startup

- Margin Up/Down Controls

- Under-Voltage Lockout

- Auto-Track<sup>TM</sup> Sequencing

- Output Over-Current Protection (Non-Latching, Auto-Reset)

- Operating Temp: -40 to +85 °C

- DSP Compatible Output Voltages

- IPC Lead Free 2

- Safety Agency Approvals (Pending) UL 1950, CSA 22.2 950, & EN60950

- Point-of-Load Alliance (POLA) Compatible

#### **Description**

**ADVANCE INFORMATION**

The ATH10T05 series non-isolated power module is small in size but big on performance and flexibility. Its high output current, compact footprint, and industry-leading features offers system designers a versatile module for powering complex multi-processor digital systems.

This product employs double-sided surface mount construction and provides high-performance step-down power conversion for up to 10 A of output current from a 5-V input bus voltage. The output voltage is adjustable and can be set to any value over the range, 0.8 V to 3.6 V, using a single resistor.

This series includes Auto-Track<sup>TM</sup>

Sequencing. Auto-Track simplifies the task of supply voltage sequencing in a power system by enabling modules to track each other, or any external voltage, during power up and power down.

Other operating features include an on/off inhibit, margin up/down controls, and the ability to start up into an existing output voltage or prebias. To ensure tight load regulation, an output voltage sense is also provided. A non-latching overcurrent trip serves as load fault protection.

Target applications include complex multi-voltage, multi-processor systems that incorporate the industry's high-speed DSPs, micro-processors and bus drivers.

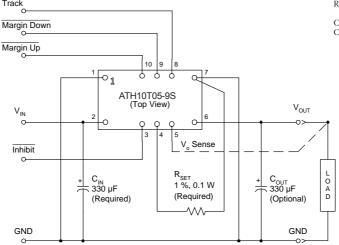

#### **Pin Configuration**

| Pin | Function              |

|-----|-----------------------|

| 1   | GND                   |

| 2   | V <sub>in</sub>       |

| 3   | Inhibit *             |

| 4   | V <sub>o</sub> Adjust |

| 5   | V <sub>o</sub> Sense  |

| 6   | V <sub>out</sub>      |

| 7   | GND                   |

| 8   | Track                 |

| 9   | Margin Down *         |

| 10  | Margin Up *           |

\* Denotes negative logic: Open = Normal operation Ground = Function active

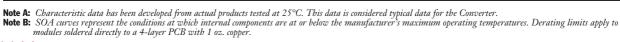

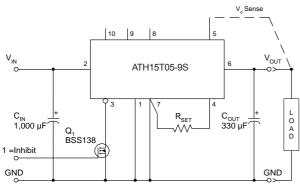

#### **Standard Application**

$R_{set}$  = Resistor to set the desired output voltage (see spec. table for values)  $C_{in}$  = Required 330 µF capacitor

$C_{\text{in}}$  = Required 330 µF capacitor  $C_{\text{out}}$  = Optional 330 µF capacitor

# 10-A, 5-V Input Non-Isolated Wide-Output Adjust Power Module

#### **Ordering Information**

| Input Volta                          | ge          | <b>Output Voltage</b>                                            | Output Current | Model Number     |

|--------------------------------------|-------------|------------------------------------------------------------------|----------------|------------------|

| 4.5V to 5.5V                         | 1           | 0.8V1 to 3.6V                                                    | 10A            | ATH10T05-9(S)(J) |

| Options:     "-J"     "-SJ"     "-S" | -<br>-<br>- | Through-hole Termin<br>SMT Termination, To<br>SMT Termination, T |                |                  |

#### Notes:

#### **Pin Descriptions**

**Vin:** The positive input voltage power node to the module, which is referenced to common *GND*.

**Vout:** The regulated positive power output with respect to the *GND* node.

**GND:** This is the common ground connection for the *Vin* and *Vout* power connections. It is also the 0 VDC reference for the control inputs.

**Inhibit:** The Inhibit pin is an open-collector/drain negative logic input that is referenced to *GND*. Applying a low-level ground signal to this input disables the module's output and turns off the output voltage. When the *Inhibit* control is active, the input current drawn by the regulator is significantly reduced. If the *Inhibit* pin is left open-circuit, the module will produce an output whenever a valid input source is applied.

**Vo Adjust:** A 0.1 W 1 % resistor must be directly connected between this pin and pin 7 (GND) to set the output voltage to a value higher than 0.8 V. The temperature stability of the resistor should be 100 ppm/°C (or better). The set point range for the output voltage is from 0.8 V to 3.6 V. The resistor value required for a given output voltage may be calculated from the following formula. If left open circuit, the output voltage will default to its lowest value. For further information on output voltage adjustment consult the related application note.

$$R_{set} \hspace{1cm} = 10 \hspace{1mm} k\Omega \hspace{1mm} \frac{0.8 \hspace{1mm} V}{V_{out} - 0.8 \hspace{1mm} V} \hspace{1mm} - 2.49 \hspace{1mm} k\Omega$$

The specification table gives the preferred resistor values for a number of standard output voltages. **Vo Sense:** The sense input allows the regulation circuit to compensate for voltage drop between the module and the load. For optimal voltage accuracy *Vo Sense* should be connected to *Vout*. It can also be left disconnected.

**Track:** This is an analog control input that enables the output voltage to follow an external voltage. This pin becomes active typically 20 ms after the input voltage has been applied, and allows direct control of the output voltage from 0 V up to the nominal set-point voltage. Within this range the output will follow the voltage at the *Track* pin on a volt-for-volt basis. When the control voltage is raised above this range, the module regulates at its set-point voltage. The feature allows the output voltage to rise simultaneously with other modules powered from the same input bus. If unused, the input may be left unconnected. *Note: Due to the under-voltage lockout, this feature does not allow the output from the module to follow its own input voltage during power up. For more information, consult the related application note.*

**Margin Down:** When this input is asserted to *GND*, the output voltage is decreased by 5% from the nominal. The input requires an open-collector (open-drain) interface. It is not TTL compatible. A lower percent change can be accommodated with a series resistor. If unused, the input may be left unconnected. For further information, consult the related application note.

**Margin Up:** When this input is asserted to *GND*, the output voltage is increased by 5%. The input requires an open-collector (open-drain) interface. It is not TTL compatible. The percent change can be reduced with a series resistor. If unused, the input may be left unconnected. For further information, consult the related application note.

<sup>&</sup>lt;sup>1</sup>Preset output voltage is 0.8V; externally adjustable to 3.6V through the Vo,Adjust pin

#### 10-A, 5-V Input Non-Isolated **Wide-Output Adjust Power Module**

#### **Environmental & Absolute Maximum Ratings** (Voltages are with respect to GND)

| Characteristics             | Symbols      | Conditions                                                  | Min     | Тур        | Max            | Units |

|-----------------------------|--------------|-------------------------------------------------------------|---------|------------|----------------|-------|

| Track Input Voltage         | $V_{track}$  |                                                             | -0.3    | _          | $V_{in} + 0.3$ | V     |

| Operating Temperature Range | $T_a$        | Over Vin Range                                              | -40 (i) | _          | 85             | °C    |

| Solder Reflow Temperature   | $T_{reflow}$ | Surface temperature of module body or pins                  |         |            | 215 (ii)       | °C    |

| Storage Temperature         | $T_s$        | _                                                           | -40     | _          | 125            | °C    |

| Mechanical Shock            |              | Per Mil-STD-883D, Method 2002.3<br>1 msec, ½ Sine, mounted  | _       | TBD        | _              | G's   |

| Mechanical Vibration        |              | Mil-STD-883D, Method 2007.2 Suffix H<br>20-2000 Hz Suffix S | _       | TBD<br>TBD | _              | G's   |

| Weight                      | _            |                                                             | _       | 3.7        | _              | grams |

| Flammability                | _            | Meets UL 94V-O                                              |         |            |                |       |

(i) For operation below 0 °C the external capacitors must have stable characteristics. use either a low ESR tantalum, Os-Con, or ceramic capacitor.

(ii) During reflow of SMD package version do not elevate peak temperature of the module, pins or internal components above the stated maximum. For further guidance refer to the application note, "Reflow Soldering Requirements for Plug-in Power Surface Mount Products."

### $\textbf{Specifications} \hspace{0.2cm} \text{(Unless otherwise stated, $T_a=25$ °C, $V_{in}=5$ V, $V_o=3.3$ V, $C_{in}=330$ $\mu$F, $C_{out}=0$ $\mu$F, and $I_o=I_omax$)}$

|                                                                   |                                     |                                                                                                                                                          |                              | ATH10T05   |                  |            |  |

|-------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------|------------------|------------|--|

| Characteristics                                                   | Symbols                             | Conditions                                                                                                                                               | Min                          | Тур        | Max              | Units      |  |

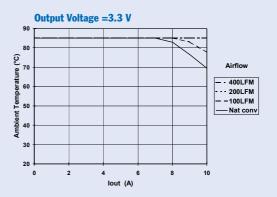

| Output Current                                                    | $I_o$                               | $0.8 \text{ V} \le \text{V}_{\text{o}} \le 3.6 \text{ V}$ , $60 ^{\circ}\text{C}$ , $200  \text{LFM}$ airflow $25 ^{\circ}\text{C}$ , natural convection | 0                            | _          | 10 (1)<br>10 (1) | A          |  |

| Input Voltage Range                                               | Vin                                 | Over Io range                                                                                                                                            | 4.5                          | _          | 5.5              | V          |  |

| Set-Point Voltage Tolerance                                       | $V_{o}$ tol                         |                                                                                                                                                          | _                            | _          | ±2 (2)           | $%V_{o}$   |  |

| Temperature Variation                                             | $\Delta Reg_{temp}$                 | -40 °C <t<sub>a &lt; +85 °C</t<sub>                                                                                                                      | _                            | ±0.5       | _                | $%V_{o}$   |  |

| Line Regulation                                                   | $\Delta Regline$                    | Over V <sub>in</sub> range                                                                                                                               | _                            | ±10        | _                | mV         |  |

| Load Regulation                                                   | $\Delta Reg_{load}$                 | Over Io range                                                                                                                                            | _                            | ±12        | _                | mV         |  |

| Total Output Variation                                            | $\Delta Reg_{tot}$                  | Includes set-point, line, load, $-40~^{\circ}\text{C} \le \text{T}_{\text{a}} \le +85~^{\circ}\text{C}$                                                  | _                            | _          | ±3 (2)           | $%V_{o}$   |  |

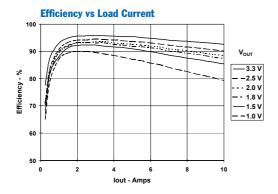

| Efficiency                                                        | η                                   | $I_o = 7 \text{ A}$ $R_{SET} = 698 \Omega$ $V_o = 3.3 \text{ V}$                                                                                         | _                            | 94         | _                |            |  |

|                                                                   |                                     | $R_{SET} = 2.21 \text{ k}\Omega \text{ V}_{o} = 2.5 \text{ V}$<br>$R_{SET} = 4.12 \text{ k}\Omega \text{ V}_{o} = 2.0 \text{ V}$                         | _                            | 92<br>91   | _                |            |  |

|                                                                   |                                     | $R_{SET} = 7.12 \text{ kgz} V_0 - 2.0 \text{ V}$<br>$R_{SET} = 5.49 \text{ k}\Omega V_0 = 1.8 \text{ V}$                                                 | _                            | 90         | _                | %          |  |

|                                                                   |                                     | $R_{SET} = 8.87 \text{ k}\Omega \text{ V}_{o} = 1.5 \text{ V}$                                                                                           | _                            | 89         | _                |            |  |

|                                                                   |                                     | $R_{SET} = 17.4 \text{ k}\Omega \text{ V}_{o} = 1.2 \text{ V}$<br>$R_{SET} = 36.5 \text{ k}\Omega \text{ V}_{o} = 1.0 \text{ V}$                         | _                            | 86<br>85   | _                |            |  |

| V <sub>o</sub> Ripple (pk-pk)                                     | V <sub>r</sub>                      | 20 MHz bandwidth                                                                                                                                         | _                            | 25         | _                | mVpp       |  |

| Over-Current Threshold                                            | I <sub>o</sub> trip                 | Reset, followed by auto-recovery                                                                                                                         | _                            | 20         | _                | A          |  |

| Transient Response                                                |                                     | 1 A/μs load step, 50 to 100 % I <sub>o</sub> max,<br>C <sub>out</sub> =330 μF                                                                            |                              | 70         |                  | C          |  |

|                                                                   | $	au_{ m tr} \ \Delta  m V_{ m tr}$ | Recovery Time<br>Vo over/undershoot                                                                                                                      | _                            | 70<br>100  | _                | μSec<br>mV |  |

| Margin Up/Down Adjust                                             | $\Delta V_o$ margin                 |                                                                                                                                                          | _                            | ± 5        | _                | %          |  |

| Margin Input Current (pins 9 /10)                                 | ${ m I_{IL}}$ margin                | Pin to GND                                                                                                                                               | _                            | -8 (3)     | _                | μA         |  |

| Track Input Current (pin 8)                                       | I <sub>IL</sub> track               | Pin to GND                                                                                                                                               | _                            | _          | -130 (4)         | μA         |  |

| Track Slew Rate Capability                                        | dV <sub>track</sub> /dt             | $ V_{\text{track}} - V_{\text{o}}  \le 50 \text{ mV} \text{ and } V_{\text{track}} < V_{\text{o}}(\text{nom})$                                           | 5                            | _          | _                | V/ms       |  |

| Under-Voltage Lockout                                             | UVLO                                | $V_{ m in}$ increasing $V_{ m in}$ decreasing                                                                                                            | 3.4                          | 4.3<br>3.7 | 4.45<br>—        | V          |  |

| Inhibit Control (pin3)<br>Input High Voltage<br>Input Low Voltage | $V_{ m IH} \ V_{ m IL}$             | Referenced to GND                                                                                                                                        | V <sub>in</sub> -0.5<br>-0.2 | _          | Open (4)<br>0.6  | V          |  |

| Input Low Current                                                 | $I_{\rm IL}$ inhibit                | Pin to GND                                                                                                                                               | _                            | -130       | _                | μA         |  |

| Input Standby Current                                             | I <sub>in</sub> inh                 | Inhibit (pin 3) to GND, Track (pin 8) open                                                                                                               | _                            | 10         | _                | mA         |  |

| Switching Frequency                                               | $f_{s}$                             | Over V <sub>in</sub> and I <sub>o</sub> ranges                                                                                                           | 275                          | 300        | 325              | kHz        |  |

| External Input Capacitance                                        | C <sub>in</sub>                     |                                                                                                                                                          | 330 (5)                      | _          | _                | μF         |  |

| External Output Capacitance                                       | C <sub>out</sub>                    |                                                                                                                                                          | 0                            | 330 (6)    | 15,000           | μF         |  |

| Reliability                                                       | MTBF                                | Per Bellcore TR-332<br>50 % stress, T <sub>a</sub> =40 °C, ground benign                                                                                 | TBD                          | _          | _                | 106 Hrs    |  |

**Notes:** (1) See SOA curves or consult factory for appropriate derating.

- See SOA curves or consult factory for appropriate derating.

The set-point voltage tolerance is affected by the tolerance and stability of R<sub>SET</sub>. The stated limit is unconditionally met if R<sub>SET</sub> has a tolerance of 1 % with 100 ppm/°C or better temperature stability.

A small low-leakage (<100 nA) MOSFET is recommended to control this pin. The open-circuit voltage is less than 1 Vdc.</li>

This control pin has an internal pull-up to the input voltage Vin. If it is left open-circuit the module will operate when input power is applied. A small low-leakage (<100 nA) MOSFET is recommended for control. For further information, consult the related application note.</li>

A 330 µF input capacitor is required for proper operation. The capacitor must be rated for a minimum of 500 mA rms of ripple current.

An external output capacitor is not required for basic operation. Adding 330 µF of distributed capacitance at the load will improve the transient response.

10-A, 5-V Input Non-Isolated Wide-Output Adjust Power Module

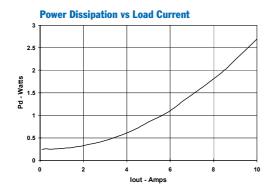

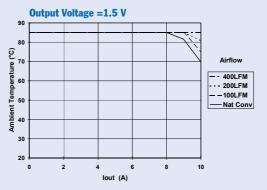

#### Characteristic Data; V<sub>in</sub> = 5 V (See Note A)

###

#### Safe Operating Area; V<sub>in</sub> =5 V (See Note B)

The products listed hereunder are prototype or pre-production devices which have not been fully qualified to Astec's specifications. Product specifications are subject to change without notice. Astec makes no warranty, either expressed, implied, or statutory, including implied warranty of merchantability or fitness for a specific purpose, of these products.

#### ATH10T03 & ATH10T05 Series

# Adjusting the Output Voltage of the ATH10T033 & ATH10T05 Wide-Output Adjust Power Modules

The  $V_0$  Adjust control (pin 4) sets the output voltage of the ATH10T033 and ATH10T05 products to a value higher than 0.8 V. The adjustment range of the ATH10T033 (3.3-V input) is from 0.8 V to 2.5 V¹, and the ATH10T05 (5-V input) from 0.8 V to 3.6 V. For an output voltage other than 0.8 V a single external resistor,  $R_{\rm set}$  must be connected directly between the  $V_0$  Adjust and GND pins ². Table 1-1 gives the preferred value of the external resistor for a number of standard voltages, along with the actual output voltage that this resistance value provides.

For other output voltages the value of the required resistor can either be calculated using the following formula, or simply selected from the range of values given in Table 1-2. Figure 1-1 shows the placement of the required resistor.

$$R_{set} = 10 \text{ k}\Omega \cdot \frac{0.8 \text{ V}}{V_{out} - 0.8 \text{ V}} - 2.49 \text{ k}\Omega$$

Table 1-1; Preferred Values of R<sub>set</sub> for Standard Output Voltages

| V <sub>out</sub> (Standard) | R <sub>set</sub> (Pref'd Value) | V <sub>out</sub> (Actual) |

|-----------------------------|---------------------------------|---------------------------|

| 3.3 V 1                     | 698 Ω                           | 3.309V                    |

| 2.5 V                       | 2.21 kΩ                         | 2.502 V                   |

| 2 V                         | 4.12 kΩ                         | $2.010\mathrm{V}$         |

| 1.8 V                       | 5.49 kΩ                         | 1.803 V                   |

| 1.5 V                       | $8.87~\mathrm{k}\Omega$         | $1.504\mathrm{V}$         |

| 1.2 V                       | $17.4 \mathrm{k}\Omega$         | $1.202\mathrm{V}$         |

| 1 V                         | 36.5 kΩ                         | 1.005 V                   |

| 0.8 V                       | Open                            | $0.8\mathrm{V}$           |

Figure 1-1; Vo Adjust Resistor Placement

Table 1-2; Output Voltage Set-Point Resistor Values

| V <sub>a</sub> Req'd | R <sub>set</sub>         | V <sub>a</sub> Req'd | R <sub>set</sub>        |

|----------------------|--------------------------|----------------------|-------------------------|

| 0.800                | Open                     | 2.00                 | 4.18 kΩ                 |

| 0.825                | 318 kΩ                   | 2.05                 | 3.91 kΩ                 |

| 0.850                | 158 kΩ                   | 2.10                 | $3.66~\mathrm{k}\Omega$ |

| 0.875                | $104  \mathrm{k}\Omega$  | 2.15                 | $3.44\mathrm{k}\Omega$  |

| 0.900                | 77.5 kΩ                  | 2.20                 | $3.22~\mathrm{k}\Omega$ |

| 0.925                | 61.5 kΩ                  | 2.25                 | $3.03~\mathrm{k}\Omega$ |

| 0.950                | 50.8 kΩ                  | 2.30                 | $2.84\mathrm{k}\Omega$  |

| 0.975                | 43.2 kΩ                  | 2.35                 | $2.67~\mathrm{k}\Omega$ |

| 1.000                | 37.5 kΩ                  | 2.40                 | $2.51~\mathrm{k}\Omega$ |

| 1.025                | 33.1 kΩ                  | 2.45                 | $2.36\mathrm{k}\Omega$  |

| 1.050                | 29.5 kΩ                  | 2.50                 | $2.22~\mathrm{k}\Omega$ |

| 1.075                | $26.6 \mathrm{k}\Omega$  | 2.55                 | $2.08\mathrm{k}\Omega$  |

| 1.100                | 24.2 kΩ                  | 2.60                 | $1.95~\mathrm{k}\Omega$ |

| 1.125                | 22.1 kΩ                  | 2.65                 | 1.83 kΩ                 |

| 1.150                | $20.4\mathrm{k}\Omega$   | 2.70                 | $1.72~\mathrm{k}\Omega$ |

| 1.175                | $18.8 \mathrm{k}\Omega$  | 2.75                 | $1.61~\mathrm{k}\Omega$ |

| 1.200                | 17.5 kΩ                  | 2.80                 | $1.51~\mathrm{k}\Omega$ |

| 1.225                | 16.3 kΩ                  | 2.85                 | 1.41 kΩ                 |

| 1.250                | 15.3 kΩ                  | 2.90                 | $1.32~\mathrm{k}\Omega$ |

| 1.275                | $14.4\mathrm{k}\Omega$   | 2.95                 | $1.23~\mathrm{k}\Omega$ |

| 1.300                | 13.5 kΩ                  | 3.00                 | $1.15~\mathrm{k}\Omega$ |

| 1.325                | 12.7 kΩ                  | 3.05                 | $1.07~\mathrm{k}\Omega$ |

| 1.350                | 12.1 kΩ                  | 3.10                 | $988\Omega$             |

| 1.375                | $11.4\mathrm{k}\Omega$   | 3.15                 | 914Ω                    |

| 1.400                | $10.8  \mathrm{k}\Omega$ | 3.20                 | 843 Ω                   |

| 1.425                | 10.3 kΩ                  | 3.25                 | $775 \Omega$            |

| 1.450                | 9.82 kΩ                  | 3.30                 | $710\Omega$             |

| 1.475                | 9.36 kΩ                  | 3.35                 | $647 \Omega$            |

| 1.50                 | 8.94 kΩ                  | 3.40                 | $587\Omega$             |

| 1.55                 | $8.18 \mathrm{k}\Omega$  | 3.45                 | 529 Ω                   |

| 1.60                 | 7.51 kΩ                  | 3.50                 | 473 Ω                   |

| 1.65                 | 6.92 kΩ                  | 3.55                 | 419 Ω                   |

| 1.70                 | 6.4 kΩ                   | 3.60                 | 367 Ω                   |

| 1.75                 | 5.93 kΩ                  |                      |                         |

| 1.80                 | 5.51 kΩ                  |                      |                         |

| 1.85                 | 5.13 kΩ                  |                      |                         |

#### Notes:

1.95

1. Modules that operate from a 3.3-V input bus should not be adjusted higher than 2.5 V.

$4.78 \,\mathrm{k}\Omega$

$4.47~\mathrm{k}\Omega$

- 2. Use a 0.1 W resistor. The tolerance should be 1 %, with temperature stability of 100 ppm/°C (or better). Place the resistor as close to the regulator as possible. Connect the resistor directly between pins 4 and 7 using dedicated PCB traces.

- Never connect capacitors from V<sub>o</sub> Adjust to either GND or V<sub>out</sub>. Any capacitance added to the V<sub>o</sub> Adjust pin will affect the stability of the regulator.

#### ATH10T033 & ATH10T05 Series

#### ATH10T033/T05: Capacitor Recommendations

#### **Input Capacitor**

The recommended input capacitor(s) is determined by 330 µF minimum capacitance, and 500 mA rms minimum ripple current rating.

Ripple current and <150 m $\Omega$  equivalent series resistance (ESR) values are the major considerations, along with temperature, when designing with different types of capacitors. Tantalum capacitors have a recommended minimum voltage rating of twice 2× (the maximum DC voltage + AC ripple). This is standard practice for tantalum capacitors to insure reliability.

#### **Output Capacitors (Optional)**

The ESR of the bulk (non-ceramic) capacitors must be equal to, or less than 150 m $\Omega$ . Electrolytic capacitors have marginal ripple performance at frequencies greater than 400 kHz but excellent low frequency transient response. Above the ripple frequency, ceramic capacitors are necessary to improve the transient response and reduce any high frequency noise components apparent during higher current excursions.

#### **Tantalum Capacitors**

Tantalum type capacitors can be used for the output but only the AVX TPS, Sprague 593D/594/595 or Kemet T495/T510 series. These capacitors are recommended

over many other tantalum types due to their higher rated surge, power dissipation, and ripple current capability. As a caution the TAJ series by AVX is not recommended. This series has considerably higher ESR, reduced power dissipation, and lower ripple current capability. The TAJ series is less reliable than the AVX TPS series when determining power dissipation capability. Tantalum or Oscon® types are recommended for applications where ambient temperatures fall below 0 °C.

#### **Ceramic Capacitors**

Ceramic capacitors will compliment electrolytic types. Adding  $10 \, \mu F$  to  $47 \, \mu F$  of ceramic capacitance will reduce ripple on the input and output bus. Output ripple and transient measurement accuracy is improved by measuring directly across a  $10 \, \mu F$  ceramic capacitor.

#### **Capacitor Table**

Table 2-1 identifies the characteristics of capacitors from a number of vendors with acceptable ESR and ripple current (rms) ratings. The number of capacitors required at both the input and output buses is identified for each capacitor type.

This is not an extensive capacitor list. Capacitors from other vendors are available with comparable specifications. Those listed are for guidance. The RMS ripple current rating and ESR (at 100 kHz) are critical parameters necessary to insure both optimum regulator performance and long capacitor life.

Table 1: Input/Output Capacitors

| Capacitor Vendor/<br>Series                                 |                              |                          | Capacitor                                | Characteristics                          |                                       | Qua              | ntity            |                                                                  |

|-------------------------------------------------------------|------------------------------|--------------------------|------------------------------------------|------------------------------------------|---------------------------------------|------------------|------------------|------------------------------------------------------------------|

|                                                             | Working<br>Voltage           | Value (µF)               | (ESR) Equivalent<br>Series Resistance    | Max. Ripple<br>Current @105 °C<br>(Irms) | Physical Size<br>(mm)                 | Input<br>Bus     | Output<br>Bus    | Vendor Part Number                                               |

| Panasonic (FC Radial)<br>WA (SMT.)<br>FK (SMT.)<br>FC (SMT) | 10 V<br>10 V<br>25 V<br>16 V | 330<br>330<br>470<br>330 | 0.117 Ω<br>0.022 Ω<br>0080 Ω<br>0.150 Ω  | 555 mA<br>4500 mA<br>850 mA<br>670 mA    | 8×10<br>10×10.2<br>10×10.2<br>10×10.2 | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 | EEUFC1A331<br>EEFWA1A331P<br>EEVFK1E471P<br>EEVFC1C331P          |

| United Chemi-con<br>PXA (SMT)<br>PS<br>FX<br>LXZ Series     | 10 V<br>16 V<br>10 V<br>16 V | 330<br>330<br>390<br>330 | 0.024 Ω<br>0.014 Ω<br>0.018 Ω<br>0.120 Ω | 3770 mA<br>5050 mA<br>3710 mA<br>555 mA  | 10×7.7<br>10×12.5<br>8×10.5<br>8×12.5 | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 | PXA10VC331MJ80TP<br>16PS330MJ12<br>10FX390M<br>LXZ16VB331M8X12LL |

| Nichicon (WG)<br>HD Series<br>PM Series                     | 25 V<br>16 V<br>16 V         | 330<br>330<br>330        | 0.150 Ω<br>0.072 Ω<br>0.120 Ω            | 670 mA<br>760 mA<br>625 mA               | 10×10<br>8×11.5<br>10×12.5            | 1<br>1<br>1      | 1<br>1<br>1      | UWG1E331MNR1GS<br>UHD1A331MPR<br>UPM1C331MPH6                    |

| Sanyo-Os-con (SP)<br>SVP (SMT)                              | 10 V<br>10 V                 | 470<br>330               | 0.015 Ω<br>0.017 Ω                       | >4500 mA<br>>3950mA                      | 10×10.5<br>8×12                       | 1<br>1           | 1<br>1           | 10SP470M<br>10SVP330M                                            |

| AVX Tantalum<br>TPS (SMT.)                                  | 10 V<br>10 V                 | 330<br>330               | 0.045 Ω<br>0.060 Ω                       | 1723 mA<br>1826 mA                       | 7.3L<br>×5.7W<br>×4.1H                | 1                | 1<br>1           | TPSE337M010R0045<br>TPSV337M010R0060                             |

| Kemet Polymer<br>Tantalum T520/T530<br>(SMT)                | 10 V<br>10 V                 | 330<br>330               | 0.040 Ω<br>0.015 Ω                       | 1800 mA<br>>3800 mA                      | 4.3W<br>×7.3L<br>×4.0H                | 1                | 1<br>1           | T520X337M010AS<br>T530X337M010AS                                 |

| Sprague Tantalum<br>595D Series<br>(SMT)                    | 10 V<br>10 V                 | 330<br>330               | 0.100 Ω<br>0.045 Ω                       | 1040 mA<br>2360 mA                       | 7.2L<br>×6W<br>×4.1H                  | 1                | 1                | 595D337X0010D2T<br>594D337X0016R2T                               |

### **Application Notes**

ATH Series of Wide-Output Adjust Power Modules (3.3/5-V Input)

# Features of the ATH Family of Non-Isolated Wide Output Adjust Power Modules

#### **Point-of-Load Alliance**

The ATH family of non-isolated, wide-output adjust power modules are optimized for applications that require a flexible, high performance module that is small in size. These products are part of the "Point-of-Load Alliance" (POLA), which ensures compatible footprint, interoperability and true second sourcing for customer design flexibility. The POLA is a collaboration between Texas Instruments, Artesyn Technologies, and Astec Power to offer customers advanced non-isolated modules that provide the same functionality and form factor. Product series covered by the alliance includes the ATH06 (6 A), ATH10 (10 A), ATH12/15 (12/15 A), ATH18/22 (18/22 A), and the ATH26/30 (26/30 A).

From the basic, "Just Plug it In" functionality of the 6-A modules, to the 30-A rated feature-rich ATH30 Series, these products were designed to be very flexible, yet simple to use. The features vary with each product. Table 3-1 provides a quick reference to the available features by product and input bus voltage.

Table 3-1; Operating Features by Series and Input Bus Voltage

|            |             |                  | Adjust (Trim) | On/Off Inhibit | Over-Current | Pre-Bias Startup | Auto-Track™ | Margin Up/Down | Output Sense | Thermal Shutdown |

|------------|-------------|------------------|---------------|----------------|--------------|------------------|-------------|----------------|--------------|------------------|

| Series     | Input Bus   | I <sub>OUT</sub> | Adju          | /uO            | Öve          | Pre              | Aut         | Mar            | Out          | The              |

|            | 3.3 V       | 6 A              | •             | ٠              | •            | •                | •           |                |              |                  |

| ATH06      | 5 V         | 6 A              | •             | ٠              | •            | •                | •           |                |              |                  |

|            | 12 V        | 6 A              | •             | •              | •            |                  | •           |                |              |                  |

| ATH10      | 3.3 V / 5 V | 10 A             | •             | •              | •            | •                | •           | •              | •            |                  |

| 711110     | 12 V        | 10 A             | •             | •              | •            |                  | •           | •              | •            |                  |

| ATH12/15   | 3.3 V / 5 V | 15 A             | •             | ٠              | •            | •                | •           | •              | ٠            |                  |

| ATTTIZ/13  | 12 V        | 12 A             | •             | ٠              | •            |                  | •           | •              | ٠            |                  |

| ATH18/22   | 3.3 V / 5 V | 22 A             | •             | ٠              | •            | •                | •           | •              | ٠            | •                |

|            | 12 V        | 18 A             | •             | ٠              | •            |                  | •           | •              | ٠            | •                |

| ATL 100/00 | 3.3 V / 5 V | 30 A             | •             | •              | •            | •                | •           | •              | •            | •                |

| ATH26/30   | 12 V        | 26 A             | •             | •              | •            | •                | •           | •              | •            | •                |

For simple point-of-use applications, the ATH06 (6A) provides operating features such as an on/off inhibit, output voltage trim, pre-bias startup (3.3/5-V input only), and over-current protection. The ATH10 (10 A), and ATH12/15 (12/15 A) include an output voltage sense, and margin up/down controls. Then the higher output current, ATH18/22 (18/22A) and ATH26/30 (26/30A) products incorporate over-temperature shutdown protection. All of the products referenced in Table 3-1 include Auto-Track<sup>TM</sup>.

This is a feature unique to the ATH family, and was specifically designed to simplify the task of sequencing the supply voltage in a power system. These and other features are described in the following sections.

#### **Power-Up Characteristics**

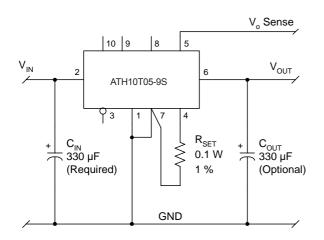

When configured per their standard application all the ATH products will produce a regulated output voltage following the application of a valid input source voltage. All the modules include soft-start circuitry. This slows the initial rate in which the output voltage can rise, thereby limiting the amount of in-rush current that can be drawn from the input source. The soft-start circuitry also introduces a short time delay (typically 5 ms-10 ms) into the power-up characteristic. This delay is from the point that a valid input source is recognized, to the initial rise of the output voltage. Figure 3-1 shows the power-up characteristic of the 22-A output product (ATH22T05-9xx), operating from a 5-V input bus and configured for a 3.3-V output. The waveforms were measured with a 5-A resistive load. The initial rise in input current when the input voltage first starts to rise is the charge current drawn by the input capacitors.

Figure 3-1

#### **Over-Current Protection**

For protection against load faults, all modules incorporate output over-current protection. Applying a load that exceeds the regulator's over-current threshold will cause the regulated output to shut down. Following shutdown a module will periodically attempt to recover by initiating a soft-start power-up. This is described as a "hiccup" mode of operation, whereby the module continues in a cycle of successive shutdown and power up until the load fault is removed. During this period, the average current flowing into the fault is significantly reduced. Once the fault is removed, the module automatically recovers and returns to normal operation.

# ATH Series of Wide-Output Adjust Power Modules (3.3/5-V Input)

#### **Output On/Off Inhibit**

For applications requiring output voltage on/off control, each series of the ATH family incorporates an output *Inhibit* control pin. The inhibit feature can be used wherever there is a requirement for the output voltage from the regulator to be turned off.

The power modules function normally when the *Inhibit* pin is left open-circuit, providing a regulated output whenever a valid source voltage is connected to  $V_{in}$  with respect to GND.

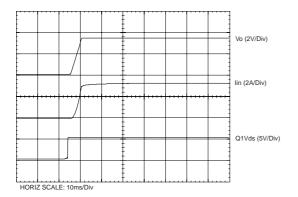

Figure 3-2 shows the typical application of the inhibit function. Note the discrete transistor ( $Q_1$ ). The *Inhibit* control has its own internal pull-up to  $V_{in}$  potential. The input is not compatible with TTL logic devices. An open-collector (or open-drain) discrete transistor is recommended for control.

Turning  $Q_1$  on applies a low voltage to the *Inhibit* control pin and disables the output of the module. If  $Q_1$  is then turned off, the module will execute a soft-start power-up sequence. A regulated output voltage is produced within 20 msec. Figure 3-3 shows the typical rise in both the output voltage and input current, following the turn-off of  $Q_1$ . The turn off of  $Q_1$  corresponds to the rise in the waveform,  $Q_1$   $V_{ds}$ . The waveforms were measured with a 5-A load.

Figure 3-2

Figure 3-3

#### **Remote Sense**

The ATH10, ATH12/15, ATH18/22, and ATH26/30 products incorporate an output voltage sense pin,  $V_o$  Sense. The  $V_o$  Sense pin should be connected to  $V_{out}$  at the load circuit (see data sheet standard application). A remote sense improves the load regulation performance of the module by allowing it to compensate for any 'IR' voltage drop between itself and the load. An IR drop is caused by the high output current flowing through the small amount of pin and trace resistance. Use of the remote sense is optional. If not used, the  $V_o$  Sense pin can be left open-circuit. An internal low-value resistor (15- $\Omega$  or less) is connected between the  $V_o$  Sense and  $V_{out}$ . This ensures the output voltage remains in regulation.

With the sense pin connected, the difference between the voltage measured directly between the  $V_{out}$  and GND pins, and that measured from  $V_o$  Sense to GND, is the amount of IR drop being compensated by the regulator. This should be limited to a maximum of 0.3 V.

Note: The remote sense feature is not designed to compensate for the forward drop of non-linear or frequency dependent components that may be placed in series with the converter output. Examples include OR-ing diodes, filter inductors, ferrite beads, and fuses. When these components are enclosed by the remote sense connection they are effectively placed inside the regulation control loop, which can adversely affect the stability of the regulator.

#### Over-Temperature Protection

The ATH18/22 and ATH26/30 series of products have over-temperature protection. These products have an on-board temperature sensor that protects the module's internal circuitry against excessively high temperatures. A rise in the internal temperature may be the result of a drop in airflow, or a high ambient temperature. If the internal temperature exceeds the OTP threshold, the module's *Inbibit* control is automatically pulled low. This turns the output off. The output voltage will drop as the external output capacitors are discharged by the load circuit. The recovery is automatic, and begins with a soft-start power up. It occurs when the the sensed temperature decreases by about 10 °C below the trip point.

Note: The over-temperature protection is a last resort mechanism to prevent thermal stress to the regulator. Operation at or close to the thermal shutdown temperature is not recommended and will reduce the long-term reliability of the module. Always operate the regulator within the specified Safe Operating Area (SOA) limits for the worst-case conditions of ambient temperature and airflow.

### **Application Notes**

# ATH Series of Wide-Output Adjust Power Modules (3.3/5-V Input)

#### **Auto-Track<sup>™</sup> Function**

The Auto-Track<sup>TM</sup> function is unique to the ATH family, and is available with the all "Point-of-Load Alliance" (POLA) products. Auto-Track<sup>TM</sup> was designed to simplify the amount of circuitry required to make the output voltage from each module power up and power down in sequence. The sequencing of two or more supply voltages during power up is a common requirement for complex mixed-signal applications, that use dual-voltage VLSI ICs such as DSPs, micro-processors, and ASICs.

#### How Auto-Track<sup>TM</sup> Works

Auto-Track<sup>TM</sup> works by forcing the module's output voltage to follow a voltage presented at the Track control pin. This control range is limited to between 0 V and the module's set-point voltage. Once the track-pin voltage is raised above the set-point voltage, the module's output remains at its set-point <sup>1</sup>. As an example, if the Track pin of a 2.5-V regulator is at 1 V, the regulated output will be 1 V. But if the voltage at the Track pin rises to 3 V, the regulated output will not go higher than 2.5 V.

When under track control, the regulated output from the module follows the voltage at its Track pin on a volt-for-volt basis. By connecting the Track pin of a number of these modules together, the output voltages will follow a common signal during power-up and power-down. The control signal can be an externally generated master ramp waveform, or the output voltage from another power supply circuit <sup>3</sup>. The Track control also incorporates an internal RC charge circuit. This operates off the module's input voltage to produce a suitable rising waveform at power up.

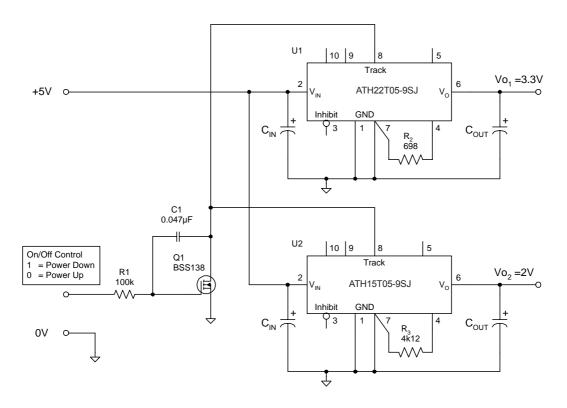

#### Typical Application

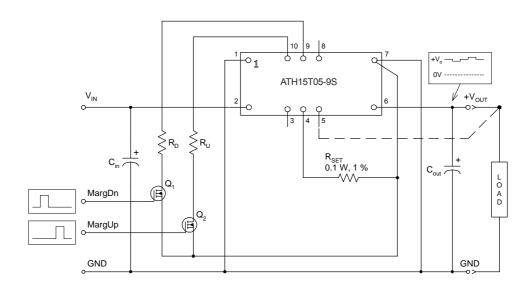

The basic implementation of Auto-Track<sup>TM</sup> allows for simultaneous voltage sequencing of a number of Auto-Track<sup>TM</sup> compliant modules. Connecting the Track control pins of two or more modules forces the Track control of all modules to follow the same collective RC ramp waveform, and allows them to be controlled through a single transistor or switch;  $Q_1$  in Figure 3-4.

To initiate a power-up sequence, it is recommended that the Track control be first pulled to ground potential. This should be done at or before input power is applied to the modules, and then held for at least 10 ms thereafter. This brief period gives the modules time to complete their internal soft-start initialization. Applying a logic-level high signal to the circuit's On/Off Control turns  $Q_1$  on and applies a ground signal to the Track pins. After completing their internal soft-start intialization, the output of all modules will remain at zero volts while  $Q_1$  is on.

10 ms after a valid input voltage has been applied to the modules,  $Q_1$  may be turned off. This allows the track control voltage to automatically rise toward to the modules' input voltage. During this period the output voltage of

each module will rise in unison with other modules, to its respective set-point voltage.

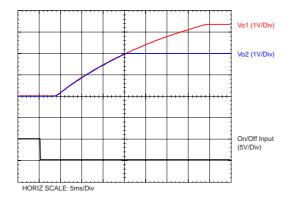

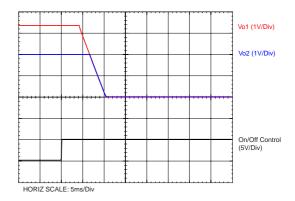

Figure 3-5 shows the output voltage waveforms from the circuit of Figure 3-4 after the On/Off Control is set from a high to a low-level voltage. The waveforms,  $Vo_1$  and  $Vo_2$  represent the output voltages from the two power modules,  $U_1$  (3.3 V) and  $U_2$  (2.0 V) respectively.  $Vo_1$  and  $Vo_2$  are shown rising together to produce the desired simultaneous power-up characteristic.

The same circuit also provides a power-down sequence. Power down is the reverse of power up, and is accomplished by lowering the track control voltage back to zero volts. The important constraint is that a valid input voltage must be maintained until the power down is complete. It also requires that  $Q_1$  be turned off relatively slowly. This is so that the Track control voltage does not fall faster than Auto-Track's slew rate capability, which is 5 V/ms. The components  $R_1$  and  $C_1$  in Figure 3-4 limit the rate at which  $Q_1$  can pull down the Track control voltage. The values of 100 k-ohm and 0.047  $\mu$ F correlate to a decay rate of about 0.6 V/ms.

The power-down sequence is initiated with a low-to-high transition at the On/Off Control input to the circuit. Figure 3-6 shows the power-down waveforms. As the Track control voltage falls below the nominal set-point voltage of each power module, then its output voltage decays with all the other modules under Auto-Track<sup>TM</sup> control.

#### Notes on Use of Auto-Track<sup>TM</sup>

- 1. The Track pin voltage must be allowed to rise above the module's set-point voltage before the module can regulate at its adjusted set-point voltage.

- 2. The Auto-Track  $^{\text{TM}}$  function will track almost any voltage ramp during power up, and is compatible with ramp speeds of up to 5 V/ms.

- 3. The absolute maximum voltage that may be applied to the Track pin is  $V_{\rm in}$ .

- 4. The module will not follow a voltage at its Track control input until it has completed its soft-start initialization. This takes about 10 ms from the time that the module has sensed that a valid voltage has been applied its input. During this period, it is recommended that the Track pin be held at ground potential.

- 5. Once its soft-start initialization is complete, the module is capable of both sinking and sourcing current when following the voltage at the Track pin.

- 6. The Auto-Track<sup>TM</sup> function can be disabled by connecting the *Track* pin to the input voltage  $(V_{in})$  through a 1-k $\Omega$  resistor. When Auto-Track<sup>TM</sup> is disabled, the output voltage will rise faster following the application of input power.

\*\*Auto-Track is a trademark of Texas Instruments, Inc.

### **Application Notes**

# ATH Series of Wide-Output Adjust Power Modules (3.3/5-V Input)

Figure 3-4; Sequenced Power Up & Power Down Using Auto-Track

Figure 3-5; Simultaneous Power Up with Auto-Track Control

Figure 3-6; Simultaneous Power Down with Auto-Track Control

# ATH Series of Wide-Output Adjust Power Modules (3.3/5-V Input)

#### **Margin Up/Down Controls**

The ATH10 (10A), ATH12/15 (12/15A), ATH18/22 (18/22A) and ATH26/30 (26/30A) products incorporate *Margin Up* and *Margin Down* control inputs. These controls allow the output voltage to be momentarily adjusted <sup>1</sup>, either up or down, by a nominal 5 %. This provides a convenient method for dynamically testing the operation of the load circuit over its supply margin or range. It can also be used to verify the function of supply voltage supervisors. The  $\pm 5$  % change is applied to the adjusted output voltage, as set by the external resistor,  $R_{\rm set}$  at the  $V_0$  *Adjust* pin.

The 5 % adjustment is made by pulling the appropriate margin control input directly to the *GND* terminal <sup>2</sup>. A low-leakage open-drain device, such as an n-channel MOSFET or p-channel JFET is recommended for this purpose <sup>3</sup>. Adjustments of less than 5 % can also be accommodated by adding series resistors to the control inputs (See Figure 3-4). The value of the resistor can be selected from Table 3-2, or calculated using the following formula.

#### Up/Down Adjust Resistance Calculation

To reduce the margin adjustment to something less than 5 %, series resistors are required (See  $R_D$  and  $R_U$  in Figure 3-7). For the same amount of adjustment, the resistor value calculated for  $R_U$  and  $R_D$  will be the same. The formulas is as follows.

$$R_{\rm U}$$

or  $R_{\rm D}$ =  $\frac{499}{\Delta\%}$  - 99.8  $k\Omega$

Where  $\Delta\%$  = The desired amount of margin adjust in percent.

#### Notes:

- 1. The *Margin Up\** and *Margin Dn\** controls were not intended to be activated simultaneously. If they are their affects on the output voltage may not completely cancel, resulting in the possibility of a slightly higher error in the output voltage set point.

- 2. The ground reference should be a direct connection to the module GND at pin 7 (pin 1 for the ATH06). This will produce a more accurate adjustment at the load circuit terminals. The transistors Q<sub>1</sub> and Q<sub>2</sub> should be located close to the regulator.

- 3. The Margin Up and Margin Dn control inputs are not compatible with devices that source voltage. This includes TTL logic. These are analog inputs and should only be controlled with a true open-drain device (preferably a discrete MOSFET transistor). The device selected should have low off-state leakage current. Each input sources 8 μA when grounded, and has an open-circuit voltage of 0.8 V.

Table 3-2; Margin Up/Down Resistor Values

| % Adjust | $R_U/R_D$                 |  |

|----------|---------------------------|--|

| 5        | $0.0~\mathrm{k}\Omega$    |  |

| 4        | $24.9 \text{ k}\Omega$    |  |

| 3        | 66.5 kΩ                   |  |

| 2        | $150.0  \mathrm{k}\Omega$ |  |

| 1        | $397.0 \mathrm{k}\Omega$  |  |

Figure 3-7; Margin Up/Down Application Schematic

# ATH Series of Wide-Output Adjust Power Modules (3.3/5-V Input)

#### **Pre-Bias Startup Capability**

Only selected products in the ATH family incorporate this capability. Consult Table 3-1 to identify which products are compliant.

A pre-bias startup condition occurs as a result of an external voltage being present at the output of a power module prior to its output becoming active. This often occurs in complex digital systems when current from another power source is backfed through a dual-supply logic component, such as an FPGA or ASIC. Another path might be via clamp diodes as part of a dual-supply power-up sequencing arrangement. A prebias can cause problems with power modules that incorporate synchronous rectifiers. This is because under most operating conditions, these types of modules can sink as well as source output current.

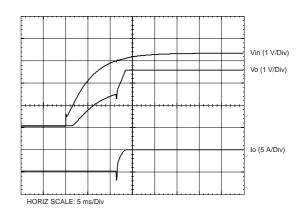

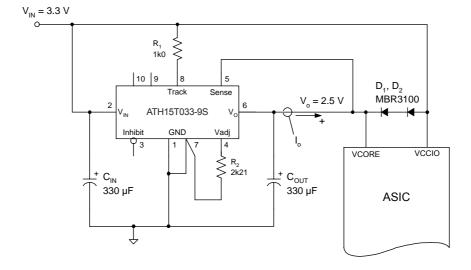

The ATH family of power modules incorporate synchronous rectifiers, but will not sink current during startup  $^1$ , or whenever the *Inhibit* pin is held low. However, to ensure satisfactory operation of this function, certain conditions must be maintained.  $^2$  Figure 3-7 shows an application demonstrating the pre-bias startup capability. The startup waveforms are shown in Figure 3-9. Note that the output current from the ATH15T033-9xx ( $I_0$ ) shows negligible current until its output voltage rises above that backfed through diodes  $D_1$  and  $D_2$ .

Note: The pre-bias start-up feature is not compatible with Auto-Track. When the module is under Auto-Track control, it is fully active and will sink current if the output voltage is below that of a back-feeding source. Therefore to ensure a pre-bias hold-off, one of two approaches must be followed when input power is applied to the module. The Auto-Track function must either be disabled 3, or the module's output held off using the Inhibit pin. The latter allows Auto-Track's internal (RC) voltage ramp to rise above the set-point voltage.

#### Notes

- 1. Startup is the relatively short period (approx. 10 ms) prior to the output voltage rising. The startup period immediately follows either the application of a valid input source voltage, or the release of a ground signal at the *Inhibit* pin.

- 2. To ensure that the regulator does not sink current when power is first applied (even with a ground signal applied to the *Inhibit* control pin), the input voltage <u>must</u> always be greater than the output voltage <u>throughout</u> the power-up and power-down sequence.

- 3. The Auto-Track function can be disabled at power up by immediately applying a voltage to the module's *Track* pin that is greater than its set-point voltage. This can be easily accomplished by connecting the *Track* pin to V<sub>in</sub> through a 1-kΩ resistor.

Figure 3.9; Pre-Bias Startup Waveforms

Figure 3.8; Application Circuit Demonstrating Pre-Bias Startup

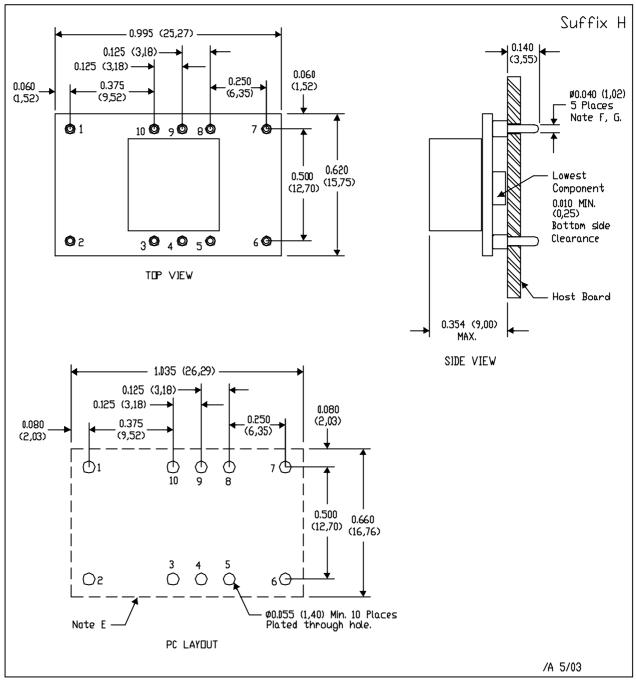

### EUW (R-PDSS-T10)

### DOUBLE SIDED MODULE

NOTES:

- All linear dimensions are in inches (nm).

This drawing is subject to change without notice.

2 place decimals are ±0.030 (±0,76mm).

3 place decimals are ±0.010 (±0,25mm). В.

- E. Recommended keep but area for user components

- Pins are 0.040" (1,02) diameter with 0.070" (1,78) diameter standoff shoulder.

- F. All pins: Material Copper Alloy Finish - Tin (100%) over Nickel plate

SHEET 2 SCALE 2.5X SIZE

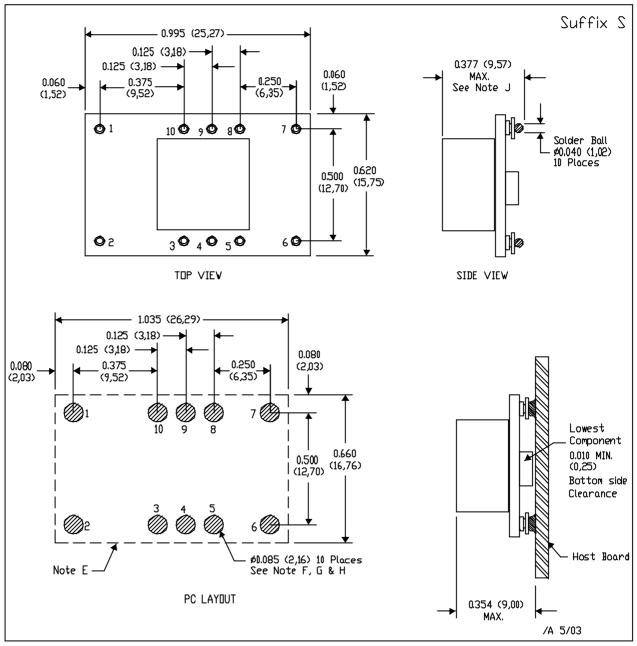

### EUY (R-PDSS-B10)

### DOUBLE SIDED MODULE

NOTES: A.

- All linear dimensions are in inches (mm). This drawing is subject to change vithout notice.

- 2 place decimals are ±0.03D (±0,76mm).

- 3 place decimals are ±0.010 (±0,25mn). Recommended keep out area for user components.

- F. Power pin connection should utilize two or more vias to the interior power plane of 0.025 (0,63) I.D. per input,

J. Dimension prior to reflow solder. ground and output pin (or the electrical equivalent).

- G. Paste screen opening: 0.080 (2,03) to 0.085 (2,16). Paste screen thickness: 0.006 (0,15).

- H. Pad type: Solder mask defined.

- I. All pins: Material Copper Allby

Finish - Tin (100%) over Nickel plate Solder Ball - See product data sheet,

SHEET SCALE 2.5 X SIZE