# KH104 DC to 1.1GHz Linear Amplifier

### Features

- -3dB bandwidth of 1.1GHz

- 325psec rise and fall times

- 14dB gain, 50Ω input and output

- Low distortion, linear phase

- 1.4:1 VSWR (output, DC-1.1GHz)

- Direct replacement for CLC104

### **Applications**

- Digital and wideband analog communications

- Radar, IF and RF processors

- Fiber optic drivers and receivers

- Photomultiplier preamplifiers

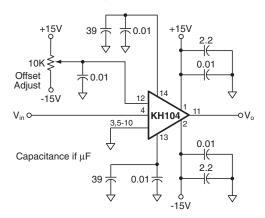

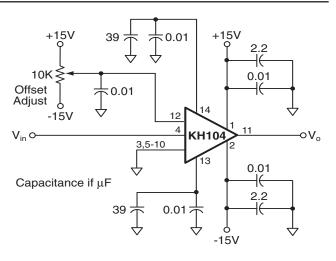

### **Basic Circuit Diagram**

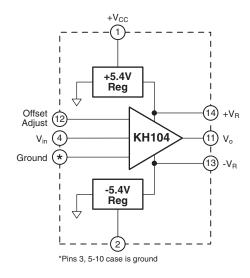

## Equivalent Circuit Diagram

### **General Description**

The KH104 linear amplifier represents a significant advance in linear amplifiers. Proprietary design techniques have yielded an amplifier with 14dB of gain and a -3dB bandwidth of DC to 1100MHz. Gain flatness to 750MHz of ±0.4dB coupled with excellent VSWR and phase linearity gives outstanding pulse fidelity and low signal distortion.

Designed for  $50\Omega$  systems, the KH104 is very easy to use, requiring only properly bypassed power supplies for operation. This translates to time and cost savings in all stages of design and production.

Fast rise time, low overshoot and linear phase make the KH104 ideal for high speed pulse amplification. These properties plus low distortion combine to produce an amplifier well suited to many communications applications. With a 1.1GHz bandwidth, the KH104 can handle the fastest digital traffic, even when the demodulation scheme or the digital coding format requires that DC be maintained. It is also ideal for traditional video amplifier applications such as radar or wideband analog communications systems.

These same characteristics make the KH104 an excellent choice for use in fiber optics systems, on either the transmitting or receiving end of the fiber. The low group delay distortion insures that pulse integrity will be maintained. As a photomultiplier tube preamp, its fast response and quick overload recovery provide for superior system performance.

The KH104 is constructed using thin film resistor/ bipolar transistor technology, and is available in the following versions:

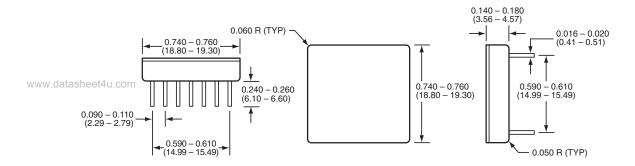

### KH104AI -25°C to +85°C 14-pin double-wide DIP

# KH104 Electrical Characteristics (T<sub>A</sub> = +25°C, V<sub>CC</sub> = ±15V, R<sub>L</sub> = 50Ω, R<sub>s</sub> = 50Ω; unless specified)

| PARAMETERS                                                                                                                                                                                                                                                                                                                    | CONDITIONS                                                                                                                     | ТҮР                                                      | MIN & MAX RATINGS    |                                | UNITS                                                | SYM                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|--------------------------------|------------------------------------------------------|------------------------------|

| Ambient Temperature                                                                                                                                                                                                                                                                                                           | KH104AI                                                                                                                        | +25°C                                                    | Min                  | Max                            |                                                      |                              |

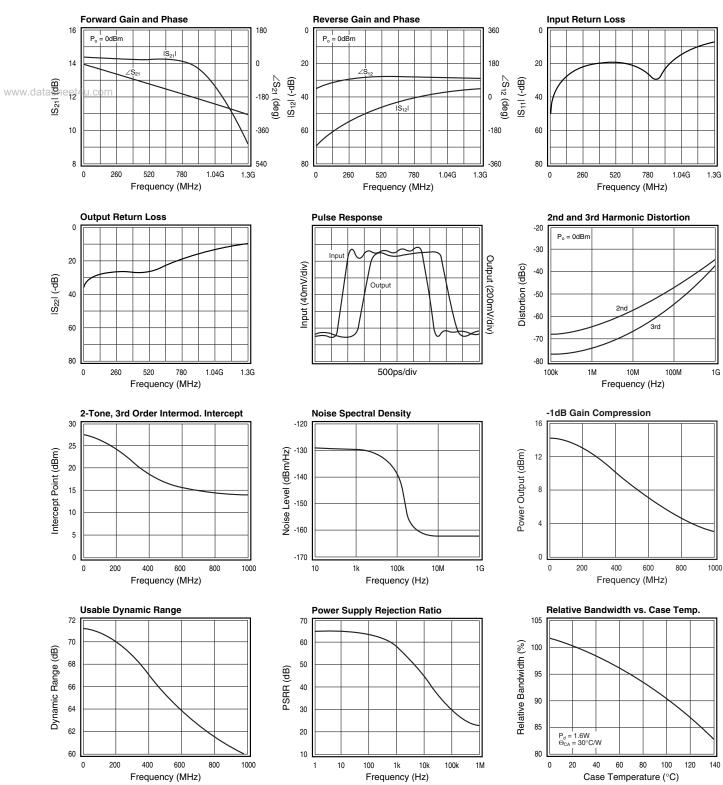

| FREQUENCY DOMAIN RESPONSE<br>+ -3dB bandwidth<br>+ gain flatness<br>linear phase deviation<br>group delay                                                                                                                                                                                                                     | 0dBm out<br>10dBm out<br>@ 100MHz<br>DC - 750MHz<br>DC - 600MHz                                                                | 1100<br>1050<br>14.2<br>±0.4<br>1.5<br>600               | 1000<br>13.8<br>-0.6 | 14.9<br>+0.6<br>3              | MHz<br>MHz<br>dB<br>dB<br>°<br>ps                    | SSBW<br>SSBW<br>LPD<br>GD    |

| reverse isolation<br>input return loss<br>output return loss                                                                                                                                                                                                                                                                  | DC - 750MHz<br>750MHz - 1100MHz<br>DC - 750MHz<br>750MHz - 1100MHz<br>DC - 750MHz<br>750MHz - 1100MHz                          | 40<br>35<br>18<br>11<br>17<br>10                         |                      |                                | dB<br>dB<br>dB<br>dB<br>dB<br>dB                     | RINI<br>RIIN                 |

| TIME DOMAIN RESPONSE<br>rise and fall time<br>(10% to 90%)<br>settling time to 0.8%<br>overshoot<br>overload recovery                                                                                                                                                                                                         | 1V step<br>2V step<br>1V step<br>1V step<br>V <sub>inpeak</sub> = ±0.5V                                                        | 325<br>375<br>1.2<br>3<br>1.2                            |                      | 375<br>450<br>1.6              | ps<br>ps<br>ns<br>%<br>ns                            | TRS<br>TRL<br>TS<br>OS<br>OR |

| <ul> <li>NOISE AND DISTORTION RESPONS</li> <li>2nd harmonic distortion</li> <li>3rd harmonic distortion</li> <li>2nd harmonic distortion</li> <li>3rd order intermolulation intercept</li> <li>2-tone, 1MHz separation</li> <li>equivalent input noise voltage</li> <li>noise figure</li> <li>usable dynamic range</li> </ul> | E<br>OdBm, 100MHz<br>OdBm, 100MHz<br>10dBm, 100MHz<br>10dBm, 100MHz<br>100MHz<br>500MHz<br>10Hz to 1200MHz<br>100MHz<br>500MHz | 47<br>53<br>40<br>43<br>26<br>17<br>55<br>11<br>71<br>65 | 30<br>35             |                                | -dBc<br>-dBc<br>-dBc<br>+dBm<br>dB<br>dB<br>dB<br>dB | HD2<br>HD3<br>HD2<br>HD3     |

| STATIC, DC PERFORMANCE<br>input bias current<br>input bias current (drift)<br>output offset voltage<br>output offset voltage (drift)<br>* supply current<br>supply rejection ratio                                                                                                                                            | note 2<br>note 2<br>note 3<br>no load<br>1KHz                                                                                  | 80<br>0.6<br>50<br>375<br>54<br>55                       |                      | 280<br>2.0<br>250<br>625<br>60 | μΑ<br>μΑ/°C<br>mV<br>μV/°C<br>mA<br>dB               | IBN<br>IBN<br>ICC<br>PSRR    |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

### **Absolute Maximum Ratings**

| Notes |

|-------|

|-------|

$\begin{array}{ccc} V_{CC} & \pm 9V \mbox{ to } \pm 16V \\ I_o & \pm 40mA \\ \mbox{input voltage} & \pm 0.5V \\ \mbox{junction temperature} & +175^{\circ}C \\ \mbox{operating temperature} & AI: & -25^{\circ}C \mbox{ to } +85^{\circ}C \\ \mbox{storage temperature} & -65^{\circ}C \mbox{ to } +150^{\circ}C \end{array}$

1. Nominal gain only - gain variation over temperature is ±0.1dB.

2. Input offset voltage = (input bias current) x ( $R_s \parallel 50\Omega$ ).

3. Output offset can be adjusted to zero with an external potentiometer – see "Reducing DC Offset".

4. \* AI 100% tested at 25°C.

+ AI Sample tested at 25°C.

# KH104 Performance Characteristics ( $T_A = +25^{\circ}C$ , $V_{CC} = \pm 15V$ , $R_L = 50\Omega$ , $R_s = 50\Omega$ ; unless specified)

#### PC Board Layout Considerations

Proper layout of printed circuit boards is important to achieve optimum performance of a circuit operating in the 1GHz frequency range. Use of microstripline is recommended for all signal-carrying paths and low resistance, low inductance signal return and bypass paths should be used. To keep the impedance of "these paths low, use as much ground plane as possible. Ground plane also serves to increase the flow of heat out of the package.

The KH104 has three types of connections: signal paths (input and output), DC inputs (supplies and offset adjust), and grounds.  $50\Omega$  microstrip is recommended for connection to the input (pin 4) and output (pin 11). Microstrip on a doublesided PC board consists of a ground plane on one side of the board and a constant-width signal-carrying trace on the other side of the board. For 1/16" G10 or FR-4 PC board material, a 0.1" wide trace will have a  $50\Omega$  characteristic impedance. The ground plane beneath the signal trace must extend at least one trace width on either side of the trace. Also, all traces (including ground) should be kept at least one trace width from the signal carrying traces.

To keep power supply noise and oscillations from appearing at the amplifier output, all supply pins should be capacitively bypassed to ground. The power supply pins (1 and 2) are the inputs to a pair of voltage regulators whose outputs are at pins 13 and 14. It is recommended that 0.01µF or larger ceramic capacitors be connected from pins 1, 2, 13 and 14 to ground, within 0.2" of the pins. A 1µF or larger solid tantalum capacitor to ground is required within 3" of pins 1 and 2, and for good low frequency performance, solid tantalum capacitors of at least 15µF should be connected from pins 13 and 14 to ground within 3" of the pins. Use 0.025" or wider traces for the supply lines. The offset adjust pin (12) also requires by passing; a  $0.01\mu$ F or larger ceramic capacitor to ground within 0.2" of the pin is recommended.

Grounding is the final layout consideration. Pins 3 and 5-10 should all be connected to a ground plane which should cover as much of one side of the board around the amplifier as possible.

#### **Reducing DC Offset**

DC offset of the KH104 may be adjusted by applying a DC voltage to the amplifier's offset adjust pin (12). The simplest method is shown in Figure 1. Using this method of offset adjust it is possible to vary the output offset by approximately ±400mV. This simple adjustment has no effect on the offset drift characteristics of the KH104.

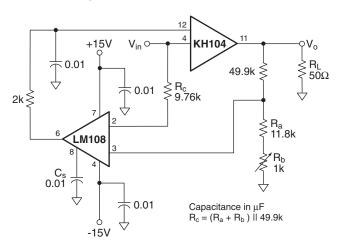

If lower offset and offset drift are required, a low frequency op amp may be used in conjunction with the KH104 in a composite configuration. The suggested circuit appears in Figure 2. Its method of operation is to compare an attenuated version of the output signal to the input signal and apply a correcting voltage at the offset adjust pin. A compensation capacitor C<sub>s</sub> reduces the bandwidth of the op amp correction circuit to limit the op amp's effect on the KH104 to frequencies below f<sub>45</sub>, the frequency at which the op amp has 45dB of open loop gain. Using an LM108, f<sub>45</sub> is about 7Hz with C<sub>s</sub> =  $0.1\mu$ F. Thus the op amp can correct DC and low frequency errors below f<sub>45</sub>, without affecting KH104 performance above f<sub>45</sub>. Also note that the noise performance of the op amp will dominate below f<sub>45</sub>.

**Figure 2: Composite Amplifier**

With an LM108 op amp in this composite configuration, input offset is typically 2mV and drift is 15mV/°C. At frequencies well below  $f_{45}$ , the composite gain is equal to  $(1\,+\,49.9k/(R_a\,+\,R_b))$  and the output impedance is

very low. As the signal frequency increases beyond  $f_{45}$ , the op amp loses influence and the KH104 gain and output impedance dominate. To ensure a smooth transition and matched gain at all frequencies, adjust  $R_b$  for a minimum op amp output swing with a 0.1V<sub>pp</sub> sinewave input (to the KH104) at the frequency  $f_{45}$ . Since the KH104 has a 50 $\Omega$  output impedance, its www.doutput4voltage is a function of the load impedance ( $A_v \simeq 10R_L/(R_L + 50)$ ), whereas the gain of the composite amplifier at low frequencies and DC is relatively independent of the load impedance, due to the high open-loop gain of the op amp. Thus, to avoid gain mismatching and phase non-linearity, use the composite amplifier only if the load impedance is constant from DC to at least 10( $f_{45}$ ).

Use of a composite amplifier reduces input offset voltage and its corresponding drift, but has no effect on input bias current. This current is converted to an input voltage by the resistance to ground seen at the amplifier input and the voltage appears, amplified, at the output. Typical input offset voltage due to the bias current is 2mV and input offset drift is approximately 15mV/°C.

#### **Thermal Considerations**

The KH104 case must be maintained at or below 140°C. Note that because of the amplifier design, power dissipation remains fairly constant, independent of the load or drive level. Therefore, standard derating is not possible. There are two ways to keep the case temperature low. The first is to keep the amount of power dissipated inside the package to a minimum and the second is to get the heat out of the package quickly by reducing the thermal resistance from case to ambient.

A large portion of the heat dissipated inside the package is in the voltage regulators. At the minimum +9V supply level the regulators dissipate 390mW and at the maximum  $\pm 16V$  supply level they dissipate 1.2W.

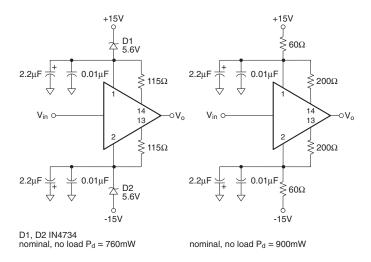

The amplifier itself dissipates a fairly constant 600mW (55mA x 10.8V). Reducing the power dissipation of the internal regulators will go far towards reducing the internal junction temperatures without impacting the so performance. Reducing either the input supply voltages (on pins 1 and 2) and/or shunting the regulator current through external resistors (from pins 1 to 14 and pins 2 to 13) are both effective means towards significantly reducing the internal power dissipation. A minimum

voltage across the regulator of 3.6V and a minimum regulator current of 10mA will satisfy the regulator dropout voltage and current limits.

Given the maximum anticipated power supply voltages, the shunt resistor should be calculated to yield a 35mA current from that voltage to the regulated voltage of 5.4V. This will leave 10mA through the regulator at the minimum quiescent current of 45mA. The regulator input voltages may be reduced directly by dropping the voltage supplies, or, if that option is not available, using either a zener or resistive dropping element in series with the supply. If a series dropping element is used, the decoupling capacitors must appear on pins 1 and 2 of the KH104. Figure 3 shows two possible power reduction circuits from fixed  $\pm 15$ V supplies.

Several methods of decreasing the thermal resistance from case to ambient are possible. With no heat paths other than still air at 25°C, the thermal resistance from case to ambient for the KH104 is about 40°C/W. When placed in a printed circuit board with all ground pins soldered into a ground plane 1" X 1.5", the thermal resistance drops to about 30°C/W In this configuration, the case rise will be 30°C for 9V supplies and 50°C for 16V supplies. This results in maximum allowable ambient temperatures of 110°C and 90°C, respectively. If higher operating temperatures are required, heat sinking of the package is recommended.

**Figure 3: Reducing Power Dissipation**

### **KH104 Package Dimensions**

Life Support Policy

Cadeka's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Cadeka Microcircuits, Inc. As used herein:

1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Cadeka does not assume any responsibility for use of any circuitry described, and Cadeka reserves the right at any time without notice to change said circuitry and specifications as here to change said circuitry and specifications and cadeka reserves the right at any time without notice to change said circuitry and specifications and cadeka reserves the right at any time without notice to change said circuitry and specifications and cadeka reserves the right at any time without notice to change said circuitry and specifications and cadeka reserves the right at any time without notice to change said circuitry and specifications and cadeka reserves the right at any time without notice to change said circuitry and specifications and cadeka reserves the right at any time without notice to change said circuitry and specifications and cadeka reserves the right at any time without notice to change said circuitry and specifications and cadeka reserves the right at any time without notice to change said circuitry and specifications and cadeka reserves the right at any time without notice to change said circuitry and specifications and cadeka reserves the right at any time without notice to change said circuitry and specifications and cadeka reserves the right at any time without notice to change said circuitry and specifications at a specification a