## NEC NEC Electronics Inc.

### VR4400SC (µPD30411) 64-Bit RISC Microprocessor: Primary/Secondary Cache Memory

### **Preliminary Information**

November 1993

### Description

The VR4400SC™ is a 64-bit RISC microprocessor with the enhancement version of R4000 architecture. It delivers excellent processing solutions in a wide variety of applications.

Two other versions of the RISC microprocessor are compared with the VR4400SC below.

VR4400PC™ VR4400SC™ On-chip primary cache

On-chip primary cache and secondary cache support

VR4400MC™

Same as VR4400SC plus multiprocessing capability

System applications range from inexpensive highly integrated desktop systems through large multiprocessor servers whose CPU performance rivals current mainframes and whose address space requirements are not by current generation microprocessors.

The VR4400SC microprocessor provides complete application software compatibility with the MIPS R2000, R3000, and R6000 microprocessors. The RISC/os and RISC compilers and thousands of application programs that run on the MIPS architecture augment this powerful family of processors and provide a complete solution to a large number of processing needs. In addition, an array of development tools supports R4000-based applications

High integer performance, as well as floating-point performance, has been achieved through techniques such as superpipelining, on-chip caches, a pipelined floating-point unit, two-level cache memory, and a high-performance on-chip translation lookaside buffer (TLB).

The cache and memory management unit (MMU) can handle large address space tasks and a large number of users. These features allow the design of balanced systems, suitable not only for technical and graphics applications but also for commercial applications like transaction processing with fault tolerant support,

The 64-bit wide on-chip cache path, 64-bit on-chip FPU, 64-bit integer registers, and 64-bit virtual address space provide a compatible, timely, and necessary path from 32-bit to true 64-bit computing for users and software developers. Compatibility with existing 32-bit application code is maintained; however, an efficient mix of 32-bit and 64-bit programs can run on the same VR4400SC machine.

The 64-bit addressing capability of the VR4400SC microprocessor supports operating systems with extensive file mapping-allowing direct access to files without explicit I/O calls-and paves the way for nextgeneration video technology and documentation with high-quality photographs. In addition, CAD applications with huge databases of complex structures, geographic information systems, and technical number crunching applications with large data sets will benefit greatly from this addressing capability.

The other enhancements of the VR4400SC are (1) fully functional status pins and (2) a cache error bit (EW) added to the cache error register.

#### **Features**

- ☐ True 64-bit microprocessor with 64-bit integer and floating-point operations, registers, and virtual addresses

- □ Fully compatible with earlier 32-bit MIPS microprocessors

- Dual instruction issue with no restrictions on the type of instruction issued

- □ 50-, 67-, or 75-MHz Master Clock (100-, 133-, or 150-MHz internal clock)

- 3.3- or 5-volt power supply

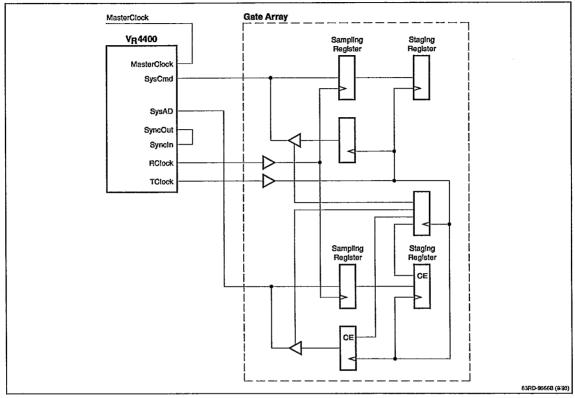

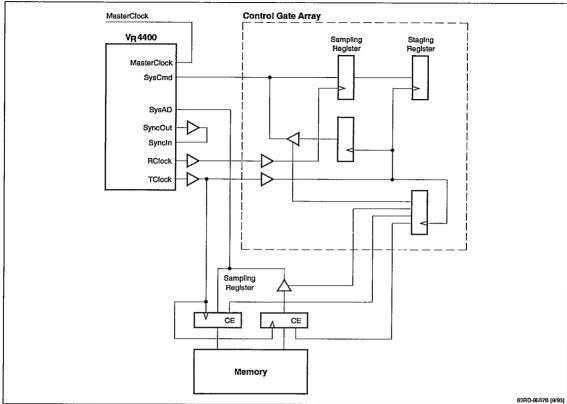

- On-chip 16-Kbyte instruction cache, 16-Kbyte data cache, and 128-bit secondary cache interface support

- On-chip memory management unit containing a fully associative TLB whose entries have a variable page size ranging from 4 Kbytes to 16 Mbytes

- On-chip ANSI/IEEE-754 standard floating-point unit with precise exceptions

- 32 doubleword (64-bit) general-purpose registers and 16 doubleword (64-bit) floating-point registers

- 36-bit physical address accessing 64 Gbytes of physical memory

- Dynamically configurable big-endian or littleendian byte ordering

50630-1

**Ordering Information**

-75

150 MHz

### VR4400SC (µPD30411)

- ☐ Timing flexibility for 128-bit secondary cache interface and 64-bit system interface to allow speed matching of logic and memory components

- □ System interface clock modes: divide-by-2, -3, -4,

- □ Master/checker mode

- One-level deep uncached store buffers

VR4400PC, VR4400SC, and VR4400MC are trademarks of NEC Corporation.

| Part Number    | PClock     | Power<br>Supply                     | Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| μPD30411RJ-50  | 100 MHz    | •                                   | 447-pin ceramic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -67            | 133 MHz    | -                                   | PGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -75            | 150 MHz    | _                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| μPD30411RP-50  | 100 MHz    |                                     | 447-pin ceramic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -67            | 37 133 MHz | PGA with heat-sink<br>adapter plate |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -75            | 150 MHz    | •                                   | and provide the control of the contr |

| μPD30411LRJ-50 | 100 MHz    | 3.3 V                               | 447-pin ceramic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -67            | 133 MHz    | _                                   | PGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -75            | 150 MHz    | -                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| μPD30411LRP-50 | 100 MHz    | 3.3 V                               | 447-pin ceramic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -67 1          | 133 MHz    | -                                   | PGA with heat-sink<br>adapter plate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

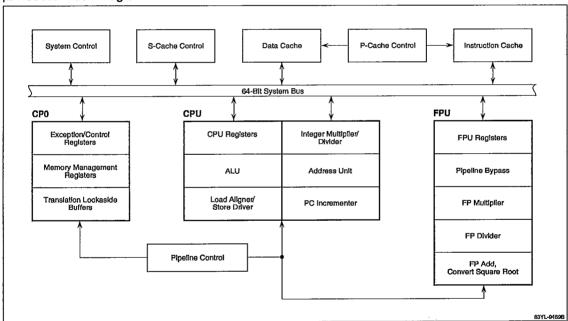

### μPD30411 Block Diagram

VR4400SC (µPD30411)

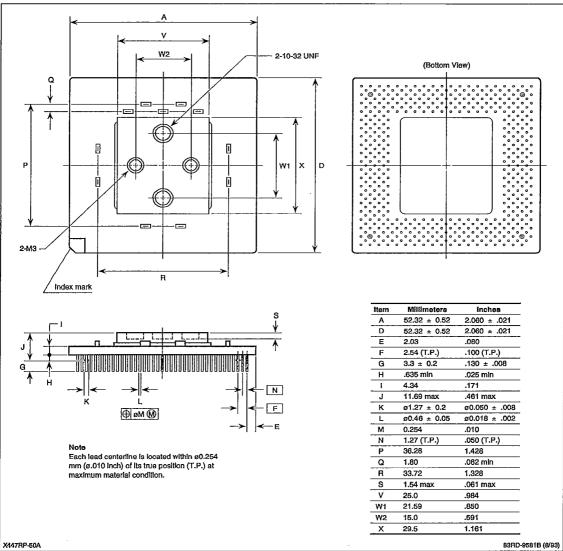

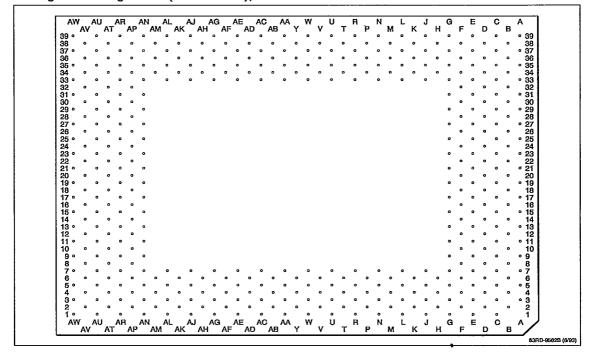

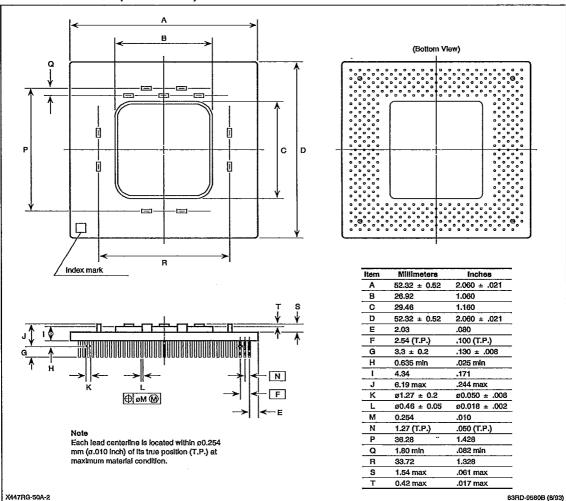

Package Pin Configuration (Bottom View); 447-Pin PGA

**NEC**

Pin Assignments; System Address/Data, System Command, Clock and Control

| System<br>Address/Data                                        | Pin<br>No.                                                                | System<br>Address/Data                                        | Pin<br>No.                                                               | System<br>Command                               | Pin<br>No.                                               | Clock and<br>Control                                                                      | Pin<br>No.                                                               |

|---------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| SysAD0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9           | T2<br>M2<br>J3<br>G3<br>C1<br>A3<br>A9<br>A13<br>A21<br>A25               | SysAD40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49 | A23<br>A27<br>A31<br>A35<br>C37<br>E39<br>H38<br>M38<br>AE1<br>AJ1       | SysCmd0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | G1<br>E3<br>B2<br>B12<br>B16<br>B20<br>B24<br>B28<br>B32 | ColdReset ExtRqst GndP GndSense Into IOIn IOOut MasterClock MasterCut ModeClock           | AW37<br>AV2<br>Y34<br>U37<br>AL1<br>AV32<br>AV28<br>AA37<br>AJ39<br>B8   |

| SysAD10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19 | A29<br>A33<br>B38<br>E37<br>G39<br>L39<br>AD2<br>AH2<br>AL3<br>AN3        | SysAD50<br>51<br>52<br>53<br>54<br>55<br>56<br>57<br>58<br>59 | AM2<br>AR1<br>AU3<br>AW5<br>AW11<br>AW15<br>AW23<br>AW27<br>AW31<br>AW35 | SysCmdP                                         | A37                                                      | Modeln NMI RClock0 RClock1 RdRdy Release Reset SyncIn SyncOut TClock0                     | AV8<br>AV16<br>AM34<br>AL33<br>AW7<br>AV12<br>AU39<br>W39<br>AN39<br>H34 |

| SysAD20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29 | AU1<br>AW3<br>AW9<br>AW13<br>AW21<br>AW25<br>AW29<br>AW33<br>AV38<br>AR37 | SysAD60<br>61<br>62<br>63                                     | AU37<br>AR39<br>AL39<br>AG39                                             |                                                 |                                                          | TClock1 ValidIn ValidOut V <sub>DD</sub> Ok V <sub>DD</sub> P V <sub>DD</sub> Sense WrRdy | J33<br>AN1<br>AR3<br>AE39<br>AA33<br>W33<br>A7                           |

| SyeAD30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39 | AM38<br>AH38<br>RI<br>LI<br>H2<br>EI<br>C3<br>A5<br>A11<br>A15            | SysADC0<br>1<br>2<br>3<br>4<br>5<br>6<br>7                    | A17<br>R39<br>AW17<br>AD38<br>A19<br>T38<br>AW19<br>AC39                 | JTAG<br>JTCK<br>JTDI<br>JTDO<br>JTMS            | U39<br>N39<br>J39<br>G37                                 | Status0<br>Status1<br>Status2<br>Status3<br>Status4<br>Status5<br>Status6<br>Status7      | U33<br>U35<br>V36<br>W35<br>W37<br>AC37<br>AC33<br>AC33                  |

Pin Assignments; Secondary Cache Data

| No.  |                                                                                                                                      |                                                                                                                                                                                                                                                                                | 1          | 1    | 1          | 1    |

|------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------------|------|

|      | Cache Data                                                                                                                           | No.                                                                                                                                                                                                                                                                            | Cache Data | No.  | Cache Data | No.  |

| R3   | SCData40                                                                                                                             | C23                                                                                                                                                                                                                                                                            | SCData80   | AC7  | SCData120  | AR21 |

| R7   | 41                                                                                                                                   | F24                                                                                                                                                                                                                                                                            | 81         | AE5  | 121        | AP24 |

| L.5  | 42                                                                                                                                   | E27                                                                                                                                                                                                                                                                            | 82         | AG7  | 122        | AU27 |

| F8   | 43                                                                                                                                   | D30                                                                                                                                                                                                                                                                            | 83         | AR5  | 123        | AT30 |

| C9   | 44                                                                                                                                   | C33                                                                                                                                                                                                                                                                            | 84         | AR9  | 124        | AU33 |

| F12  | 45                                                                                                                                   | E35                                                                                                                                                                                                                                                                            | 85         | AR11 | 125        | AN33 |

| G15  | 46                                                                                                                                   | L35                                                                                                                                                                                                                                                                            | 86         | AN15 | 126        | AL37 |

| E17  | 47                                                                                                                                   | R33                                                                                                                                                                                                                                                                            | 87         | AP16 | 127        | AG33 |

| G21  | . 48                                                                                                                                 | AF4                                                                                                                                                                                                                                                                            | 88         | AU21 |            |      |

| C25  | 49                                                                                                                                   | AJЗ                                                                                                                                                                                                                                                                            | 89         | AN23 |            |      |

| G25  | SCData50                                                                                                                             | AJ7                                                                                                                                                                                                                                                                            | SCData90   | AR25 | SCDChk0    | G19  |

| E29  | 51                                                                                                                                   | AP8                                                                                                                                                                                                                                                                            | 91         | AP28 | 1          | T34  |

| G31  | 52                                                                                                                                   | AT10                                                                                                                                                                                                                                                                           | 92         | AU31 | 2          | AP20 |

| C35  | 53                                                                                                                                   | AR13                                                                                                                                                                                                                                                                           | 93         | AR33 | 3          | AD34 |

| K36  | 54                                                                                                                                   | AR15                                                                                                                                                                                                                                                                           | 94         | AL35 | 4          | C19  |

| N35  | 55                                                                                                                                   | AT18                                                                                                                                                                                                                                                                           | 95         | AH34 | 5          | R37  |

| AE3  | 56                                                                                                                                   | AU23                                                                                                                                                                                                                                                                           | 96         | U7   | 6          | AU19 |

| AG5  | 57                                                                                                                                   | AT26                                                                                                                                                                                                                                                                           | 97         | N3   | 7          | AE37 |

| AK4  | 58                                                                                                                                   | AR27                                                                                                                                                                                                                                                                           | 98         | N7   | 8          | C17  |

| AN9  | 59                                                                                                                                   | AN29                                                                                                                                                                                                                                                                           | 99         | C5   | 9          | N37  |

| AU9  | SCData60                                                                                                                             | AP32                                                                                                                                                                                                                                                                           | SCData100  | E9   | SCDChk10   | AU17 |

| AN13 | 61                                                                                                                                   | AN35                                                                                                                                                                                                                                                                           | 101        | C11  | 11         | AG37 |

|      | 62                                                                                                                                   | AJ35                                                                                                                                                                                                                                                                           | 102        |      | 12         | E19  |

|      | 63                                                                                                                                   | AE33                                                                                                                                                                                                                                                                           |            |      | 13         | R35  |

| AT22 | 64                                                                                                                                   | V4                                                                                                                                                                                                                                                                             | 104        | E21  | 14         | AR19 |

|      | 65                                                                                                                                   | R5                                                                                                                                                                                                                                                                             |            |      |            | AE35 |

| AN27 | 66                                                                                                                                   | N5                                                                                                                                                                                                                                                                             |            |      |            |      |

|      | 67                                                                                                                                   | E5                                                                                                                                                                                                                                                                             |            |      |            |      |

|      |                                                                                                                                      |                                                                                                                                                                                                                                                                                |            |      | 1          |      |

| AR35 | 69                                                                                                                                   | E11                                                                                                                                                                                                                                                                            | 109        | G33  |            | 1    |

| AK36 | SCData70                                                                                                                             | G13                                                                                                                                                                                                                                                                            | SCData110  | J37  |            |      |

| AG35 | 71                                                                                                                                   | D14                                                                                                                                                                                                                                                                            | 111        | N33  | İ          |      |

| T6   | 72                                                                                                                                   | C21                                                                                                                                                                                                                                                                            | 112        | AD6  |            |      |

| L3   | 73                                                                                                                                   | D22                                                                                                                                                                                                                                                                            | 113        | AG3  |            |      |

| L7   | 74                                                                                                                                   | E25                                                                                                                                                                                                                                                                            | 114        | AJ5  | 1          | ŀ    |

| E7   | 75                                                                                                                                   | G27                                                                                                                                                                                                                                                                            | 115        | AU5  | 1          |      |

|      |                                                                                                                                      |                                                                                                                                                                                                                                                                                |            |      | 1          |      |

|      |                                                                                                                                      |                                                                                                                                                                                                                                                                                |            |      |            |      |

|      |                                                                                                                                      |                                                                                                                                                                                                                                                                                |            |      |            | l    |

|      |                                                                                                                                      |                                                                                                                                                                                                                                                                                |            |      |            |      |

|      | L5 F8 C9 F12 G15 E17 G21 C25 G25 E29 G31 C35 K36 N35 AE3 AG5 AK4 AN9 AN13 AT14 AR17 AT22 AU25 AN27 AR29 AN31 AR35 AK36 AG36 T6 L3 L7 | L5 42 F8 43 C9 44 F12 45 G15 46 E17 47 G21 48 C25 49  G25 51 G31 52 C35 53 K36 54 N35 55 AE3 56 AG5 57 AK4 58 AN9 59  AU9 SCData60 AN13 61 AT14 62 AR17 63 AT22 64 AU25 65 AN27 66 AR29 67 AN21 68 AR35 69  AK36 SCData70 AG35 71 T6 72 L3 73 L7 74 E7 75 G11 76 E13 77 E15 78 | L5         | L5   | L5         | L5   |

Pin Assignments; Secondary Cache Address, Tag, and Control

| Secondary<br>Cache Data                      | Pin<br>No.                                                  | Secondary<br>Cache Tag                                  | Pin<br>No.                                                             | Secondary<br>Cache Control                             | Pin<br>No.                             |  |

|----------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------|--|

| SCAdd1<br>2<br>3<br>4<br>5<br>6<br>7<br>8    | AL5<br>AG1<br>AE7<br>AC1<br>AC5<br>AC3<br>AA1<br>AB4<br>AA5 | SCTag0<br>1 2<br>3 4<br>5 6<br>7 8                      | K4<br>G7<br>C7<br>D10<br>C15<br>D18<br>F20<br>E23<br>D26               | SCDCS<br>SCOE<br>SCTCS<br>SCWW<br>SCWX<br>SCWY<br>SCWZ | M6<br>N1<br>J1<br>J5<br>J7<br>H6<br>G5 |  |

| 10                                           | AA7                                                         | 9                                                       | C29                                                                    |                                                        |                                        |  |

| SCAddr11<br>12<br>13<br>14<br>15<br>16<br>17 | AA3<br>W3<br>Y6<br>W5<br>W7<br>W1<br>U3                     | SCTag10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | G29<br>E33<br>G35<br>L33<br>L37<br>P36<br>AF36<br>AJ37<br>AJ33<br>AN37 |                                                        |                                        |  |

| SCAddr0W<br>X<br>Y<br>Z                      | AN7<br>AN5<br>AM6<br>AL7                                    | SCTag20<br>21<br>22<br>23<br>24                         | AU35<br>AR31<br>AU29<br>AN25<br>AR23                                   |                                                        |                                        |  |

| SCAPar0<br>1<br>2                            | U5<br>U1<br>P4                                              | SCTChk0<br>1<br>2<br>3<br>4<br>5                        | AN21<br>AN19<br>AU15<br>AP12<br>AU7<br>AR7<br>AH6                      |                                                        |                                        |  |

Pin Assignments; V<sub>DD</sub>, GND, and NC (No Connection)

| $V_{DD}$                               | GND                                    | NC         |

|----------------------------------------|----------------------------------------|------------|

| A39                                    | B4, B14, B22, B30, B36                 |            |

| B6, B10, B18, B26, B34                 | D2, D6, D12, D20, D28, D34, D38        | Y2         |

| D4, D8, D16, D24, D32, D36             | F4, F6, F10, F18, F26, F34, F36        | AV24       |

| F2, F14, F22, F30, F38                 | K2, K34                                | AA35, AA39 |

| H4, H36                                | M4, M36                                |            |

| K6, K38                                | P6, P38                                |            |

| P2, P34                                | V2, V34                                |            |

| T4, T36                                | Y4, Y36                                |            |

| V6, V38; Y38                           | AB6, AB36, AB38; AF2, AF34             |            |

| AB2, AB34; AD4, AD36; AF6, AF38        | AH4, AH36                              |            |

| AK2, AK34; AM4, AM36                   | AK6, AK38                              |            |

| AP2, AP10, AP18, AP26, AP38            | AP4, AP6, AP14, AP22, AP30, AP34, AP36 |            |

| AT4, AT8, AT16, AT24, AT32. AT36       | AT2, AT6, AT12, AT20, AT28, AT34, AT38 |            |

| AV6, AV14, AV22, AV30, AV34; AW1, AW39 | AV4, AV10, AV18, AV26, AV36            |            |

|                                        |                                        |            |

## VR4400SC (µPD30411)

| Interface Signals | Symbol      | Input/Output | Description                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System            | ExtRqst     | Input        | External Request is asserted by the external agent to request use of the system interface. The processor grants the request by asserting Release.                                                                                                                                                                                                                                  |

|                   | Release     | Output       | Release responds to the assertion of ExtRqst. The processor asserts Release, signalling to the requesting device that the system interface is available.                                                                                                                                                                                                                           |

|                   | FidRdy      | Input        | Read Ready is asserted by the external agent to indicate that it car accept processor read, invalidate, or update requests in both secondary cache and non-secondary cache mode; or it can accept a read followed by a write request, a read followed by a potential update request, or a read followed by a potential update followed by a write request in secondary cache mode. |

|                   | SysAD(63:0) | Input/Output | System Address and Data Bus is a 64-bit bus for communication between the processor and the external agent.                                                                                                                                                                                                                                                                        |

|                   | SysADC(7:0) | Input/Output | System Address and Data Check Bus is an 8-bit bus that contains check bits for the SysAD bus.                                                                                                                                                                                                                                                                                      |

|                   | SysCmd(8:0) | Input/Output | System Command and Data Identifier is a 9-bit bus for transmission between the processor and the external agent.                                                                                                                                                                                                                                                                   |

|                   | SysCmdP     | Input/Output | System Command and Data Identifier Bus Parity is a single, even-<br>parity bit for the SysCmd bus.                                                                                                                                                                                                                                                                                 |

|                   | Validín     | Input        | Valid Input is asserted by the external agent when it is driving a valid address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus.                                                                                                                                                                                                                |

|                   | ValidOut    | Output       | Valid Out is a signal the processor asserts to indicate that it is driving a valid address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus.                                                                                                                                                                                                      |

|                   | WrRdy       | Input        | Write Ready is asserted by the external agent when it can accept a processor write request.                                                                                                                                                                                                                                                                                        |

| Clock/Control     | Fault       | Output       | Fault is asserted by the processor to indicate a mismatch output or<br>boundary comparators and an indication of system interface input<br>parity or ECC errors.                                                                                                                                                                                                                   |

|                   | iOln        | Input        | I/O Input is the output slew-rate control feedback loop input. (See IOOut.)                                                                                                                                                                                                                                                                                                        |

|                   | lOOut       | Output       | I/O Output is the output slew-rate control feedback loop output. It must be connected to IOIn through a delay loop that models the I/O path from the processor to the external agent.                                                                                                                                                                                              |

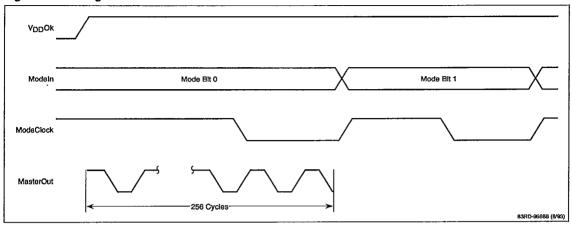

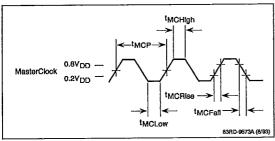

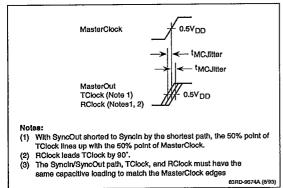

|                   | MasterClock | Input        | Master Clock is the primary clock input to establish the processor operating frequency.                                                                                                                                                                                                                                                                                            |

|                   | MasterOut   | Output       | Master Clock Output is aligned with Master Clock.                                                                                                                                                                                                                                                                                                                                  |

|                   | RClock(1:0) | Output       | Receive Clooks 1 and 0 are identical clocks that establish the system interface frequency.                                                                                                                                                                                                                                                                                         |

|                   | Status(7:0) | Output       | Status7 through Status0 indicate the current operational status of the processor.                                                                                                                                                                                                                                                                                                  |

| Interface Signals       | Symbol                              | Input/Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------|-------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

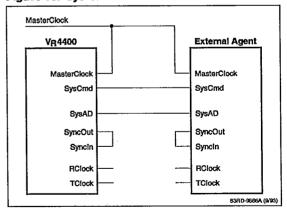

| Clock/Control<br>(cont) | SyncOut                             | Output       | Synchronization Clock Out is a signal to model the interconnect between MasterOut, TClock, RClock, and the external agent. It must be connected to Syncin through an interconnect.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                         | Syncin                              | Input        | Synchronization Clock Input is the input of the synchronization clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                         | TClock(1:0)                         | Output       | Transmit Clocks 1 and 0 are identical clocks that establish the system interface frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                         | V <sub>DD</sub> P                   | Input        | V <sub>DD</sub> P is quiet V <sub>DD</sub> to the internal phase-locked loop (PLL).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                         | V <sub>DD</sub> Sense               | Input/Output | V <sub>DD</sub> Sense Is a special pin used only in component testing and characterization. It provides a separate, direct connection from the on-chip V <sub>DD</sub> node to the package pin without connecting to the in-package power planes. Testing fixtures treat V <sub>DD</sub> Sense as an analog output pin; the voltage at this pin directly exhibits the behavior of the on-chip V <sub>DD</sub> . Thus, characterization engineers can easily observe the effects of di/dt noise, transmission line reflections, etc. V <sub>DD</sub> Sense should be connected to V <sub>DD</sub> in functional system designs |

|                         | GndP                                | Input        | Quiet Ground is directed to the internal phase-locked loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                         | GndSense                            | Input/Output | Ground Sense provides a separate, direct connection from the on-<br>chip ground node to a package pin without having to connect to<br>the in-package ground planes. GndSense should be connected to<br>Gnd in functional system designs.                                                                                                                                                                                                                                                                                                                                                                                      |

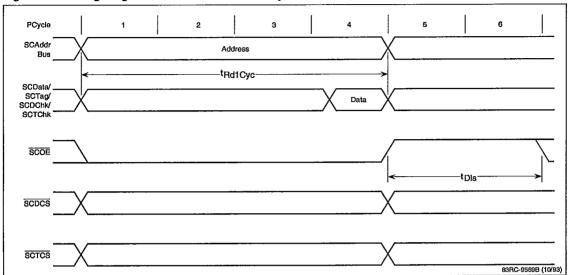

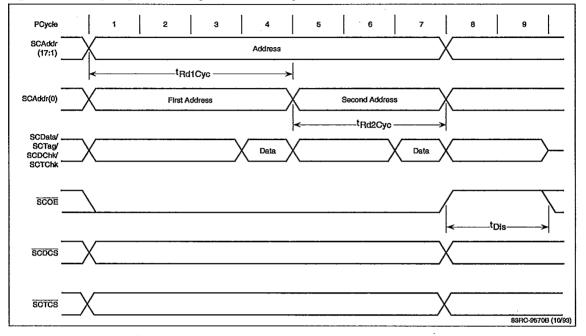

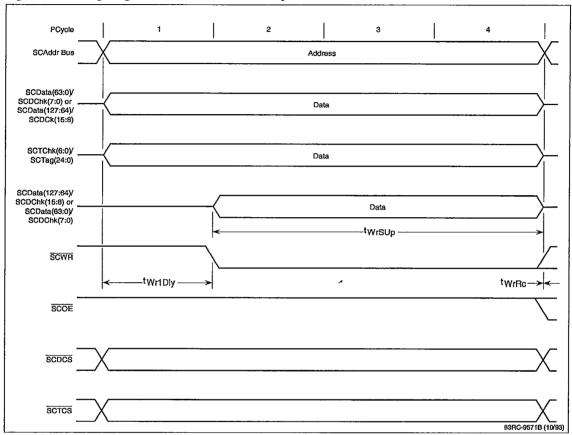

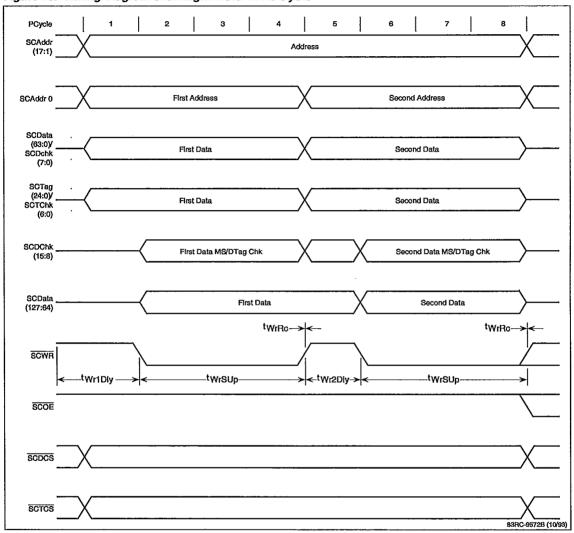

| Secondary Cache         | SCAddr (17:1),<br>SCAddr0 (W:Z)     | Output       | Secondary Cache Address Bus is an 18-bit address bus for the secondary cache. The least significant bit (bit 0) has four output lines, SCAddr0 (W, X, Y, Z), to provide additional drive current.                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                         | SCAPar(2:0)                         | Output       | Secondary Cache Address Parity Bus is a 3-bit bus that carries the parity of the SCAddr bus and the cache control line SCWr. Below are the individual bit definitions.  Even parity for SCAddr(17:12) and SCWr.  Even parity for SCAddr(11:6) and SCDCS.  Even parity for SCAddr(5:0) and SCTCS.                                                                                                                                                                                                                                                                                                                              |

|                         | SCData(127:0)                       | Input/Output | Secondary Cache Data Bus is a 128-bit bus used to read and write cache data from and to the secondary cache data RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

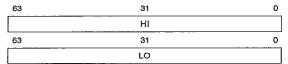

|                         | SCDChk(15:0)                        | Input/Output | Secondary Cache Data ECC Bus is a 16-bit bus carrying two 8-bit ECC fields that cover the 128 bits of SCData from/to secondary cache.  SCDChk(15:8) corresponds to SCData(127:64).  SCDChk(7:0) corresponds to SCData(63:0).                                                                                                                                                                                                                                                                                                                                                                                                  |

|                         | SCDCS                               | Output       | Secondary Cache Data Chip Select is a signal for the secondary cache data RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | SCOE                                | Output       | Secondary Cache Output Enable is a signal for the secondary cache data and tag RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                         | SCTag(24:0)                         | Input/Output | Secondary Cache Tag Bus is a 25-bit bus used to read or write cache tags from and to the secondary cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                         | SCTChk(6:0)                         | Input/Output | Secondary Cache Tag ECC Bus is a 7-bit bus carrying an ECC field covering the SCTag from and to the secondary cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                         | SCTCS                               | Output       | Secondary Cache Tag Chip Select is a signal for the secondary cache tag RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                         | SCWrW,<br>SCWrX,<br>SCWrY,<br>SCWrZ | Output       | Secondary Cache Write Enables are signals for the secondary cache RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

### VR4400SC (µPD30411)

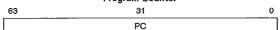

### Pin Descriptions (cont)