## V96BMC Rev. D

# HIGH PERFORMANCE BURST DRAM CONTROLLER

#### FOR i960Cx/Hx/Jx<sup>®</sup> PROCESSORS

- Pin/Software compatible with earlier V96BMC.

- Direct interfaces to i960Cx/Hx/Jx processors.

- 3.3V DRAM interface support.

- Near SRAM performance achieved with DRAM.

- Supports up to 512Mb of DRAM.

older versions of the device.

- Interleaved or non-interleaved operation.

- Supports symmetric and non-symmetric arrays.

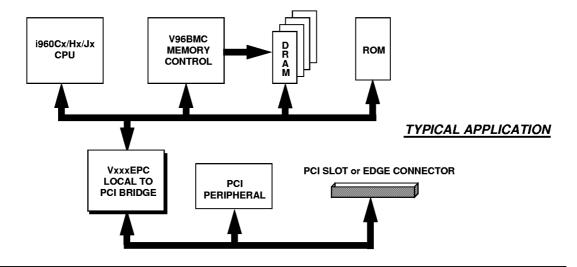

The V96BMC Revision D Burst DRAM Controller is an enhanced version of the previous V96BMC with improved timing and provides dedicated Power and Ground rails to support the increasingly popular 3.3V DRAM modules. Timing parameters are also improved over the

The V96BMC provides the DRAM access protocols, buffer signals, data multiplexer signals, and bus timing resources required to work with DRAM. By using the V96BMC, system designers can replace tedious design work, expensive FPGAs and valuable board space with a single, high-performance, easily configured device. The processor interface of the V96BMC implements the bus protocol of the i960Cx/Hx/Jx. The pin naming convention has been duplicated on the V96BMC; simply wire like-named pins together to create the interface.

The V96BMC supports a total DRAM memory subsystem size of 512Mbytes. The array may be

- Software-configured operational parameters.

- Integrated Page Cache Management.

- 2Kbyte burst transaction support.

- On chip memory address multiplexer/drivers.

- Two 24-bit timers, 8-bit bus watch timer.

- Up to 40MHz operation.

- · Low cost 132-pin PQFP package.

organized as 1 or 2 leafs of 32-bits each. Standard memory sizes of 256Kbit to 64Mbit devices are supported and 8, 16, and 32-bit accesses are allowed. The V96BMC takes advantage of Fast Page Mode or EDO DRAMs and row comparison logic to achieve static RAM performance using dynamic RAMs. Control signals required for optional external data path buffers/latches are also provided by the V96BMC. The V96BMC provides an 8-bit bus watch timer to detect and recover from accesses to unpopulated memory regions. Two 24-bit counters/timers can supply an external interrupt signal at a constant frequency relative to the system clock. The V96BMC is packaged in a low-cost 132-pin PQFP package and is available in 25, 33, or 40MHz versions.

This document contains the product codes, pinouts, package mechanical information, DC characteristics, and AC characteristics for the V96BMC. Detailed functional information is contained in the User's Manual.

V3 Semiconductor retains the rights to change documentation, specifications, or device functionality at any time without notice. Please verify that you have the latest copy of all documents before finalizing a design.

#### 1.0 Product Codes

**Table 1: Product Codes**

| Product Code | Processor    | Bus Type                             | Package      | Frequency |

|--------------|--------------|--------------------------------------|--------------|-----------|

| V96BMC-33LP  | i960Cx/Hx/Jx | 32-bit multiplexed/<br>demultiplexed | 132-pin PQFP | 33MHz     |

| V96BMC-40LP  | i960Cx/Hx/Jx | 32-bit multiplexed/<br>demultiplexed | 132-pin PQFP | 40MHz     |

### 2.0 Pin Description and Pinout

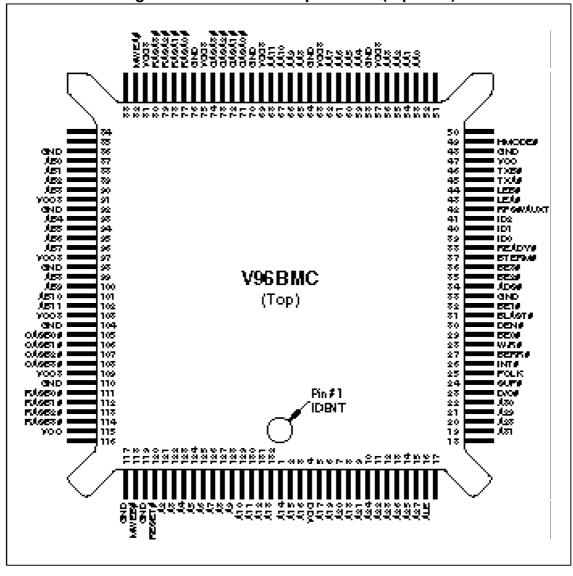

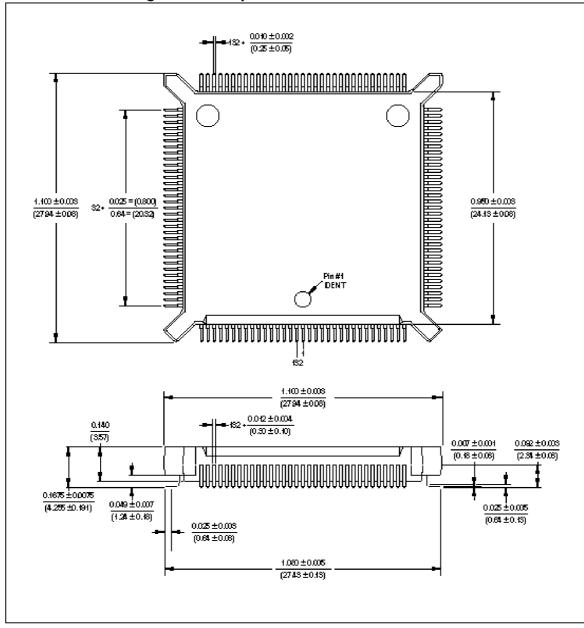

Table 2 below lists the pin types found on the V96BMC. Table 3 describes the function of each pin on the V96BMC. Table 4 lists the pins by pin number. Figure 1 shows the pinout for the 132-pin PQFP package and Figure 2 shows the mechanical dimensions of the package.

Table 2: Pin Types

| Pin Type          | Description                                                                                                                                                                                                                                                                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O <sub>12</sub> | TTL I/O pin with 12 mA output drive                                                                                                                                                                                                                                                                                                       |

| I                 | TTL input only pin                                                                                                                                                                                                                                                                                                                        |

| O <sub>12</sub>   | TTL Output pin with 12 mA output drive                                                                                                                                                                                                                                                                                                    |

| O <sub>12-3</sub> | TTL Output pin with 12 mA output drive that can be configured for either 5 volt or 3.3 volt signaling, These outputs can be configured for 3.3V operation by connecting the Vcc3 power pins to a 3.3V power plane (Vcc should always be connected to a 5V supply). Vcc3 can also be connected to the 5V plane if 5V signaling is desired. |

**Table 3: Signal Descriptions**

|                        | Memory Interface Signals |    |                                                                                                                                                                                                                                                                                                                   |  |  |  |

|------------------------|--------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Signal                 | Туре                     | Rª | Description                                                                                                                                                                                                                                                                                                       |  |  |  |

| AA[11:0]<br>AB[11:0]   | O <sub>12-3</sub>        | Х  | Leaf A and B row and column address, multiplexed on the same pins. When non-interleaved operation is selected, only address bus AA should be used.                                                                                                                                                                |  |  |  |

| RASA[3:0]<br>RASB[3:0] | O <sub>12-3</sub>        | н  | Row Address Strobe. These strobes indicate the presence of a valid row address on busses AA(B)[11:0]. These signals are to be connected one to each 32-bit leaf of memory.                                                                                                                                        |  |  |  |

| CASA[3:0]<br>CASB[3:0] | O <sub>12-3</sub>        | Н  | Column Address Strobe. These strobes latch a column address from AA(B)[11:0]. They are assigned one to each byte in a leaf.                                                                                                                                                                                       |  |  |  |

| MWEA<br>MWEB           | O <sub>12-3</sub>        | Н  | Memory Write Enable. These are the DRAM write strobes. One is supplied for each leaf to minimize signal loading.                                                                                                                                                                                                  |  |  |  |

| RFS/AUXT               | O <sub>12</sub>          | H  | Refresh in progress. This output is multi-function signal. The signal name, as it appears on the logic symbol, is the default signal names. This signal gives notice that a refresh cycle is to be executed. The timing leads RAS only refresh by one cycle. The output may also function as AUX timer interrupt. |  |  |  |

| Configuration |      |   |                                                       |  |

|---------------|------|---|-------------------------------------------------------|--|

| Signal        | Туре | R | Description                                           |  |

| HMODE         | I    |   | Connected to Vcc (for i960Cx) or GND (for i960Hx/Jx). |  |

| Buffer Controls Signals |                 |   |                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------------------|-----------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal                  | Туре            | R | Description                                                                                                                                                                                                                                                                                                                                                         |  |

| TXA<br>TXB              | O <sub>12</sub> | Н | Data Transmit A and B. These outputs are multi-function signals. The signal names, as they appear on the logic symbol, are the default signal names (Mode 0). The purpose of these outputs is to control buffer output enables during data read transactions and, in effect, control the multiplexing of data from each memory leaf onto the i960Cx/Hx/Jx data bus. |  |

| LEA<br>LEB              | O <sub>12</sub> | L | These outputs are mode independent, however, the timing of the signals change for different operational modes. They control transparent latches that hold data transmitted during a write transaction. In modes 0 and 1, the latch controls follow the timing of CAS for each leaf, while in modes 2 and 3 the timing of LEA and LEB is shortened to 1/2 clock.     |  |

|                         |                 |   | Local Bus Interface                                                                                                                                                                                                                                                                                                                                                 |  |

Table 3: Signal Descriptions (cont'd)

| Signal  | Туре            | R | Description                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------|-----------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A[31:2] | ı               |   | Local address bus.                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| ALE     | I               |   | Address Latch Enable: controls a set of transparent latches on the address bus. When asserted high, the address input flows through the latch. When ALE is low, the internal address holds the previous value. With an i960Cx/Hx processor ALE is not typically used and has an internal pull-up resistor that will keep it high when not connected (to provide backward pin compatibility with earlier versions). |  |

| D/C     | I               |   | Data/Code.                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| BE[3:0] | I               |   | Local bus byte write enables.                                                                                                                                                                                                                                                                                                                                                                                      |  |

| W/R     | I               |   | Write/Read.                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| READY   | O <sub>12</sub> | Z | Local Bus data ready.                                                                                                                                                                                                                                                                                                                                                                                              |  |

| ADS     | I               |   | Asserted low to indicate the beginning of a bus cycle                                                                                                                                                                                                                                                                                                                                                              |  |

| DEN     | I               |   | Data Enable. This input is monitored by the Bus Watch Timer to detect a bus access not returning READY.                                                                                                                                                                                                                                                                                                            |  |

| SUP     | I               |   | Indicates supervisor mode. Required for access to configuration registers.                                                                                                                                                                                                                                                                                                                                         |  |

| BLAST   | I               |   | Burst last.                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| BTERM   | O <sub>12</sub> | Z | Burst terminate. (this signal requires a nominal pull up resistor so that the signal is deasserted when RESET goes inactive)                                                                                                                                                                                                                                                                                       |  |

| BERR    | O <sub>12</sub> | Н | Bus Time-out error.                                                                                                                                                                                                                                                                                                                                                                                                |  |

| ĪNT     | O <sub>12</sub> | I | Local interrupt request. This signal is asserted when the 24-bit counter reaches terminal count, and interrupt out is enabled. May be programmed for pulse or level operation.                                                                                                                                                                                                                                     |  |

| RESET   | I               |   | Local bus reset signal.                                                                                                                                                                                                                                                                                                                                                                                            |  |

| PCLK    | I               |   | Local bus clock.                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| ID[2:0] | I               |   | These inputs select the address offset of the configuration registers.                                                                                                                                                                                                                                                                                                                                             |  |

|         |                 |   | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Signal  | Туре            | R | Description                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Vcc     | -               |   | POWER leads intended for external connection to a 5V Vcc plane                                                                                                                                                                                                                                                                                                                                                     |  |

| Vcc3    | -               |   | POWER for DRAM control outputs. Can be connected to 3.3V or 5V.                                                                                                                                                                                                                                                                                                                                                    |  |

|         |                 |   | GROUND leads intended for external connection to a GND plane.                                                                                                                                                                                                                                                                                                                                                      |  |

a.  ${\bf R}$  indicates state during reset.

**Table 4: Pin Assignments**

| PIN# | Signal | PIN# | Signal   | PIN# | Signal | PIN# | Signal           |

|------|--------|------|----------|------|--------|------|------------------|

| 1    | A14    | 34   | ADS      | 67   | AA10   | 100  | AB9              |

| 2    | A15    | 35   | BE2      | 68   | AA11   | 101  | AB10             |

| 3    | A16    | 36   | BE3      | 69   | Vcc3   | 102  | AB11             |

| 4    | Vcc    | 37   | BTERM    | 70   | GND    | 103  | Vcc3             |

| 5    | A17    | 38   | READY    | 71   | CASA0  | 104  | GND              |

| 6    | A19    | 39   | ID0      | 72   | CASA1  | 105  | CASB0            |

| 7    | A20    | 40   | ID1      | 73   | CASA2  | 106  | CASB1            |

| 8    | A18    | 41   | ID2      | 74   | CASA3  | 107  | CASB2            |

| 9    | A21    | 42   | RFS/AUXT | 75   | Vcc3   | 108  | CASB3            |

| 10   | A24    | 43   | LEA      | 76   | GND    | 109  | Vcc3             |

| 11   | A22    | 44   | LEB      | 77   | RASA0  | 110  | GND              |

| 12   | A23    | 45   | TXA      | 78   | RASA1  | 111  | RASB0            |

| 13   | A26    | 46   | TXB      | 79   | RASA2  | 112  | RASB1            |

| 14   | A25    | 47   | Vcc      | 80   | RASA3  | 113  | RASB2            |

| 15   | A27    | 48   | GND      | 81   | Vcc3   | 114  | RASB3            |

| 16   | ALE    | 49   | HMODE    | 82   | MWEA   | 115  | Vcc              |

| 17   | -      | 50   | -        | 83   | -      | 116  | -                |

| 18   | -      | 51   | -        | 84   | -      | 117  | GND <sup>1</sup> |

| 19   | A31    | 52   | -        | 85   | -      | 118  | MWEB             |

| 20   | A28    | 53   | AA0      | 86   | GND    | 119  | GND              |

| 21   | A29    | 54   | AA1      | 87   | AB0    | 120  | RESET            |

| 22   | A30    | 55   | AA2      | 88   | AB1    | 121  | A2               |

| 23   | D/C    | 56   | AA3      | 89   | AB2    | 122  | А3               |

| 24   | SUP    | 57   | Vcc3     | 90   | AB3    | 123  | A4               |

| 25   | PCLK   | 58   | GND      | 91   | Vcc3   | 124  | A5               |

| 26   | ĪNT    | 59   | AA4      | 92   | GND    | 125  | A6               |

| 27   | BERR   | 60   | AA5      | 93   | AB4    | 126  | A7               |

#### V96BMC Rev.D

Table 4: Pin Assignments (cont'd)

| PIN# | Signal | PIN# | Signal | PIN# | Signal | PIN# | Signal |

|------|--------|------|--------|------|--------|------|--------|

| 28   | W/R    | 61   | AA6    | 94   | AB5    | 127  | A8     |

| 29   | BE0    | 62   | AA7    | 95   | AB6    | 128  | A9     |

| 30   | DEN    | 63   | Vcc3   | 96   | AB7    | 129  | A10    |

| 31   | BLAST  | 64   | GND    | 97   | Vcc3   | 130  | A11    |

| 32   | BE1    | 65   | AA8    | 98   | GND    | 131  | A12    |

| 33   | GND    | 66   | AA9    | 99   | AB8    | 132  | A13    |

<sup>1.</sup> We recommend connecting PIN # 117 to GND but it is not a must especially for those who are replacing V96BMC rev D in rev AB socket. (This pin was unconnected in rev AB)

Figure 1: Pinout for 132-pin PQFP (top view)

Figure 2: 132-pin PQFP mechanical details

## 3.0 DC Specifications

**Table 5: Absolute Maximum Ratings**

| Symbol           | Parameter           | Rating                       | Units |

|------------------|---------------------|------------------------------|-------|

| V <sub>CC</sub>  | Supply voltage      | -0.3 to +7                   | V     |

| V <sub>IN</sub>  | DC input voltage    | -0.3 to V <sub>CC</sub> +0.3 | V     |

| I <sub>IN</sub>  | DC input current    | ± 50                         | mA    |

| T <sub>STG</sub> | Storage temperature | -65 to +150                  | °C    |

**Table 6: Guaranteed Operating Conditions**

| Symbol                             | Parameter                                                                       | Rating       | Units |

|------------------------------------|---------------------------------------------------------------------------------|--------------|-------|

| V <sub>CC</sub> , V <sub>CC3</sub> | Supply voltage                                                                  | 4.75 to 5.25 | V     |

| V <sub>CC3</sub>                   | Supply voltage for 3.3 Volt DRAM interface <sup>1</sup> . Vcc is still as above | 3.0 to 3.6   | V     |

| T <sub>A</sub>                     | Ambient temperature range                                                       | 0 to 70      | °C    |

1. For 3.3 Volt DRAM intreface operation.( See also note 8 table 11)

Table 7: DC Operating Specifications Vcc=5Volt and Vcc3=5 Volt

| Symbol                | Description                       | Conditions                                                     | Min                  | Max       | Units |

|-----------------------|-----------------------------------|----------------------------------------------------------------|----------------------|-----------|-------|

| V <sub>IL</sub>       | Low level input voltage           | Vcc = 4.75V                                                    |                      | 0.8       | V     |

| V <sub>IH</sub>       | High level input voltage          | Vcc = 5.25V                                                    | 2.0                  |           | ٧     |

| I <sub>IL</sub>       | Low level input current           | $V_{IN} = GND, V_{CC} = 5.25V$                                 | -10                  |           | μΑ    |

| I <sub>IH</sub>       | High level input current          | $V_{IN} = V_{CC} = 5.25V$                                      |                      | 10        | μΑ    |

| V <sub>OL</sub>       | Low level output voltage          | $V_{IN} = V_{IL} \text{ or } V_{IH}$ $I_{OL} = -12 \text{ mA}$ |                      | 0.4       | V     |

| V <sub>OH</sub>       | High level output voltage         | $V_{IN} = V_{IL} \text{ or } V_{IH}$ $I_{OL} = -12 \text{ mA}$ | V <sub>CC</sub> -1.0 |           | V     |

| l <sub>OZL</sub>      | Low level float input<br>leakage  | $V_{IN} = V_{IL} \text{ or } V_{IH}$<br>$V_O = GND$            | -20                  |           | μΑ    |

| I <sub>OZH</sub>      | High level float input<br>leakage | $V_{IN} = V_{IL} \text{ or } V_{IH}$<br>$V_O = 5.25V$          |                      | 20        | μΑ    |

| I <sub>CC</sub> (max) | Maximum supply current            | Continuous simple access<br>Continuous burst access            |                      | 100<br>30 | mA    |

| C <sub>IO</sub>       | Input and output capacitance      |                                                                |                      | 20        | pF    |

Table 8: DC Operating Specifications Vcc3=3.3 Volt and Vcc=5 Volt

| Symbol                | Description                    | Conditions                                           | Min | Max       | Units |

|-----------------------|--------------------------------|------------------------------------------------------|-----|-----------|-------|

| V <sub>OL</sub>       | Low level output voltage       | V <sub>IN</sub> = Vcc3<br>I <sub>OL</sub> = 12 mA    |     | 0.4       | ٧     |

| V <sub>OH</sub>       | High level output voltage      | $V_{IN} = Vcc3$<br>$I_{OL} = -12 \text{ mA}$         | 2.4 |           | ٧     |

| I <sub>OZL</sub>      | Low level float input leakage  | $V_{IN} = Vcc2$<br>$V_O = GND$                       | -10 |           | μА    |

| I <sub>OZH</sub>      | High level float input leakage | $V_{IN} = V_{IL} \text{ or } V_{IH}$ $V_{O} = 4.46V$ |     | 10        | μА    |

| I <sub>CC</sub> (max) | Maximum supply current         | Continuous simple access Continuous burst access     |     | 140<br>40 | mA    |

## 4.0 AC Specifications

**Table 9: AC Test Conditions**

| Symbol           | Parameter                                                                                  | Limits       | Units |

|------------------|--------------------------------------------------------------------------------------------|--------------|-------|

| Vcc3/Vcc         | Supply voltage                                                                             | 4.75 to 5.25 | V     |

| V <sub>CC3</sub> | Supply voltage when 3.3 Volt DRAM interface operation <sup>1</sup> (Vcc is still as above) | 3.0 to 3.6   | V     |

| V <sub>IN</sub>  | Input low and high voltages                                                                | 0.4 and 4.25 | ٧     |

| C <sub>OUT</sub> | Capacitive load on output and I/O pins                                                     | 50           | pF    |

<sup>1.</sup> For 3.3 Volt DRAM intreface operation.( See also note 8 table 11)

Table 10: Capacitive Derating for Output and I/O Pins

| <b>Output Drive Limit</b> | Supply voltage            | Derating                     |

|---------------------------|---------------------------|------------------------------|

| 12 mA                     | Vcc=5 Volt, Vcc3=3.3 Volt | 0.06 ns/pF for loads > 50 pF |

| 12 mA                     | Vcc=5 Volt, Vcc3=5 Volt   | 0.04 ns/pF for loads > 50 pF |

Table 11: Timing Parameters for V96BMC Vcc=5 Volts +/- 5% and Vcc3= 5 or  $3.3~^8$ Volts +/- 5%

|                   |                                                                |      | 33 MHz               |                   | 40 MHz               |                   |       |

|-------------------|----------------------------------------------------------------|------|----------------------|-------------------|----------------------|-------------------|-------|

| Symbol            | Description                                                    | Note | Min                  | Max               | Min                  | Max               | Units |

| t <sub>C</sub>    | PCLK period                                                    |      | 30                   |                   | 25                   |                   | ns    |

| t <sub>СН</sub>   | PCLK high time                                                 |      | 12                   |                   | 11                   |                   | ns    |

| t <sub>CL</sub>   | PCLK low time                                                  |      | 12                   |                   | 11                   |                   | ns    |

| t <sub>SU</sub>   | Synchronous input setup                                        |      | 9                    |                   | 8                    |                   | ns    |

| t <sub>H</sub>    | Synchronous input hold                                         |      |                      | 1                 |                      | 0.5               | ns    |

| t <sub>H</sub>    | Synchronous input hold (RESET#)                                |      |                      | 3                 |                      | 3                 | ns    |

| t <sub>RZH</sub>  | READY 3-state to valid delay                                   | 1    | 3                    | 13                | 3                    | 10                | ns    |

| t <sub>RHL</sub>  | READY synchronous assertion delay                              |      | 3                    | 13                | 3                    | 11                | ns    |

| t <sub>RLH</sub>  | READY synchronous de-assertion delay                           |      | 3                    | 13                | 3                    | 11                | ns    |

| t <sub>RHZ</sub>  | READY valid to 3-state delay                                   | 1    | 3                    | 10                | 3                    | 7                 | ns    |

| t <sub>BHL</sub>  | BTERM synchronous assertion delay                              |      | 3                    | 14                | 3                    | 12                | ns    |

| t <sub>BLH</sub>  | BTERM synchronous de-assertion delay                           |      | 3                    | 13                | 3                    | 11                | ns    |

| t <sub>EHL</sub>  | BERR synchronous assertion delay                               |      | 3                    | 13                | 3                    | 11                | ns    |

| t <sub>ELH</sub>  | BERR synchronous de-assertion delay                            |      | 3                    | 12                | 3                    | 10                | ns    |

| t <sub>IHL</sub>  | INT synchronous assertion delay                                |      | 3                    | 13                | 3                    | 11                | ns    |

| t <sub>ILH</sub>  | INT synchronous de-assertion delay                             |      | 3                    | 12                | 3                    | 10                | ns    |

| t <sub>ARA1</sub> | Address Input to Row Address output delay (Interleaved)        |      | 3                    | 14                | 3                    | 12                | ns    |

| t <sub>ARA2</sub> | Address Input to Row Address output delay (Non-interleaved)    |      | 4                    | 18                | 4                    | 15                | ns    |

| t <sub>RAH</sub>  | Row address hold from RAS assertion                            | 2    | t <sub>M</sub>       | t <sub>M</sub> +2 | t <sub>M</sub>       | t <sub>M</sub> +2 | ns    |

| t <sub>CAV</sub>  | Column address valid from RAS assertion                        | 2    | t <sub>M</sub> +1    | t <sub>M</sub> +4 | t <sub>M</sub> +1    | t <sub>M</sub> +4 | ns    |

| t <sub>CAH</sub>  | Column address hold from CAS assertion                         |      | t <sub>C</sub>       |                   | t <sub>C</sub>       |                   | ns    |

| t <sub>BCAV</sub> | Column address valid delay from previous CAS assertion (Burst) |      |                      | t <sub>C</sub> +3 |                      | t <sub>C</sub> +3 | ns    |

| t <sub>RHL</sub>  | PCLK to RAS asserted delay                                     |      | 3                    | 13                | 3                    | 11                | ns    |

| t <sub>RLH</sub>  | PCLK to RAS de-asserted delay                                  |      | 3                    | 13                | 3                    | 11                | ns    |

| t <sub>RAS</sub>  | RAS pulse width                                                | 3    | 3t <sub>C</sub> -1   |                   | 3t <sub>C</sub> -1   |                   | ns    |

| t <sub>RSH</sub>  | RAS hold from last CAS assertion                               | 4    | t <sub>N</sub>       |                   | t <sub>N</sub>       |                   | ns    |

| t <sub>RP</sub>   | RAS precharge time                                             | 5    | t <sub>P</sub> -2    |                   | t <sub>P</sub> -2    |                   | ns    |

| t <sub>CHL</sub>  | PCLK to CAS asserted delay                                     | 1    | 3                    | 13                | 3                    | 12                | ns    |

| t <sub>CLH</sub>  | PCLK to CAS de-asserted delay                                  |      | 4                    | 12                | 3                    | 11                | ns    |

| t <sub>CAS</sub>  | CAS pulse width                                                | 4    | t <sub>N</sub> -1    |                   | t <sub>N</sub> -1    |                   | ns    |

| t <sub>CPN</sub>  | CAS precharge time                                             |      | 0.5t <sub>C</sub>    |                   | 0.5t <sub>C</sub>    |                   | ns    |

| t <sub>RCD</sub>  | RAS to CAS delay time                                          |      | 1.5t <sub>C</sub> -2 | 1.5t <sub>C</sub> | 1.5t <sub>C</sub> -2 | 1.5t <sub>C</sub> | ns    |

|                   | Write Enable setup to RAS assertion                            |      | 10                   |                   | 9                    |                   |       |

Table 11: Timing Parameters for V96BMC Vcc=5 Volts +/- 5% and Vcc3= 5 or 3.3 <sup>8</sup>Volts +/- 5%

| t <sub>WEH</sub>   | Write Enable hold from RAS de-assertion                          |   | 1 | 3  | 1 | 3  | ns |

|--------------------|------------------------------------------------------------------|---|---|----|---|----|----|

| t <sub>LED</sub>   | PCLK to Latch Enable output delay                                | 6 | 3 | 12 | 3 | 10 | ns |

| t <sub>TXHL1</sub> | PCLK to Buffer Control fall delay                                | 7 | 3 | 13 | 3 | 11 | ns |

| t <sub>TXHL2</sub> | PCLK to Buffer Control fall delay (Mode 2 and 3 at TXA pin only) |   | 4 | 15 | 4 | 13 | ns |

| t <sub>TXLH</sub>  | PCLK to Buffer Control rise delay                                |   | 3 | 12 | 3 | 10 | ns |

| t <sub>RFHL</sub>  | REFRESH synchronous assertion delay                              |   | 3 | 13 | 3 | 11 | ns |

| t <sub>RFLH</sub>  | REFRESH synchronous de-assertion delay                           |   | 3 | 13 | 3 | 11 | ns |

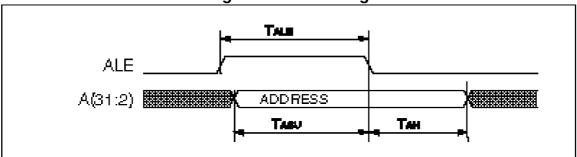

| t <sub>ASU</sub>   | Address setup to ALE Falling                                     |   | 6 |    | 5 |    | ns |

| t <sub>AH</sub>    | Address hold from ALE Falling                                    |   | 5 |    | 4 |    | ns |

#### NOTES:

- 1. Specified from PCLK falling edge.

- 2. t<sub>M</sub> = t<sub>C</sub> wh<u>en T</u>MUX = 1; t<sub>M</sub> = 0.5 t<sub>C</sub> when T\_MUX = 0. 3. Maximum RAS pulse width depends on the number of burst access.

- s. Maximum has pulse width depends on the number of burst access. 4.  $t_N$  = 1.5  $t_C$  when T\_RAS = 0;  $t_N$  = 2.5  $t_C$  when T\_RAS = 1. 5.  $t_P$  = 2  $t_C$  when T\_RAS = 0;  $t_P$  = 2  $t_C$  when T\_RAS = 1 and T\_RP = 1;  $t_P$  = 3  $t_C$  when T\_RAS = 1 and T\_RP = 0.

- 6. Rising delay is measured from PCLK falling edge, falling delay is measured from PCLK rising edge.

- 7. Except for Mode 2 and 3 at TXA pin.

8. In order to have 3.3 Volt DRAM interface Vcc3 pins must be connected to 3.3 Volt.

Vcc3 pins are: PIN # 91, 97, 103, 109, 57, 63, 69, 75, 81.

The power supply pins that must always be connected to 5V are Vcc.

Vcc pins are: PIN # 4, 47, 115.

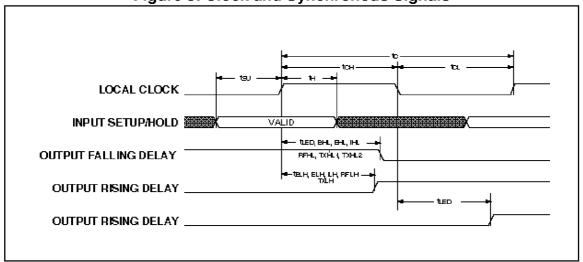

Figure 3: Clock and Synchronous Signals

Figure 4: ALE Timing

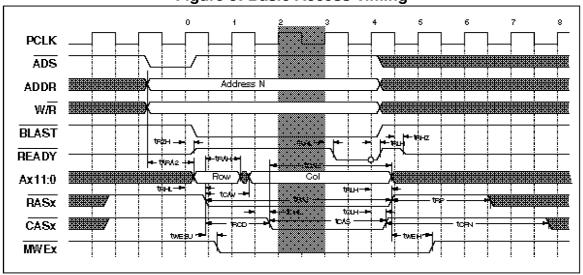

Figure 5: Basic Access Timing

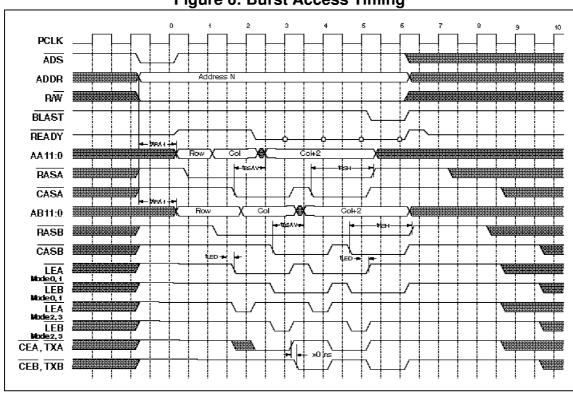

**Figure 6: Burst Access Timing**

## 5.0 Revision History

**Table 12: Revision History**

| Revision<br>Number | Date  | Comments and Changes                                                                                                  |

|--------------------|-------|-----------------------------------------------------------------------------------------------------------------------|

| 3.2                | 7/98  | V96BMC Rev D timing parameters with 3.3V DRAM support.                                                                |

| 3.1                | 10/96 | Data Book revision.                                                                                                   |

| 3.0                | 05/96 | Updated timings to final D-step values. Simplified data sheet format.                                                 |

| 2.0                | 7/92  | Updated timings to final A-step values.                                                                               |

| 1.0                | 7/92  | First pre-silicon revision of preliminary data sheet. DC and AC specs TBD. Sent only to a limited number of customers |

*USA:* 2348G Walsh Ave. Santa Clara CA 95051

Phone: (408)988-1050 Fax: (408)988-2601 Toll Free: (800)488-8410 (Canada and U.S. only) World Wide Web: http://www.vcubed.com