# Am29C01

CMOS Four-Bit Microprocessor Slice

# DISTINCTIVE CHARACTERISTICS

### Low Power

The CMOS Am29C01 is a plug-in replacement for the bipolar Am2901C. The Am29C01 dissipates less than 20% of the power of the equivalent bipolar part.

- Two-address architecture Independent simultaneous access to two working registers saves machine cycles.

- Eight-function ALU

Performs addition, two subtraction operations, and five logic functions on two source operands.

# Expandable

Connect any number of Am29C01s together for longer word lengths.

- Four status flags

- Carry, overflow, zero, and negative.

- Flexible data source selection

ALU data is selected from five source ports for a total of 203 source operand pairs for every ALU function.

# **GENERAL DESCRIPTION**

The Am29C01 industry standard four-bit microprocessor slice is a high-speed cascadable ALU intended for use in CPUs, peripheral controllers, and programmable microprocessors. The microinstruction flexibility of the Am29C01 permits efficient emulation of almost any digital computing machine.

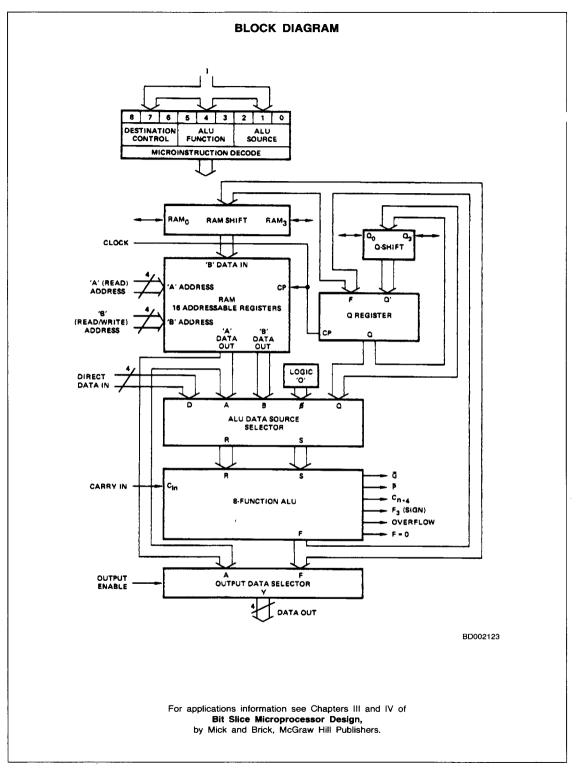

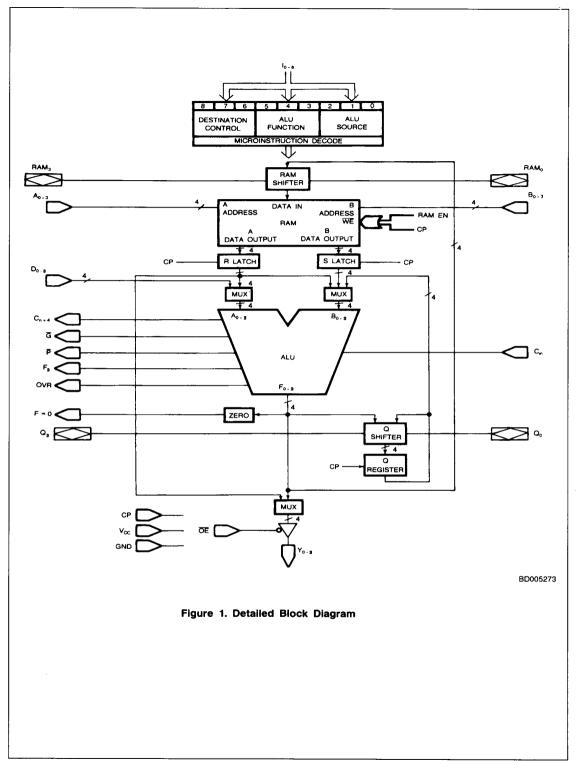

The device, as shown in the block diagram, consists of a 16-word by 4-bit two-port RAM, a high-speed ALU, and the associated shifting, decoding and multiplexing circuitry. The

9-bit microinstruction word is organized into three groups of three bits each and selects the ALU source operands, the ALU function, and the ALU destination register. The microprocessor is cascadable with full look ahead or with ripple carry, has three-state outputs, and provides various status flag outputs from the ALU.

The Am29C01 is a low power CMOS plug-in replacement for the Am2901C.

### RELATED AMD PRODUCTS

| Part No. | Description                                     |

|----------|-------------------------------------------------|

| Am27S35A | 1024 x 8 Registered PROM                        |

| Am29C03  | CMOS 4-Bit SUPERSLICE                           |

| Am2904   | Status and Shift Controller                     |

| Am29C10A | CMOS Microprogram Controller                    |

| Am29C101 | CMOS 16-Bit Microprocessor Slice                |

| Am29C111 | CMOS 16-Bit Microsequencer                      |

| Am29C116 | CMOS 16-Bit Microprocessor                      |

| Am2914   | Vectored Interrupt Controller                   |

| Am2918   | Pipeline Register                               |

| Am2922   | Condition Code Mux                              |

| Am2925   | Clock Generator                                 |

| Am29C331 | CMOS 16-Bit Microprogram<br>Sequencer           |

| Am2940   | DMA Address Generator                           |

| Am2952A  | 8-Bit Bidirectional I/O Port                    |

| Am29800A | High-Performance Bus Interface Family           |

| Am29C800 | High-Performance CMOS Bus<br>Interface Family   |

| Am29818A | SSR <sup>TM</sup> Diagnostics/Pipeline Register |

Chap

)4695

W 12/2

LIBERTY CHIP and SSR are trademarks and SUPERSLICE a registered trademark of Advanced Micro Devices, Inc.

Publication # Rev. Amendment 07366 C /0 Issue Date: April 1987

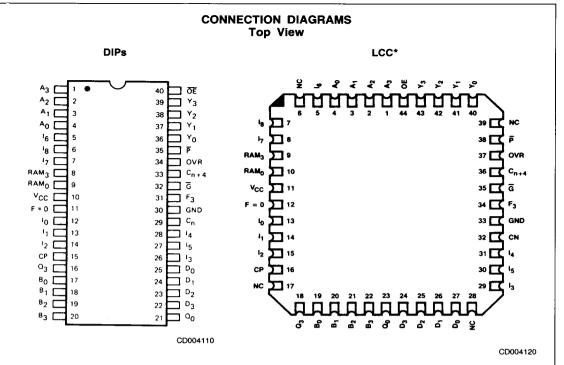

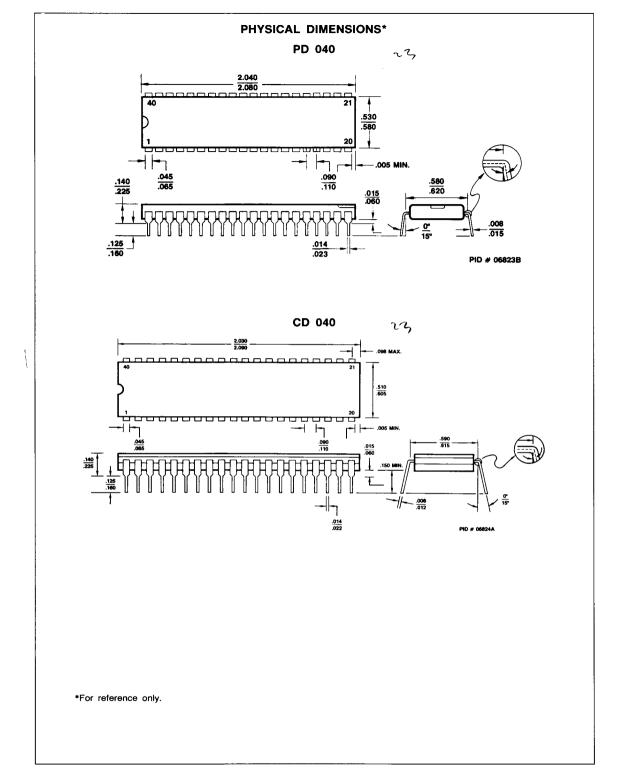

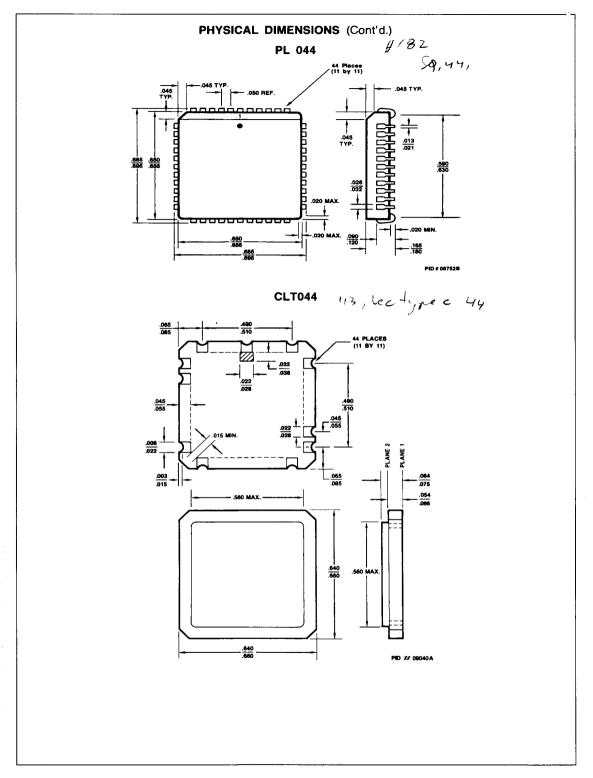

\* Also available in 44-Pin PLCC. Pinout is identical to LCC.

Note: Pin 1 is marked for orientation.

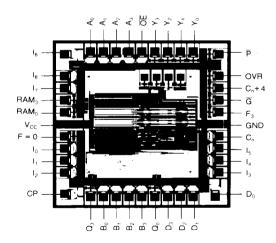

# **METALLIZATION AND PAD LAYOUT**

Die Size: 0.129" x 0.134" Equivalent Gate Count: 550 Gates

# LOGIC SYMBOL Address input Ao-As Bo-Bs Vo-Vs Data Output Control Input OE Co, CP CP CP Control Cont

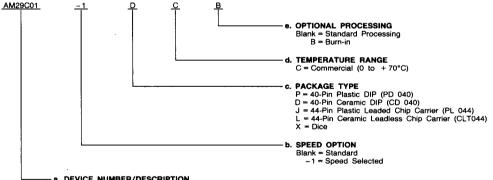

# ORDERING INFORMATION Standard Products

GND = Ground

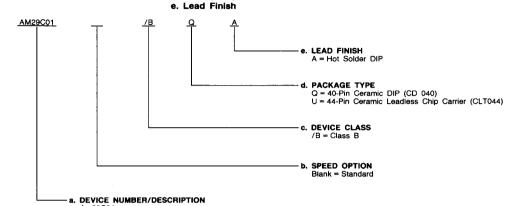

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

b. Speed Option (if applicable)c. Package Type

d. Temperature Range

e. Optional Processing

a. DEVICE NUMBER/DESCRIPTION Am29C01 4-Bit CMOS Microprocessor Slice

| Valid Co  | ombinations                             |

|-----------|-----------------------------------------|

| AM29C01 / | PC, PCB, DC,<br>DCB, JC, JCB,<br>LC, XC |

| AM29C01-1 | PC, PCB, DC,<br>DCB, JC, JCB            |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

**Valid Combinations**

# **ORDERING INFORMATION** (Cont'd.)

APL Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

- b. Speed Option (if applicable) c. Device Class

- d. Package Type

4-Bit CMOS Microprocessor Slice

| Valid Co | mbinations |

|----------|------------|

| AM29C01  | /BQA, /BUA |

### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

# **Group A Tests**

Group A tests consist of subgroups 1, 2, 3, 7, 8, 9, 10, 11.

# PIN DESCRIPTION

# A<sub>0</sub> - A<sub>3</sub> Address inputs — A Port (input)

The four address inputs to the register stack used to select one register whose contents are displayed through the A Port.

# B<sub>0</sub> - B<sub>3</sub> Address Inputs — B Port (Input)

The four address inputs to the register stack used to select one register whose contents are displayed through the B Port and into which new data can be written when the clock goes LOW.

# Cin Carry In (Input)

The carry-in to the internal ALU.

# Cn + 4 Carry Out (Output)

The carry-out of the internal ALU.

### CP Clock (input)

The Q-register and register-stack outputs change on the clock LOW-to-HIGH transition. The clock LOW time is internally the write enable pulse width to the 16 x 4 RAM. While the clock is LOW, the "slave" latches on the RAM outputs are closed, storing the data previously on the RAM outputs. This allows synchronous master-slave operation of the register stack.

### D<sub>0</sub> - D<sub>3</sub> Direct Data Inputs (Input)

A 4-bit data field which may be selected as one of the ALU data sources for entering data into the device.  $D_0$  is the LSB.

### F = 0 Status Bit (Output, Open Drain)

This is an open-drain output which goes HIGH (OFF) if the data on the four ALU outputs  $(F_0 - F_3)$  are all LOW. In positive logic, it indicates the result of an ALU operation is zero.

# F<sub>3</sub> Status Bit (Output)

The most significant ALU output bit.

### G, P Carry Generate, Propagate Outputs (Output)

The carry generate and propagate outputs of the internal ALU. These signals are used with the Am2902 for carry-lookahead.

### In-Is Instruction Control Lines (Input)

The nine instruction control lines used to determine what data sources will be applied to the ALU (|<sub>012</sub>), what function the ALU will perform (|<sub>345</sub>), and what data is to be deposited in the Q register or the register stack (|<sub>678</sub>).

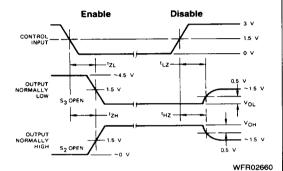

# OE Output Enable (Input, Active LOW)

When  $\overline{OE}$  is HIGH, the Y outputs are OFF; when  $\overline{OE}$  is LOW, the Y outputs are active (HIGH or LOW).

# OVR Overflow Status Bit (Output, Active HIGH)

This pin is logically the Exclusive-OR of the carry-in and carry-out of the MSB of the ALU. At the most significant end of the word, this pin indicates that the result of an arithmetic two's-complement operation has overflowed into the sign hit

# Q<sub>0</sub>, RAM<sub>0</sub> Shift Lines (Input/Output)

Shift lines like Q<sub>3</sub> and RAM<sub>3</sub>, but at the LSB of the Q register and RAM. These pins are tied to the Q<sub>3</sub> and RAM<sub>3</sub> pins of the adjacent device to transfer data between devices for up and down shifts of the Q register and ALU data.

# Q<sub>3</sub>, RAM<sub>3</sub> Shift Lines (Input/Output)

A shift line at the MSB of the Q register ( $Q_3$ ) and the register stack (RAM<sub>3</sub>). Electrically these lines are three-state outputs connected to TTL inputs internal to the device. When the destination code on  $I_{678}$  indicates an up shift (octal 6 or 7), the three-state outputs are enabled and the MSB of the Q register is available on the  $Q_3$  pin and the MSB of the ALU output is available on the RAM<sub>3</sub> pin. Otherwise, the three-state outputs are electrically OFF (high impedance) and the pins are electrically LS-TTL inputs. When the destination code calls for a down shift, the pins are used as the data inputs to the MSB of the Q register (octal 4) and RAM (octal 4 or 5).

### Yo - Y<sub>3</sub> Data Outputs (Output, Three-State)

The four data outputs. These are three-state output lines. When enabled they display either the four outputs of the ALU or the data on the A Port of the register stack, as determined by the destination code I<sub>678</sub>.

### **FUNCTIONAL DESCRIPTION**

A detailed block diagram of the CMOS microprogrammable microprocessor structure is shown in Figure 1. The circuit is a 4-bit slice cascadable to any number of bits. Therefore, all 4 data paths within the circuit are 4 bits wide. The two key elements in the Figure 1 diagram are the 16-word by 4-bit 2-port RAM and the high-speed ALU.

Data in any of the 16 words of the Random-Access Memory (RAM) can be read from the A-port of the RAM as controlled by the 4-bit A-address field input. Likewise, data in any of the 16 words of the RAM as defined by the B-address field input can be simultaneously read from the B-port of the RAM. The same code can be applied to the A-select field and B-select field in which case the identical file data will appear at both the RAM A-port and B-port outputs simultaneously.

When enabled by the RAM write enable (RAM EN), new data is always written into the file (word) defined by the B-address field of the RAM. The RAM data input field is driven by a 3-input multiplexer. This configuration is used to shift the ALU output data (F) if desired. This three-input multiplexer scheme allows the data to be shifted up one bit position, shifted down one bit position. or not shifted in either direction.

The RAM A-port data outputs and RAM B-port data outputs drive separate 4-bit latches. These latches hold the RAM data while the clock input is LOW. This eliminates any possible race conditions that could occur while new data is being written into the RAM.

The high-speed Arithmetic Logic Unit (ALU) can perform three binary arithmetic and five logic operations on the two 4-bit input words R and S. The R-input field is driven from a 2-input multiplexer, while the S-input field is driven from a 3-input multiplexer. Both multiplexers also have an inhibit capability; that is, no data is passed. This is equivalent to a "zero" source operand.

Referring to Figure 1, the ALU R-input multiplexer has the RAM A-port and the direct data inputs (D) connected as inputs. Likewise, the ALU S-input multiplexer has the RAM A-port, the RAM B-port and the Q register connected as inputs.

This multiplexer scheme gives the capability of selecting various pairs of the A, B, D, Q and "0" inputs as source operands to the ALU. These five inputs, when taken two at a time, result in ten possible combinations of source operand pairs. These combinations include AB, AD, AQ, A0, BD, BQ, B0, DQ, D0 and Q0. It is apparent that AD, AQ and A0 are somewhat redundant with BD, BQ and B0 in that if the A address and B address are the same, the identical function results. Thus, there are only seven completely non-redundant source operand pairs for the ALU. The Am29C01 microprocessor implements eight of these pairs. The microinstruction inputs used to select the ALU source operands are the I<sub>0</sub>, I<sub>1</sub>, and I<sub>2</sub> inputs. The definition of I<sub>0</sub>, I<sub>1</sub>, and I<sub>2</sub> for the eight source operand combinations are as shown in Table 1. Also shown is the octal code for each selection.

The two source operands not fully described as yet are the D input and Q input. The D input is the 4-bit wide direct data field input. This port is used to insert all data into the working registers inside the device. Likewise, this input can be used in the ALU to modify any of the internal data files. The Q register is a separate 4-bit file intended primarily for multiplication and division routines but it can also be used as an accumulator or holding register for some applications.

The ALU itself is a high-speed arithmetic/logic operator capable of performing three binary arithmetic and five logic functions. The I<sub>3</sub>, I<sub>4</sub>, and I<sub>5</sub> microinstruction inputs are used to select the ALU function. The definition of these inputs is

shown in Table 2. The octal code is also shown for reference. The normal technique for cascading the ALU of several devices is in a look-ahead carry mode. Carry generate,  $\overline{G}$ , and carry propagate,  $\overline{P}$ , are outputs of the device for use with a carry-look-ahead-generator such as the Am2902A. A carry-out,  $C_{n+4}$ , is also generated and is available as an output for use as the carry flag in a status register. Both carry-in  $(C_{in})$  and carry-out  $(C_{n+4})$  are active HIGH.

The ALU has three other status-oriented outputs. These are  $F_3$ , F=0, and overflow (OVR). The  $F_3$  output is the most significant (sign) bit of the ALU and can be used to determine positive or negative results without enabling the three-state data outputs.  $F_3$  is non-inverted with respect to the sign bit output  $Y_3$ . The F=0 output is used for zero detect. It is an open-drain output and can be wire OR'ed between microprocessor slices. F=0 is HIGH when all F outputs are LOW. The overflow output (OVR) is used to flag arithmetic operations that exceed the available two's complement number range. The overflow output (OVR) is HIGH when overflow exists. That is, when  $C_{n+3}$  and  $C_{n+4}$  are not the same polarity.

The ALU data output is routed to several destinations. It can be a data output of the device and it can also be stored in the RAM or the Q register. Eight possible combinations of ALU destination functions are available as defined by the  $I_6$ ,  $I_7$ , and  $I_8$  microinstruction inputs. These combinations are shown in Table 3.

The 4-bit data output field (Y) features three-state outputs and can be directly bus organized. An output control  $(\overline{OE})$  is used to enable the three-state outputs. When  $\overline{OE}$  is HIGH, the Y outputs are in the high-impedance state.

A 2-input multiplexer is also used at the data output such that either the A-port of the RAM or the ALU outputs (F) are selected at the device Y outputs. This selection is controlled by the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs. Refer to Table 3 for the selected output for each microinstruction code combination.

As was discussed previously, the RAM inputs are driven from a 3-input multiplexer. This allows the ALU outputs to be entered non-shifted, shifted up one position (X2) or shifted down one position ( $\div 2$ ). The shifter has two ports; one is labeled RAM0 and the other is labeled RAM3. Both of these ports consist of a buffer-driver with a three-state output and an input to the multiplexer. Thus, in the shift up mode, the RAM3 buffer is enabled and the RAM0 multiplexer input is enabled. Likewise, in the shift-down mode, the RAM0 buffer and RAM3 input are enabled. In the no-shift mode, both buffers are in the high-impedance state and the multiplexer inputs are not selected. This shifter is controlled from the  $1_6,\ 1_7$  and  $1_8$  microinstruction inputs as defined in Table 3.

Similarly, the Q register is driven from a 3-input multiplexer. In the no-shift mode, the multiplexer enters the ALU data into the Q register. In either the shift-up or shift-down mode, the multiplexer selects the Q-register data appropriately shifted up or down. The Q shifter also has two ports; one is labeled  $Q_0$  and the other is  $Q_3$ . The operation of these two ports is similar to the RAM shifter and is also controlled from  $\mathsf{I}_6$ ,  $\mathsf{I}_7$ , and  $\mathsf{I}_8$  as shown in Table 3.

The clock input to the Am29C01 controls the RAM, the Q register, and the A- and B- data latches. When enabled, data is clocked into the Q register on the LOW-to-HIGH transition of the clock. When the clock input is HIGH, the A and B latches are open and will pass whatever data is present at the RAM outputs. When the clock input is LOW, the latches are closed and will retain the last data entered. If the RAM-EN is enabled, new data will be written into the RAM file (word) defined by the B-address field when the clock input is LOW.

# **FUNCTIONAL TABLES**

TABLE 1. ALU SOURCE OPERAND CONTROL

| Mnemonic |                | Micr | o Co           | de            |   | Source<br>ands |

|----------|----------------|------|----------------|---------------|---|----------------|

| Mnemonic | l <sub>2</sub> | 11   | I <sub>0</sub> | Octal<br>Code | R | s              |

| AQ       | L              | L    | L              | 0             | Α | Q              |

| AB       | L              | L    | H              | 1             | A | В              |

| ZQ       | L              | н    | L              | 2             | 0 | Q              |

| ZB       | L              | н    | н              | 3             | 0 | В              |

| ZA       | Н              | L    | L              | 4             | 0 | Α              |

| DA       | Н              | L    | Н              | 5             | D | Α              |

| DQ       | H              | н    | L              | 6             | D | Q              |

| DZ       | Н              | Н    | Н              | 7             | D | 0              |

**TABLE 2. ALU FUNCTION CONTROL**

|          |    | Micr | o C | ode           | 41.11           |                   |

|----------|----|------|-----|---------------|-----------------|-------------------|

| Mnemonic | 15 | 14   | lз  | Octal<br>Code | ALU<br>Function | Symbol            |

| ADD      | L  | L    | L   | 0             | R Plus S        | R+S               |

| SUBR     | L  | L    | н   | 1             | S Minus R       | S-R               |

| SUBS     | L  | н    | L   | 2             | R Minus S       | R-S               |

| OR       | L  | н    | н   | 3             | RORS            | RvS               |

| AND      | Н  | L    | L   | 4             | RANDS           | R^S               |

| NOTRS    | Н  | L    | н   | 5             | RANDS           | R∧S               |

| EXOR     | Н  | н    | L   | 6             | R EX-OR S       | R <del>-∀</del> S |

| EXNOR    | Н  | Н    | Н   | 7             | R EX-NOR S      | R <del>∀</del> S  |

TABLE 3. ALU DESTINATION CONTROL

|          | Micro Code     |    |                | RAM<br>Function |       | Q-Reg.<br>Function |       | Y      | RAM<br>Shifter |                  | Q<br>Shifter     |                 |                 |

|----------|----------------|----|----------------|-----------------|-------|--------------------|-------|--------|----------------|------------------|------------------|-----------------|-----------------|

| Mnemonic | l <sub>8</sub> | 17 | l <sub>6</sub> | Octal<br>Code   | Shift | Load               | Shift | Load   | Output         | RAM <sub>0</sub> | RAM <sub>3</sub> | Q <sub>0</sub>  | Q <sub>3</sub>  |

| QREG     | L              | L  | L              | 0               | ×     | NONE               | NONE  | F→Q    | F              | Х                | Х                | Х               | Х               |

| NOP      | L              | L  | Н              | 1               | X     | NONE               | Х     | NONE   | F              | Х                | Х                | Х               | Х               |

| RAMA     | L              | Н  | L              | 2               | NONE  | F→B                | ×     | NONE   | Α              | Х                | Х                | Х               | X               |

| RAMF     | L              | Н  | Н              | 3               | NONE  | F→B                | Х     | NONE   | F              | Х                | X                | Х               | Х               |

| RAMQD    | Н              | L  | L              | 4               | DOWN  | F/2→B              | DOWN  | Q/2→Q  | F              | F <sub>0</sub>   | IN <sub>3</sub>  | Q <sub>0</sub>  | IN <sub>3</sub> |

| RAMD     | Н              | Ł  | н              | 5               | DOWN  | F/2→B              | Х     | NONE   | F              | F <sub>0</sub>   | IN <sub>3</sub>  | Q <sub>0</sub>  | Х               |

| RAMQU    | Н              | Н  | L              | 6               | UP    | 2F → B             | UP    | 2Q → Q | F              | IN <sub>0</sub>  | F <sub>3</sub>   | IN <sub>0</sub> | Q <sub>3</sub>  |

| RAMU     | Н              | Н  | Н              | 7               | UP    | 2F→B               | Х     | NONE   | F              | IN <sub>0</sub>  | F <sub>3</sub>   | X               | Q <sub>3</sub>  |

X = Don't care. Electrically, the shift pin is a TTL-equivalent input internally connected to a three-state output which is in the high-impedance state. B = Register Addressed by B inputs. UP is toward MSB, DOWN is toward LSB.

TABLE 4. SOURCE OPERAND and ALU FUNCTION MATRIX

|       | I <sub>210</sub> Octal          |            |       |      |      |        |           |                  |      |

|-------|---------------------------------|------------|-------|------|------|--------|-----------|------------------|------|

|       |                                 | 0          | 1     | 2    | 3    | 4      | 5         | 6                | 7    |

| Octal | ALU                             | ALU Source |       |      |      |        |           |                  |      |

| 1543  | Function                        | A, Q       | A, B  | 0, Q | 0, B | 0, A   | D, A      | D, Q             | D, 0 |

| 0     | C <sub>n</sub> = L<br>R Plus S  | A + Q      | A + B | Q    | В    | Α      | D+A       | D+Q              | D    |

| U     | C <sub>n</sub> = H              | A + Q + 1  | A+B+1 | Q+1  | B+1  | A + 1  | D+A+1     | D+Q+1            | D+1  |

|       | C <sub>n</sub> =L               | Q-A-1      | B-A-1 | Q-1  | B-1  | A – 1  | A - D - 1 | Q-D-1            | -D-1 |

| 1.    | S Minus R<br>C <sub>n</sub> = H | Q-A        | B-A   | a    | В    | Α      | A – D     | Q-D              | -D   |

|       | C <sub>n</sub> = L              | A – Q – 1  | A-B-1 | -Q-1 | -B-1 | -A - 1 | D-A-1     | D-Q-1            | D-1  |

| 2     | R Minus S<br>C <sub>n</sub> = H | A-Q        | A-B   | -a   | -В   | -A     | D-A       | D-Q              | D    |

| 3     | RORS                            | AVQ        | AVB   | ۵    | В    | Α      | DVA       | DVQ              | D    |

| 4     | R AND S                         | A^Q        | A^B   | 0    | 0    | 0      | D^A       | D^Q              | 0    |

| 5     | R AND S                         | Ā^Q        | Ã∧B   | Q    | В    | Α      | D∧A       | Ď∧Q              | 0    |

| 6     | R EX-OR S                       | A¥Q        | A¥B   | Q    | В    | Α      | D₩A       | D <del>V</del> Q | D    |

| 7     | R EX-NOR S                      | Ā₩Q        | Ā₩B   | ۵    | B    | Ā      | D₩A       | D₩Q              | ō    |

<sup>+ =</sup> Plus

<sup>- =</sup> Minus v = OR ^ = AND V = EX-OR

TABLE 5. ALU LOGIC MODE FUNCTIONS

| Octal<br>I <sub>543</sub> , I <sub>210</sub> | Group  | Function                                                                     |

|----------------------------------------------|--------|------------------------------------------------------------------------------|

| 4 0<br>4 1<br>4 5<br>4 6                     | AND    | A^Q<br>A^B<br>D^A<br>D^Q                                                     |

| 3 0<br>3 1<br>3 5<br>3 6                     | OR     | A V Q<br>A V B<br>D V A<br>D V Q                                             |

| 6 0<br>6 1<br>6 5<br>6 6                     | EX-OR  | A <del>V</del> Q<br>A <del>V</del> B<br>D <del>V</del> A<br>D <del>V</del> Q |

| 7 0<br>7 1<br>7 5<br>7 6                     | EX-NOR | A <del>V</del> Q<br>A <del>V</del> B<br>D <del>V</del> A<br>D <del>V</del> Q |

| 7 2<br>7 3<br>7 4<br>7 7                     | INVERT | Q<br>B<br>A<br>D                                                             |

| 6 2<br>6 3<br>6 4<br>6 7                     | PASS   | Q<br>B<br>A<br>D                                                             |

| 3 2<br>3 3<br>3 4<br>3 7                     | PASS   | Q<br>B<br>A<br>D                                                             |

| 4 2<br>4 3<br>4 4<br>4 7                     | "ZERO" | 0<br>0<br>0<br>0                                                             |

| 5 0<br>5 1<br>5 5<br>5 6                     | MASK   | Ā^Q<br>Ā^B<br>D^A<br>D^Q                                                     |

TABLE 6. ALU ARITHMETIC MODE FUNCTIONS

| Octal                                                | C <sub>in</sub> =      | = L                                                                  | C <sub>in</sub> =      | : H                                                                  |

|------------------------------------------------------|------------------------|----------------------------------------------------------------------|------------------------|----------------------------------------------------------------------|

| l <sub>543</sub> ,<br>l <sub>210</sub>               | Group                  | Function                                                             | Group                  | Function                                                             |

| 0 0<br>0 1<br>0 5<br>0 6                             | ADD                    | A+Q<br>A+B<br>D+A<br>D+Q                                             | ADD plus<br>one        | A+Q+1<br>A+B+1<br>D+A+1<br>D+Q+1                                     |

| 0 2<br>0 3<br>0 4<br>0 7                             | PASS                   | Q<br>B<br>A<br>D                                                     | Increment              | Q+1<br>B+1<br>A+1<br>D+1                                             |

| 1 2<br>1 3<br>1 4<br>2 7                             | Decrement              | Q-1<br>B-1<br>A-1<br>D-1                                             | PASS                   | Q B A D                                                              |

| 2 2<br>2 3<br>2 4<br>1 7                             | 1's Comp.              | -Q-1<br>-B-1<br>-A-1<br>-D-1                                         | 2's Comp.<br>(Negate)  | -Q<br>-B<br>-A<br>-D                                                 |

| 1 0<br>1 1<br>1 5<br>1 6<br>2 0<br>2 1<br>2 5<br>2 6 | Subtract<br>(1's Comp) | Q-A-1<br>B-A-1<br>A-D-1<br>Q-D-1<br>A-Q-1<br>A-B-1<br>D-A-1<br>D-Q-1 | Subtract<br>(2's Comp) | Q - A<br>B - A<br>A - D<br>Q - D<br>A - Q<br>A - B<br>D - A<br>D - Q |

# Source Operands and ALU Functions

There are eight source operand pairs available to the ALU as selected by the  $l_0,\,l_1,\,$  and  $l_2$  instruction inputs. The ALU can perform eight functions; five logic and three arithmetic. The  $l_3,\,$   $l_4,\,$  and  $l_5$  instruction inputs control this function selection. The carry input,  $C_{in},\,$  also affects the ALU results when in the arithmetic mode. The  $C_{in}$  input has no effect in the logic mode. When  $l_0$  through  $l_5$  and  $C_{in}$  are viewed together, the matrix of Table 4 results. This matrix fully defines the ALU/source operand function for each state.

The ALU functions can also be examined on a "task" basis, i.e., add, subtract, AND, OR, etc. In the arithmetic mode, the carry will affect the function performed while in the logic mode,

the carry will have no bearing on the ALU output. Table 5 defines the various logic operations that the Am29C01 can perform and Table 6 shows the arithmetic functions of the device. Both carry-in LOW ( $C_{in} = 0$ ) and carry-in HGH ( $C_{in} = 1$ ) are defined in these operations.

# Logic Functions for $\overline{G}$ , $\overline{P}$ , $C_{n+4}$ , and OVR

The four signals  $\overline{G}$ ,  $\overline{P}$ ,  $C_{n+4}$ , and OVR are designed to indicate carry and overflow conditions when the Am29C01 is in the add or subtract mode. Table 7 indicates the logic equations for these four signals for each of the eight ALU functions. The R and S inputs are the two inputs selected according to Table 1.

| 1543 | Function    | P                                                                                                     | G                                                                                                                                                              | C <sub>n + 4</sub>                                                                                                                                                                                          | OVR                                                                                |

|------|-------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 0    | R+S         | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub>                                           | G <sub>3</sub> + P <sub>3</sub> G <sub>2</sub> + P <sub>3</sub> P <sub>2</sub> G <sub>1</sub> +<br>P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> G <sub>0</sub> | C <sub>4</sub>                                                                                                                                                                                              | C <sub>3</sub> <del>V</del> C <sub>4</sub>                                         |

| 1    | S-R         | 4                                                                                                     | Same as R + S equations, but                                                                                                                                   | t substitute Ri for Ri in definitions—                                                                                                                                                                      | <b>•</b>                                                                           |

| 2    | R-S         | +                                                                                                     | Same as R + S equations, bu                                                                                                                                    | t substitute Si for Si in definitions—                                                                                                                                                                      |                                                                                    |

| 3    | RVS         | LOW                                                                                                   | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub>                                                                                                    | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> + C <sub>n</sub>                                                                                                                                | P3 P2 P1 P0 + Cn                                                                   |

| 4    | R^S         | LOW                                                                                                   | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub>                                                                                              | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub> + C <sub>n</sub>                                                                                                                          | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub> + C <sub>n</sub> |

| 5    | Fi∧s        | LOW                                                                                                   | ← Same as R ^ S                                                                                                                                                | equations, but substitute $\overline{R_i}$ for $R_i$ in                                                                                                                                                     | definitions                                                                        |

| 6    | R₩S         | 4                                                                                                     | Same as R ¥ S, but sub                                                                                                                                         | stitute Ri for Ri in definitions                                                                                                                                                                            |                                                                                    |

| 7    | R₩S         | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub>                                     | G <sub>3</sub> + P <sub>3</sub> G <sub>2</sub> + P <sub>3</sub> P <sub>2</sub> G <sub>1</sub> +<br>P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> | G <sub>3</sub> + P <sub>3</sub> G <sub>2</sub> + P <sub>3</sub> P <sub>2</sub> G <sub>1</sub> +<br>P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> (G <sub>0</sub> + C <sub>n</sub> )           | (See Note 1)                                                                       |

|      | Definitions | $P_0 = P_0 + P_0$<br>$P_0 = P_0 + P_0$<br>$P_1 = P_1 + P_1$<br>$P_2 = P_2 + P_2$<br>$P_3 = P_3 + P_3$ | $G_0 = R_0S_0$ $G_1 = R_1S_1$ $G_2 = R_2S_2$ $G_3 = R_3S_3$ $C_4 = G_3 + P_3G_2 + P_3P_2G_1$ $C_3 = G_2 + P_2G_1 + P_2P_1G_0$                                  | + P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> G <sub>0</sub> + P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> C <sub>n</sub><br>+ P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> C <sub>n</sub> |                                                                                    |

# **APPLICATIONS**

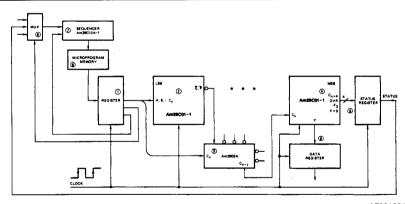

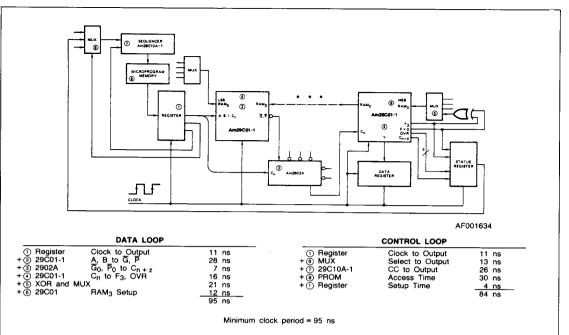

# Minimum Cycle Time Calculations for 16-Bit Systems

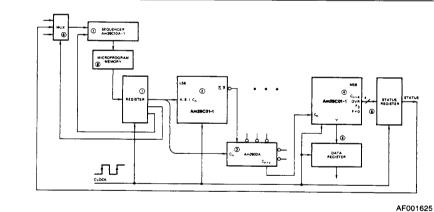

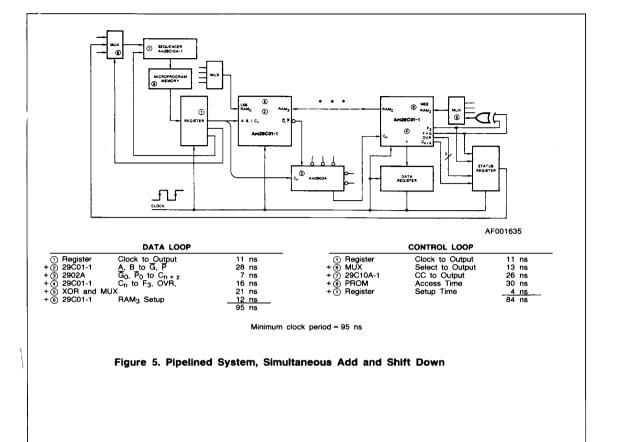

Speeds used in calculations for parts other than Am29C01-1 and Am29C10A-1 are representative for available MSI parts (see Figures 2 and 3).

AF001624

|                          | DATA LOOP                               |               |                         | CONTROL LOOP                     |                |

|--------------------------|-----------------------------------------|---------------|-------------------------|----------------------------------|----------------|

| ① Register               | Clock to Output                         | 11 ns         | ① Register              | Clock to Output                  | 11 ns          |

| + ② 29C01-1              | A, B to G, P<br>Gn, Pn to Cn+7          | 28 ns<br>7 ns | + ⑥ MUX<br>+ ⑦ 29C10A-1 | Select to Output<br>CC to Output | 13 ns<br>26 ns |

| + ③ 2902A<br>+ ④ 29C01-1 | $C_n$ to $C_{n+4}$ , OVR,               | 18 ns         | +® PROM                 | Access Time                      | 30 ns          |

| + (6) Register           | F <sub>3</sub> , F = 0, Y<br>Setup Time | 4 ns          | + ① Register            | Setup Time                       | 4 ns           |

| T (5) Register           | Setup Time                              | 68 ns         | 1 () Hogister           | Cotap Timo                       | 84 ns          |

Minimum clock period = 84 ns

Figure 2. Pipelined System, Add without Simultaneous Shift

Figure 3. Pipelined System, Simultaneous Add and Shift Down

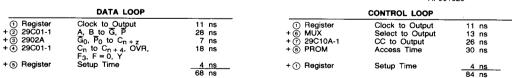

Speeds used in calculations for parts other than Am29C01-1 and Am29C10A-1 are representative for available MSI parts (see Figures 4 and 5).

Minimum clock period = 84 ns

Figure 4. Pipelined System, Add without Simultaneous Shift

# ABSOLUTE MAXIMUM RATINGS

| Storage Temperature65 to +150°C Ambient Temperature Under Bias55 to +125°C |

|----------------------------------------------------------------------------|

| Supply Voltage to Ground Potential                                         |

| Continuous0.3 to +7.0 V                                                    |

| DC Voltage Applied to Outputs For                                          |

| High Output State0.3 to +V <sub>CC</sub> + 0.3 V                           |

| DC Input Voltage0.3 to +V <sub>CC</sub> + 0.3 V                            |

| DC Output Current, Into LOW Outputs30 mA                                   |

| DC Input Current10 to +10 mA                                               |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

|                                   | 0° to +70°C<br>+4.5 to +5.5 V |

|-----------------------------------|-------------------------------|

| Military* (M) Devices             |                               |

| Temperature (T <sub>A</sub> )     | 55 to +125°C                  |

| Supply Voltage (V <sub>CC</sub> ) | +4.5 to +5.5 V                |

Operating ranges define those limits between which the functionality of the device is guaranteed.

\*Military Product 100% tested at T<sub>C</sub> = +25°C, +125°C, and -55°C.

DC CHARACTERISTICS over operating ranges unless otherwise specified; Included in Group A, Subgroup 1, 2. 3 tests unless otherwise noted.

| Parameter<br>Symbol | Parameter<br>Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                   | Test Con                                                                                                | ditions (N       | ote 1)                 | Min.    | Max. | Units |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------|------------------------|---------|------|-------|

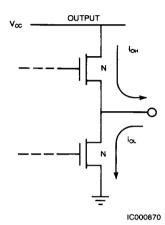

| Vou                 | VOH Output HIGH Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | but HIGH Voltage         V <sub>CC</sub> = Min.         I <sub>OH</sub> = -1.6 mA         All Others           V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> I <sub>OH</sub> = -600 μA         RAM <sub>0</sub> , RAM <sub>3</sub> , Q <sub>0</sub> , Q <sub>3</sub>       |                                                                                                         | 2.4              |                        | v       |      |       |

| -011                | - Conposition of the control of the |                                                                                                                                                                                                                                                                                   |                                                                                                         |                  |                        | 2.4     |      |       |

| ICEX                | Output Leakage Current<br>For F = 0 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                   | V <sub>CC</sub> = Min., V <sub>OH</sub> = 5.5 V<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> |                  |                        |         | 10   | μА    |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                   | All Others                                                                                              | lOL € 20         | mA )                   |         | 0.5  | Ī     |

| VOL                 | Output LOW Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VIN = VIH                                                                                                                                                                                                                                                                         | RAM <sub>0</sub> , RAM <sub>3</sub> ,<br>Q <sub>0</sub> , Q <sub>3</sub>                                | IOL = 6.0 mA     |                        |         | 0.5  | 1 '   |

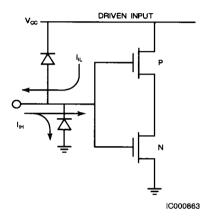

| V <sub>IH</sub>     | Input HIGH Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Guaranteed input logical HIGH voltage for all inputs (Note 2)                                                                                                                                                                                                                     |                                                                                                         |                  |                        | 2.0     |      | V     |

| V <sub>IL</sub>     | Input LOW Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Guaranteed input logical LOW voltage for all inputs (Note 2)                                                                                                                                                                                                                      |                                                                                                         |                  |                        |         | 0.8  | ٧     |

| կլ                  | Input LOW Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>CC</sub> = Max.,<br>V <sub>IN</sub> = 0.5 V                                                                                                                                                                                                                                |                                                                                                         |                  |                        |         | -10  | μА    |

| liн<br>П            | Input HIGH Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>CC</sub> = Max.,                                                                                                                                                                                                                                                           | VIN = VCC -0.5 V                                                                                        | r                | *****                  |         | 10   | μА    |

| lozh                | Off State (High Impedance)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                   |                                                                                                         |                  | V <sub>O</sub> = 2.4 V |         | 10   |       |

| OZL                 | Output Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CC</sub> = Max.                                                                                                                                                                                                                                                            |                                                                                                         | Y <sub>0-3</sub> | V <sub>O</sub> = 0.5 V |         | -10  | μΑ    |

| loo                 | Static Power Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $ \begin{array}{c} V_{CC} = Max., \\ V_{IN} = V_{CC} \text{ or GND,} \\ I_{O} = 0 \ \mu A \end{array} \qquad \begin{array}{c} T_{A} = 0^{\circ} \text{ to } + 70^{\circ} \text{C (COM'L only)} \\ T_{A} = -55^{\circ} \text{ to } + 125^{\circ} \text{C (MIL only)} \end{array} $ |                                                                                                         |                  |                        |         | 20   | mA    |

| icc                 | (Note 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                   |                                                                                                         |                  | 25                     | 1 mA    |      |       |

| C <sub>PD</sub>     | Power Dissipation Capacitance (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 5.0 V,<br>T <sub>A</sub> = 25°C,<br>No Load                                                                                                                                                                                                                     |                                                                                                         |                  | 500 pF                 | Typical |      |       |

- For conditions shown as Min. or Max., use the appropriate value specified under operating ranges for the applicable device type.

These input levels provide zero noise immunity and should only be statically tested in a noise-free environment (not functionally tested).

- Worst-case ICC is measured at the lowest temperature in the specified operating range.

- 4. CpD determines the no-load dynamic current consumption: ICC (Total) = ICC (Static) + CPD VCC f, where f is the switching frequency of the majority of the internal nodes, normally one-half of the clock frequency.

# SWITCHING CHARACTERISTICS over Commercial Operating Range unless otherwise specified.

# Am29C01

The following tables specify the guaranteed performance of the Am29C01 over the commercial operating range of 0°C to  $+70^{\circ}\text{C}$ , with V<sub>CC</sub> from 4.5 V to 5.5 V. All data are in ns, with measurements made at 1.5 V. All outputs have maximum DC load, C<sub>L</sub> = 50 pF.

# A. Cycle Time and Clock Characteristics

| Read-Modify-Write Cycle (from selection of A, B registers to end of cycle.) | 31 ns*  |

|-----------------------------------------------------------------------------|---------|

| Maximum Clock Frequency to shift Q (50% duty cycle, I = 432 or 632)         | 32 MHz* |

| Minimum Clock LOW Time                                                      | 15 ns   |

| Minimum Clock HIGH Time                                                     | 15 ns   |

| Minimum Clock Period                                                        | 31 ns*  |

<sup>\*</sup>These specs are not tested, but are derived from other specs.

# **B. Combinational Propagation Delays** (Note 1)