Semiconductor

4,194,304 bit MNOS High Speed EEPROM

#### **Features**

Fast Access Time of 120/150/200 ns.

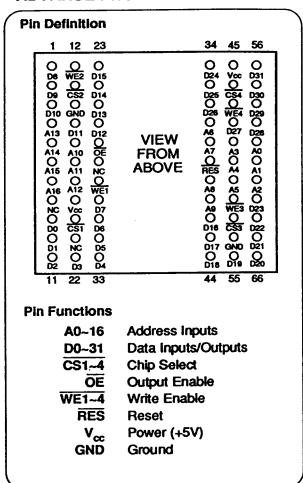

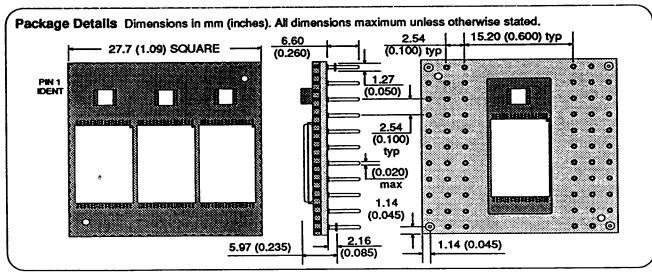

66 PGA FR4 Epoxy Substrate.

User Configurable as: 8 / 16 / 32 bit wide output.

Operating Power @ 1MHz: 100 /180 / 330 mW (max).

Low Power Standby 400 µW (max).

Single Byte and Page Write (128 Bytes) operation.

Software and Hardware Data Protection.

**RES Data Protection.**

DATA Polling Indication of End of Write.

105 Write/Erase Cycles in Page Mode.

10 Year Data Retention Time.

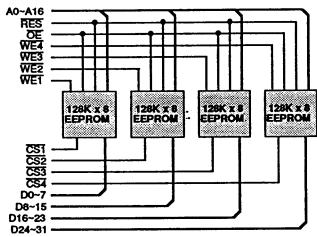

#### **Block Diagram**

# 128Kx 32 EEPROM MODULE

#### PUMA 3E4000X-12/15/20

Issue 1.1: September1993

## ADVANCE PRODUCT INFORMATION

| Absolute Maximum Ratings (1)                                 |                  |              |    |  |  |  |  |  |

|--------------------------------------------------------------|------------------|--------------|----|--|--|--|--|--|

| Operating Temperature                                        | T <sub>OPR</sub> | -55 to +125  | .c |  |  |  |  |  |

| Storage Temperature                                          | T <sub>stG</sub> | -65 to +150  | ·c |  |  |  |  |  |

| Input voltages (including N.C. pins) with Respect to GND (2) | V.,              | -0.5 to +7.0 | V  |  |  |  |  |  |

| Supply Voltage with respect to GND                           | V <sub>∞</sub>   | -0.6 to +7.0 | V  |  |  |  |  |  |

Notes: (1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

(2) May be -3.0V for pulse width of less than 50 ns.

| Recommended Operating Conditions |                |      |     |                      |                                 |  |  |  |

|----------------------------------|----------------|------|-----|----------------------|---------------------------------|--|--|--|

|                                  |                | min  | typ | max                  |                                 |  |  |  |

| DC Power Supply Voltage          | V <sub>∞</sub> | 4.5  | 5.0 | 5.5                  | V                               |  |  |  |

| Input Low Voltage                | V,             | -0.3 | -   | 8.0                  | V                               |  |  |  |

| nput High Voltage                | V <sub>H</sub> | 2.2  | -   | V <sub>cc</sub> +1.0 | V                               |  |  |  |

| Operating Temp Range             | T_             | 0    | -   | 70                   | c                               |  |  |  |

|                                  | T              | -40  | -   | 85                   | °C (I Suffix)-15 and -20ns only |  |  |  |

| DC Electrical Characteristics ( $T_A=0$ °C to +70°C, $V_{cc}=5V\pm10\%$ ) |          |                   |                                                                                                                                      |     |     |      |  |  |

|---------------------------------------------------------------------------|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|--|--|

| Parameter                                                                 |          | Sym               | bol Test Condition                                                                                                                   | min | max | Unit |  |  |

| Input Leakage CS1~4,                                                      | WE1~4    | l <sub>un</sub>   | $V_{\rm N}$ = GND to $V_{\rm cc}$                                                                                                    | -2  | 2   | μА   |  |  |

| Current                                                                   | RES      | LIZ.              | $V_{\rm pt}$ = GND to $V_{\rm cc}$                                                                                                   | -   | 100 | μА   |  |  |

|                                                                           | r Inputs | l <sub>Lts</sub>  | $V_{\rm IN}$ = GND to $V_{\rm cc}$                                                                                                   | -8  | 8   | μA   |  |  |

| Output Leakage Current                                                    | 32 bit   | ľω                | $V_{IN} = GND \text{ to } V_{CC}, \overline{CS}^{(1)} = V_{IH}$                                                                      | -2  | 2   | μA   |  |  |

| Operating Supply Current                                                  | 32 bit   | CC32              | $\overrightarrow{CS}^{(1)} = \overrightarrow{OE} = V_{E}$ , $\overrightarrow{WE}^{(1)} = V_{H}$ , $I_{OUT} = OmA$ , $f = 5MHz^{(2)}$ | -   | 200 | mA   |  |  |

|                                                                           | 16 bit   | I <sub>CC16</sub> | As above                                                                                                                             | -   | 106 | mΑ   |  |  |

|                                                                           | 8 bit    | lccs              | As above                                                                                                                             | -   | 59  | mA   |  |  |

| Standby Supply Current TT                                                 |          | <br>SB1           | $\overline{CS}^{(1)} = V_{H1}$ , $I_{LO} = 0$ mA, Other inputs = $V_{H1}$                                                            | -   | 12  | mA   |  |  |

| CMOS                                                                      | S levels | 582               | $\overline{\text{CS}}^{(1)} = V_{cc}$ -0.3V, $I_{yo}$ = 0mA, Other Inputs = $V_{cc}$                                                 | -   | 2   | mA   |  |  |

| Output Low Voltage                                                        |          | Val               | l <sub>ot</sub> = 2.1mA.                                                                                                             | -   | 0.4 | ٧    |  |  |

| Output High Voltage                                                       |          | V <sub>OH</sub>   | l <sub>он</sub> = -400µA.                                                                                                            | 2.4 | -   | V    |  |  |

Notes (1)  $\overline{\text{CS}}$  and  $\overline{\text{WE}}$  above are accessed through  $\overline{\text{CS1-4}}$  and  $\overline{\text{WE1-4}}$  repectively. These inputs must be operated simultaneously for 32 bit operation, in pairs in 16 bit mode and singly for 8 bit mode.

(2) At an operating frequency of 1MHz, the 32 /16 / 8 bit currents will be 60 / 32 / 18 mA (max) respectively.

| Parameter              |             | Symbol             | Test Condition       | typ | max | Unit |

|------------------------|-------------|--------------------|----------------------|-----|-----|------|

| Input Capacitance CS1- | -4, WE1~4   | CINT               | V <sub>ev</sub> =0V  |     | 16  | pF   |

| 0                      | ther Inputs | C <sub>IN2</sub>   | V <sub>IN</sub> =0V  | -   | 34  | pF   |

| Output Capacitance     | 32 bit      | C <sub>OUT32</sub> | V <sub>out</sub> =0V | -   | 22  | рF   |

#### **AC READ CHARACTERISTICS**

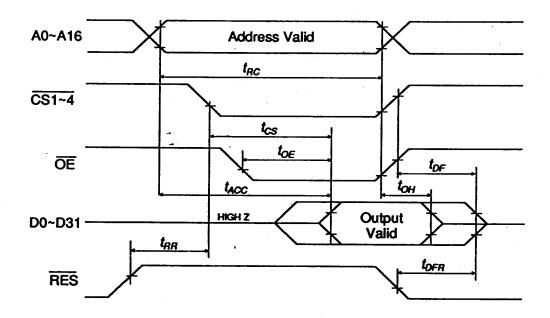

# **Read Cycle**

|                               |                      | -1  | 2 <sup>(3)</sup> | -   | 15  | -   | 20  |      |

|-------------------------------|----------------------|-----|------------------|-----|-----|-----|-----|------|

| Parameter                     | Symbol               | min | max              | min | max | min | max | Unit |

| Address to Output Delay       | t <sub>ACC</sub>     | -   | 120              | -   | 150 | -   | 200 | ns   |

| Chip Select to Output Delay   | t <sub>cs</sub>      | -   | 120              | -   | 150 | -   | 200 | ns   |

| Output Enable to Output Delay |                      | 10  | 60               | 10  | 75  | 10  | 80  | ns   |

| Address to Output Hold        | t <sub>on</sub>      | 0   | -                |     | -   | 0   | -   | ns   |

| Output Enable to Output Float | t <sub>DF</sub> (1)  | 0   | 45               | 0   | 50  | 0   | 55  | ns   |

|                               | t <sub>DFR</sub> (2) | 0   | 350              | 0   | 350 | 0   | 350 | ns   |

| Reset to Output Delay         | t <sub>RR</sub> (2)  | 0   | 600              | 0   | 600 | 0   | 600 | ns   |

Notes: (1) t<sub>pr</sub> is defined as the time at which the output achieves the open circuit condition and is not referenced to output voltage levels. This parameter is guaranteed and not 100% tested.

- (2) These parameters are not tested but guaranteed by design.

- (3) Available over commercial temperature range only.

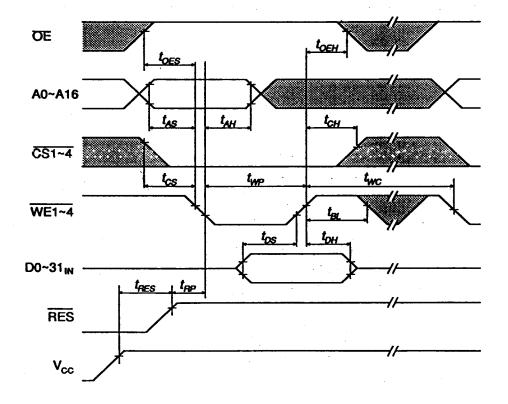

## **Read Cycle Timing Waveform**

# \* Input pulse levels: 0.0V to 3.0V \* Input rise and fall times: 5ns \* Input and Output timing reference levels: 1.5V \* V<sub>∞</sub>=5V±10% \* Module tested in 32 bit mode. Output Load \* Input and Output liming reference levels: 1.5V \* V<sub>∞</sub>=5V±10% \* Including scope and jig

ISSUE 1.1 : SEPTEMBER1993 PUMA 3E4000X-12/15/20

# **AC WRITE CHARACTERISTICS - BYTE AND PAGE**

| W | rite | Cv | cle |

|---|------|----|-----|

|   |      |    |     |

| Parameter                           | Symbol           | min          | typ      | max        | Unit |

|-------------------------------------|------------------|--------------|----------|------------|------|

| Address Set-up Time                 | t <sub>as</sub>  | 0            | -        | •          | ns   |

| Chip Select Set-up Time             | tcs              | 0            | -        | . <b>-</b> | ns   |

| Write Pulse Width                   | t <sub>wp</sub>  | 150          | -        | -          | ns   |

|                                     | t <sub>cw</sub>  | 150          | -        | •          | ns   |

| Address Hold Time                   | t <sub>AH</sub>  | 150          | -        | -          | ns   |

| Data Set-up Time                    | t <sub>os</sub>  | 100          | -        | •          | ns   |

| Data Hold Time                      | t <sub>DH</sub>  | 0            | -        | -          | ns   |

| Chip Select Hold Time               | t <sub>ch</sub>  | 0            | -        | -          | ns   |

| Output Enable Set-up Time           | t <sub>oes</sub> | 0            | -        | -          | ns   |

| Output Enable Hold Time             | t <sub>oeh</sub> | 0            | -        | -          | ns   |

| Data Latch Time                     | t <sub>DL</sub>  | 200          | -        | -          | ns   |

| Write Cycle Time                    | t <sub>wc</sub>  | -            | -        | 10         | ms   |

| Byte Load Window                    | t <sub>ec</sub>  | 100          | -        | -          | μs   |

| Byte Load Cycle                     | t <sub>BLC</sub> | 0.35         | <u>-</u> | 30         | μs   |

| Reset to Write Set-up Time          | t <sub>BP</sub>  | <b>. 100</b> | -        | -          | μs   |

| V <sub>∞</sub> to Reset Set-up Time | t <sub>RES</sub> | 1            | -        | -          | μs   |

Note: (1) Normal writing is not possible when the RES terminal becomes low during writing. The RES terminal should not be made low for at least 10ms after the last writing pulse is input.

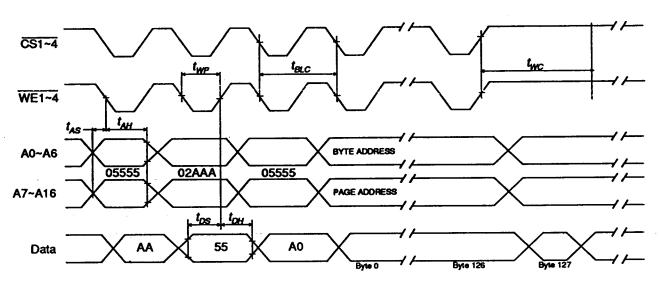

# **AC Write Waveform - WE Controlled**

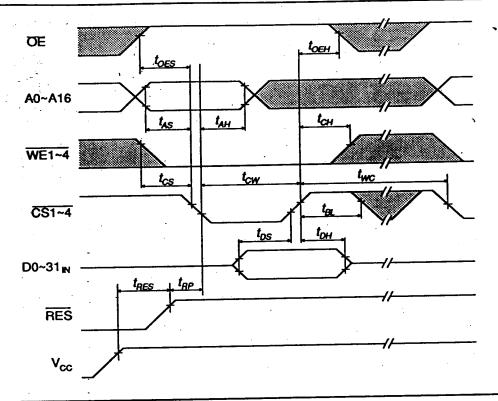

# AC Write Waveform - CS Controlled

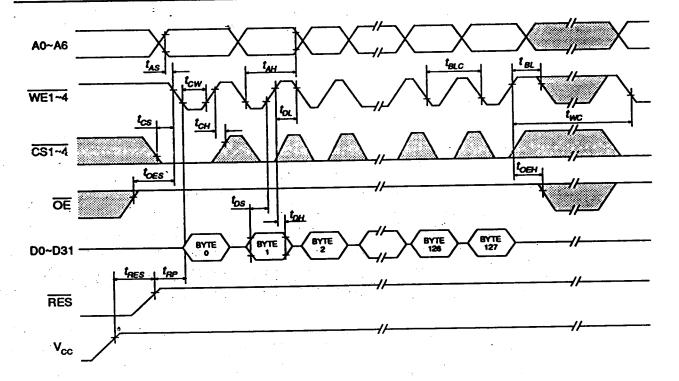

Page Mode Write Waveform - WE Controlled

Note: A7 through A16 must specify the page address during each high to low transition of WE (or CS).

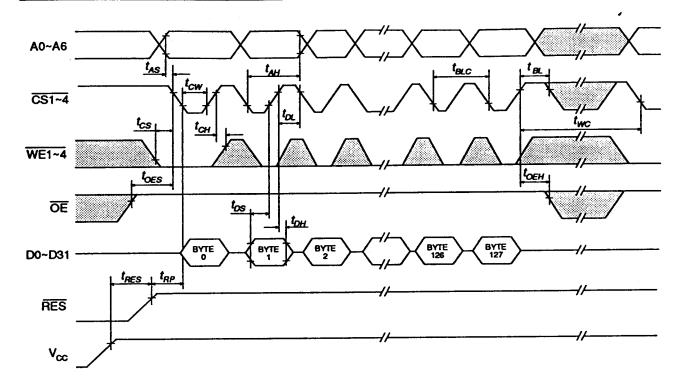

# Page Mode Write Waveform - CS Controlled

Note: A7 through A16 must specify the page address during each high to low transition of WE (or CS).

## **Software Protected Write Waveform**

Notes: (1) A7 through A15 must specify the page address during each high to low transition of WE (or CS)

(2) The example above is for the PUMA 3E4000X module operating in 8 bit mode.

| DATA Polling Characteristics |                  |     |     |     |        |  |

|------------------------------|------------------|-----|-----|-----|--------|--|

| Parameter                    | Symbol           | min | typ | max | Unit , |  |

| Output Enable Hold Time      | t <sub>oek</sub> | 0   | -   | -   | ns     |  |

| Output Enable Set-up Time    | t <sub>oes</sub> | 0   | -   | -   | ns     |  |

| Write Start Time             | t <sub>ow</sub>  | 150 | -   | -   | ns     |  |

| Write Cycle Time             | t <sub>wc</sub>  | -   | -   | 10  | ms     |  |

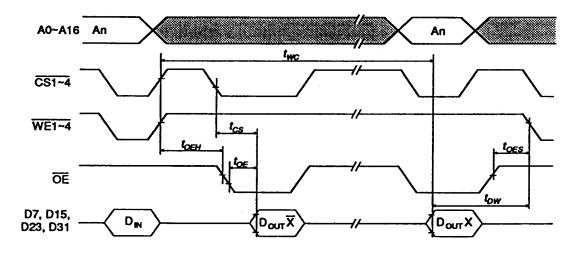

# **DATA Polling Waveform**

•

<u>:</u> .

#### **DEVICE OPERATION**

#### Read

The PUMA 3E4000X is accessed in the same way as a static RAM, with the data stored at the memory location determined by the address pins being placed on the output pins when CS1~4 and OE are low, and WE1~4 are high. Whenever CS1~4 or OE are high, the outputs are in the OFF or high impedance state.

#### Write

A low pulse on WE1~4 with CS1~4 low or a low pulse on CS1~4 with WE1~4 low indicates a write cycle. The address is latched on the falling edge of CS1~4 or WE1~4, and the data is latched on the first rising edge of CS1~4 or WE1~4. Once a byte write has begun it will automatically time itself to completion.

#### **Page Mode Write**

This operation mode allows 1 to 128 bytes of data to be loaded into a device, which are then simultaneously written. Once the first byte has been written, each subsequent byte must have the high to low transition of WE1~4 (or CS1~4) within 30µs of the same transition of the previous byte. If CS1~4 and WE1~4 are held high for 100µs after a byte has been loaded, the loaded bytes are automatically written. A7 to A16 specify the page address (which must be valid during the above transitions) and A0 to A6 specify which bytes within the page are to be written. Note that the bytes may be loaded in any order and may be changed within the same load period.

#### **DATA Polling**

In order to detect the end of a Write Cycle, DATA Polling is provided. During a Write operation (Byte or Page) an attempt to read the last byte written will result in the complement of the written data appearing on D7 (or D15, D23 or D31, depending on the device selected). Once the Write Cycle is complete, true data appears on the outputs and the next Write Cycle may begin. Using this method of indicating the end of a Write can effectively halve the total write time.

#### Write Cycle Endurance

Each device used on the PUMA 3E4000X is able to withstand at least 10<sup>5</sup> Write/Erase cycles when used in Page Mode, and at least 10<sup>4</sup> such cycles when used in Byte Mode.

#### **Data Protection**

Both hardware and software protection is provided as described below.

Four types of hardware protection give high security against accidental writes:

- (a) If RES is kept low, no devices on the PUMA 3E4000X can be Erased or Programmed, so data can be protected while V<sub>∞</sub> is switched.

- (b) OE low, CS1~4 or WE1~4 high inhibits inadvertent Write Cycles during power-on and power-off. Write Cycle timing specifications must be observed concurrently.

- (c) Pulses of less than 20ns on WE1~4 do not initiate a Write Cycle.

- (d) If  $V_{cc} \le 3.0V$ , Write is inhibited

Software controlled data protection, once enabled by the user, means that a software algorithm must be used before any write can be performed. To enable this feature the algorithm on page 9 is followed, and must be reused for each subsequent write operation. Once set the data protection remains operational until it is disabled by the using the second algorithm; power transitions will not reset this feature.

## **Operating Modes**

The table below shows the logic inputs required to control the operating modes of each EEPROM on the PUMA 3E4000X. Note that  $\overline{CS}$  and  $\overline{WE}$  below are accessed by  $\overline{CS1}\sim4$  and  $\overline{WE1}\sim4$  respectively to allow 8, 16 and 32 bit operation.

\*Further operating information can be found in the EEPROM application notes available from MSI.

| MODE          | cs | ŌĒ | WE | RES            | Outputs               |

|---------------|----|----|----|----------------|-----------------------|

| Standby       | 1  | X  | X  | X              | High Z                |

| Read          | 0  | 0  | 1  | V <sub>H</sub> | D <sub>out</sub>      |

| Write         | 0  | 1  | 0  | V <sub>H</sub> | D <sub>M</sub>        |

| Deselect      | 0  | 1  | 1  | V <sub>H</sub> | High Z                |

| Write Inhibit | X  | X  | 1  | X              |                       |

|               | X  | 0  | X  | X              |                       |

| Data Polling  | 0  | 0  | 1  | V <sub>H</sub> | D <sub>out</sub> (D7) |

| Program       | X  | X  | X  | 0              | High Z                |

$$1 = V_H$$

$$0 = V_L$$

$$V_H = V_{cc}-1.0V \text{ to } V_{cc}+1.0V$$

$$X = Don't \text{ care}$$

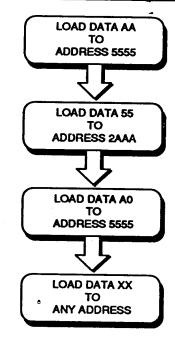

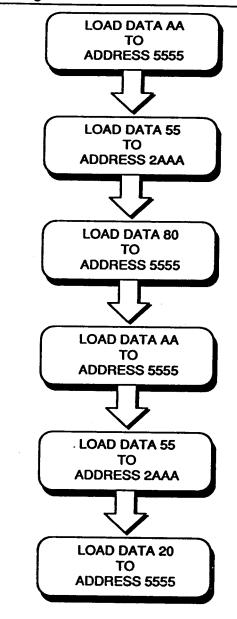

# Software Data Protection

The algorithms below describe the process by which an individual 128K x 8 device on the PUMA may be software write protected and unprotected. Thus, these algorithms apply to the PUMA operating in 8 bit mode; if 16 or 32 bit modes are being used, then the relevant data would be placed on the 16 or 32 bit buses as two or four 8 bit bytes respectively e.g. 5555<sub>H</sub> and 55555555<sub>H</sub>. In the case of 16 bit mode, this process would be repeated twice with the appropriate devices selected.

The PUMA 3E4000X is shipped with data Protection NOT ENABLED. In this mode data should be protected during power-up and power-down operations through the use of external circuits.

Once data protection has been enabled it is set for the life of the device unless the reset algorithm is followed. In protected mode write operations to the device(s) on the PUMA must be preceeded by a series of three write operations to three specific locations, after which 1 to 128 bytes of data may be written. Once the page load cycle is complete, the device(s) return to the data protected state.

NOTE: Once initiated, the sequence of write operations to Enable and Disable Write Protect should not be interrupted.

# Enable Algorithm(1)(4)(2)

#### Disable Algorithm(1)

#### Notes:

- (1) Data Format I/O7-I/O0 (Hex);

Once Initiated, this sequence of write operations should not be interrupted.

- (2) Enable Write Protect state will be initiated at end of write even if no other data is loaded.

- (3) 1 to 128 bytes of data may be loaded.

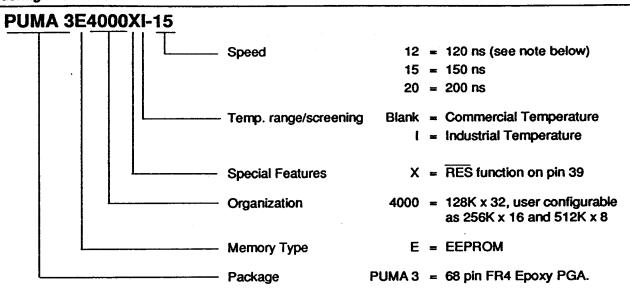

# **Ordering Information**

NOTE: THE 120 ns MODULE IS AVAILIBLE OVER THE COMMERCIAL TEMPERATURE RANGE ONLY.

The policy of the company is one of continuous development and while the information presented in this data sheet is believed to be accurate, no liability is assumed for any data contained within. The company reserves the right to make changes without notice at any time.

© 1988 This design is the property of Mosaic Semiconductor, Inc.

10

7420 Carroll Road San Diego, CA 92121 Tel: (619) 271 4565 FAX: (619) 271 6058

038928 🗸 \_ \_